D Read register number 1 32 bit Register

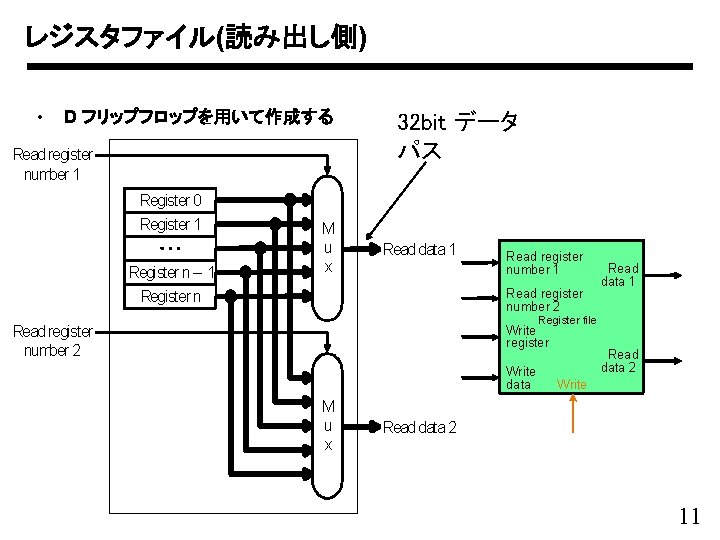

レジスタファイル(読み出し側) • D フリップフロップを用いて作成する Read register number 1 32 bit データ パス Register 0 Register 1 Register n – 1 Register n M u x Read data 1 Read register number 2 Read data 1 Register file Read register number 2 Write register Write data M u x Read data 2 Write Read data 2 11

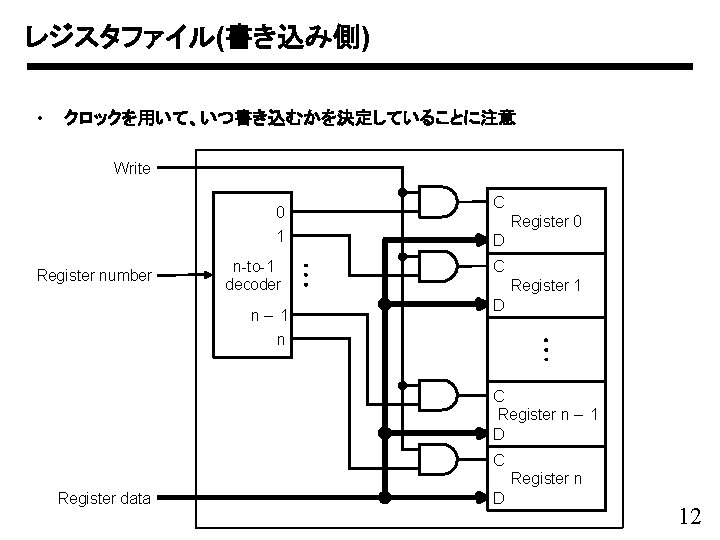

レジスタファイル(書き込み側) • クロックを用いて、いつ書き込むかを決定していることに注意 Write 0 1 Register number n-to-1 decoder n– 1 C Register 0 D C Register 1 D n C Register n – 1 D C Register n Register data D 12

機能ユニットの組み合わせによるMIPSの実装 • それぞれの命令の実装に必要な機能ユニットを組み合わせる。 Mem. Write Instruction address Address PC Instruction Add Sum Write data Instruction memory Read data Data memory 16 Sign extend 32 Mem. Read a. Instruction memory 5 Register numbers 5 5 Data b. Program counter a. Data memory unit 3 Read register 1 Read register 2 Registers Write register Write data c. Adder b. Sign-extension unit ALU control Read data 1 Data ALU Zero ALU result Read data 2 どのように組み合わせて、 データパスを構築すれば 良いのであろうか? Reg. Write a. Registers b. ALU 13

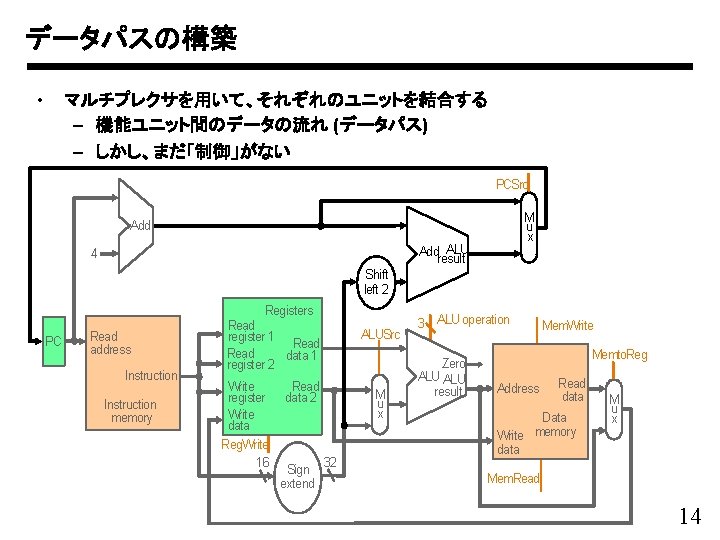

データパスの構築 • マルチプレクサを用いて、それぞれのユニットを結合する – 機能ユニット間のデータの流れ (データパス) – しかし、まだ「制御」がない PCSrc M u x Add ALU result 4 Shift left 2 Registers PC Read address Instruction memory Read register 1 Read data 1 register 2 Write register Write data Reg. Write 16 ALUSrc Read data 2 Sign extend M u x 32 3 ALU operation Zero ALU result Mem. Write Memto. Reg Address Read data Data memory Write data M u x Mem. Read 14

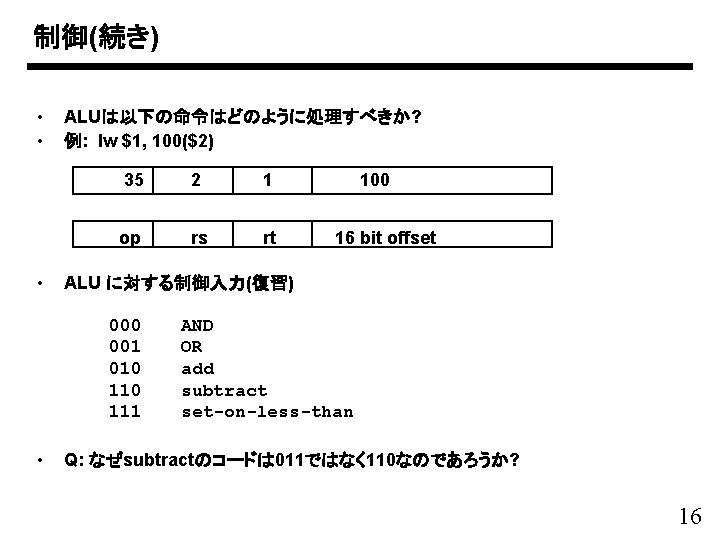

ALUの復習 • ALUの制御信号 000 = and 001 = or 010 = add 110 = subtract 111 = slt Binvert a Bnegate a 0 b 0 Operation Carry. In Result 0 ALU 0 Less Carry. Out a 1 b 1 0 Carry. In ALU 1 Less Carry. Out Result 1 a 2 b 2 0 Carry. In ALU 2 Less Carry. Out Result 2 Zero 1 b Less 0 1 2 Result a 31 b 31 0 Carry. In ALU 31 Less Result 31 Set Overflow 3 Carry. Out 17

![制御 (全体) 0 M u x Add 4 Instruction [31– 26] PC Instruction [25– 制御 (全体) 0 M u x Add 4 Instruction [31– 26] PC Instruction [25–](http://slidetodoc.com/presentation_image/2380d052585b52b414454c18fe609963/image-20.jpg)

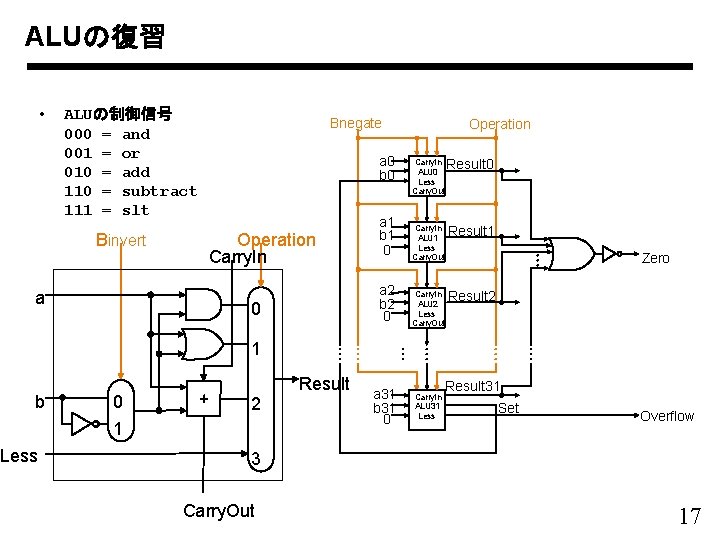

制御 (全体) 0 M u x Add 4 Instruction [31– 26] PC Instruction [25– 21] Read address Instruction [15– 11] 1 Shift left 2 Reg. Dst Branch Mem. Read Memto. Reg ALUOp Mem. Write ALUSrc Reg. Write Read register 1 Instruction [20– 16] Instruction [31– 0] Instruction memory Control ALU result 0 M u x 1 Read data 1 Read register 2 Registers Read Write data 2 register Zero 0 M u x 1 Write data ALU result Address Write data Instruction [15– 0] 16 Sign extend Read data Data memory 1 M u x 0 32 ALU control Instruction [5– 0] 20

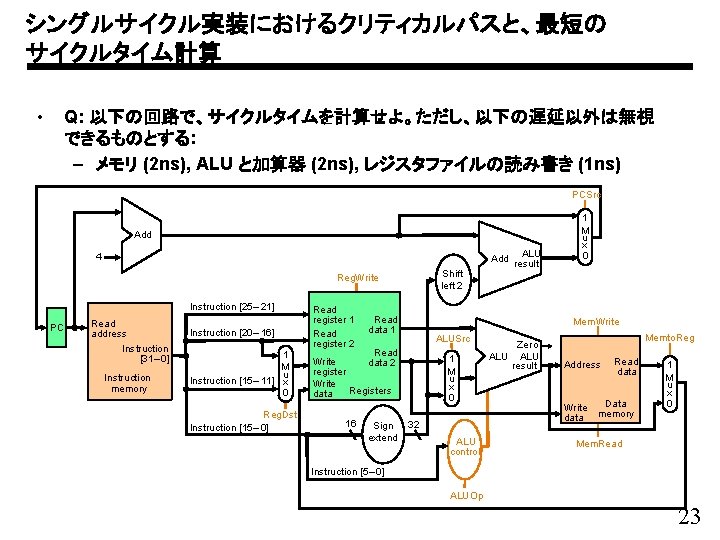

シングルサイクル実装におけるクリティカルパスと、最短の サイクルタイム計算 • Q: 以下の回路で、サイクルタイムを計算せよ。ただし、以下の遅延以外は無視 できるものとする: – メモリ (2 ns), ALU と加算器 (2 ns), レジスタファイルの読み書き (1 ns) PCSrc Add 4 Shift left 2 Reg. Write Instruction [25– 21] PC Read address Instruction [31– 0] Instruction memory Instruction [20– 16] 1 M u Instruction [15– 11] x 0 Reg. Dst Instruction [15– 0] Read register 1 Read register 2 Read data 1 Mem. Write ALUSrc Read data 2 1 M u x 0 Write register Write Registers data 16 Sign extend ALU Add result 1 M u x 0 32 ALU control Zero ALU result Memto. Reg Address Write data Read data Data memory 1 M u x 0 Mem. Read Instruction [5– 0] ALUOp 23

- Slides: 24