Cyclic Combinational Circuits Analysis for Synthesis Marc D

Cyclic Combinational Circuits: Analysis for Synthesis Marc D. Riedel and Jehoshua Bruck California Institute of Technology

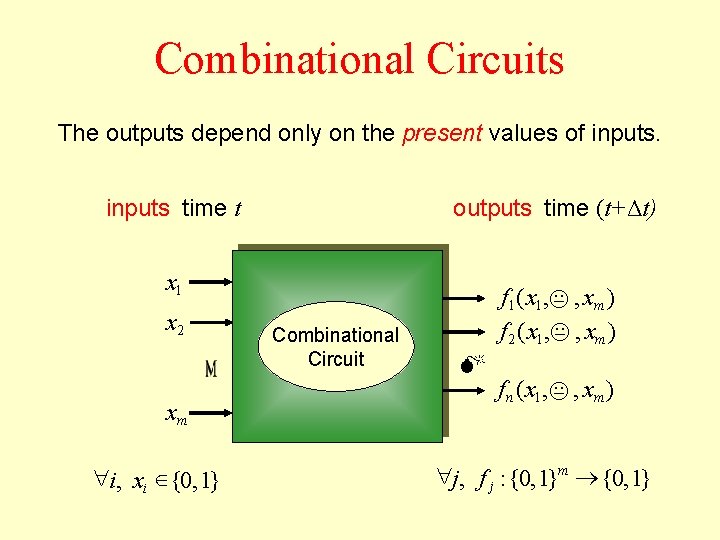

Combinational Circuits The outputs depend only on the present values of inputs time t outputs time (t+Δt) x 1 x 2 xm "i, xi Î{0, 1} Combinational Circuit f 1 ( x 1 , K , xm ) f 2 ( x 1 , K , xm ) M f n ( x 1 , K , xm ) "j, f j : {0, 1}m ® {0, 1}

Combinational Circuits Generally acyclic (i. e. , feed-forward) structures. x y z f 1 x y x z f 2 y z

Combinational Circuits Generally acyclic (i. e. , feed-forward) structures. 0 0 1 1 1 1 0 0 1 0

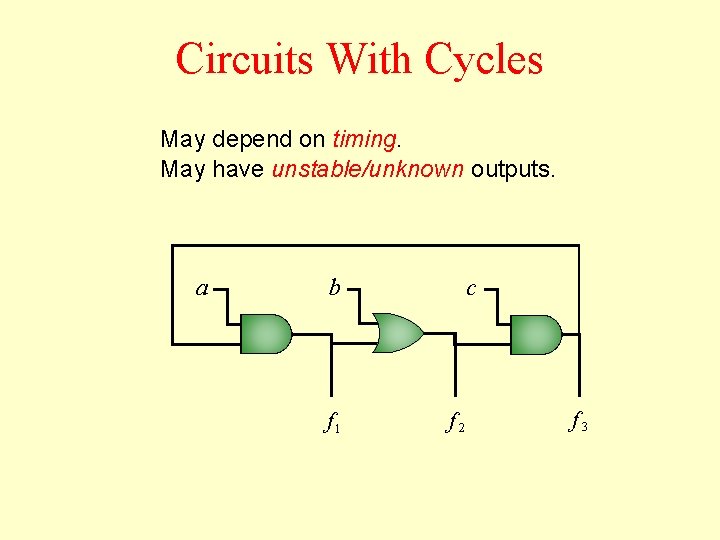

Circuits With Cycles May depend on timing. May have unstable/unknown outputs. a b f 1 c f 2 f 3

Circuits With Cycles May depend on timing. May have unstable/unknown outputs. 1 ? 0: non-controlling for OR 1: non-controlling for AND 1 0 ? ?

Cyclic Combinational Circuits Cyclic circuits can be combinational. Example due to Rivest (1977): a b c f 1 f 2 f 3 f 4 f 5 f 6

Cyclic Combinational Circuits Cyclic circuits can be combinational. Example due to Rivest (1977): 1 b c f 1 f 2 f 3 f 4 f 5 f 6

Cyclic Combinational Circuits Cyclic circuits can be combinational. Example due to Rivest (1977): 1 b c f 1 f 2 f 3 1 f 5 f 6

Cyclic Combinational Circuits Cyclic circuits can be combinational. Example due to Rivest (1977): a b c f 1 f 2 f 3 f 4 f 5 f 6

Cyclic Combinational Circuits Cyclic circuits can be combinational. Example due to Rivest (1977): 0 b c f 1 f 2 f 3 f 4 f 5 f 6

Cyclic Combinational Circuits Cyclic circuits can be combinational. Example due to Rivest (1977): 0 b c 0 f 2 f 3 f 4 f 5 f 6

Cyclic Combinational Circuits Cyclic circuits can be combinational. Example due to Rivest (1977): a b c f 1 f 2 f 3 f 4 f 5 There is feedback is a topological sense, but not in an electrical sense. f 6

Cyclic Combinational Circuits Cyclic circuits can be combinational. Example due to Rivest (1977): a b a(b + c) c b +a c ( a + b) b a +b c There is feedback is a topological sense, but not in an electrical sense. c b( a + c ) c +a b

Cyclic Combinational Circuits Cyclic circuits can be smaller than acyclic circuits. • Rivest constructed a family of cyclic circuits that are 2 3 the size of any equivalent acyclic circuits (1977). • We have constructed a family of cyclic circuits that are 1 2 the size.

Cyclic Combinational Circuits Most circuits can be optimized with cycles. • We have proposed a general methodology for the synthesis of cyclic combinational circuits. • Benchmark circuits were optimized significantly: improvements of up to 30% in the area (literal count). For details see The Synthesis of Cyclic Combinational Circuits, DAC’ 03.

Illustrative Example Lookup Table for Digits of p a b c d Circuit e f g h e = b + ac d + d (a + c) f = a(bc + b d ) + d (a b c + bc) g = ac(b d + bd ) + a (b cd + c (b + d )) h = a cd + a(b cd + bc d ) inputs 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 dcba p 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 3 1 4 1 5 9 2 6 5 3 5 8 9 7 9 3 outputs hgfe 0011 0001 0100 0001 0101 1001 0010 0101 0011 0101 1000 1001 0111 1001 0011

Example: Digits of p h Multilevel acyclic network: e = agh + a d + b g f = a d g + a(de + g ) g = a bc + h (c(ad + b ) + a d ) e h = a cd + a(b cd + bc d ) Cost: 33 (literal count) f

Example: Digits of p e Multilevel cyclic network: e = f (ah + c) + dh + b f = a d g + a(b d + bc) g = a bc + h (ae + a d + b c) g h = f (a(c + d ) + cd ) Cost: 31 (literal count) f h Is it combinational?

Example: Digits of p e Inputs d, c, b, a = [0, 0, 0, 0]: e = f (ah + c) + dh + b =1 =1 =g =1 f = a d g + a(b d + bc) g = a bc + h (ae + a d + b c) = 0 h = f (a(c + d ) + cd ) g =0 =0 Outputs h, g, f, e = [0, 0, 1, 1] (3 is the first digit of p ) f h

Example: Digits of p e Inputs d, c, b, a = [1, 1, 1, 1]: e = f (ah + c) + dh + b = f +h =1 f = a d g + a(b d + bc) g = a bc + h (ae + a d + b c) = e h = f (a(c + d ) + cd ) Outputs h, g, f, e = [0, 0, 1, 1] (3 is the 16 th digit of p ) =1 =1 =0 g =0 f h

Analysis e There are cycles in a topological sense, but none are sensitized in an electrical sense. g f h

Analysis e Timing Analysis: find the length of sensitized paths. Combinationality Analysis: ensure that there are no sensitized cycles. ? g f h

Synthesis Goal: optimize a multi-level network representation. Strategy: introduce cycles in the substitute/minimize step. network N 1 network N 2 e = b + ac d + d (a + c) e = f ( ah + c ) + dh + b f = a d g + a ( b d + bc ) f = a(bc + b d ) + d (a b c + bc) h = a cd + a(b cd + bc d ) g = a b c + h ( ae + a d + b c ) h = f ( a ( c + d ) + cd ) Cost 40 (literal count) Cost 31 (literal count) g = ac(b d + bd ) + a (b cd + c (b + d ))

Synthesis N 1 N 3 Select best solution through a branch-and-bound search. N 2 N 4 N 5 N 6 N 7 N 9 N 8

Analysis Central step in synthesis: • Determine if a cyclic circuit is combinational for all input assignments in the “care” set. • Perform analysis symbolically (using BDD’s). Prior work: Malik (1994), Shiple et al. (1996), and Edwards (2003) have addressed the analysis of cyclic combinational circuits.

Analysis Novel algorithm based on a “first-cut” approach. Observation: for each input assignment, in every strongly-connected component at least one node must be fully defined independently of the others. e g f h

Marginal Given a node function e F ( X , Y ) the marginal F¯Y specifies, in terms of X, when F is fully defined independently of Y. X: primary input variables Y: internal variables g f h

Marginal For example, consider e e = f (ah + c) + dh + b Suppose b = 0 : e = f (ah + c) + dh + 1 = 1 g f h

Marginal For example, consider e e = f (ah + c) + dh + b Suppose a = c = d = 0 : e = f (0 h + 0) + 0 h + b = b g f h

Marginal For example, consider e e = f (ah + c) + dh + b For input assignments that satisfy e ¯ ( f , h) = a c d + b g e is fully defined, independently of f, h. The marginal can be computed efficiently (with BDD’s) f h

Analysis e First-Cut Analysis: Cut each node from the network, and apply the algorithm recursively. g f h

Analysis Necessary condition: e Either e ¯ ( f , h) or f¯g g or g ¯ (e , h) or h¯ f f h

Analysis Necessary and sufficient condition: e Either e ¯ ( f , h) and or f¯g and g is combinational or g ¯ (e , h) or and is combinational h¯ f and is combinational f h

Analysis for Synthesis Advantage of Recursive Formulation: Attack problem by breaking network into components. N 1 N 2 N 3 Optimal local solution (subject to constraints) is part of optimal global solution (subject to constraints).

Analysis for Synthesis Exclude non-combinational components. e Design f, g component: f = a gh + a(de + g ) g = a f h + f ( ae + b c ) f g Not combinational. Exclude all solutions with this component. h

Analysis for Synthesis Cache combinational components. e Design e, f, g component: e = f (ah + c) + dh + b f f = a d g + a(b d + bc) g = a bc + h (ae + a d + b c) g Combinational. Focus on h. h

Analysis for Synthesis Cache combinational components. e ? Design e, f, g component: e = f (ah + c) + dh + b f f = a d g + a(b d + bc) g = a bc + h (ae + a d + b c) g Combinational. Focus on h. h

Analysis for Synthesis Cache combinational components. e ? Design e, f, g component: e = f (ah + c) + dh + b f f = a d g + a(b d + bc) g = a bc + h (ae + a d + b c) g Combinational. Focus on h. h

Analysis for Synthesis Cache combinational components. e ? Design e, f, g component: e = f (ah + c) + dh + b f f = a d g + a(b d + bc) g = a bc + h (ae + a d + b c) g Combinational. Focus on h. h

Analysis for Synthesis Cache combinational components. e ? Design e, f, g component: e = f (ah + c) + dh + b f f = a d g + a(b d + bc) g = a bc + h (ae + a d + b c) g Combinational. Focus on h. h

Analysis for Synthesis Cache combinational components. e ? Design e, f, g component: e = f (ah + c) + dh + b f f = a d g + a(b d + bc) g = a bc + h (ae + a d + b c) h = f (a(c + d ) + cd ) Combinational. Focus on h. g h Combinational.

Implementation: CYCLIFY Program • Incorporated synthesis methodology in a general logic synthesis environment (Berkeley SIS package). • Trials on wide range of circuits – randomly generated – benchmarks – industrial designs. • Consistently successful at finding superior cyclic solutions.

Benchmark Circuits (best examples) Circuit dc 1 ex 6 p 82 t 4 bbsse 5 xp 1 s 386 dk 17 apla tms cse clip m 2 s 510 t 1 exp # Inputs 4 8 5 12 11 11 7 11 10 10 8 11 9 8 25 21 13 8 # Outputs 7 11 14 8 11 11 10 11 11 12 16 11 5 16 13 23 24 18 Berkeley Simplify Caltech Cyclify Improvement 39 34 12. 80% 85 76 10. 60% 104 90 13. 50% 109 89 18. 30% 118 106 10. 20% 123 109 11. 40% 131 113 13. 70% 160 136 15. 00% 185 131 29. 20% 185 158 14. 60% 212 177 16. 50% 213 189 11. 30% 231 207 10. 40% 260 227 12. 70% 273 206 24. 50% 309 276 10. 70% 320 262 18. 10% Cost (literals in factored form) of Berkeley SIS Simplify vs. Cyclify

Benchmarks Example: EXP circuit cost measured by the literal count in the substitute/minimize phase Acyclic Solution (Berkeley SIS): cost 320 Cyclic Solution (Caltech CYCLIFY): cost 262

Discussion Cyclic Combinational Circuits: • Most combinational circuits can be optimized with cycles. • Optimizations are significant. Symbolic framework for analysis: • Analyze combinationality and timing. • Tightly integrated with synthesis.

Future Directions • Extend ideas to decomposition and technology mapping phases of synthesis. • Address optimization of cyclic circuits for delay and power.

- Slides: 47