Curso de Doctorado Microelectrnica Digital Miguel ngel Aguirre

- Slides: 20

Curso de Doctorado: . Microelectrónica Digital Miguel Ángel Aguirre Echánove Departamento de Ingeniería Electrónica. Tema 5: Reconfiguración en FPGAs SRAM.

Indice de la presentación Introducción. Objetivos de la reconfiguración n Métodos de reconfiguración n – Reconfiguración Estática – Reconfiguracón Dinámica » RD Parcial Herramientas para RD n Estado del arte n 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 2

Introducción La FPGA tipo SRAM puede ser programada múltiples veces n Puede ser programada en tiempos de ejecución n Objetivos: n – Optimización del espacio efectivo – Reducción de consumo 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 3

Aplicaciones n Sistemas susceptibles de mejoras – Prototipos, sistemas en desarrollo n Sistemas con elementos activos e inactivos – Sistemas multimedia n Sistemas de difícil acceso – Apliaciones espaciales 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 4

Aplicaciones Filtros adaptativos n Redes neuronales n Estimadores de movimiento n Sistemas Operativos en Hardware n Computadores de juegos de instrucciones dinámico n 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 5

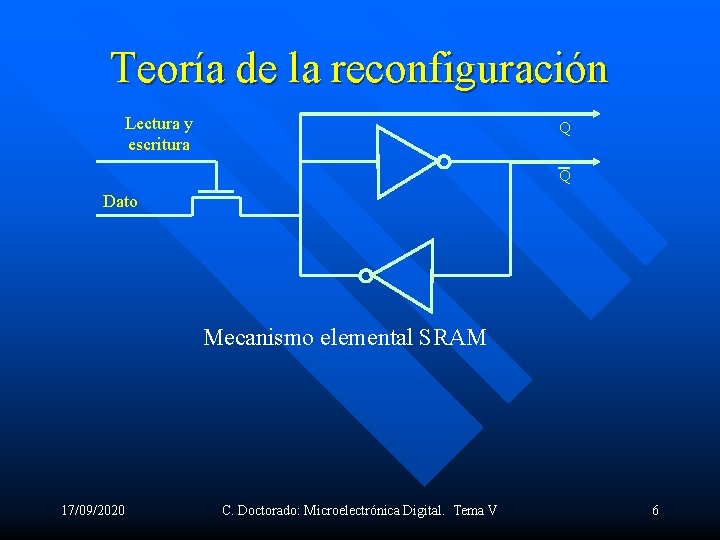

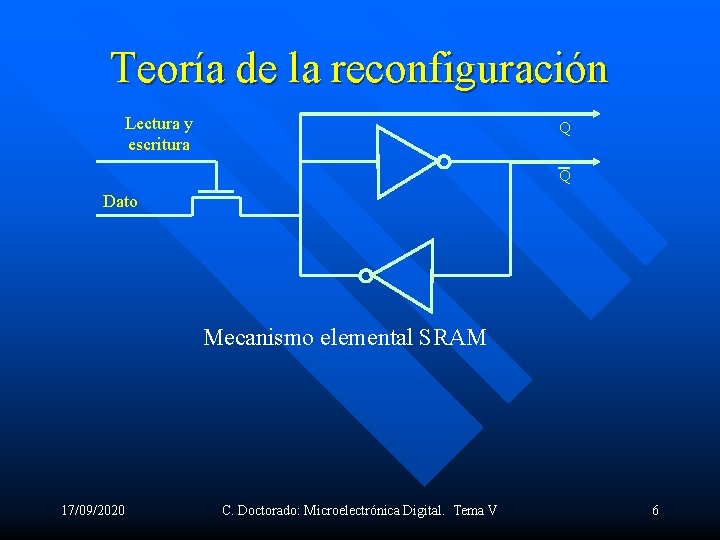

Teoría de la reconfiguración Lectura y escritura Q Q Dato Mecanismo elemental SRAM 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 6

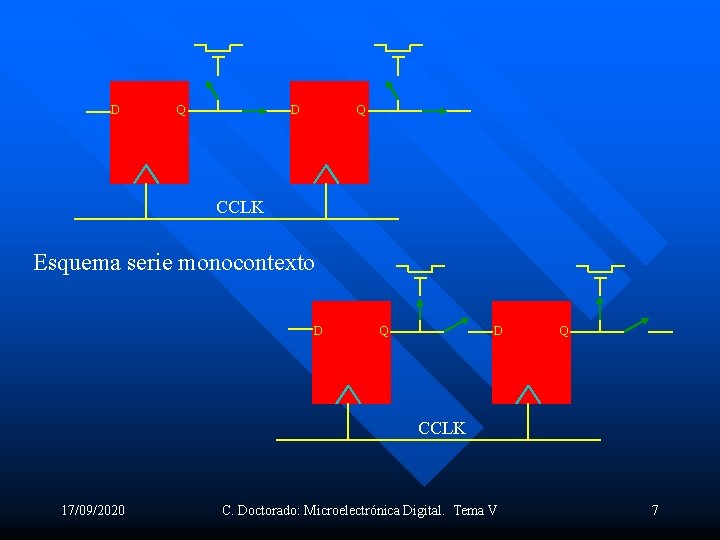

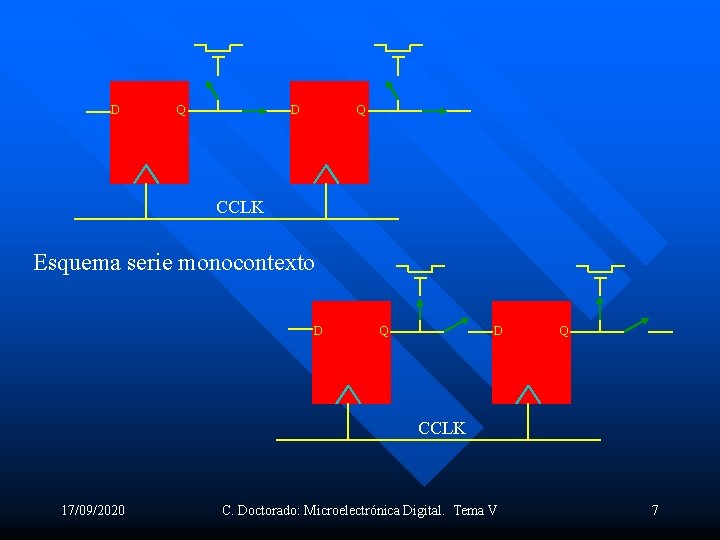

D Q CCLK Esquema serie monocontexto D Q CCLK 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 7

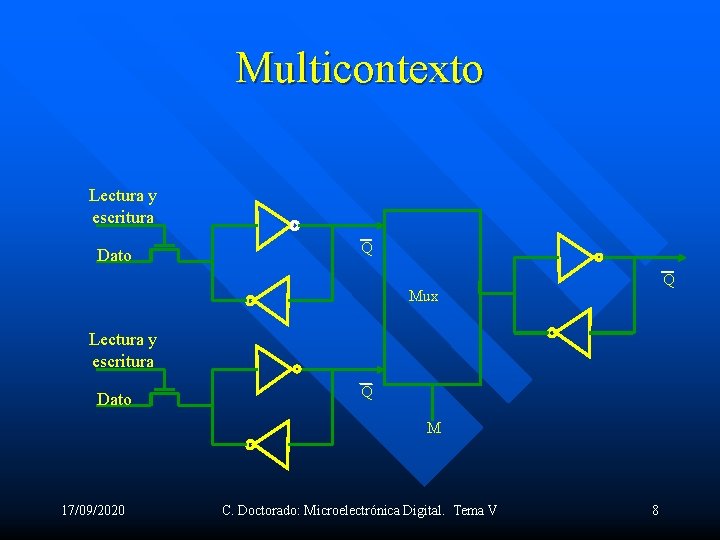

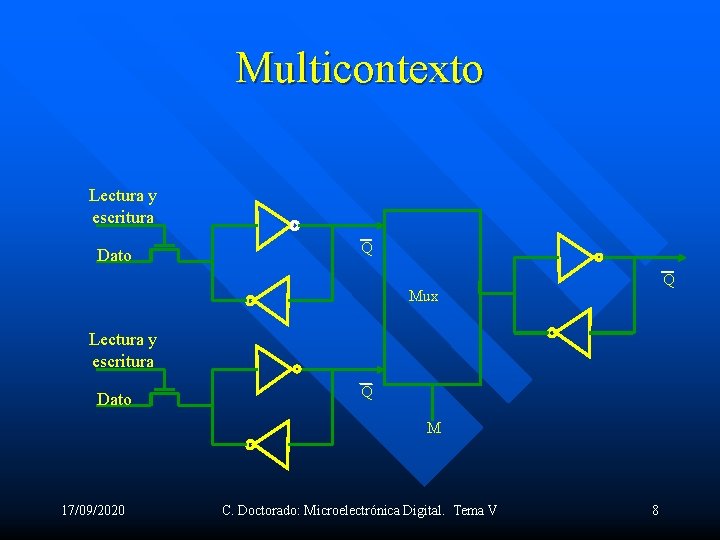

Multicontexto Lectura y escritura Dato Q Q Mux Lectura y escritura Dato Q M 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 8

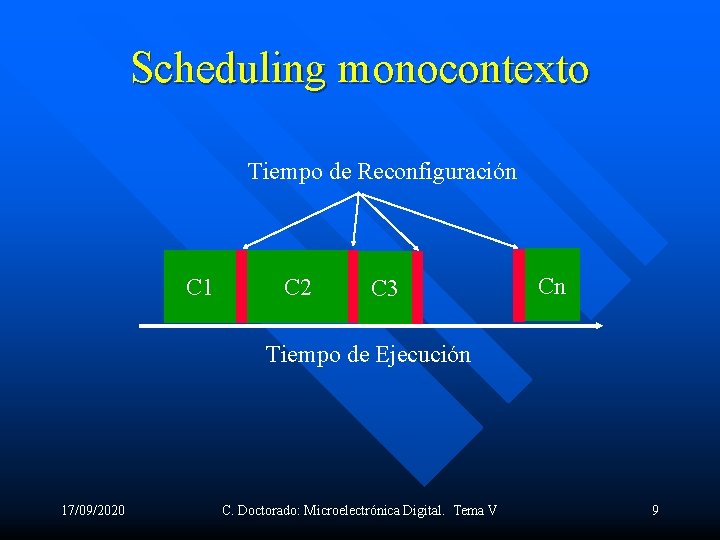

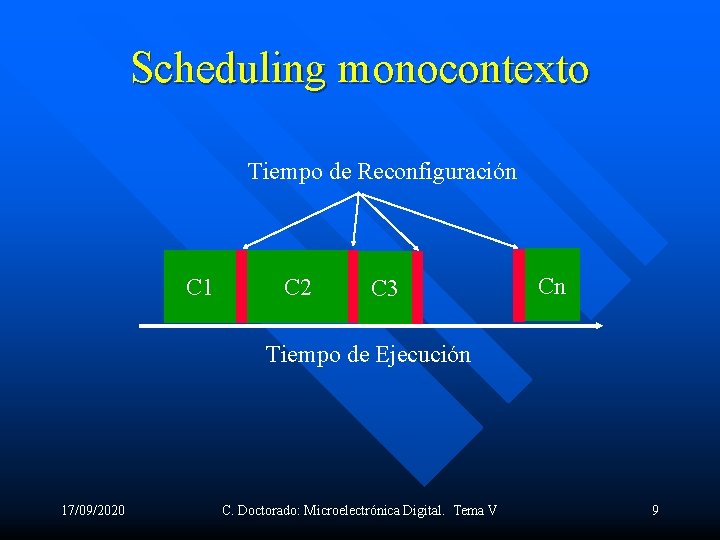

Scheduling monocontexto Tiempo de Reconfiguración C 1 C 2 C 3 Cn Tiempo de Ejecución 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 9

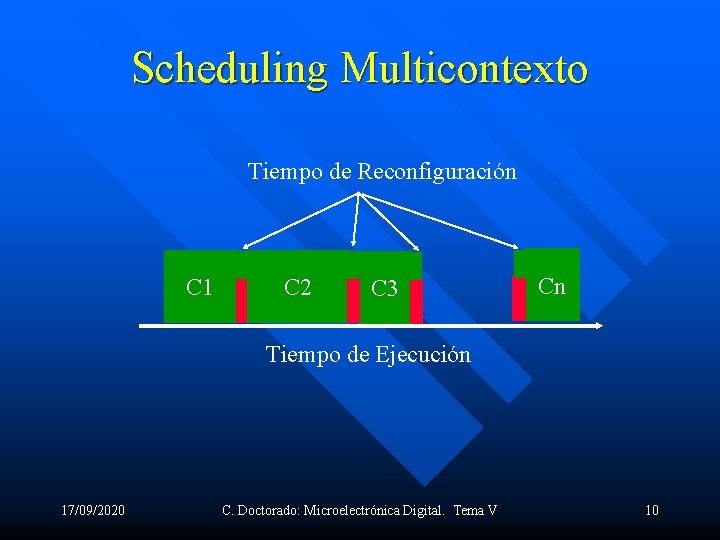

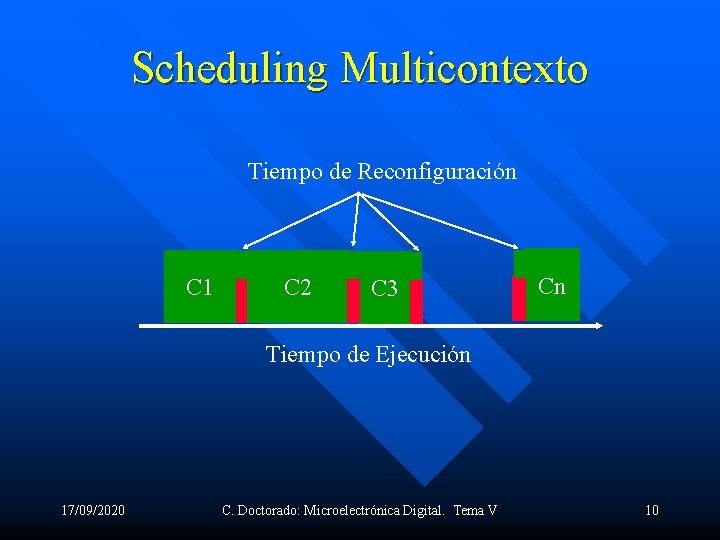

Scheduling Multicontexto Tiempo de Reconfiguración C 1 C 2 C 3 Cn Tiempo de Ejecución 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 10

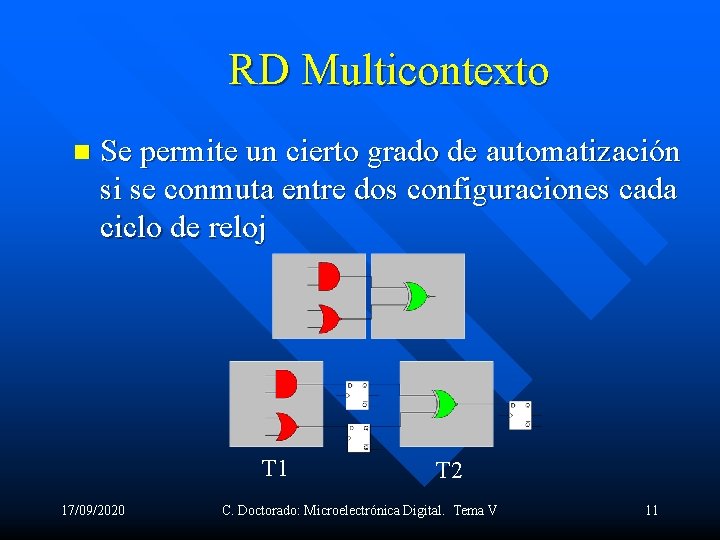

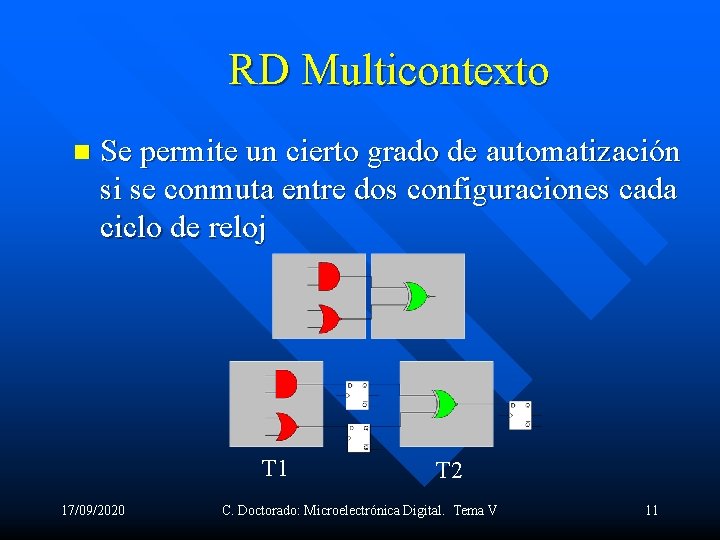

RD Multicontexto n Se permite un cierto grado de automatización si se conmuta entre dos configuraciones cada ciclo de reloj T 1 17/09/2020 T 2 C. Doctorado: Microelectrónica Digital. Tema V 11

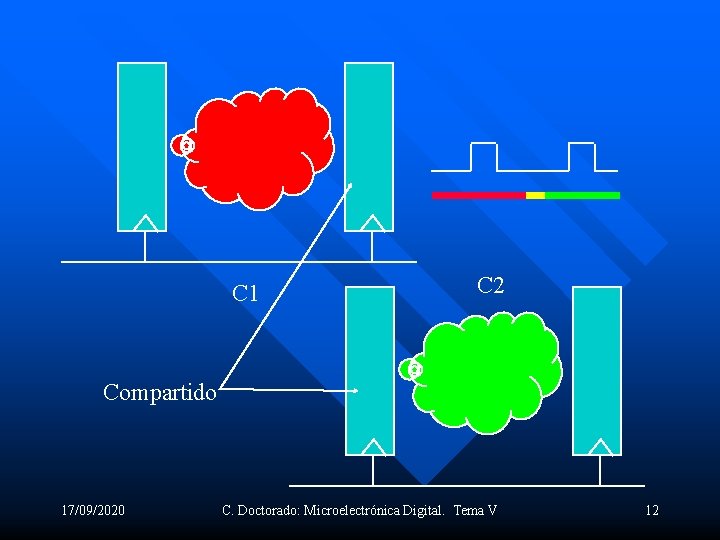

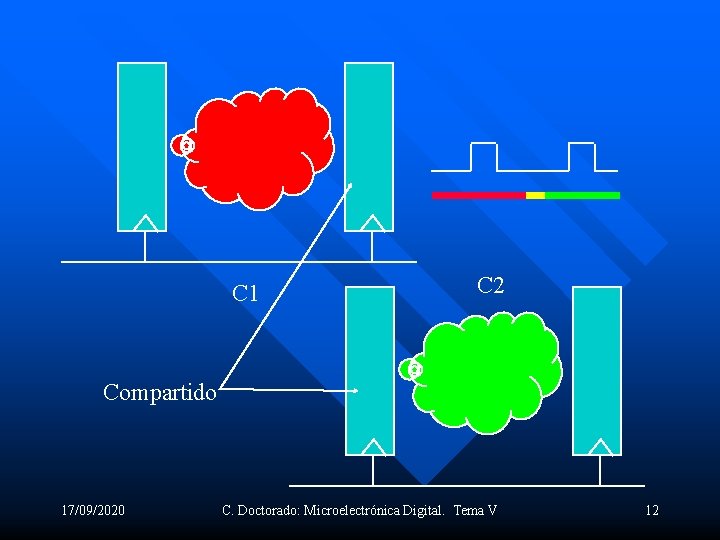

C 1 C 2 Compartido 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 12

Arquitecturas de configuración Esquema mapa de memoria 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 13

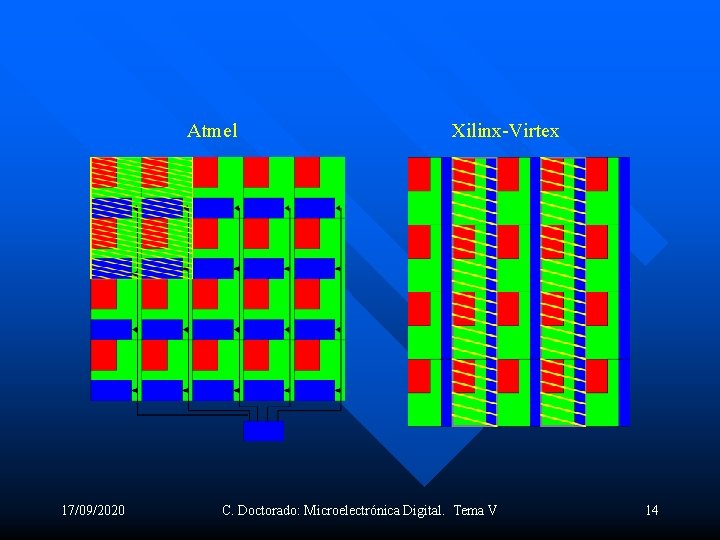

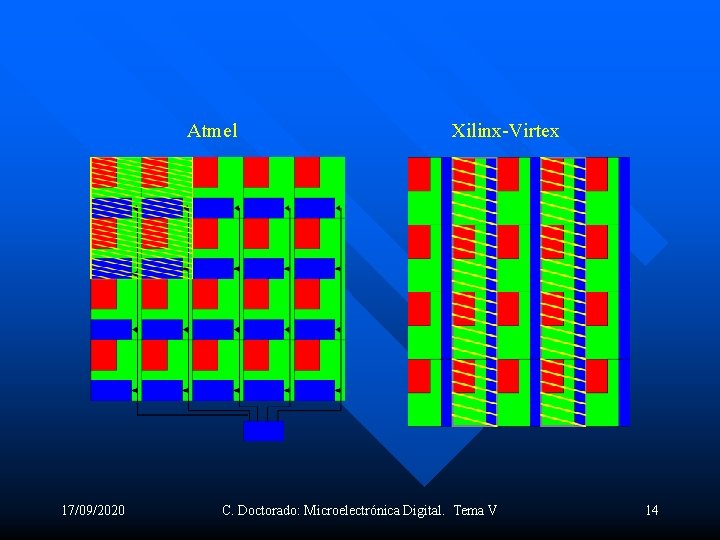

Atmel 17/09/2020 Xilinx-Virtex C. Doctorado: Microelectrónica Digital. Tema V 14

Herramientas Bajo grado de automatización n Solamente la creación del Bit. Stream impide que se trabaje a muy bajo nivel n 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 15

Modelo de Ejecución 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 16

Planificación espacial n Planificación de los recursos » Uso de recursos especiales: Memorias n Organización del área que se va a asignar a cada tarea: » Condicionada por la arquitectura de reconfiguración » Condicionada por las asimetrías de la arquitectura del dispositivo » Condicionada por los puntos de conexión entre el área fija y el área modificada. 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 17

Sobrecoste de operaciones n Las técnicas de diseño para RDP (Reconfiguración Dinámica Parcial) se basan, fundamentalmente en la creación de macrobloques programados a bajo nivel. n Se aconseja, para reducir tiempos de desarrollo utilizar arquitecturas de elementos expandibles. n Esto reduce enormemente la capacidad de selección de arquitecturas de operadores 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 18

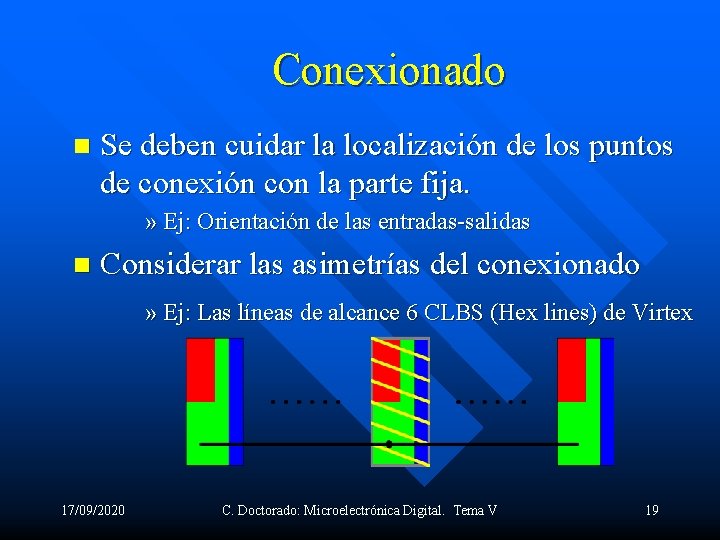

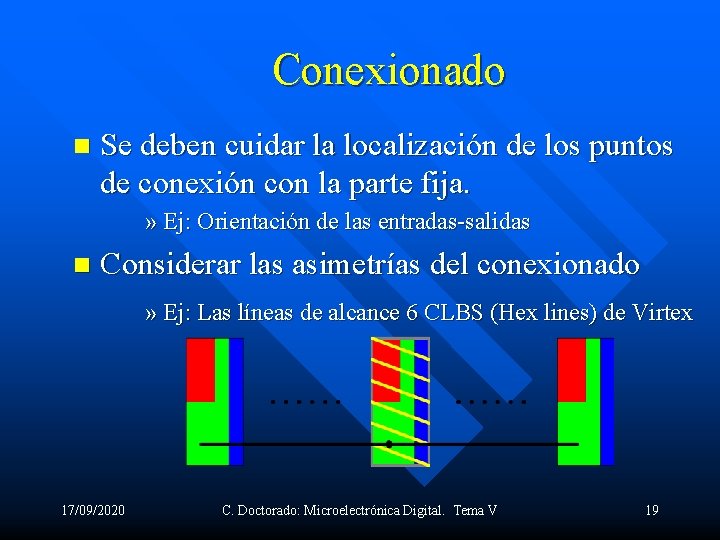

Conexionado n Se deben cuidar la localización de los puntos de conexión con la parte fija. » Ej: Orientación de las entradas-salidas n Considerar las asimetrías del conexionado » Ej: Las líneas de alcance 6 CLBS (Hex lines) de Virtex 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 19

Conclusiones n Diseñar sistemas con capacidad RD resulta ventajoso, si: – Si se precisa flexibilidad en el diseño – Si hay ganancia en determinadas tareas hardware junto con su tiempo de reconfiguración – Si se admite un reparto ventajoso: » Costo en área J » Costo en tiempos de desarrollo L » Costos de tiempos de ejecución K 17/09/2020 C. Doctorado: Microelectrónica Digital. Tema V 20