Cu trc my tnh Chng 3 B X

Cấu trúc máy tính Chương 3 BỘ XỬ LÝ TRUNG T M (CPU) 3/11/2021 Chương 3: Bộ xử lý trung tâm 1

Nội dung 3. 1. 3. 2. 3. 3. 3. 4. 3. 5. 3/11/2021 Cấu trúc cơ bản của CPU Tập lệnh Hoạt động của CPU Các kỹ thuật tiên tiến của bộ xử lý Kiến trúc Intel Chương 3: Bộ xử lý trung tâm 2

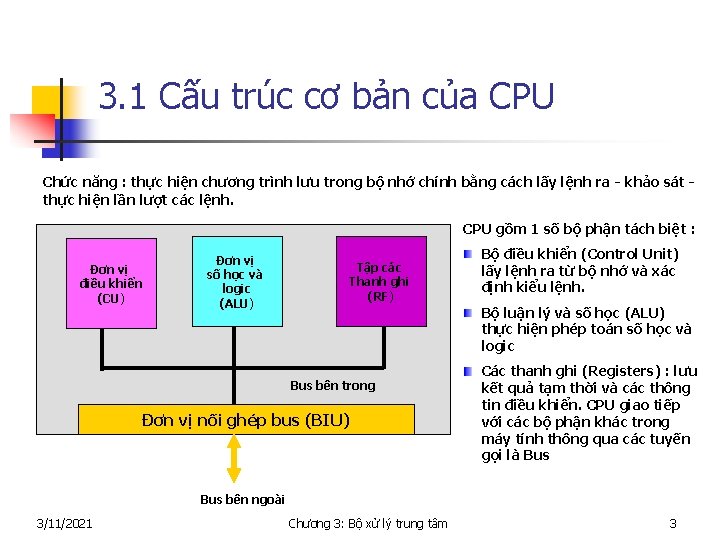

3. 1 Cấu trúc cơ bản của CPU Chức năng : thực hiện chương trình lưu trong bộ nhớ chính bằng cách lấy lệnh ra - khảo sát thực hiện lần lượt các lệnh. CPU gồm 1 số bộ phận tách biệt : Đơn vị điều khiển (CU) Đơn vị số học và logic (ALU) Tập các Thanh ghi (RF) Bộ điều khiển (Control Unit) lấy lệnh ra từ bộ nhớ và xác định kiểu lệnh. Bộ luận lý và số học (ALU) thực hiện phép toán số học và logic Bus bên trong Đơn vị nối ghép bus (BIU) Các thanh ghi (Registers) : lưu kết quả tạm thời và các thông tin điều khiển. CPU giao tiếp với các bộ phận khác trong máy tính thông qua các tuyến gọi là Bus bên ngoài 3/11/2021 Chương 3: Bộ xử lý trung tâm 3

Đơn vị điều khiển (CU) n Thanh ghi lệnh Các tín hiệu điều khiển bên trong CPU Các cờ Clock Các tín hiệu yêu cầu từ bus hệ thống Đơn vị điều khiển Các tín hiệu điều khiển đến bus hệ thống Bus điều khiển 3/11/2021 Chức năng n Điều khiển nhận lệnh từ bộ nhớ đưa vào thanh ghi lệnh n Tăng nội dung của PC để trỏ sang lệnh kế tiếp n Giải mã lệnh đã được nhận để xác định thao tác mà lệnh yêu cầu n Phát ra các tín hiệu điều khiển thực hiện lệnh n Nhận các tín hiệu yêu cầu từ bus hệ thống và đáp ứng với các yêu cầu đó. Chương 3: Bộ xử lý trung tâm 4

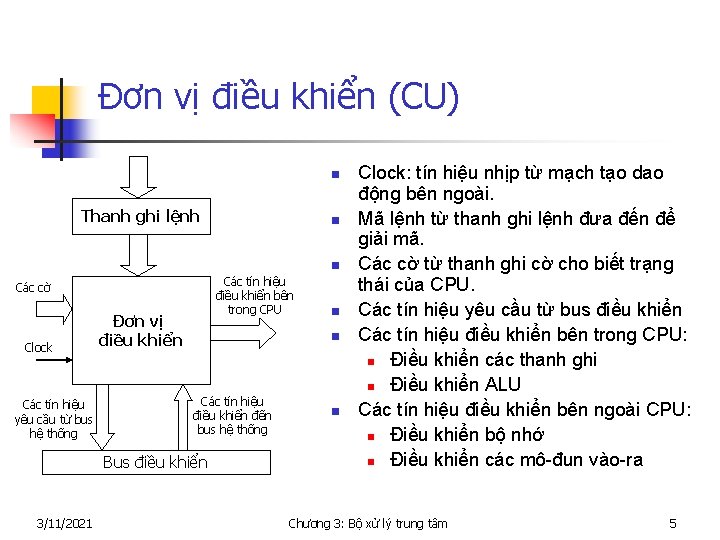

Đơn vị điều khiển (CU) n Thanh ghi lệnh n n Các tín hiệu điều khiển bên trong CPU Các cờ Clock Các tín hiệu yêu cầu từ bus hệ thống Đơn vị điều khiển n Các tín hiệu điều khiển đến bus hệ thống Bus điều khiển 3/11/2021 n n Clock: tín hiệu nhịp từ mạch tạo dao động bên ngoài. Mã lệnh từ thanh ghi lệnh đưa đến để giải mã. Các cờ từ thanh ghi cờ cho biết trạng thái của CPU. Các tín hiệu yêu cầu từ bus điều khiển Các tín hiệu điều khiển bên trong CPU: n Điều khiển các thanh ghi n Điều khiển ALU Các tín hiệu điều khiển bên ngoài CPU: n Điều khiển bộ nhớ n Điều khiển các mô-đun vào-ra Chương 3: Bộ xử lý trung tâm 5

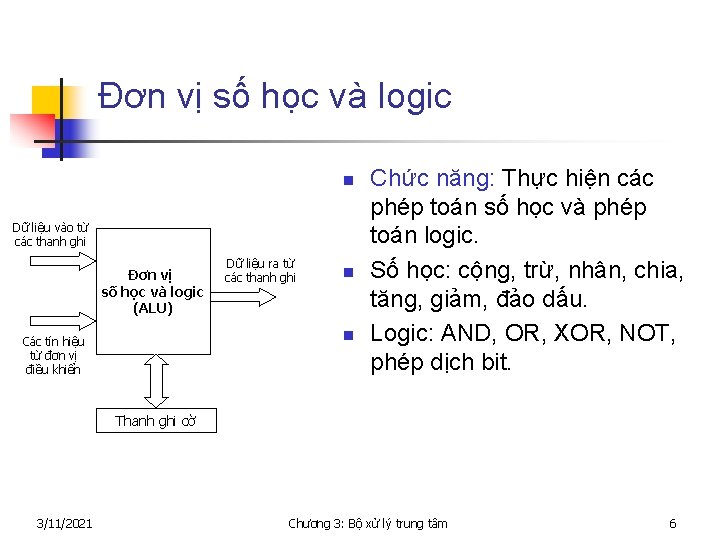

Đơn vị số học và logic n Dữ liệu vào từ các thanh ghi Đơn vị số học và logic (ALU) Dữ liệu ra từ các thanh ghi n n Các tín hiệu từ đơn vị điều khiển Chức năng: Thực hiện các phép toán số học và phép toán logic. Số học: cộng, trừ, nhân, chia, tăng, giảm, đảo dấu. Logic: AND, OR, XOR, NOT, phép dịch bit. Thanh ghi cờ 3/11/2021 Chương 3: Bộ xử lý trung tâm 6

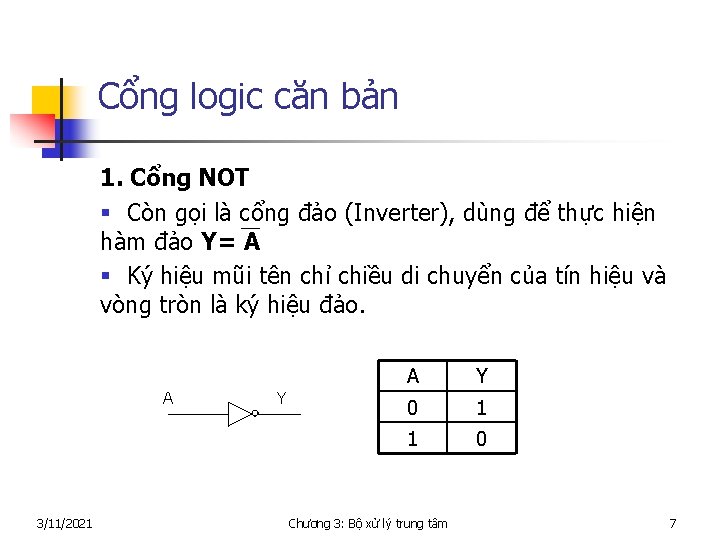

Cổng logic căn bản 1. Cổng NOT § Còn gọi là cổng đảo (Inverter), dùng để thực hiện hàm đảo Y= A § Ký hiệu mũi tên chỉ chiều di chuyển của tín hiệu và vòng tròn là ký hiệu đảo. A 3/11/2021 Y A Y 0 1 1 0 Chương 3: Bộ xử lý trung tâm 7

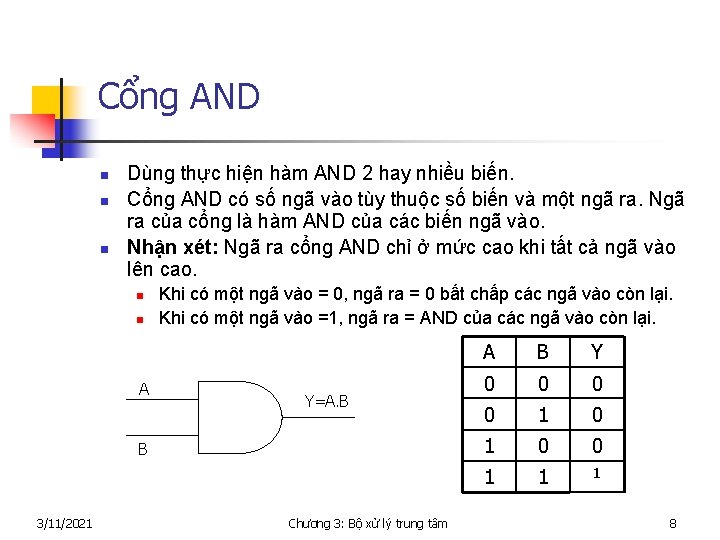

Cổng AND n n n Dùng thực hiện hàm AND 2 hay nhiều biến. Cổng AND có số ngã vào tùy thuộc số biến và một ngã ra. Ngã ra của cổng là hàm AND của các biến ngã vào. Nhận xét: Ngã ra cổng AND chỉ ở mức cao khi tất cả ngã vào lên cao. n n A Khi có một ngã vào = 0, ngã ra = 0 bất chấp các ngã vào còn lại. Khi có một ngã vào =1, ngã ra = AND của các ngã vào còn lại. Y=A. B B 3/11/2021 Chương 3: Bộ xử lý trung tâm A B Y 0 0 1 1 1 8

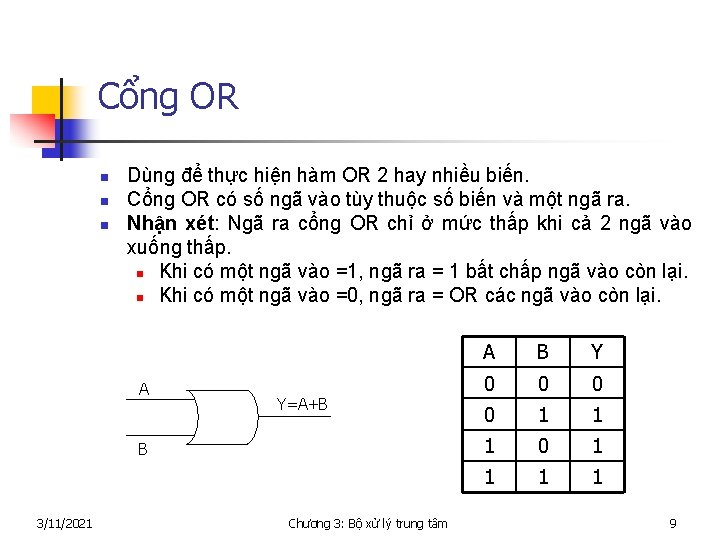

Cổng OR n n n Dùng để thực hiện hàm OR 2 hay nhiều biến. Cổng OR có số ngã vào tùy thuộc số biến và một ngã ra. Nhận xét: Ngã ra cổng OR chỉ ở mức thấp khi cả 2 ngã vào xuống thấp. n Khi có một ngã vào =1, ngã ra = 1 bất chấp ngã vào còn lại. n Khi có một ngã vào =0, ngã ra = OR các ngã vào còn lại. A Y=A+B B 3/11/2021 Chương 3: Bộ xử lý trung tâm A B Y 0 0 1 1 1 0 1 1 9

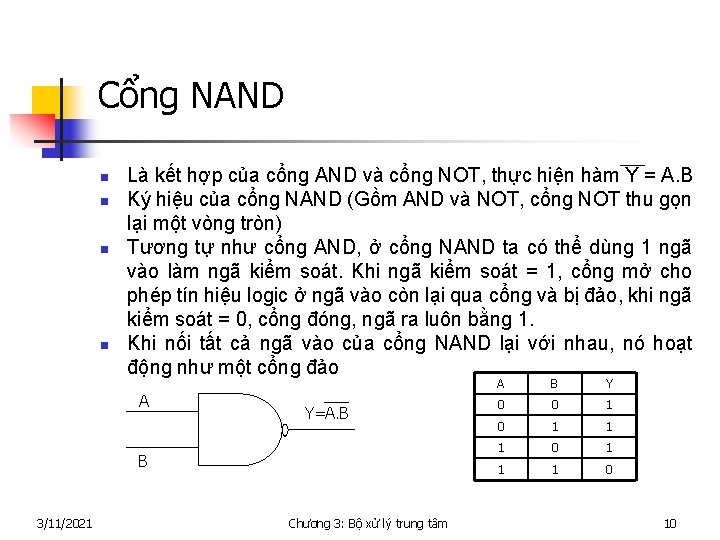

Cổng NAND n n Là kết hợp của cổng AND và cổng NOT, thực hiện hàm Y = A. B Ký hiệu của cổng NAND (Gồm AND và NOT, cổng NOT thu gọn lại một vòng tròn) Tương tự như cổng AND, ở cổng NAND ta có thể dùng 1 ngã vào làm ngã kiểm soát. Khi ngã kiểm soát = 1, cổng mở cho phép tín hiệu logic ở ngã vào còn lại qua cổng và bị đảo, khi ngã kiểm soát = 0, cổng đóng, ngã ra luôn bằng 1. Khi nối tất cả ngã vào của cổng NAND lại với nhau, nó hoạt động như một cổng đảo A Y=A. B B 3/11/2021 Chương 3: Bộ xử lý trung tâm A B Y 0 0 1 1 1 0 10

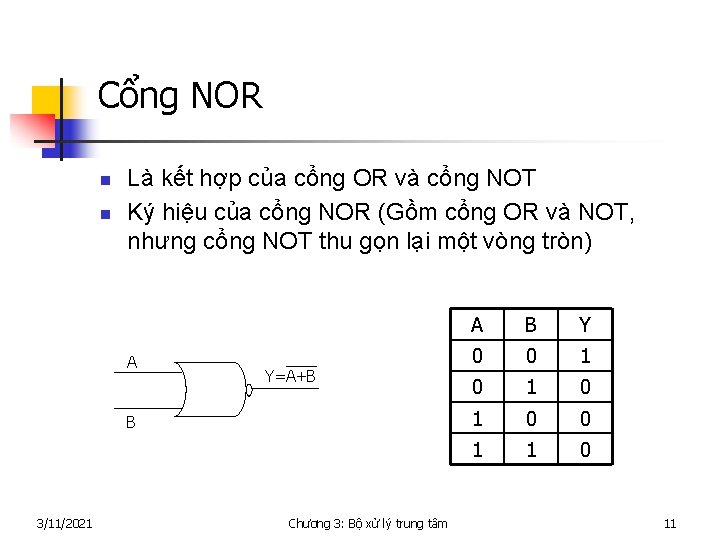

Cổng NOR n n Là kết hợp của cổng OR và cổng NOT Ký hiệu của cổng NOR (Gồm cổng OR và NOT, nhưng cổng NOT thu gọn lại một vòng tròn) A Y=A+B B 3/11/2021 Chương 3: Bộ xử lý trung tâm A B Y 0 0 1 0 1 0 0 1 1 0 11

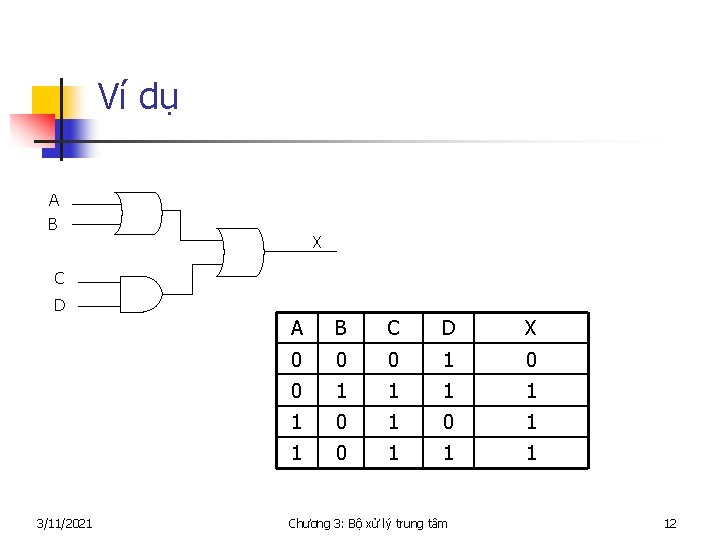

Ví dụ A B X C D 3/11/2021 A B C D X 0 0 0 1 1 1 0 1 1 1 Chương 3: Bộ xử lý trung tâm 12

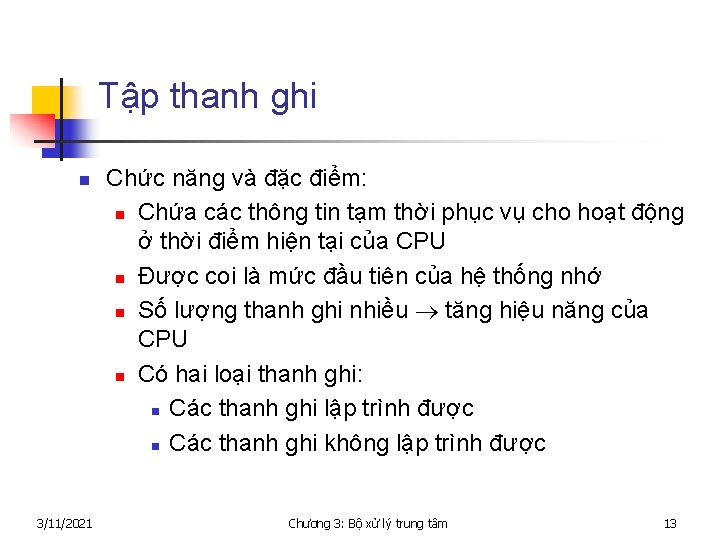

Tập thanh ghi n 3/11/2021 Chức năng và đặc điểm: n Chứa các thông tin tạm thời phục vụ cho hoạt động ở thời điểm hiện tại của CPU n Được coi là mức đầu tiên của hệ thống nhớ n Số lượng thanh ghi nhiều tăng hiệu năng của CPU n Có hai loại thanh ghi: n Các thanh ghi lập trình được n Các thanh ghi không lập trình được Chương 3: Bộ xử lý trung tâm 13

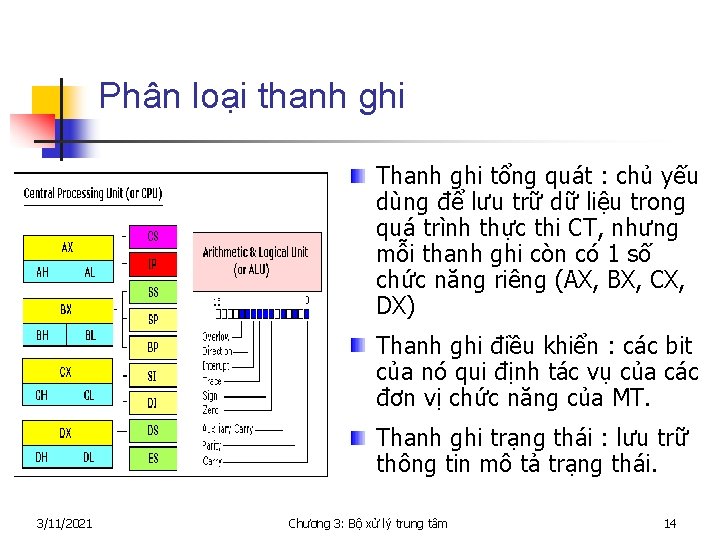

Phân loại thanh ghi Thanh ghi tổng quát : chủ yếu dùng để lưu trữ dữ liệu trong quá trình thực thi CT, nhưng mỗi thanh ghi còn có 1 số chức năng riêng (AX, BX, CX, DX) Thanh ghi điều khiển : các bit của nó qui định tác vụ của các đơn vị chức năng của MT. Thanh ghi trạng thái : lưu trữ thông tin mô tả trạng thái. 3/11/2021 Chương 3: Bộ xử lý trung tâm 14

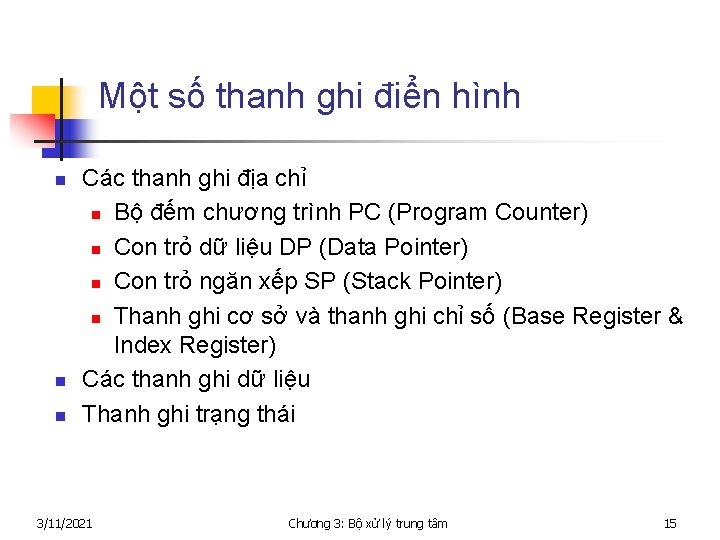

Một số thanh ghi điển hình n n n Các thanh ghi địa chỉ n Bộ đếm chương trình PC (Program Counter) n Con trỏ dữ liệu DP (Data Pointer) n Con trỏ ngăn xếp SP (Stack Pointer) n Thanh ghi cơ sở và thanh ghi chỉ số (Base Register & Index Register) Các thanh ghi dữ liệu Thanh ghi trạng thái 3/11/2021 Chương 3: Bộ xử lý trung tâm 15

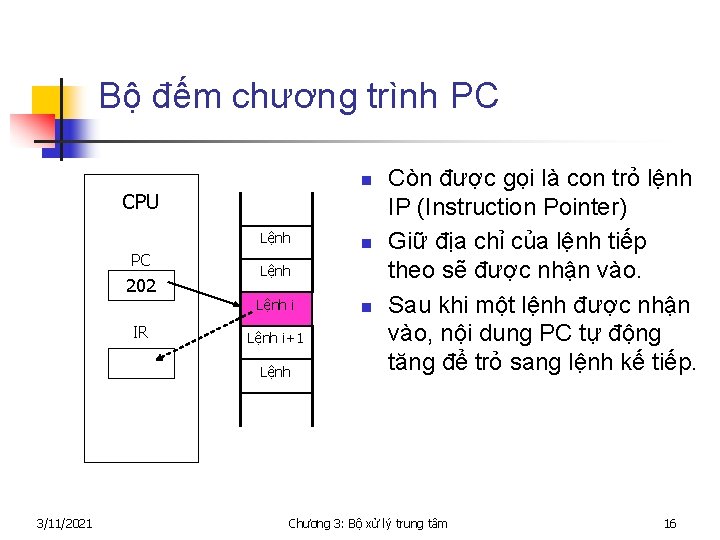

Bộ đếm chương trình PC n CPU Lệnh PC 202 IR Lệnh i+1 Lệnh 3/11/2021 n n Còn được gọi là con trỏ lệnh IP (Instruction Pointer) Giữ địa chỉ của lệnh tiếp theo sẽ được nhận vào. Sau khi một lệnh được nhận vào, nội dung PC tự động tăng để trỏ sang lệnh kế tiếp. Chương 3: Bộ xử lý trung tâm 16

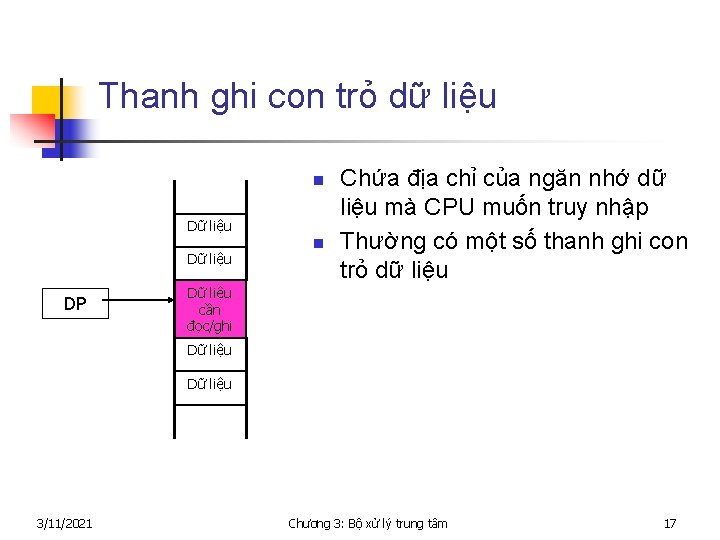

Thanh ghi con trỏ dữ liệu n Dữ liệu DP n Chứa địa chỉ của ngăn nhớ dữ liệu mà CPU muốn truy nhập Thường có một số thanh ghi con trỏ dữ liệu Dữ liệu cần đọc/ghi Dữ liệu 3/11/2021 Chương 3: Bộ xử lý trung tâm 17

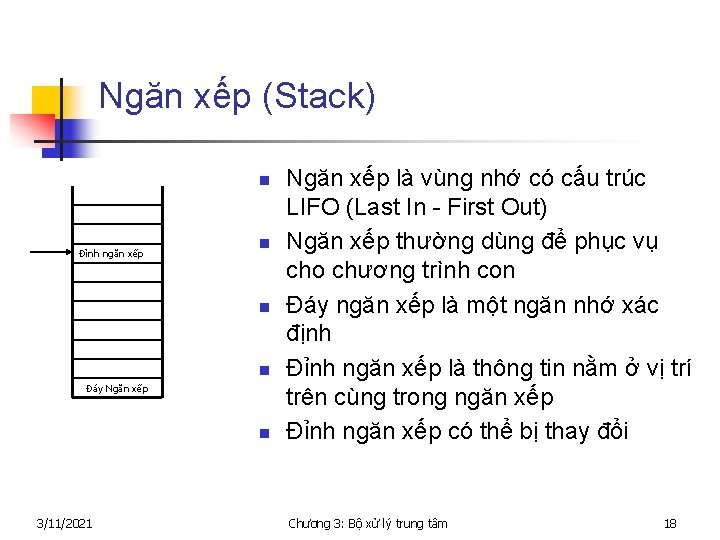

Ngăn xếp (Stack) n Đỉnh ngăn xếp n n n Đáy Ngăn xếp n 3/11/2021 Ngăn xếp là vùng nhớ có cấu trúc LIFO (Last In - First Out) Ngăn xếp thường dùng để phục vụ cho chương trình con Đáy ngăn xếp là một ngăn nhớ xác định Đỉnh ngăn xếp là thông tin nằm ở vị trí trên cùng trong ngăn xếp Đỉnh ngăn xếp có thể bị thay đổi Chương 3: Bộ xử lý trung tâm 18

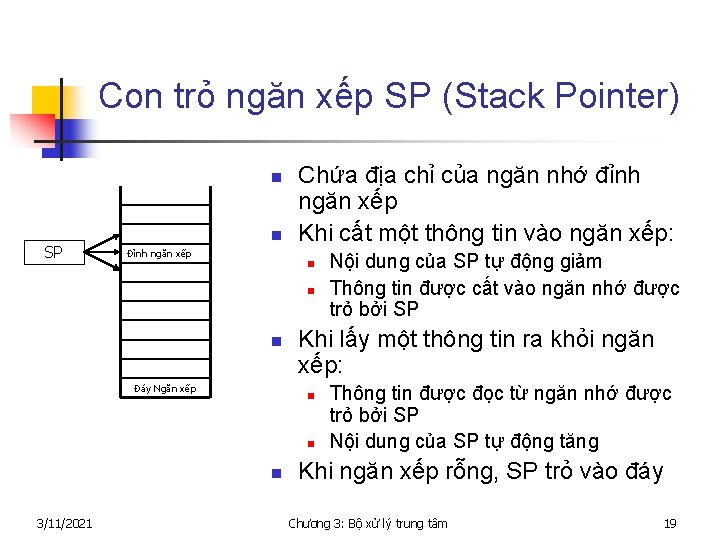

Con trỏ ngăn xếp SP (Stack Pointer) n SP n Đỉnh ngăn xếp Chứa địa chỉ của ngăn nhớ đỉnh ngăn xếp Khi cất một thông tin vào ngăn xếp: n n n Đáy Ngăn xếp Khi lấy một thông tin ra khỏi ngăn xếp: n n n 3/11/2021 Nội dung của SP tự động giảm Thông tin được cất vào ngăn nhớ được trỏ bởi SP Thông tin được đọc từ ngăn nhớ được trỏ bởi SP Nội dung của SP tự động tăng Khi ngăn xếp rỗng, SP trỏ vào đáy Chương 3: Bộ xử lý trung tâm 19

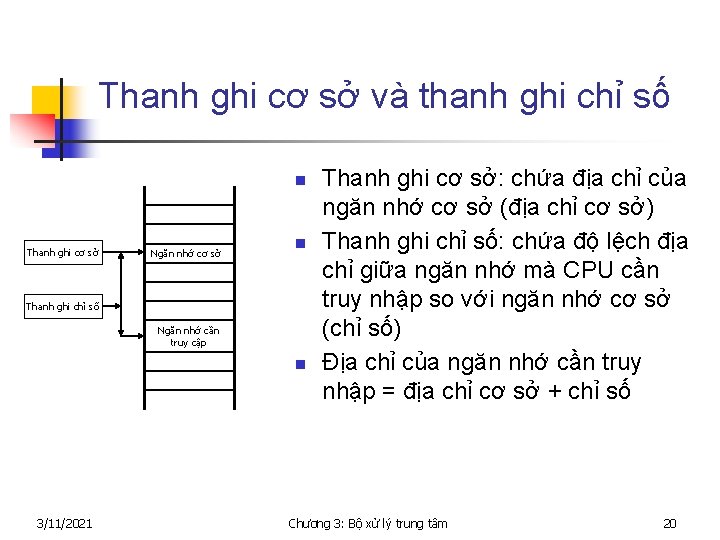

Thanh ghi cơ sở và thanh ghi chỉ số n Thanh ghi cơ sở Ngăn nhớ cơ sở n Thanh ghi chỉ số Ngăn nhớ cần truy cập n 3/11/2021 Thanh ghi cơ sở: chứa địa chỉ của ngăn nhớ cơ sở (địa chỉ cơ sở) Thanh ghi chỉ số: chứa độ lệch địa chỉ giữa ngăn nhớ mà CPU cần truy nhập so với ngăn nhớ cơ sở (chỉ số) Địa chỉ của ngăn nhớ cần truy nhập = địa chỉ cơ sở + chỉ số Chương 3: Bộ xử lý trung tâm 20

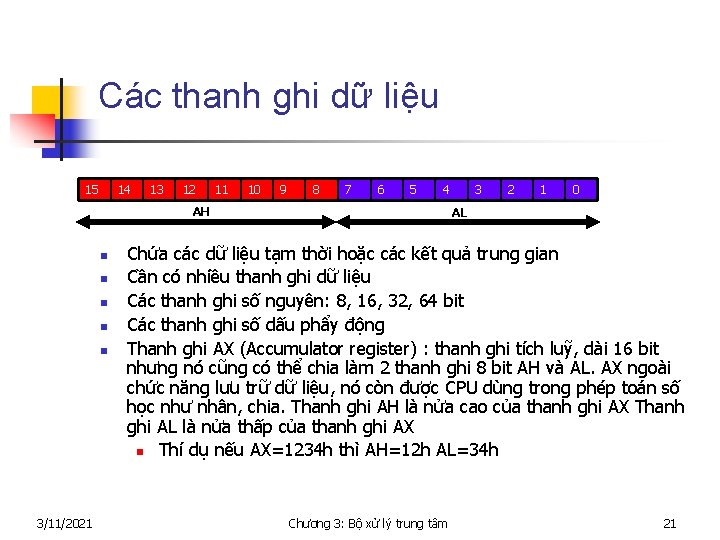

Các thanh ghi dữ liệu 15 14 13 12 11 10 9 8 7 6 5 4 AH n n n 3/11/2021 3 2 1 0 AL Chứa các dữ liệu tạm thời hoặc các kết quả trung gian Cần có nhiều thanh ghi dữ liệu Các thanh ghi số nguyên: 8, 16, 32, 64 bit Các thanh ghi số dấu phẩy động Thanh ghi AX (Accumulator register) : thanh ghi tích luỹ, dài 16 bit nhưng nó cũng có thể chia làm 2 thanh ghi 8 bit AH và AL. AX ngoài chức năng lưu trữ dữ liệu, nó còn được CPU dùng trong phép toán số học như nhân, chia. Thanh ghi AH là nửa cao của thanh ghi AX Thanh ghi AL là nửa thấp của thanh ghi AX n Thí dụ nếu AX=1234 h thì AH=12 h AL=34 h Chương 3: Bộ xử lý trung tâm 21

Các thanh ghi dữ liệu n n n 3/11/2021 Thanh ghi BX (Base register) : dài 16 bit nhưng nó cũng có thể chia làm 2 thanh ghi 8 bit BH và BL. BX lưu giữ địa chỉ của 1 thủ tục hay biến, nó cũng được dùng thực hiện các phép dời chuyển số học và dữ liệu. Thanh ghi DX (Data register) : dài 16 bit nhưng nó cũng có thể chia làm 2 thanh ghi 8 bit DH và DL. Thanh ghi DX : có vai trò đặc biệt trong phép nhân và phép chia ngoài chức năng lưu trữ dữ liệu. CX (Counter register) : thanh ghi này dùng làm bộ đếm trong các vòng lặp. Các lệnh tự động lặp lại và sau mỗi lần lặp giá trị của CX tự động giảm đi 1. CL thường chứa số lần dịch, quay trong các lệnh dịch, quay thanh ghi. CX dài 16 bit, nó cũng có thể chia làm 2 thanh ghi 8 bit là CH và CL Chương 3: Bộ xử lý trung tâm 22

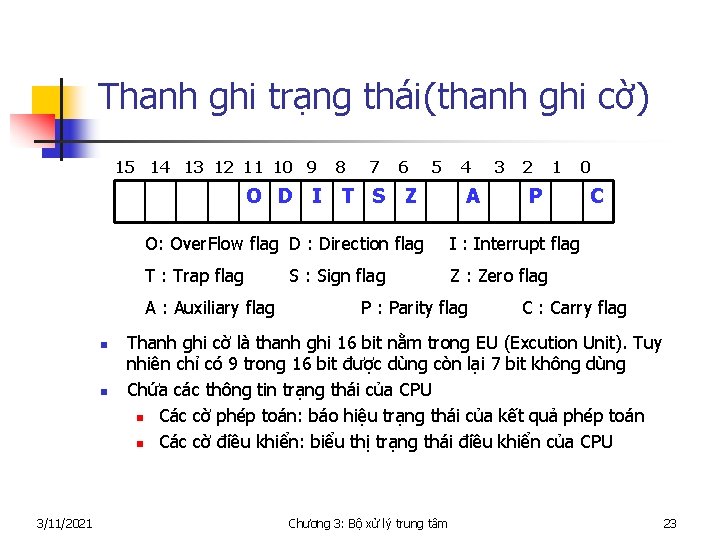

Thanh ghi trạng thái(thanh ghi cờ) 15 14 13 12 11 10 9 O D I n 3/11/2021 7 6 5 T S Z 4 A 3 2 1 P O: Over. Flow flag D : Direction flag I : Interrupt flag T : Trap flag Z : Zero flag A : Auxiliary flag n 8 S : Sign flag P : Parity flag 0 C C : Carry flag Thanh ghi cờ là thanh ghi 16 bit nằm trong EU (Excution Unit). Tuy nhiên chỉ có 9 trong 16 bit được dùng còn lại 7 bit không dùng Chứa các thông tin trạng thái của CPU n Các cờ phép toán: báo hiệu trạng thái của kết quả phép toán n Các cờ điều khiển: biểu thị trạng thái điều khiển của CPU Chương 3: Bộ xử lý trung tâm 23

Thanh ghi trạng thái(thanh ghi cờ) n n 3/11/2021 Cờ ZF: được thiết lập lên 1 khi kết quả của phép toán bằng 0. Cờ SF (cờ dấu): được thiết lập lên 1 khi kết quả phép toán nhỏ hơn 0 Cờ CF (cờ nhớ): được thiết lập lên 1 nếu phép toán có nhớ ra ngoài bit cao nhất cờ báo tràn với số không dấu. Cờ IF (Cờ cho phép ngắt): n Nếu IF = 1 CPU ở trạng thái cho phép ngắt với tín hiệu yêu cầu ngắt từ bên ngoài gửi tới n Nếu IF = 0 CPU ở trạng thái cấm ngắt với tín hiệu yêu cầu ngắt từ bên ngoài gửi tới Chương 3: Bộ xử lý trung tâm 24

Thanh ghi trạng thái(thanh ghi cờ) n n n 3/11/2021 Cờ OF (cờ tràn): OF=1 khi kết quả bị tràn số (vượt qua khả năng lưu trữ), OF=0 kết quả không bị tràn Cờ DF: xác định hướng theo chiều tăng/ giảm trong xử lý chuổi Cờ PF: PF=1 khi kết quả có số bit 1 là chẳn và ngược lại Cờ AF: Có nhớ trong phép cộng và có mượn trong phép trừ với 4 bit thấp sang 4 bit cao Cờ TF: báo cho CPU thi hành từng bước, cung cấp công cụ debug chương trình Chương 3: Bộ xử lý trung tâm 25

Các thanh ghi Segment n n n CPU có 4 thanh ghi segment dài 16 bit, các thanh ghi này không thể chia làm 2 thanh ghi 8 bit như 4 thanh ghi AX, BX, CX và DX. Các thanh ghi đoạn được sử dụng như là địa chỉ cơ sở của các lệnh trong chương trình, stack và dữ liệu. 4 thanh ghi đoạn : CS (Code Segment), DS (Data Segment), SS (Stack Segment) và ES (Extra Segment). n n 3/11/2021 CS : chứa địa chỉ bắt đầu của code trong chương trình DS : chứa địa chỉ của các biến khai báo trong chương trình SS : chứa địa chỉ của bộ nhớ Stack dùng trong chương trình ES : chứa địa chỉ cơ sở bổ sung cho các biến bộ nhớ Chương 3: Bộ xử lý trung tâm 26

Thanh ghi 32 bit § Đối với một số CPU đời mới, có các thanh ghi dài 32, 64 bit. Ta ghi thêm E đứng trước tên các thanh ghi 16 bit. . . EAX, EBX, ECX, EDX. . 3/11/2021 Chương 3: Bộ xử lý trung tâm 27

Thanh ghi đoạn và sự hình thành địa chỉ 8086 sử dụng 20 bit để đánh địa chỉ bộ nhớ quản lý trên 1 MB bộ nhớ. Nhưng 8086 lại không có thanh ghi nào 20 bit, tất cả là 16 bit do đó 1 thanh ghi chỉ có thể đánh địa chỉ tối đa là 64 KB bộ nhớ. Như vậy phải kết hợp 2 thanh ghi mới địa chỉ hoá toàn bộ bộ nhớ. 8086 sử 1 trong các thanh ghi dùng chung và 1 trong các thanh ghi đoạn (CS, DS, SS, ES) để tạo thành 1 địa chỉ 20 bit. Địa chỉ 20 bit của bộ nhớ 1 MB không thể chứa đủ trong các thanh ghi 16 bit của CPU 8086 bộ nhớ 1 MB được chia ra thành các đoạn (segment) 64 KB. Địa chỉ trong các đọan 64 KB chỉ có 16 bit nên CPU 8086 dễ dàng xử lý bằng các thanh ghi của nó. PH N ĐOẠN BỘ NHỚ : là cách dùng các thanh ghi 16 bit để biểu diễn cho địa chỉ 20 bit. 3/11/2021 Chương 3: Bộ xử lý trung tâm 28

Địa chỉ vật lý & địa chỉ luận lý n n n 3/11/2021 Địa chỉ 20 bits được gọi là địa chỉ vật lý. Địa chỉ vật lý dùng trong thiết kế các mạch giải mã địa chỉ cho bộ nhớ và xuất nhập. Còn trong lập trình , địa chỉ vật lý không thể dùng được mà nó được thay thế bằng địa chỉ luận lý (logic). Chương 3: Bộ xử lý trung tâm 29

Địa chỉ luận lý n n n 3/11/2021 Địa chỉ của 1 ô nhớ được xác định bởi 2 phần: Segment : offset n Segment: địa chỉ đoạn n Offset: địa chỉ trong đoạn (độ dời) Mỗi địa chỉ thành phần là 1 số 16 bit và được viết theo cách sau : Segment : offset VD : B 001: 1235 Chương 3: Bộ xử lý trung tâm 30

Sự hình thành địa chỉ n n 3/11/2021 Hãng Intel đề xuất 1 phương pháp để hình thành địa chỉ Mỗi địa chỉ ô nhớ được hình thành từ 1 phép tính tổng 1 địa chỉ cơ sở và 1 địa chỉ offset Địa chỉ cơ sở lưu trong 1 thanh ghi segment, còn địa chỉ offset nằm trong 1 thanh ghi chỉ số hay thanh ghi con trỏ Phép cộng này sẽ tạo 1 địa chỉ 20 bit gọi là địa chỉ vật lý Chương 3: Bộ xử lý trung tâm 31

Cách tính địa chỉ vật lý từ địa chỉ luận lý n n 3/11/2021 Địa chỉ vật lý = (segment*10 h) + offset VD : tính địa chỉ vật lý tương ứng địa chỉ luận lý B 001: 1235 n Địa chỉ vật lý = B 0010 h + 1235 h = B 1245 h Chương 3: Bộ xử lý trung tâm 32

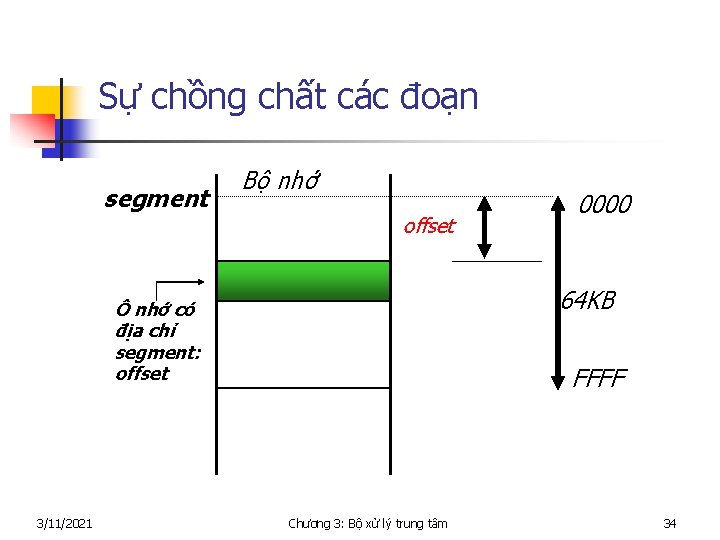

Sự chồng chất các đoạn n n Địa chỉ segment hay còn gọi là địa chỉ nền của đoạn. Nó cho biết điểm bắt đầu của đoạn trong bộ nhớ. Địa chỉ offset thể hiện khoảng cách kể từ đầu đọan của ô nhớ cần tham khảo. Do offset dài 16 bit nên chiều dài tối đa của mỗi đọan là 64 K. Mỗi ô nhớ chỉ có địa chỉ vật lý nhưng có thể có nhiều địa chỉ luận lý. VD : 1234 1334: 0234 1304: 0534 Đều có chung địa chỉ vật lý 13574 ? ? 3/11/2021 Chương 3: Bộ xử lý trung tâm 33

Sự chồng chất các đoạn segment Bộ nhớ offset 64 KB Ô nhớ có địa chỉ segment: offset 3/11/2021 0000 FFFF Chương 3: Bộ xử lý trung tâm 34

Sự chồng chất các đoạn n 3/11/2021 Khi offset tăng 1 đơn vị thì địa chỉ vật lý tăng 1 địa chỉ hoặc là tăng 1 byte. Như vậy có thể xem đơn vị của offset là byte Khi giữ nguyên phần offset chỉ tăng phần segment. Khi segment tăng 1 đơn vị thì địa chỉ vật lý tăng 10 h địa chỉ hoặc là tăng 16 bytes VD : ô nhớ có địa chỉ 0002 Ah sẽ có địa chỉ logic trong segment 0000 là 0000: 002 A n Trong segment 0001 là 0001: 001 A n Trong segment 0002 là 0002: 000 A Chương 3: Bộ xử lý trung tâm 35

Sự chồng chất các đoạn n n 3/11/2021 Nếu vùng bộ nhớ nào càng có nhiều segment chồng chập lên nhau thì các ô nhớ trong đó càng có nhiều địa chỉ luận lý. Một ô nhớ có ít nhất 1 địa chỉ luận lý và nhiều nhất là 65536/16 = 4096 địa chỉ luận lý Chương 3: Bộ xử lý trung tâm 36

3. 2. Tập lệnh n 3/11/2021 Giới thiệu chung về tập lệnh n Mỗi bộ xử lý có một tập lệnh xác định n Tập lệnh thường có hàng chục đến hàng trăm lệnh n Mỗi lệnh là một chuỗi số nhị phân mà bộ xử lý hiểu được để thực hiện một thao tác xác định n Các lệnh được mô tả bằng các ký hiệu gợi nhớ chính là các lệnh của hợp ngữ Chương 3: Bộ xử lý trung tâm 37

Các thành phần của lệnh máy Mã thao tác n n 3/11/2021 Địa chỉ của các toán hạng Mã thao tác (operation code opcode): mã hóa cho thao tác mà bộ xử lý phải thực hiện Địa chỉ toán hạng: chỉ ra nơi chứa các toán hạng mà thao tác sẽ tác động n Toán hạng nguồn: dữ liệu vào của thao tác n Toán hạng đích: dữ liệu ra của thao tác Chương 3: Bộ xử lý trung tâm 38

Số lượng địa chỉ toán hạng trong lệnh n n 3/11/2021 Ba địa chỉ toán hạng: n 2 toán hạng nguồn, 1 toán hạng đích n c = a + b n Từ lệnh dài vì phải mã hoá địa chỉ cho cả ba toán hạng n Được sử dụng trên các bộ xử lý tiên tiến Hai địa chỉ toán hạng: n Một toán hạng vừa là toán hạng nguồn vừa là toán hạng đích; toán hạng còn lại là toán hạng nguồn n a = a + b n Giá trị cũ của 1 toán hạng nguồn bị mất vì phải chứa kết quả n Rút gọn độ dài từ lệnh n Phổ biến Chương 3: Bộ xử lý trung tâm 39

Số lượng địa chỉ toán hạng trong lệnh n n 3/11/2021 Một địa chỉ toán hạng: n Một toán hạng được chỉ ra trong lệnh n Một toán hạng là ngầm định thường là thanh ghi (thanh chứa –accumulator) n Được sử dụng trên các máy ở các thế hệ trước 0 địa chỉ toán hạng: n Các toán hạng đều được ngầm định. Sử dụng Stack. Ví dụ n push a n push b n add n pop c n có nghĩa là : c = a+b. không thông dụng Chương 3: Bộ xử lý trung tâm 40

Đánh giá về số địa chỉ toán hạng n n 3/11/2021 Nhiều địa chỉ toán hạng n Các lệnh phức tạp hơn n Cần nhiều thanh ghi n Chương trình có ít lệnh hơn n Nhận lệnh và thực hiện lệnh chậm hơn Ít địa chỉ toán hạng n Các lệnh đơn giản hơn n Cần ít thanh ghi n Chương trình có nhiều lệnh hơn n Nhận lệnh và thực hiện lệnh nhanh hơn Chương 3: Bộ xử lý trung tâm 41

Các lệnh chuyển dữ liệu n n n n 3/11/2021 MOVE Copy dữ liệu từ nguồn đến đích LOAD Nạp dữ liệu từ bộ nhớ đến bộ xử lý STORE Cất dữ liệu từ bộ xử lý đến bộ nhớ EXCHANGE Trao đổi nội dung của nguồn và đích CLEAR Chuyển các bit 0 vào toán hạng đích SET Chuyển các bit 1 vào toán hạng đích PUSH Cất nội dung toán hạng nguồn vào ngăn xếp POP Lấy nội dung đỉnh ngăn xếp đưa đến toán hạng đích Chương 3: Bộ xử lý trung tâm 42

Các lệnh số học n n n n n 3/11/2021 ADD Cộng hai toán hạng SUBTRACT Trừ hai toán hạng MULTIPLY Nhân hai toán hạng DIVIDE Chia hai toán hạng ABSOLUTE Lấy trị tuyệt đối toán hạng NEGATE Đổi dấu toán hạng (lấy bù 2) INCREMENT Tăng toán hạng thêm 1 DECREMENT Giảm toán hạng đi 1 COMPARE Trừ hai toán hạng để lập cờ Chương 3: Bộ xử lý trung tâm 43

Các lệnh logic n n n n 3/11/2021 AND Thực hiện phép AND hai toán hạng OR Thực hiện phép OR hai toán hạng XOR Thực hiện phép XOR hai toán hạng NOT Đảo bit của toán hạng (lấy bù 1) TEST Thực hiện phép AND hai toán hạng để lập cờ SHIFT Dịch trái (phải) toán hạng ROTATE Quay trái (phải) toán hạng Chương 3: Bộ xử lý trung tâm 44

Các lệnh vào ra chuyên dụng n n 3/11/2021 INPUT Copy dữ liệu từ một cổng xác định đưa đến đích OUTPUT Copy dữ liệu từ nguồn đến một cổng xác định Chương 3: Bộ xử lý trung tâm 45

Các lệnh chuyển điều khiển n n 3/11/2021 JUMP (BRANCH) Lệnh nhảy không điều kiện: n nạp vào PC một địa chỉ xác định JUMP CONDITIONAL Lệnh nhảy có điều kiện: n điều kiện đúng nạp vào PC một địa chỉ xác định n điều kiện sai không làm gì cả CALL Lệnh gọi chương trình con: n Cất nội dung của PC (địa chỉ trở về) ra một vị trí xác định (thường ở Stack) n Nạp vào PC địa chỉ của lệnh đầu tiên của chương trình con RETURN Lệnh trở về từ chương trình con: n Khôi phục địa chỉ trở về trả lại cho PC để trở về chương trình chính Chương 3: Bộ xử lý trung tâm 46

Các lệnh điều khiển hệ thống n n n 3/11/2021 HALT Dừng thực hiện chương trình WAIT Tạm dừng thực hiện chương trình, lặp kiểm tra điều kiện cho đến khi thoả mãn thì tiếp tục thực hiện NO OPERATION Không thực hiện gì cả LOCK Cấm không cho xin chuyển nhượng bus UNLOCK Cho phép xin chuyển nhượng bus Chương 3: Bộ xử lý trung tâm 47

3. 3. Hoạt động của CPU n 3/11/2021 Chu trình lệnh n Nhận lệnh n Giải mã lệnh n Nhận toán hạng n Thực hiện lệnh n Cất toán hạng n Ngắt Chương 3: Bộ xử lý trung tâm 48

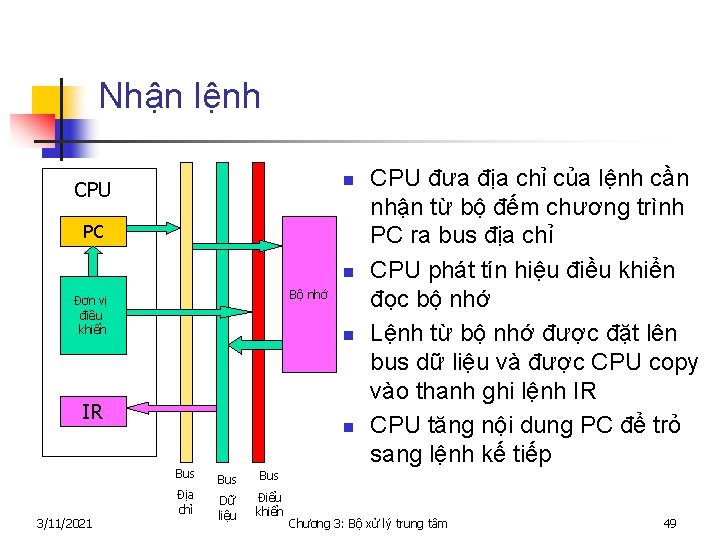

Nhận lệnh n CPU PC n Bộ nhớ Đơn vị điều khiển n IR 3/11/2021 n Bus Bus Địa chỉ Dữ liệu Điểu khiển CPU đưa địa chỉ của lệnh cần nhận từ bộ đếm chương trình PC ra bus địa chỉ CPU phát tín hiệu điều khiển đọc bộ nhớ Lệnh từ bộ nhớ được đặt lên bus dữ liệu và được CPU copy vào thanh ghi lệnh IR CPU tăng nội dung PC để trỏ sang lệnh kế tiếp Chương 3: Bộ xử lý trung tâm 49

Giải mã lệnh n n n 3/11/2021 Lệnh từ thanh ghi lệnh IR được đưa đến đơn vị điều khiển Đơn vị điều khiển tiến hành giải mã lệnh để xác định thao tác phải thực hiện Giải mã lệnh xảy ra bên trong CPU Chương 3: Bộ xử lý trung tâm 50

Nhận dữ liệu n n 3/11/2021 CPU đưa địa chỉ của toán hạng ra bus địa chỉ CPU phát tín hiệu điều khiển đọc Toán hạng được đọc vào CPU Tương tự như nhận lệnh Chương 3: Bộ xử lý trung tâm 51

Nhận dữ liệu gián tiếp n n n 3/11/2021 CPU đưa địa chỉ ra bus địa chỉ CPU phát tín hiệu điều khiển đọc Nội dung ngăn nhớ được đọc vào CPU, đó chính là địa chỉ của toán hạng Địa chỉ này được CPU phát ra bus địa chỉ để tìm ra toán hạng CPU phát tín hiệu điều khiển đọc Toán hạng được đọc vào CPU Chương 3: Bộ xử lý trung tâm 52

Thực hiện lệnh n n 3/11/2021 Có nhiều dạng tuỳ thuộc vào lệnh Có thể là: n Đọc/Ghi bộ nhớ n Vào/Ra n Chuyển giữa các thanh ghi n Thao tác số học/logic n Chuyển điều khiển (rẽ nhánh) Chương 3: Bộ xử lý trung tâm 53

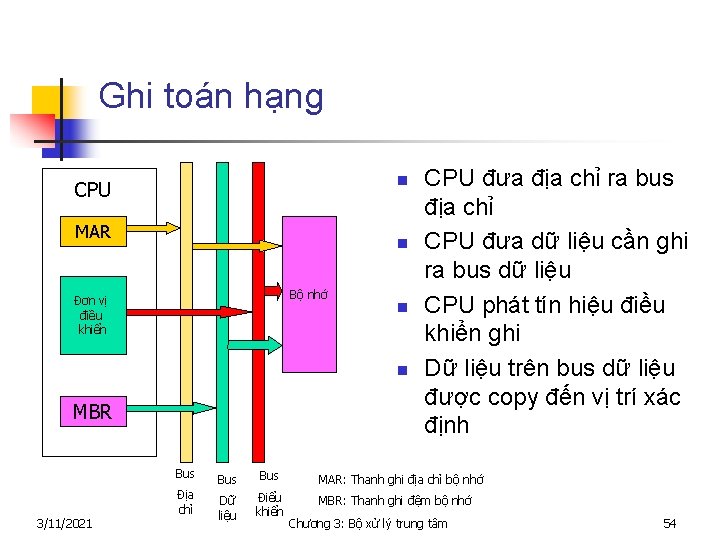

Ghi toán hạng n CPU MAR n Bộ nhớ Đơn vị điều khiển n n MBR 3/11/2021 Bus Bus Địa chỉ Dữ liệu Điểu khiển CPU đưa địa chỉ ra bus địa chỉ CPU đưa dữ liệu cần ghi ra bus dữ liệu CPU phát tín hiệu điều khiển ghi Dữ liệu trên bus dữ liệu được copy đến vị trí xác định MAR: Thanh ghi địa chỉ bộ nhớ MBR: Thanh ghi đệm bộ nhớ Chương 3: Bộ xử lý trung tâm 54

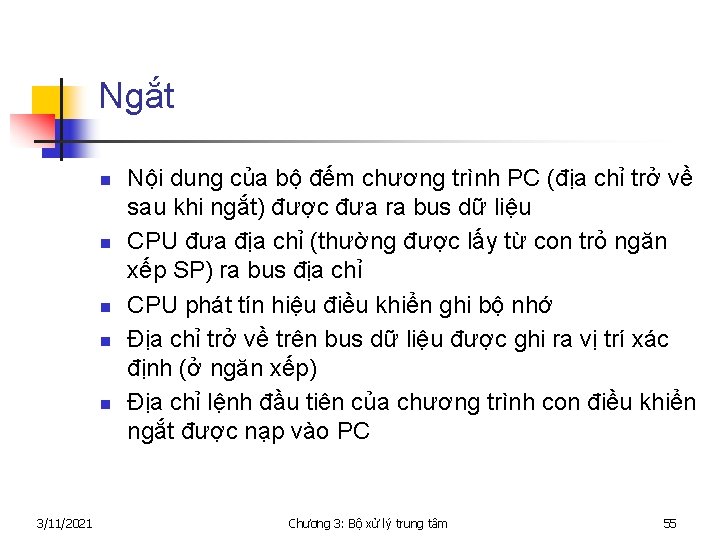

Ngắt n n n 3/11/2021 Nội dung của bộ đếm chương trình PC (địa chỉ trở về sau khi ngắt) được đưa ra bus dữ liệu CPU đưa địa chỉ (thường được lấy từ con trỏ ngăn xếp SP) ra bus địa chỉ CPU phát tín hiệu điều khiển ghi bộ nhớ Địa chỉ trở về trên bus dữ liệu được ghi ra vị trí xác định (ở ngăn xếp) Địa chỉ lệnh đầu tiên của chương trình con điều khiển ngắt được nạp vào PC Chương 3: Bộ xử lý trung tâm 55

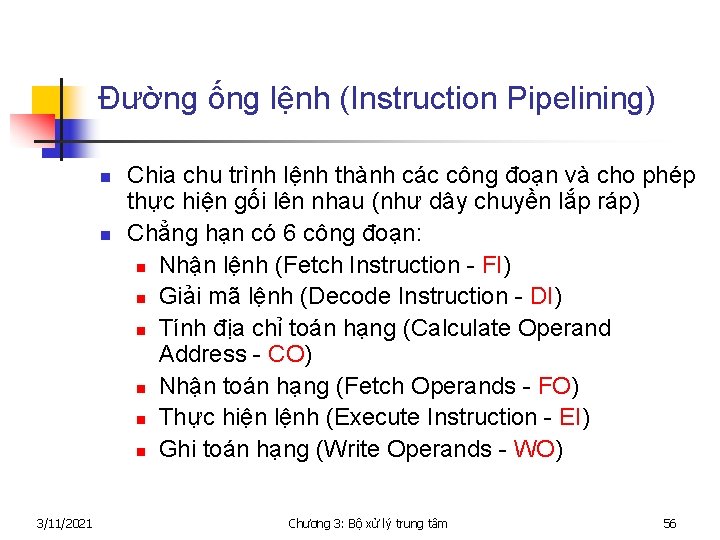

Đường ống lệnh (Instruction Pipelining) n n 3/11/2021 Chia chu trình lệnh thành các công đoạn và cho phép thực hiện gối lên nhau (như dây chuyền lắp ráp) Chẳng hạn có 6 công đoạn: n Nhận lệnh (Fetch Instruction - FI) n Giải mã lệnh (Decode Instruction - DI) n Tính địa chỉ toán hạng (Calculate Operand Address - CO) n Nhận toán hạng (Fetch Operands - FO) n Thực hiện lệnh (Execute Instruction - EI) n Ghi toán hạng (Write Operands - WO) Chương 3: Bộ xử lý trung tâm 56

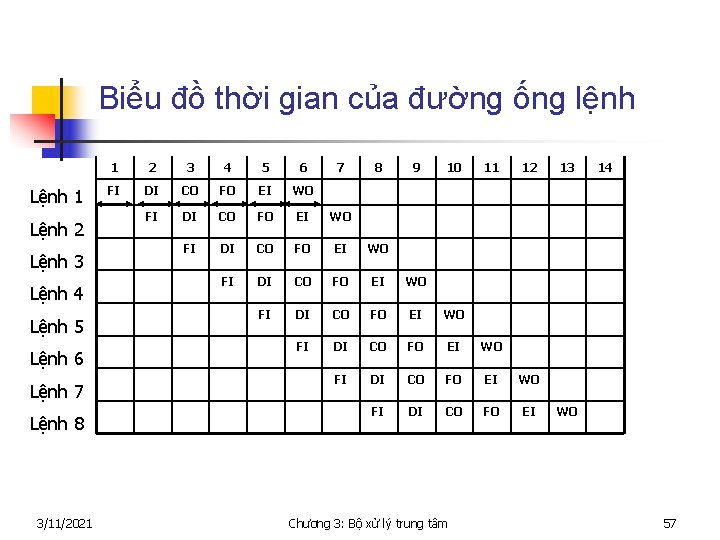

Biểu đồ thời gian của đường ống lệnh Lệnh 1 Lệnh 2 Lệnh 3 Lệnh 4 Lệnh 5 Lệnh 6 Lệnh 7 Lệnh 8 3/11/2021 1 2 3 4 5 6 7 8 9 10 FI DI CO FO EI WO FI DI CO FO EI WO FI DI CO FO EI Chương 3: Bộ xử lý trung tâm 11 12 13 14 WO 57

Các vấn đề của đường ống lệnh n n n 3/11/2021 Vấn đề cấu trúc: do nhiều công đoạn dùng chung một tài nguyên Vấn đề dữ liệu: lệnh sau sử dụng dữ liệu kết quả của lệnh trước Vấn đề điều khiển: do rẽ nhánh gây ra Chương 3: Bộ xử lý trung tâm 58

Các kiến trúc song mức lệnh n n n 3/11/2021 Siêu đường ống (Superpipeline & Hyperpipeline) Siêu vô hướng (Superscalar) VLIW (Very Long Instruction Word) Chương 3: Bộ xử lý trung tâm 59

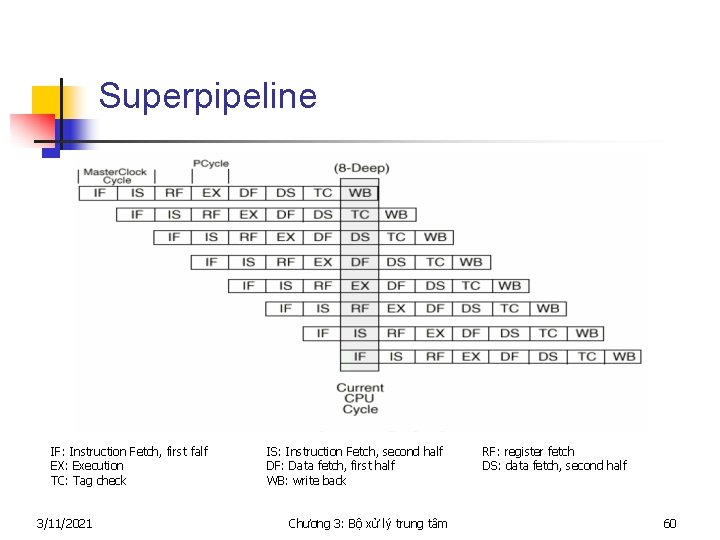

Superpipeline IF: Instruction Fetch, first falf EX: Execution TC: Tag check 3/11/2021 IS: Instruction Fetch, second half DF: Data fetch, first half WB: write back Chương 3: Bộ xử lý trung tâm RF: register fetch DS: data fetch, second half 60

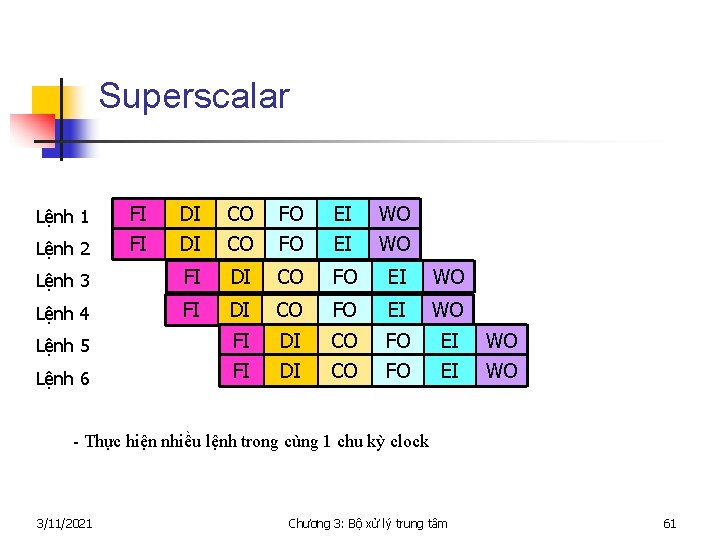

Superscalar DI DI CO CO FO FO EI EI WO WO Lệnh 3 FI DI CO FO EI WO Lệnh 4 FI DI CO FO EI WO FI FI DI DI CO CO FO FO EI EI Lệnh 1 Lệnh 2 Lệnh 5 Lệnh 6 FI FI WO WO - Thực hiện nhiều lệnh trong cùng 1 chu kỳ clock 3/11/2021 Chương 3: Bộ xử lý trung tâm 61

CISC và RISC CISC Complex Instruction Set Computer: § Máy tính với tập lệnh phức tạp § Các bộ xử lý truyền thống: x 86, 680 x 0 RISC Reduced Instruction Set Computer: § Máy tính với tập lệnh thu gọn § Sun. SPARC, Power PC, . . . § RISC đối nghịch với CISC 3/11/2021 Chương 3: Bộ xử lý trung tâm 62

Các đặc trưng của RISC n n n n n 3/11/2021 Số lượng lệnh ít Hầu hết các lệnh truy nhập toán hạng ở các thanh ghi Truy nhập bộ nhớ bằng các lệnh LOAD/STORE Thời gian thực hiện lệnh là một chu kỳ máy Các lệnh có độ dài cố định (32 bit) Số lượng khuôn dạng lệnh là ít (<=4) CPU có tập thanh ghi lớn Có ít mode địa chỉ (<=4) Hỗ trợ các thao tác của ngôn ngữ bậc cao Đều được thiết kế kiểu pipeline lệnh Chương 3: Bộ xử lý trung tâm 63

3. 5. Kiến trúc Intel n n n 3/11/2021 Kiến trúc 4 -bit: 4004 Kiến trúc 8 -bit: 8008, 8080, 8085 Kiến trúc 16 -bit: 8086/8088, 80186, 80286 Kiến trúc 32 -bit: 80386, 80486, Pentium II, Celeron, Pentium III, Pentium 4 Kiến trúc 64 -bit: Itanium Chương 3: Bộ xử lý trung tâm 64

Kiến trúc 16 -bit (IA-16) n n 3/11/2021 Các thanh ghi bên trong: 16 -bit Xử lý các phép toán số nguyên với 16 -bit Quản lý bộ nhớ theo đoạn 64 KBytes Mở đầu cho dòng máy tính IBM-PC Chương 3: Bộ xử lý trung tâm 65

Kiến trúc 32 -bit (IA-32) n n 3/11/2021 Các thanh ghi bên trong: 32 -bit Xử lý các phép toán số nguyên với 32 -bit Có ba chế độ làm việc: n Chế độ 8086 thực (Real 8086 mode): làm việc như một bộ xử lý 8086 n Chế độ 8086 ảo (Virtual 8086 mode): làm việc như nhiều bộ xử lý 8086 (đa nhiệm 16 -bit) n Chế độ bảo vệ (Protected mode) n đa nhiệm 32 -bit n quản lý bộ nhớ ảo Xử lý các phép toán số dấu phẩy động (từ 80486) Chương 3: Bộ xử lý trung tâm 66

Kiến trúc 64 -bit (IA-64) n n n 3/11/2021 Các thanh ghi bên trong: 64 -bit Xử lý các phép toán số nguyên với 64 -bit Xử lý các phép toán số dấu phẩy động Không tương thích phần cứng với các bộ xử lý trước đó Tương thích phần mềm bằng cách giả lập môi trường Chương 3: Bộ xử lý trung tâm 67

Hết chương 3 3/11/2021 Chương 3: Bộ xử lý trung tâm 68

- Slides: 68