CTPPS Motherboard 1 General Schema same for both

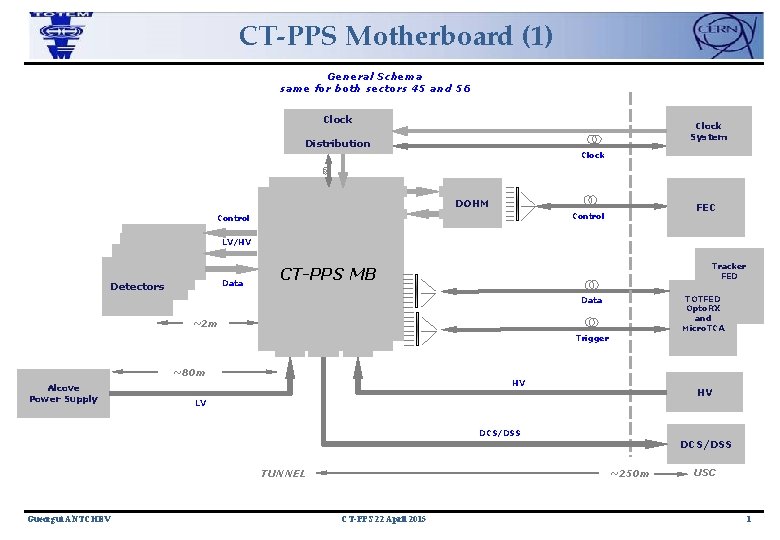

CT-PPS Motherboard (1) General Schema same for both sectors 45 and 56 Clock System Distribution Clock DOHM FEC Control LV/HV Detectors Data Detectors Tracker FED CT-PPS MB TOTFED Opto. RX and Micro. TCA Data ~2 m Trigger ~80 m Alcove Power Supply HV HV LV DCS/DSS TUNNEL Gueorgui ANTCHEV DCS/DSS ~250 m CT-PPS 22 April 2015 USC 1

CT-PPS Motherboard (2) Basic Blocks INPUT OUTPUT Connectors for Control Connector for HPTDCs Mezzanine CCUM Clock and Commands Distribution FPGA So. C M 2 S 150 -FCG 1152 MICROSEMI Connectors for SAMPIC Mezzanines + Flash EPROM POH Quick. USB Mezzanine Power Distribution Gueorgui ANTCHEV GOHs JTAG Port CT-PPS 22 April 2015 2

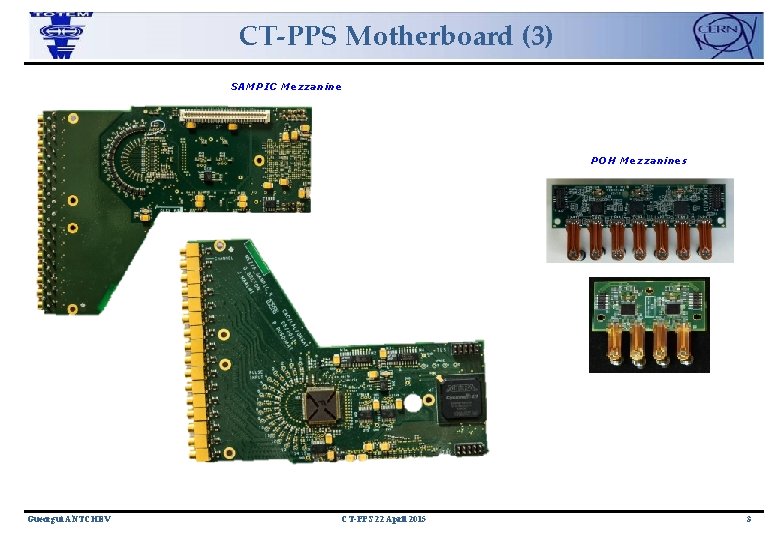

CT-PPS Motherboard (3) SAMPIC Mezzanine POH Mezzanines Gueorgui ANTCHEV CT-PPS 22 April 2015 3

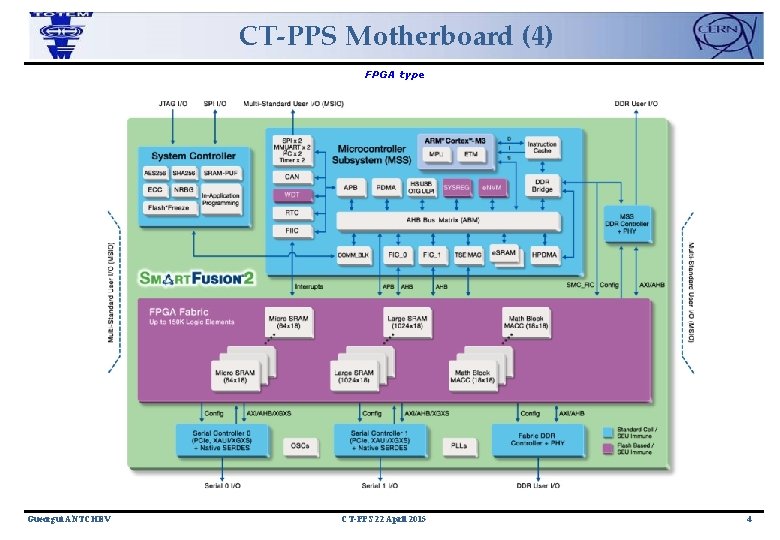

CT-PPS Motherboard (4) FPGA type Gueorgui ANTCHEV CT-PPS 22 April 2015 4

CT-PPS Motherboard (5) Schematic Gueorgui ANTCHEV CT-PPS 22 April 2015 5

CT-PPS Motherboard (6) Status 1 • To be defined • What to use CCU 25 chip or CCUM mezzanine • CCU 25 chip – no answer yet for availabilities • CCUM mezzanine – available • Using CCU 25 chip provide more functionalities (JTAG, etc. ) • POH transmitters - which to use, number of channels? • HPTDC mezzanine dimensions • SAMPIC mezzanine final version • Power distributions on board (for FPGA, detectors, etc. ) • DCS information (temp, vacuum, radmon, etc. ) ! Gueorgui ANTCHEV CT-PPS 22 April 2015 6

CT-PPS Motherboard (7) Status 2 • Schematic drawing is ongoing • Defining the connectivity to the front-end and outside electronics is ongoing • Components selection is ongoing • PCB layout time is reserved at CERN • Very preliminary plan • Components ordering now • SCH to be finished mid of May 2015 • PCB layout to start after SCH / FPGA verification beg of June 2015 Gueorgui ANTCHEV CT-PPS 22 April 2015 7

- Slides: 7