CSSE 132 Build ALU with Verilog Wednesday February

CSSE 132 Build ALU with Verilog Wednesday, February 24, 2021

Questions q. How to add more features to the ALU? ØOverflow detector (cont. ) ØZero detector q. How to program the gates -- Verilog?

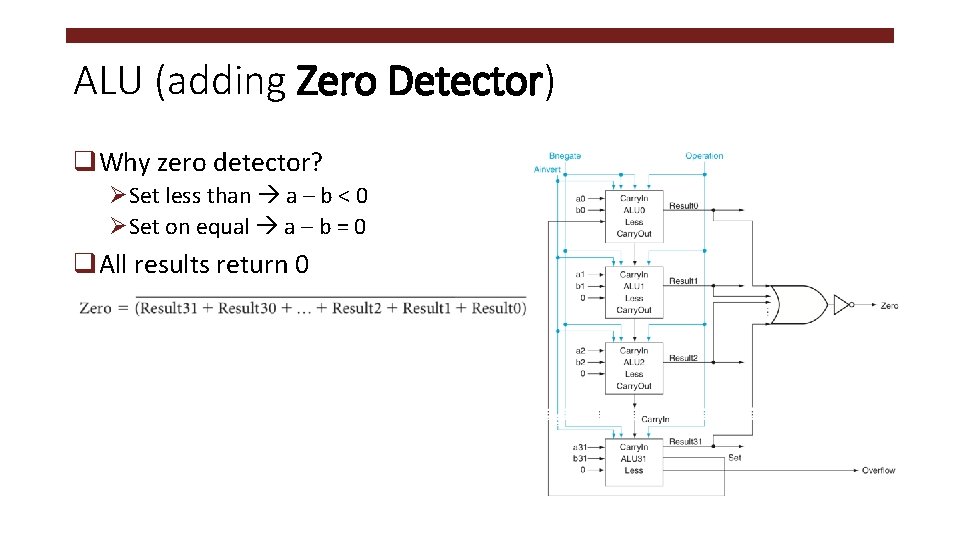

ALU (adding Zero Detector) q. Why zero detector? ØSet less than a – b < 0 ØSet on equal a – b = 0 q. All results return 0

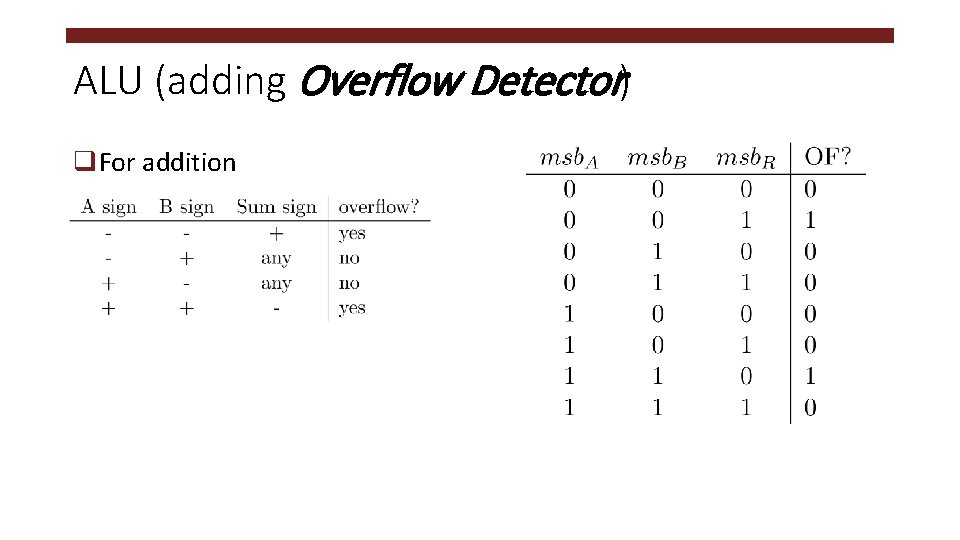

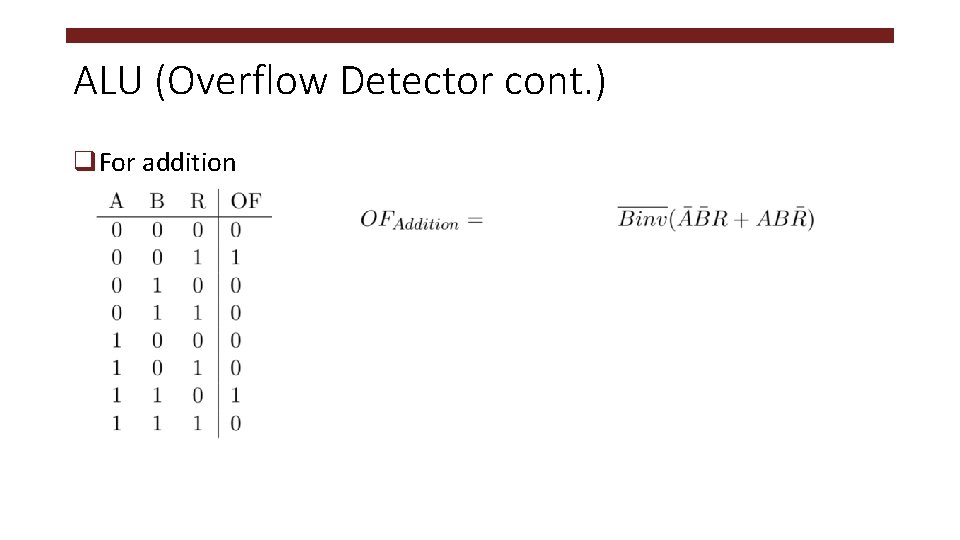

ALU (adding Overflow Detector) q. For addition

ALU (Overflow Detector cont. ) q. For addition

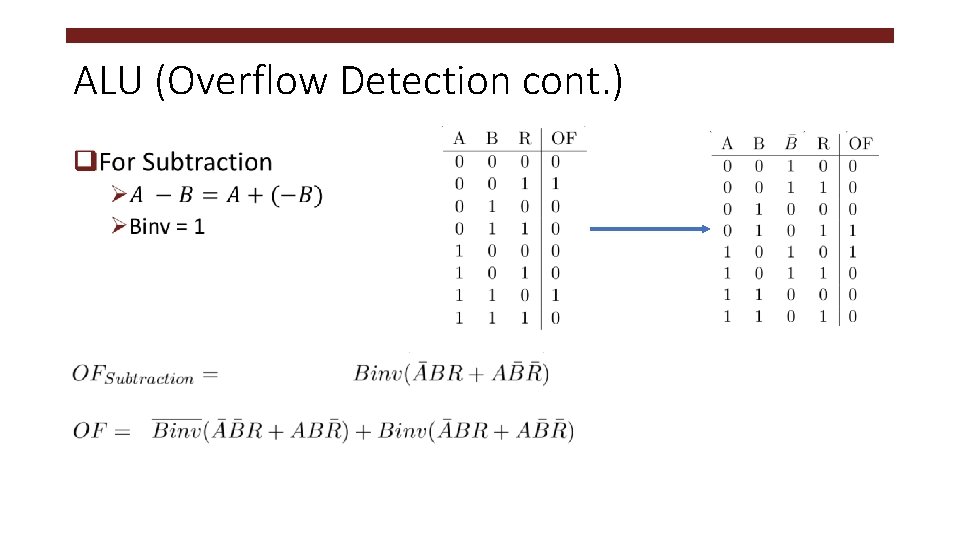

ALU (Overflow Detection cont. ) q

Introduce to Verilog q. Hardware Description Language q. Basically, it describes how to design circuits out of gates. q. All things in Verilog happen in parallel.

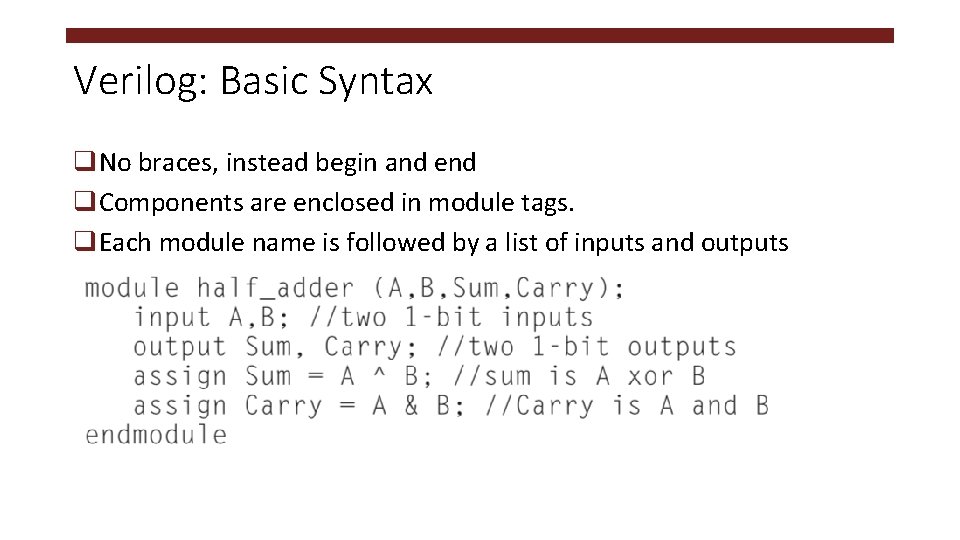

Verilog: Basic Syntax q. No braces, instead begin and end q. Components are enclosed in module tags. q. Each module name is followed by a list of inputs and outputs

Verilog: Variables q. Types Øwire : Just wires, used for combinational logic. Øreg : similar to registers: used for sequential (and sometimes combinational). q. Assignment Ø– Blocking assignment (=): execution pauses until this is done. Ø– Non-Blocking assignment (<=): happens in parallel to everything else. q. Busses: arrays of wires. Ø– Declare: wire [15: 0] blah; Ø– Assign: foo = 16’b 0010101111110101; Ø– Reference: foo = blah[15: 8];

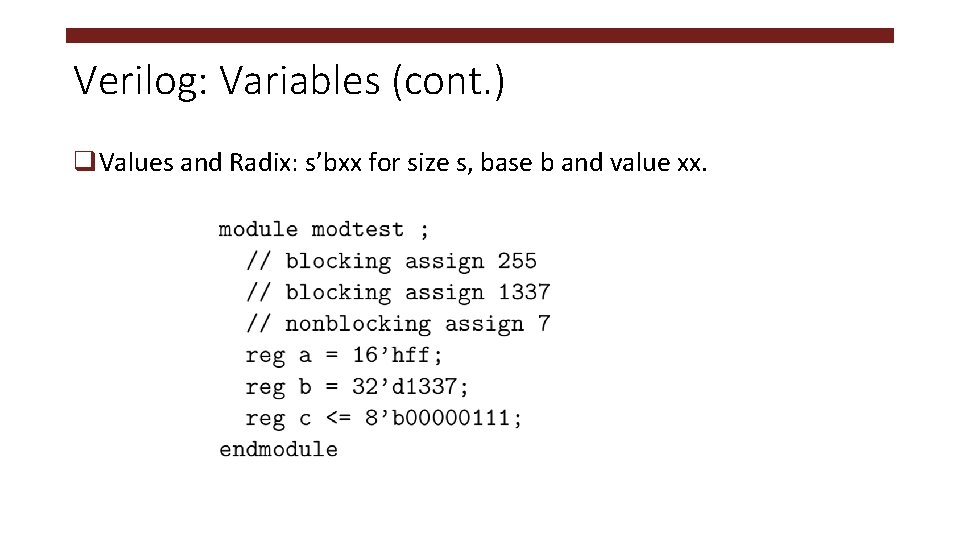

Verilog: Variables (cont. ) q. Values and Radix: s’bxx for size s, base b and value xx.

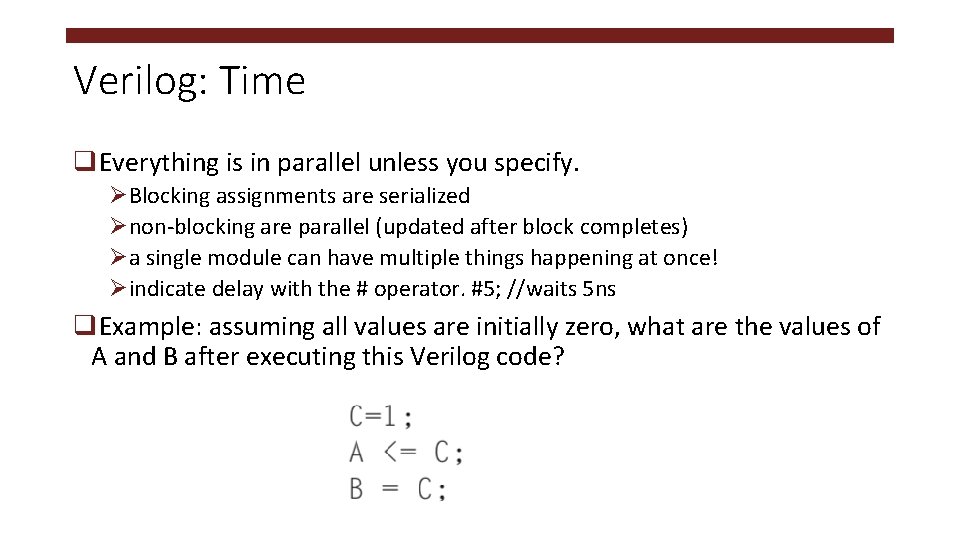

Verilog: Time q. Everything is in parallel unless you specify. ØBlocking assignments are serialized Ønon-blocking are parallel (updated after block completes) Øa single module can have multiple things happening at once! Øindicate delay with the # operator. #5; //waits 5 ns q. Example: assuming all values are initially zero, what are the values of A and B after executing this Verilog code?

Verilog: Execution Blocks qbegin and end. q. A block of things can run once, run repeatedly, or get re-run when something changes. ØOnce: initial begin ØRepeated: always begin ØTriggered (on either): always @(var)

Verilog: Abstract concepts q. These are extras for the simulator and are useful for writing test fixtures. Ø$write : like printf Ø$display : like printf with newline Ø$finish : halts the simulation

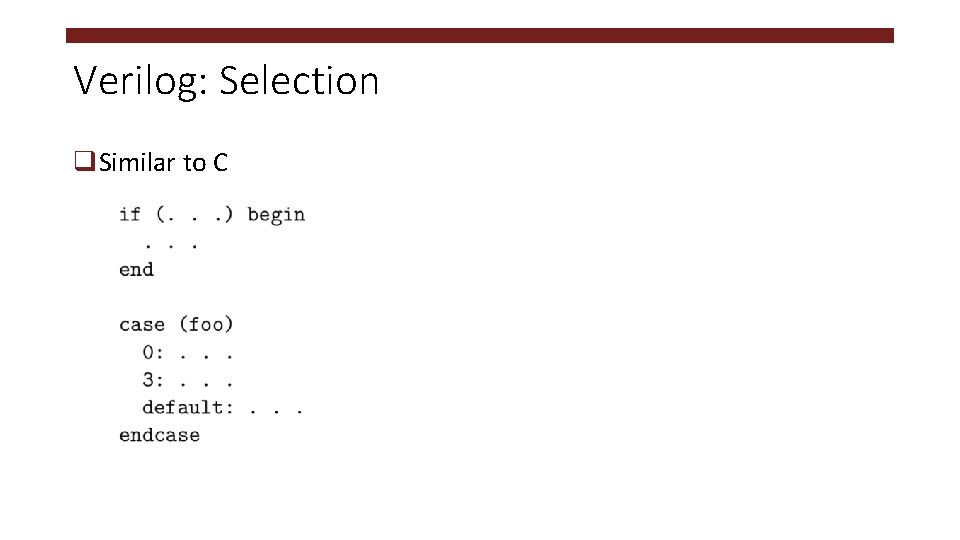

Verilog: Selection q. Similar to C

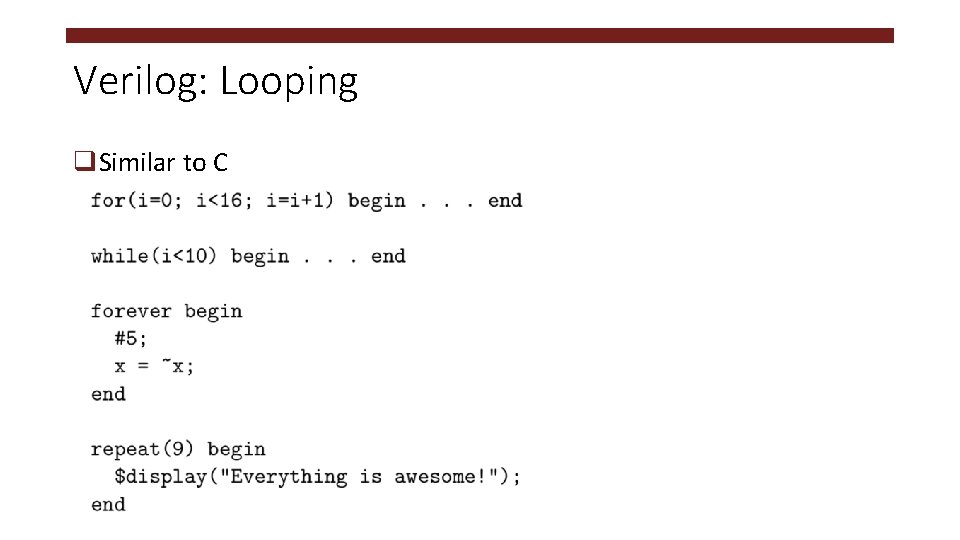

Verilog: Looping q. Similar to C

- Slides: 15