CSNSM SPIROC Silicon PM Readout ASIC Stphane Callier

- Slides: 30

CSNSM SPIROC : Silicon PM Readout ASIC Stéphane Callier, Frédéric Dulucq, Julien Fleury, Gisèle Martin-Chassard, Christophe de La Taille, Ludovic Raux IN 2 P 3/OMEGA-LAL Orsay 16 sep 08

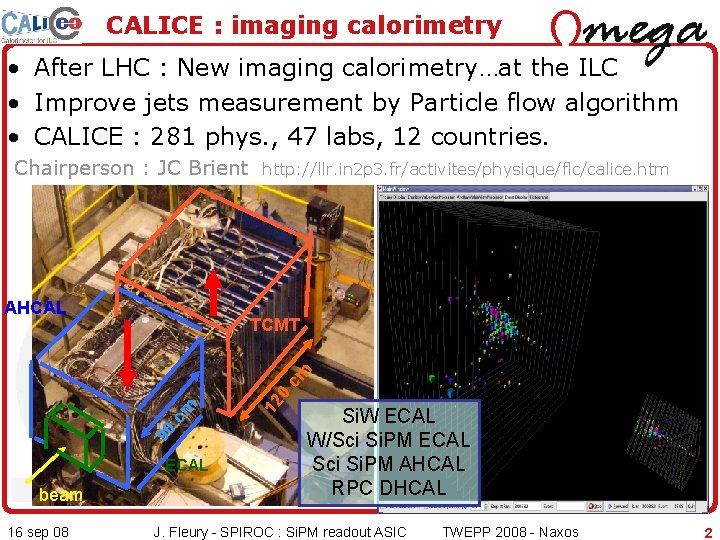

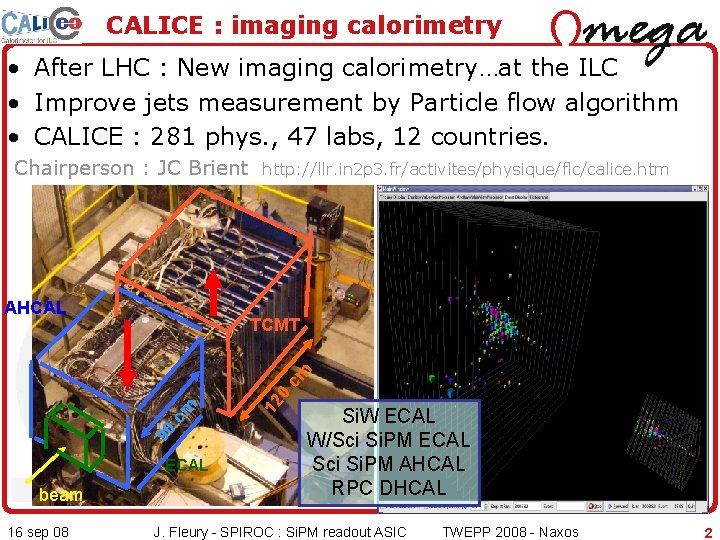

CALICE : imaging calorimetry • After LHC : New imaging calorimetry…at the ILC • Improve jets measurement by Particle flow algorithm • CALICE : 281 phys. , 47 labs, 12 countries. Chairperson : JC Brient http: //llr. in 2 p 3. fr/activites/physique/flc/calice. htm AHCAL 90 ECAL beam 16 sep 08 12 0 cm cm TCMT Si. W ECAL W/Sci Si. PM ECAL Sci Si. PM AHCAL RPC DHCAL J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 2

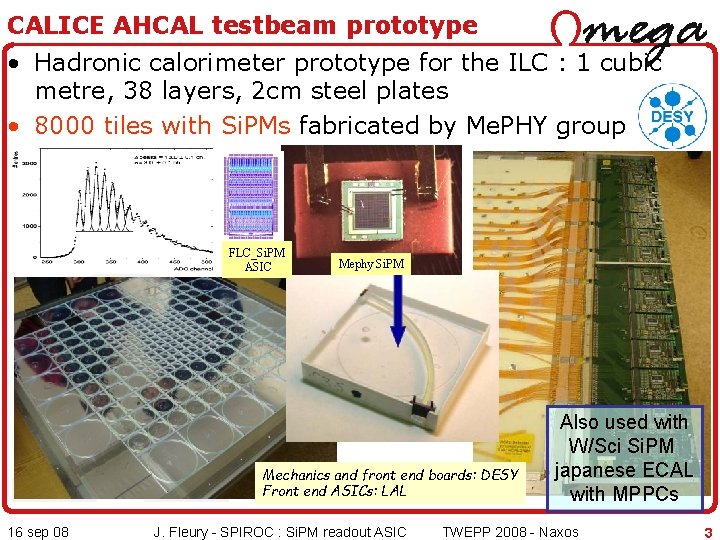

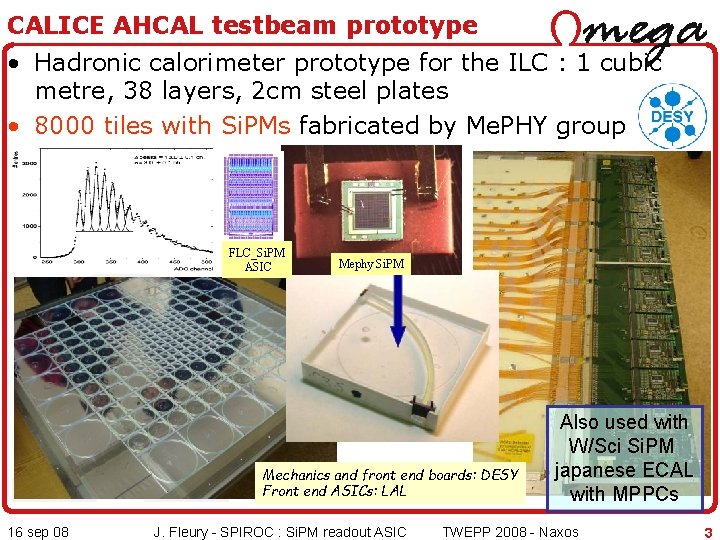

CALICE AHCAL testbeam prototype • Hadronic calorimeter prototype for the ILC : 1 cubic metre, 38 layers, 2 cm steel plates • 8000 tiles with Si. PMs fabricated by Me. PHY group FLC_Si. PM ASIC Mephy Si. PM Mechanics and front end boards: DESY Front end ASICs: LAL 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC Also used with W/Sci Si. PM japanese ECAL with MPPCs TWEPP 2008 - Naxos 3

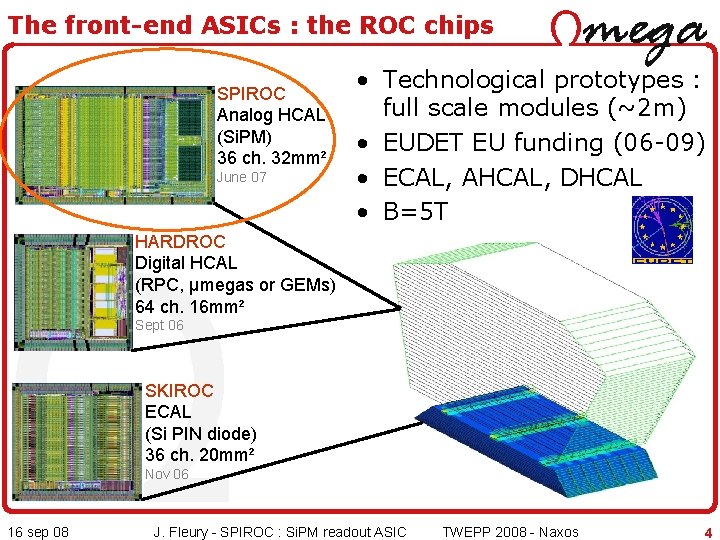

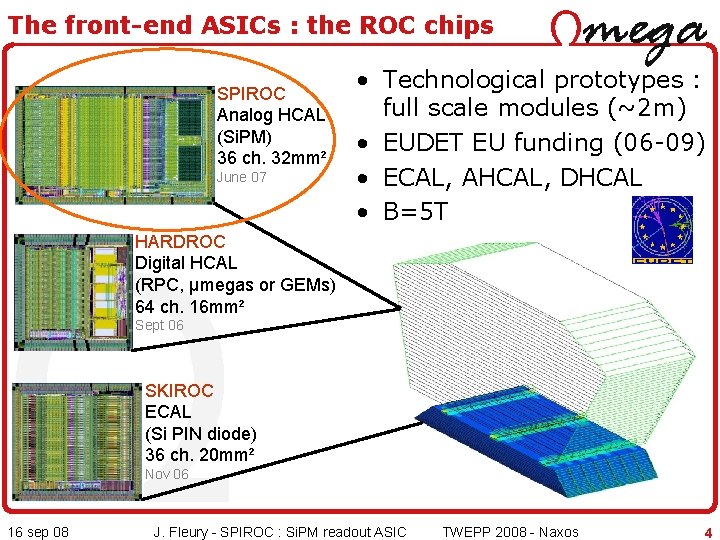

The front-end ASICs : the ROC chips SPIROC Analog HCAL (Si. PM) 36 ch. 32 mm² June 07 • Technological prototypes : full scale modules (~2 m) • EUDET EU funding (06 -09) • ECAL, AHCAL, DHCAL • B=5 T HARDROC Digital HCAL (RPC, µmegas or GEMs) 64 ch. 16 mm² Sept 06 SKIROC ECAL (Si PIN diode) 36 ch. 20 mm² Nov 06 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 4

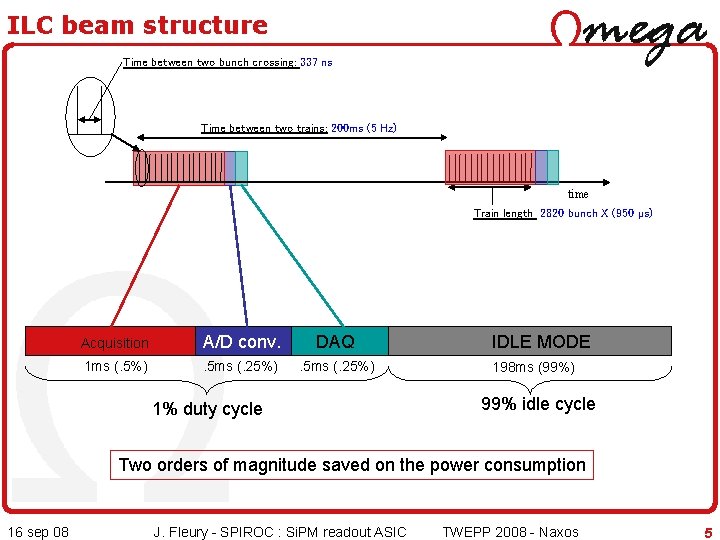

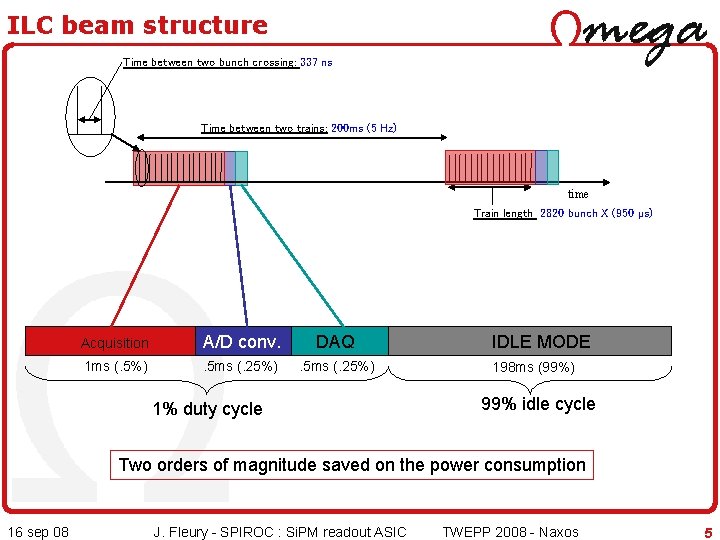

ILC beam structure Time between two bunch crossing: 337 ns Time between two trains: 200 ms (5 Hz) time Train length 2820 bunch X (950 µs) Acquisition A/D conv. DAQ 1 ms (. 5%) . 5 ms (. 25%) 1% duty cycle IDLE MODE 198 ms (99%) 99% idle cycle Two orders of magnitude saved on the power consumption 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 5

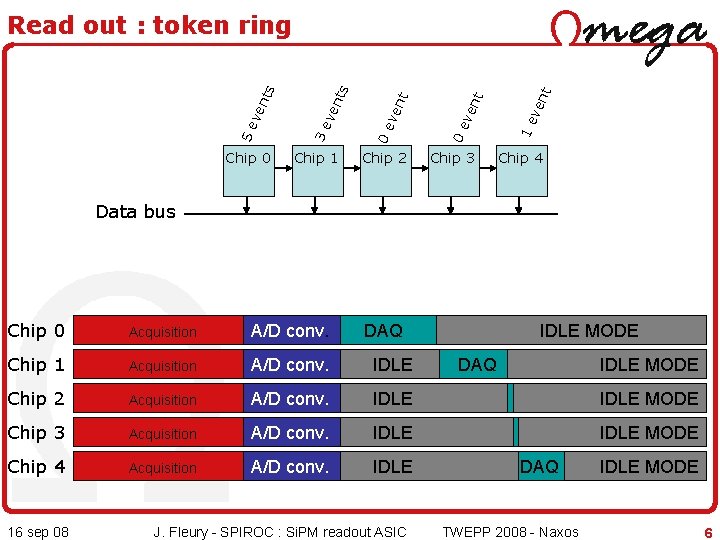

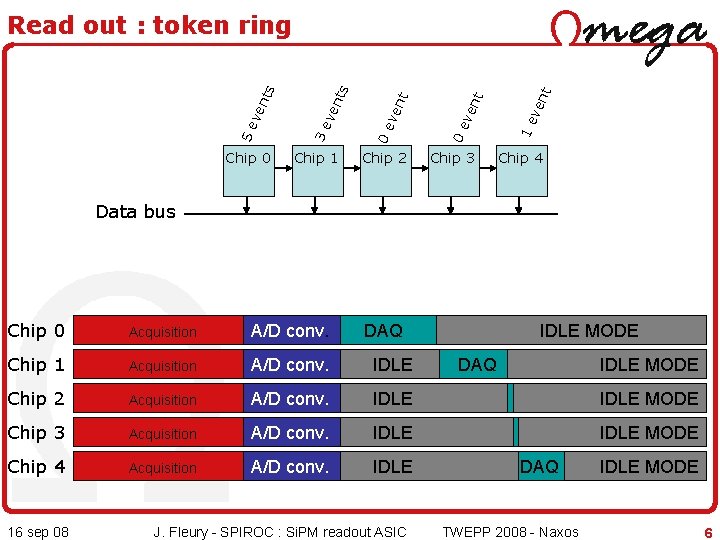

Chip 0 Chip 1 Chip 2 Chip 3 ve nt 1 e ve nt 0 e ve nts 3 e 5 e ve nts Read out : token ring Chip 4 Data bus Chip 0 Acquisition A/D conv. Chip 1 Acquisition A/D conv. IDLE Chip 2 Acquisition A/D conv. IDLE MODE Chip 3 Acquisition A/D conv. IDLE MODE Chip 4 Acquisition A/D conv. IDLE 16 sep 08 DAQ J. Fleury - SPIROC : Si. PM readout ASIC IDLE MODE DAQ TWEPP 2008 - Naxos IDLE MODE 6

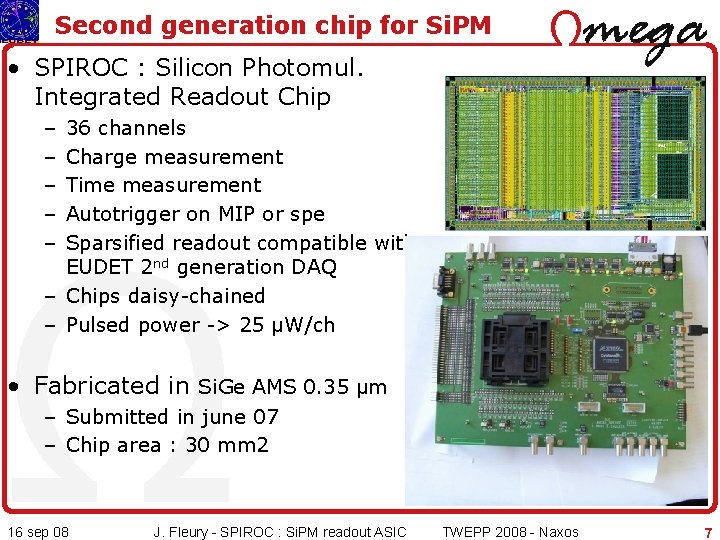

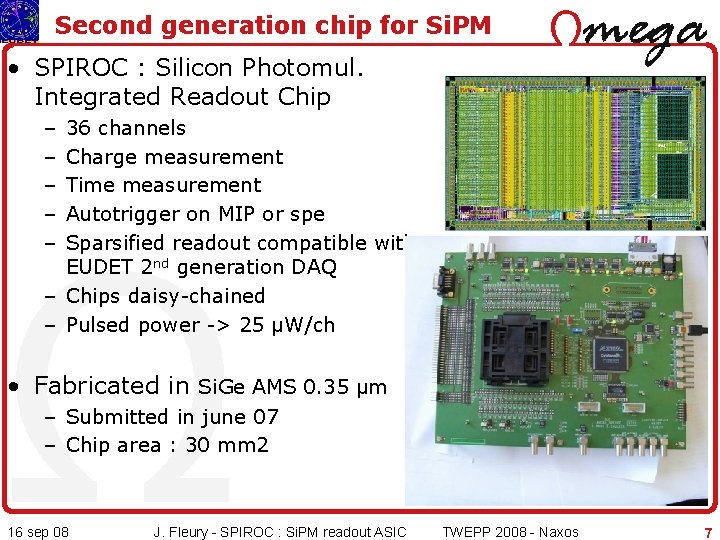

Second generation chip for Si. PM • SPIROC : Silicon Photomul. Integrated Readout Chip – – – 36 channels Charge measurement Time measurement Autotrigger on MIP or spe Sparsified readout compatible with EUDET 2 nd generation DAQ – Chips daisy-chained – Pulsed power -> 25 µW/ch • Fabricated in Si. Ge AMS 0. 35 µm – Submitted in june 07 – Chip area : 30 mm 2 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 7

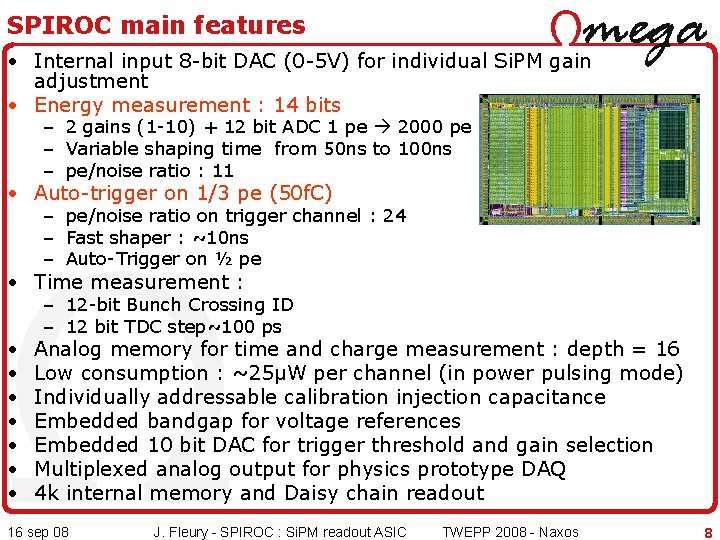

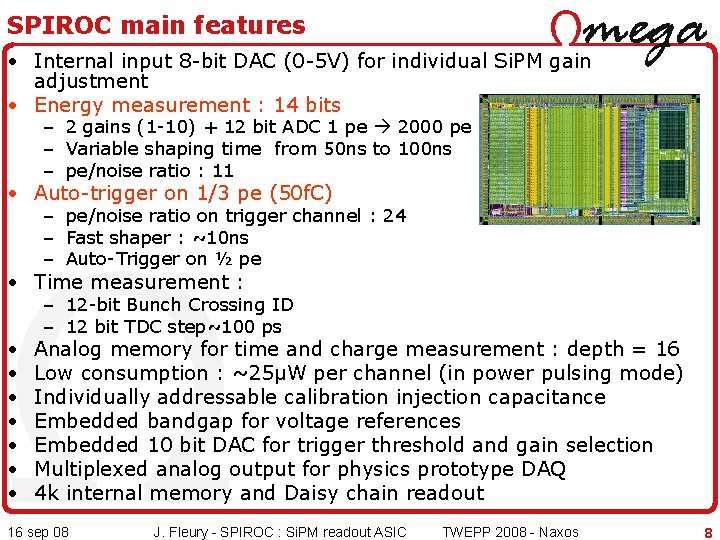

SPIROC main features • Internal input 8 -bit DAC (0 -5 V) for individual Si. PM gain adjustment • Energy measurement : 14 bits – 2 gains (1 -10) + 12 bit ADC 1 pe 2000 pe – Variable shaping time from 50 ns to 100 ns – pe/noise ratio : 11 • Auto-trigger on 1/3 pe (50 f. C) – pe/noise ratio on trigger channel : 24 – Fast shaper : ~10 ns – Auto-Trigger on ½ pe • Time measurement : • • – 12 -bit Bunch Crossing ID – 12 bit TDC step~100 ps Analog memory for time and charge measurement : depth = 16 Low consumption : ~25µW per channel (in power pulsing mode) Individually addressable calibration injection capacitance Embedded bandgap for voltage references Embedded 10 bit DAC for trigger threshold and gain selection Multiplexed analog output for physics prototype DAQ 4 k internal memory and Daisy chain readout 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 8

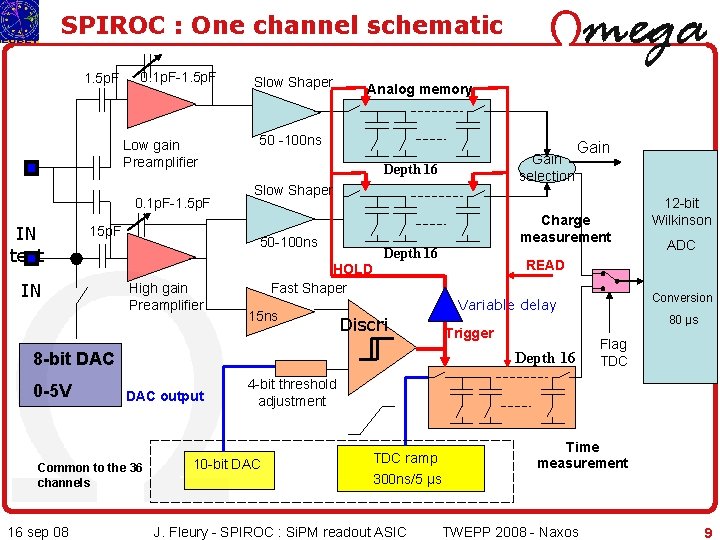

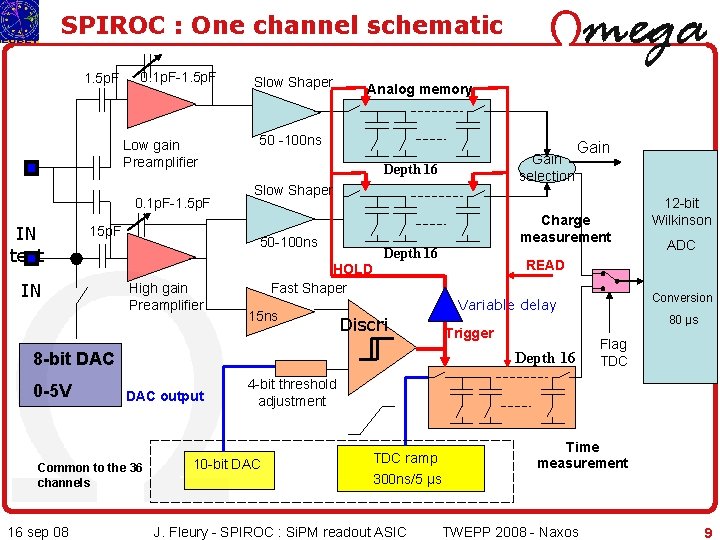

SPIROC : One channel schematic 1. 5 p. F 0. 1 p. F-1. 5 p. F Low gain Preamplifier 0. 1 p. F-1. 5 p. F IN test 15 p. F IN Slow Shaper Analog memory 50 -100 ns Depth 16 Slow Shaper Depth 16 Discri Trigger Depth 16 DAC output Common to the 36 channels 16 sep 08 ADC Conversion Variable delay 8 -bit DAC 0 -5 V 12 -bit Wilkinson READ HOLD Fast Shaper 15 ns Gain Charge measurement 50 -100 ns High gain Preamplifier Gain selection 80 µs Flag TDC 4 -bit threshold adjustment 10 -bit DAC TDC ramp 300 ns/5 µs J. Fleury - SPIROC : Si. PM readout ASIC Time measurement TWEPP 2008 - Naxos 9

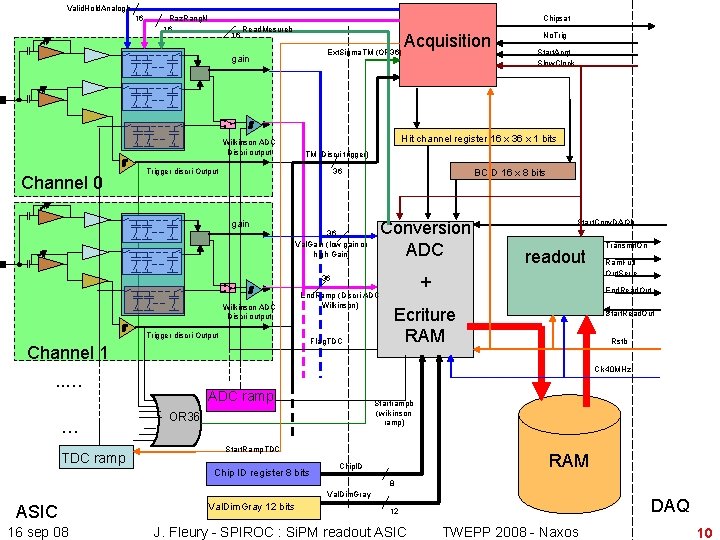

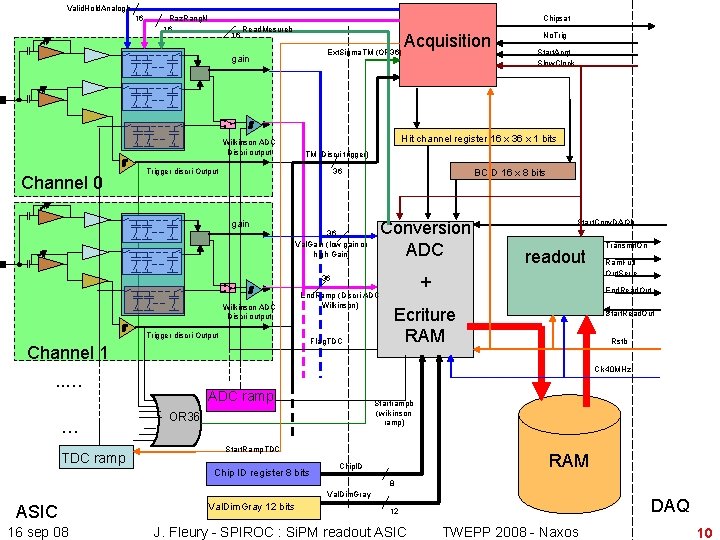

Valid. Hold. Analogb SPIROC general block scheme 16 Raz. Rang. N 16 16 Read. Mesureb Acquisition Ext. Sigma. TM (OR 36) gain Wilkinson ADC Discri output Channel 0 36 Val. Gain (low gain or high Gain) BCID 16 x 8 bits Conversion ADC End. Ramp (Discri ADC Wilkinson) Trigger discri Output Flag. TDC Channel 1 Start. Conv. DAQb readout + 36 Transmit. On Ram. Full Out. Serie End. Read. Out Ecriture RAM Start. Read. Out Rstb Clk 40 MHz . . … TDC ramp Start. Acqt Slow. Clock TM (Discri trigger) 36 Wilkinson ADC Discri output No. Trig Hit channel register 16 x 36 x 1 bits Trigger discri Output gain … Chipsat ADC ramp Startrampb (wilkinson ramp) OR 36 Start. Ramp. TDC Chip ID register 8 bits RAM Chip. ID 8 Val. Dim. Gray ASIC 16 sep 08 Val. Dim. Gray 12 bits DAQ 12 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 10

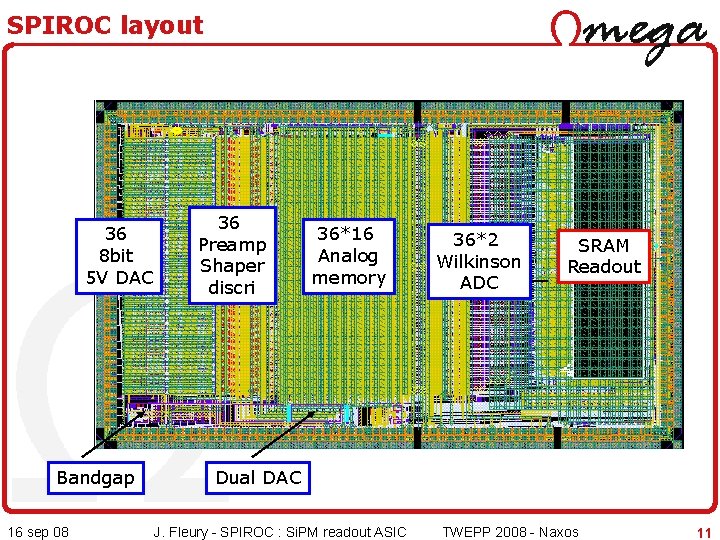

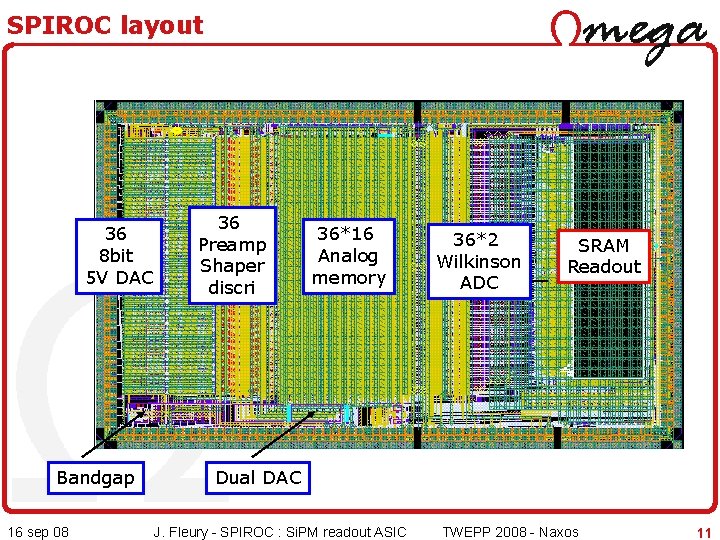

SPIROC layout 36 8 bit 5 V DAC Bandgap 16 sep 08 36 Preamp Shaper discri 36*16 Analog memory 36*2 Wilkinson ADC SRAM Readout Dual DAC J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 11

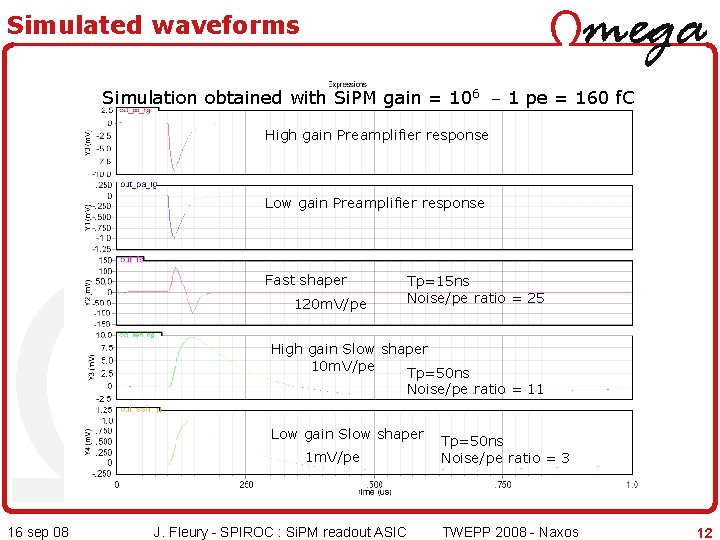

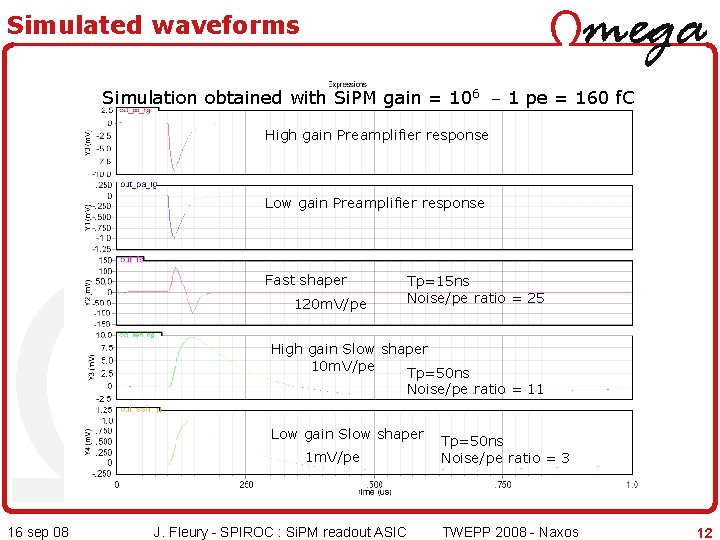

Simulated waveforms Simulation obtained with Si. PM gain = 106 _ 1 pe = 160 f. C High gain Preamplifier response Low gain Preamplifier response Fast shaper 120 m. V/pe Tp=15 ns Noise/pe ratio = 25 High gain Slow shaper 10 m. V/pe Tp=50 ns Noise/pe ratio = 11 Low gain Slow shaper 1 m. V/pe 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC Tp=50 ns Noise/pe ratio = 3 TWEPP 2008 - Naxos 12

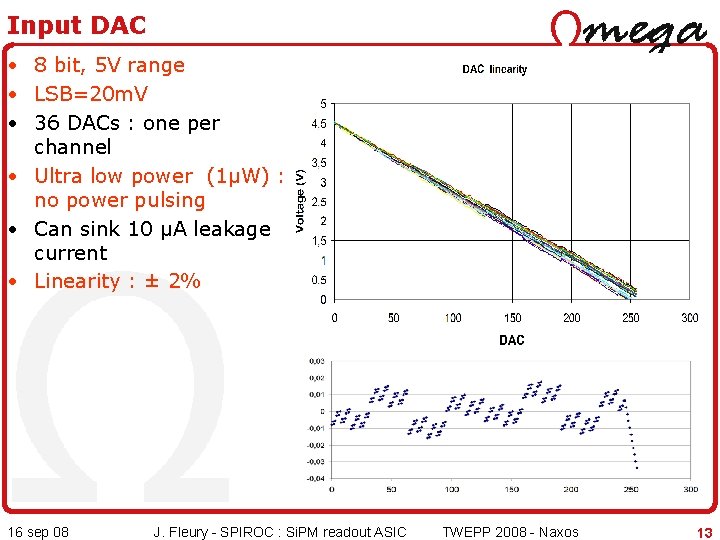

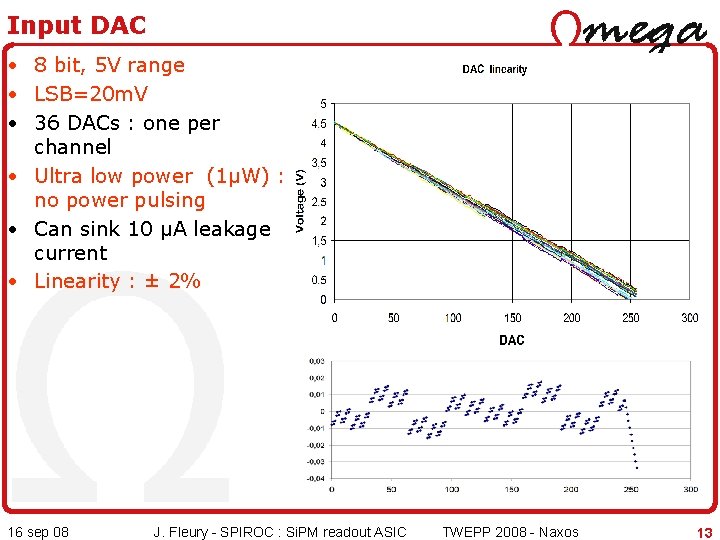

Input DAC • 8 bit, 5 V range • LSB=20 m. V • 36 DACs : one per channel • Ultra low power (1µW) : no power pulsing • Can sink 10 µA leakage current • Linearity : ± 2% 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 13

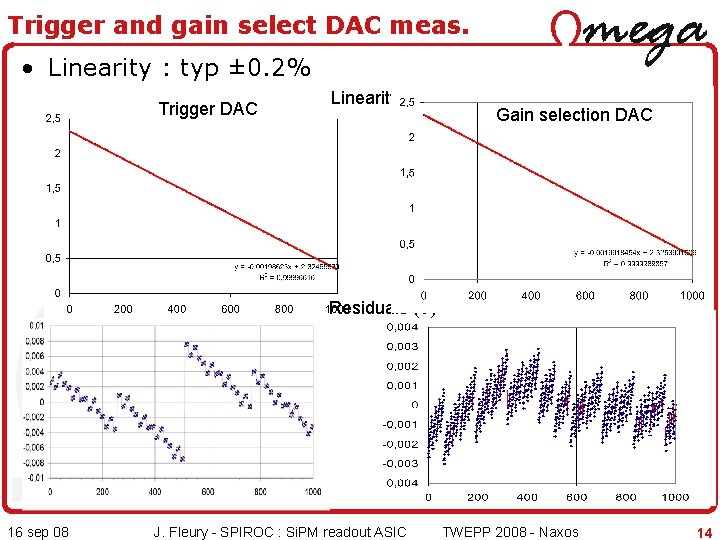

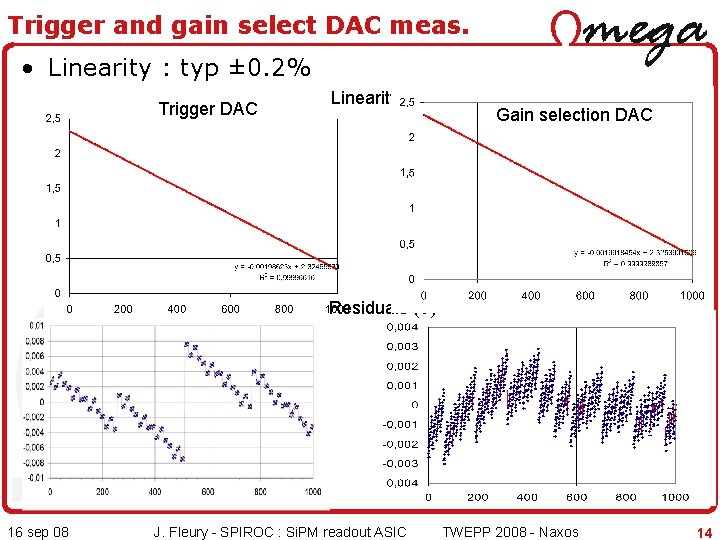

Trigger and gain select DAC meas. • Linearity : typ ± 0. 2% Trigger DAC Linearity Gain selection DAC Residuals (V) 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 14

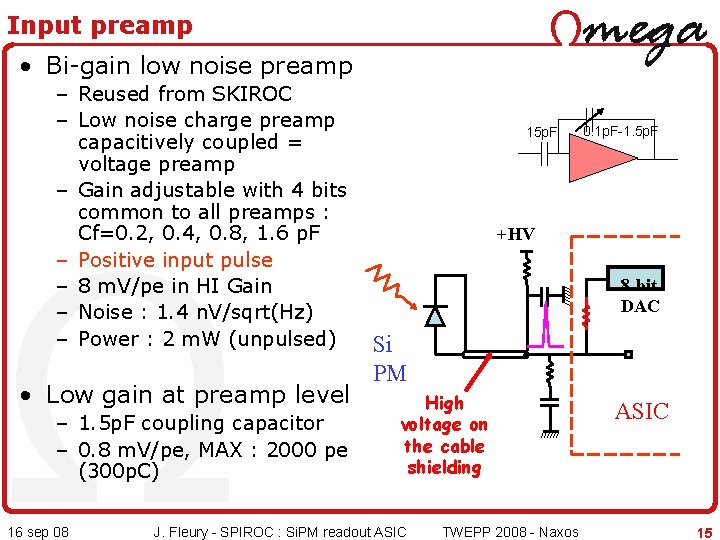

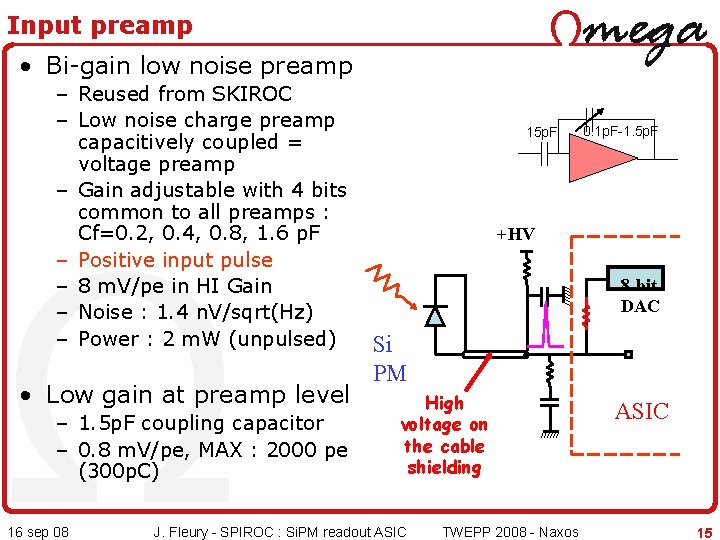

Input preamp • Bi-gain low noise preamp – Reused from SKIROC – Low noise charge preamp capacitively coupled = voltage preamp – Gain adjustable with 4 bits common to all preamps : Cf=0. 2, 0. 4, 0. 8, 1. 6 p. F – Positive input pulse – 8 m. V/pe in HI Gain – Noise : 1. 4 n. V/sqrt(Hz) – Power : 2 m. W (unpulsed) Si • Low gain at preamp level – 1. 5 p. F coupling capacitor – 0. 8 m. V/pe, MAX : 2000 pe (300 p. C) 16 sep 08 15 p. F 0. 1 p. F-1. 5 p. F +HV 8 -bit DAC PM High voltage on the cable shielding J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos ASIC 15

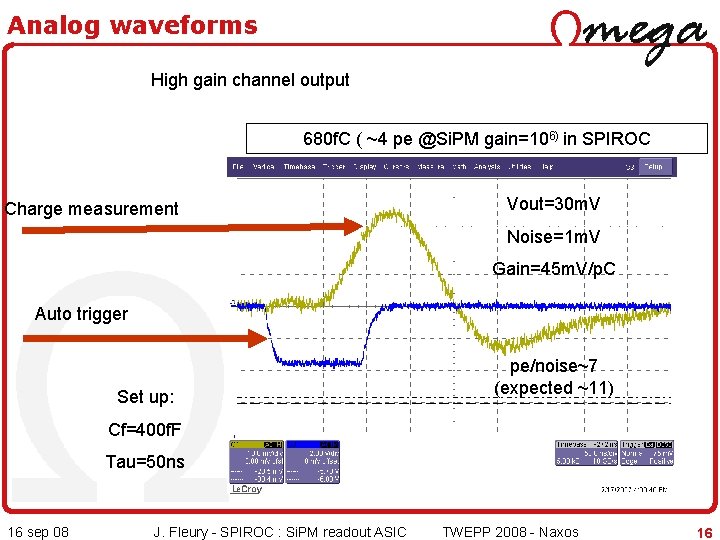

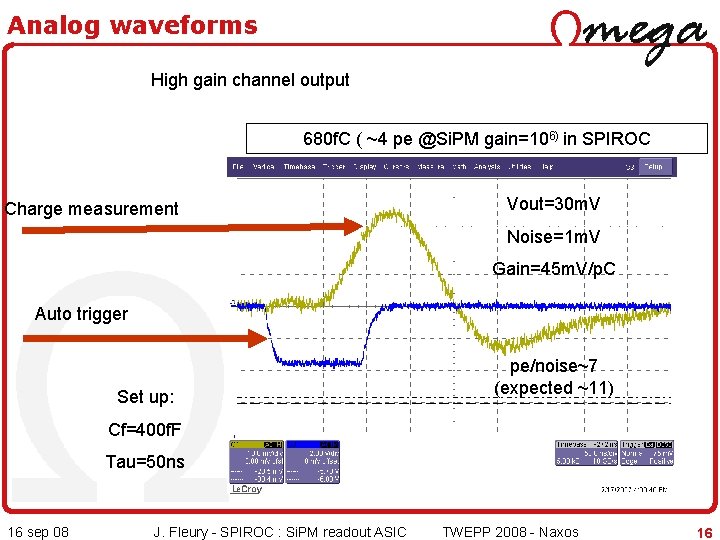

Analog waveforms High gain channel output 680 f. C ( ~4 pe @Si. PM gain=106) in SPIROC Charge measurement Vout=30 m. V Noise=1 m. V Gain=45 m. V/p. C Auto trigger Set up: pe/noise~7 (expected ~11) Cf=400 f. F Tau=50 ns 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 16

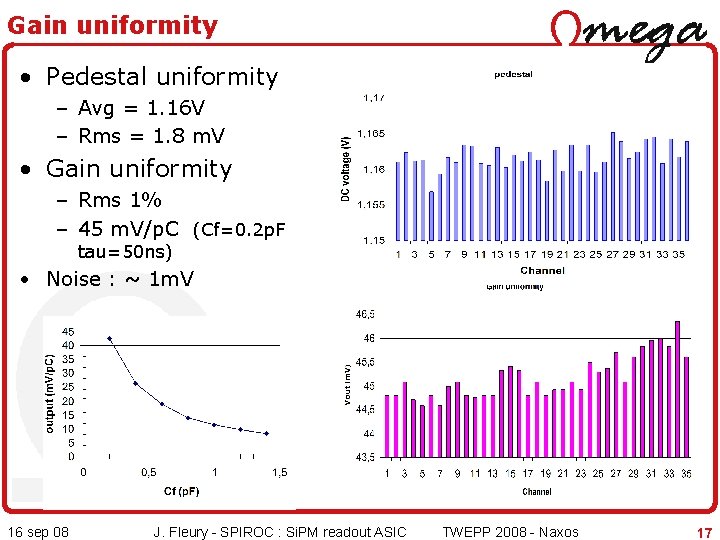

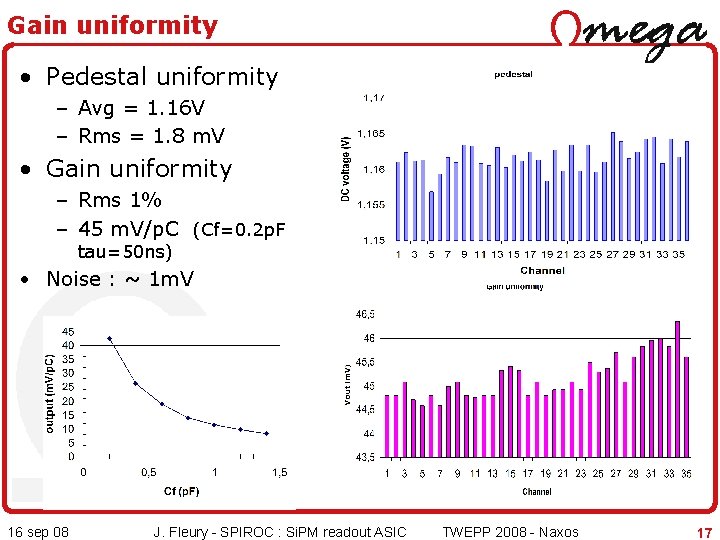

Gain uniformity • Pedestal uniformity – Avg = 1. 16 V – Rms = 1. 8 m. V • Gain uniformity – Rms 1% – 45 m. V/p. C (Cf=0. 2 p. F tau=50 ns) • Noise : ~ 1 m. V 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 17

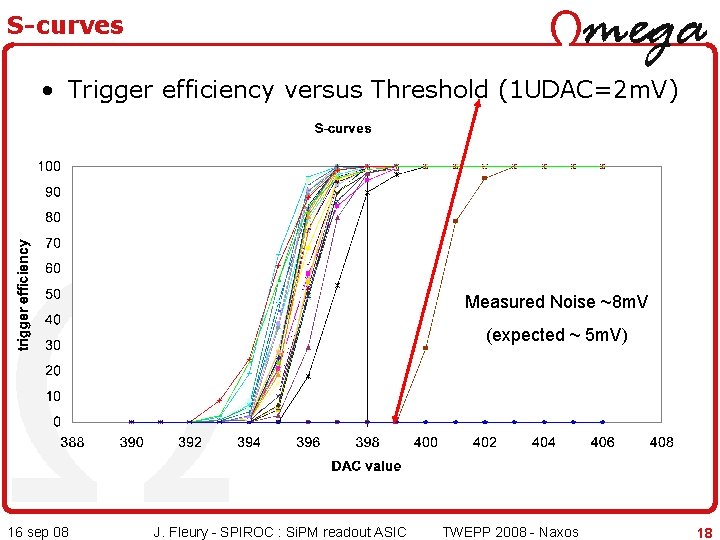

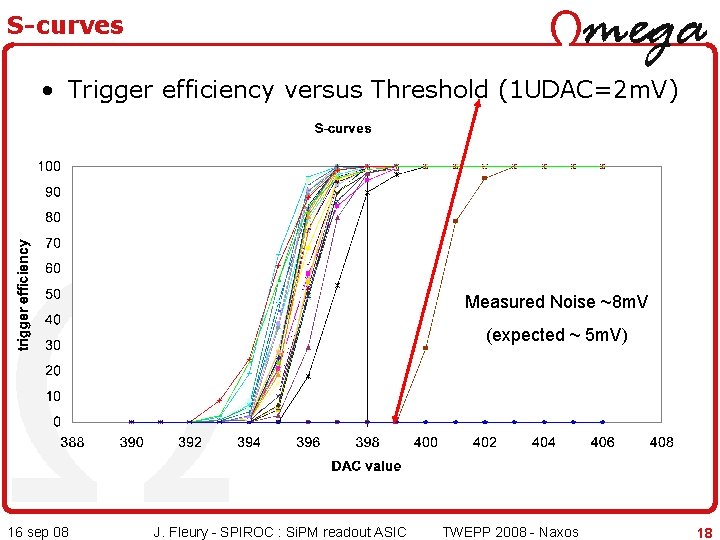

S-curves • Trigger efficiency versus Threshold (1 UDAC=2 m. V) Measured Noise ~8 m. V (expected ~ 5 m. V) 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 18

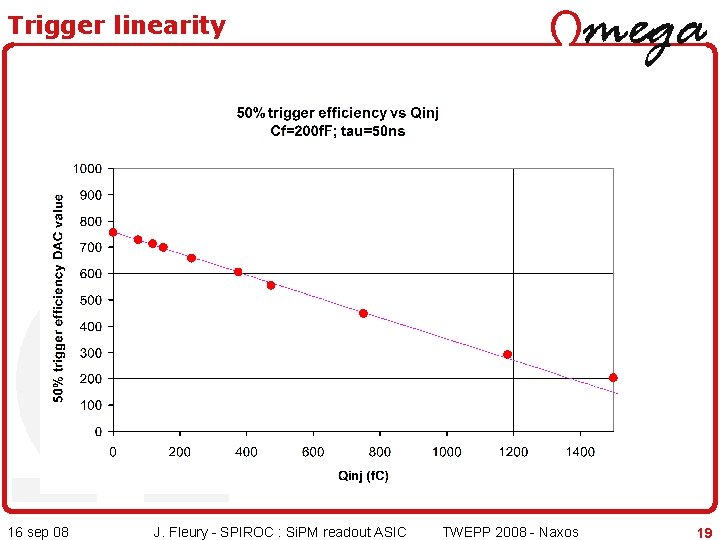

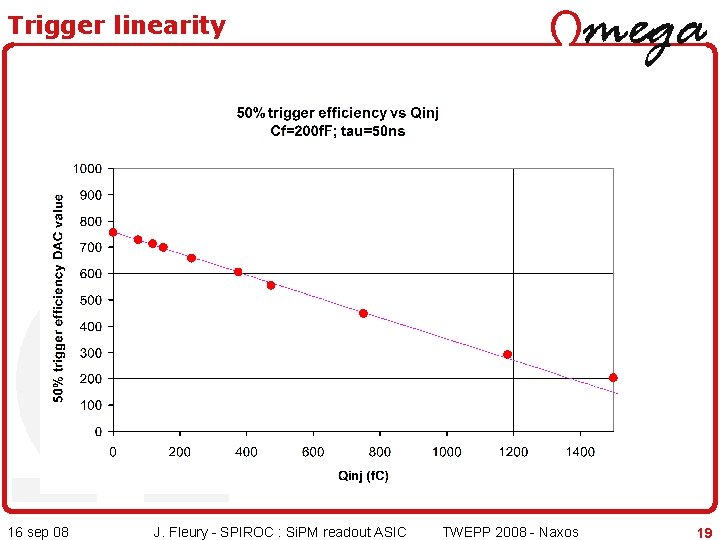

Trigger linearity 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 19

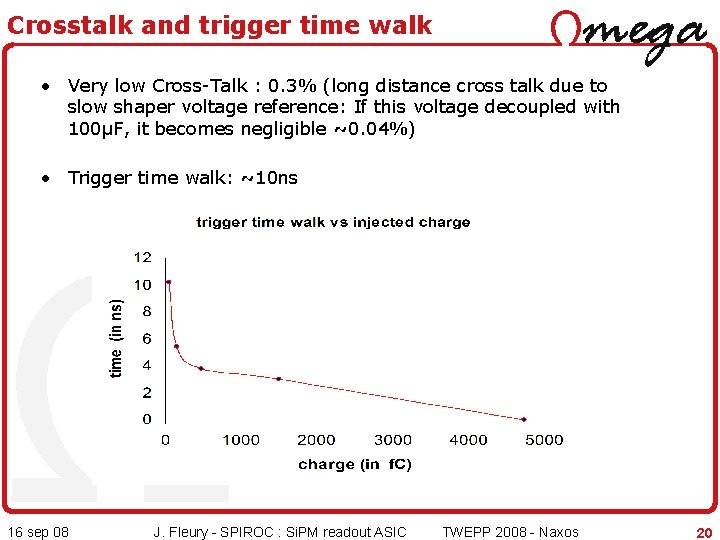

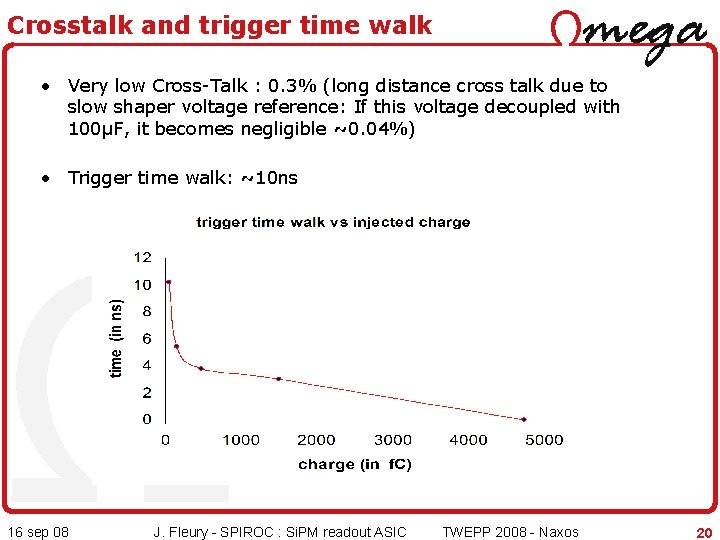

Crosstalk and trigger time walk • Very low Cross-Talk : 0. 3% (long distance cross talk due to slow shaper voltage reference: If this voltage decoupled with 100µF, it becomes negligible ~0. 04%) • Trigger time walk: ~10 ns 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 20

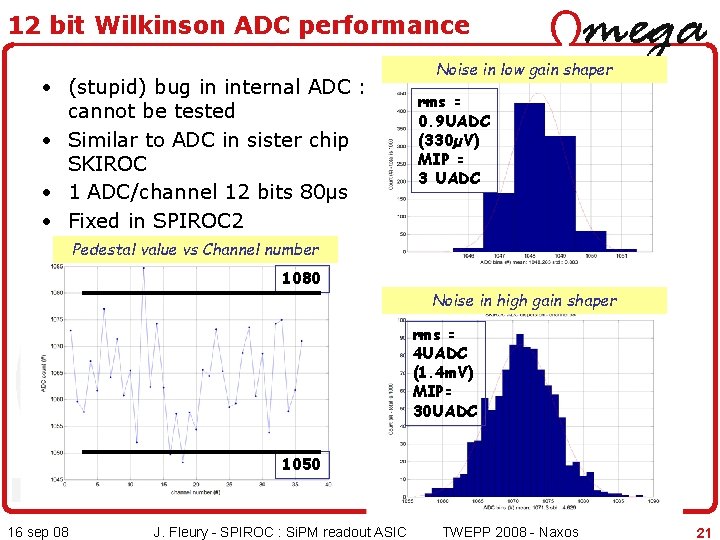

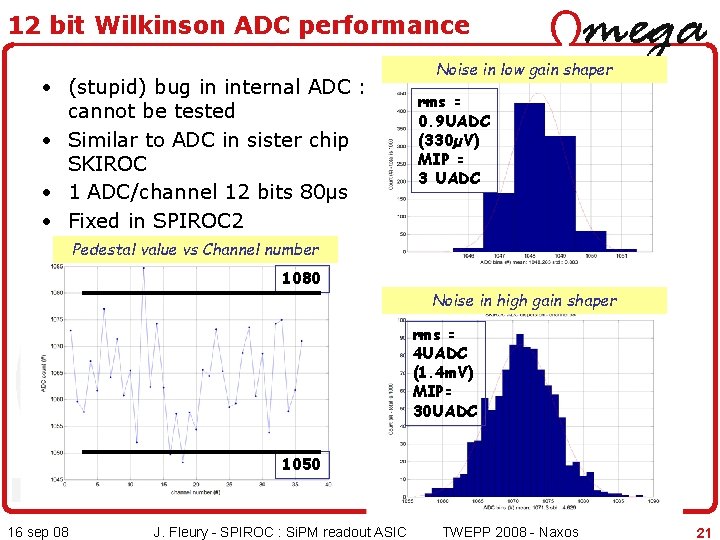

12 bit Wilkinson ADC performance • (stupid) bug in internal ADC : cannot be tested • Similar to ADC in sister chip SKIROC • 1 ADC/channel 12 bits 80µs • Fixed in SPIROC 2 Noise in low gain shaper rms = 0. 9 UADC (330µV) MIP = 3 UADC Pedestal value vs Channel number 1080 Noise in high gain shaper rms = 4 UADC (1. 4 m. V) MIP= 30 UADC 1050 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 21

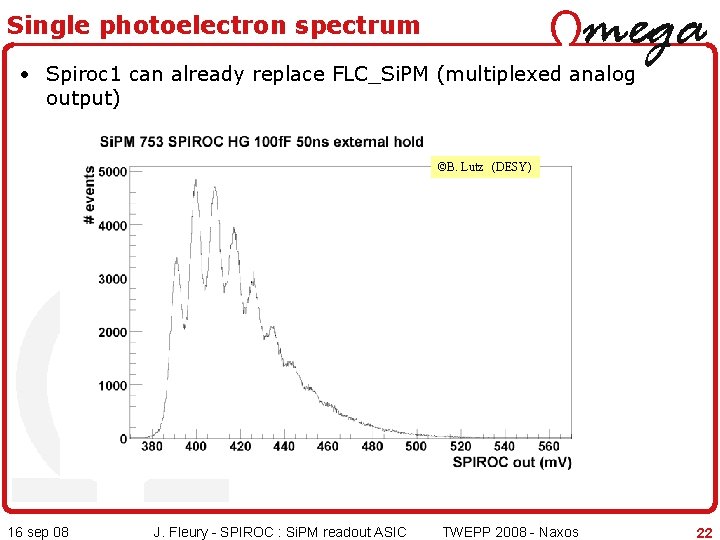

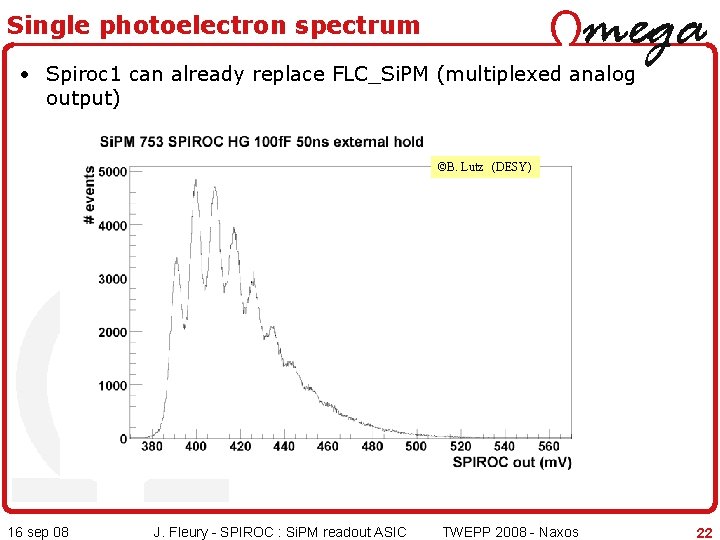

Single photoelectron spectrum • Spiroc 1 can already replace FLC_Si. PM (multiplexed analog output) ©B. Lutz (DESY) 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 22

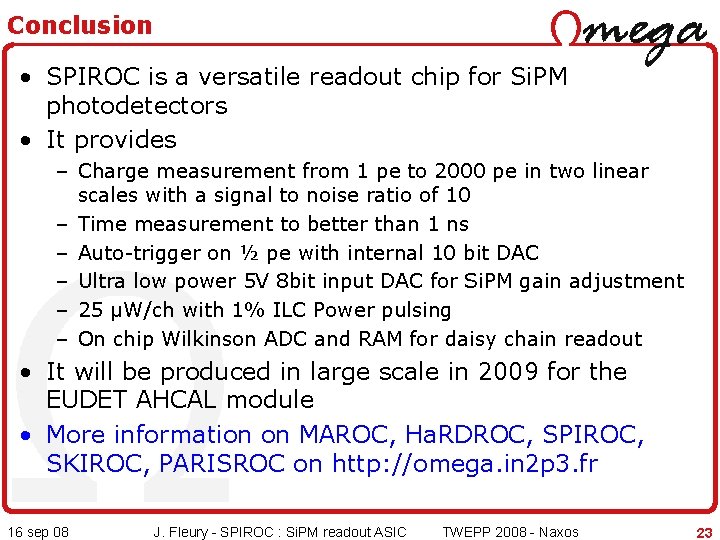

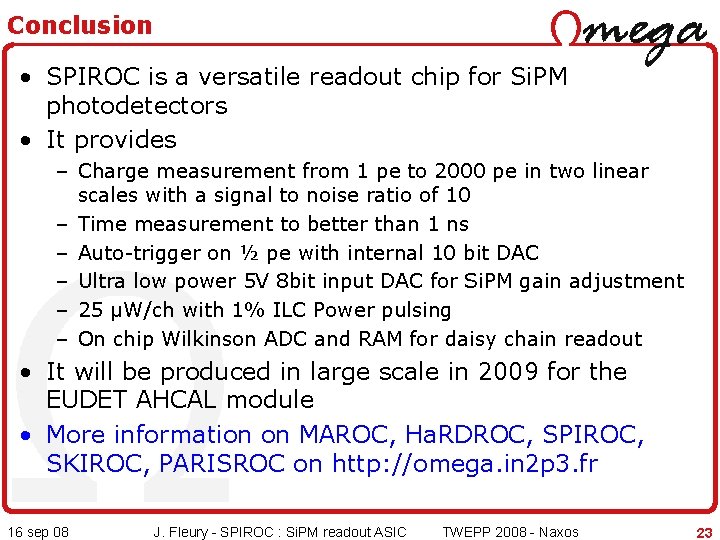

Conclusion • SPIROC is a versatile readout chip for Si. PM photodetectors • It provides – Charge measurement from 1 pe to 2000 pe in two linear scales with a signal to noise ratio of 10 – Time measurement to better than 1 ns – Auto-trigger on ½ pe with internal 10 bit DAC – Ultra low power 5 V 8 bit input DAC for Si. PM gain adjustment – 25 µW/ch with 1% ILC Power pulsing – On chip Wilkinson ADC and RAM for daisy chain readout • It will be produced in large scale in 2009 for the EUDET AHCAL module • More information on MAROC, Ha. RDROC, SPIROC, SKIROC, PARISROC on http: //omega. in 2 p 3. fr 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 23

Backup slides 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 24

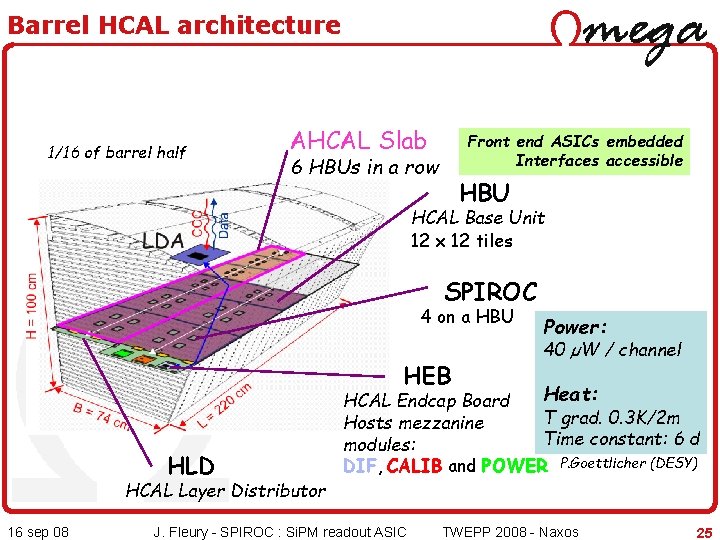

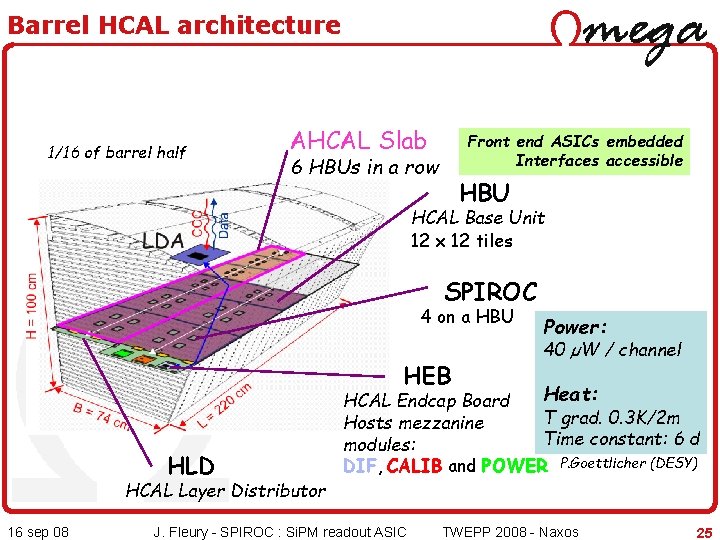

Barrel HCAL architecture 1/16 of barrel half AHCAL Slab Front end ASICs embedded Interfaces accessible 6 HBUs in a row HBU HCAL Base Unit 12 x 12 tiles SPIROC 4 on a HBU HEB HLD HCAL Layer Distributor 16 sep 08 Power: 40 µW / channel Heat: HCAL Endcap Board T grad. 0. 3 K/2 m Hosts mezzanine Time constant: 6 d modules: DIF, CALIB and POWER P. Goettlicher (DESY) J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 25

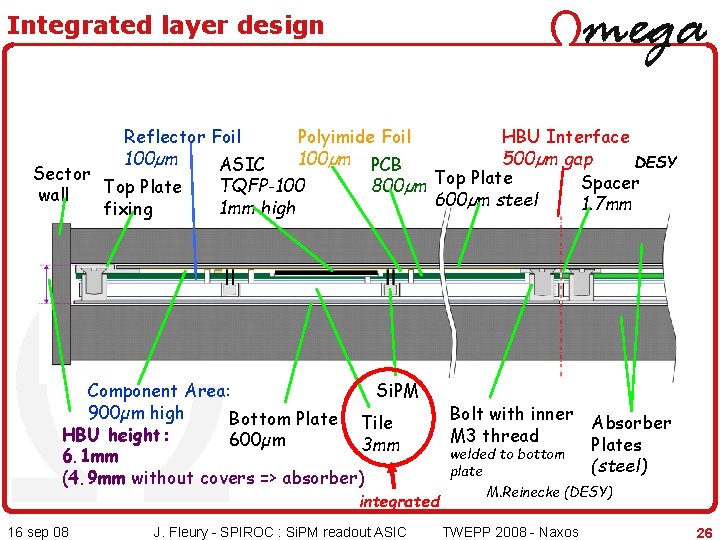

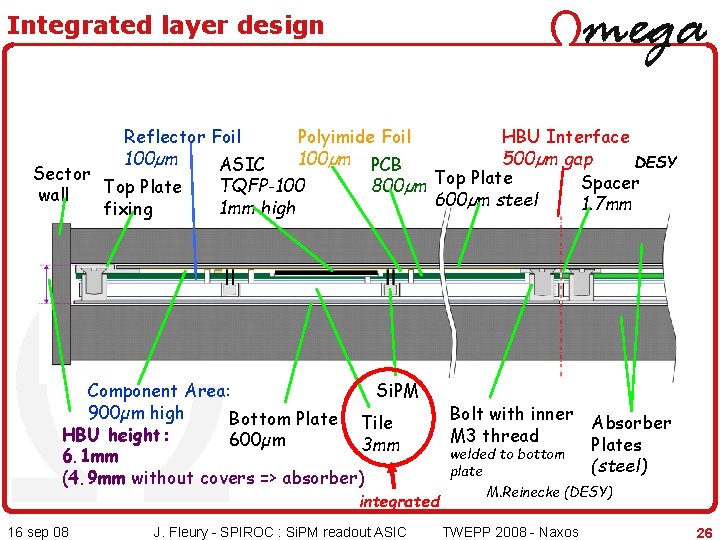

Integrated layer design Reflector Foil Polyimide Foil HBU Interface 100µm PCB 500µm gap DESY ASIC Sector Spacer TQFP-100 800µm Top Plate wall 600µm steel 1. 7 mm 1 mm high fixing Component Area: Si. PM 900µm high Bottom Plate Tile HBU height: 600µm 3 mm 6. 1 mm (4. 9 mm without covers => absorber) integrated 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC Bolt with inner M 3 thread Absorber Plates (steel) welded to bottom plate M. Reinecke (DESY) TWEPP 2008 - Naxos 26

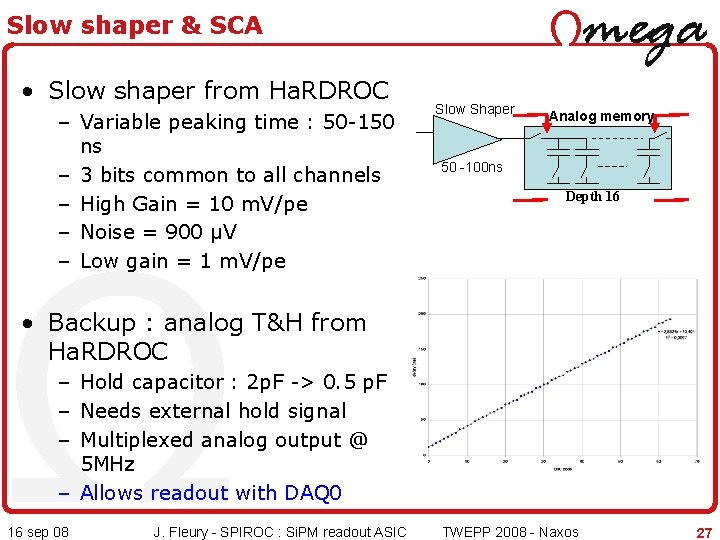

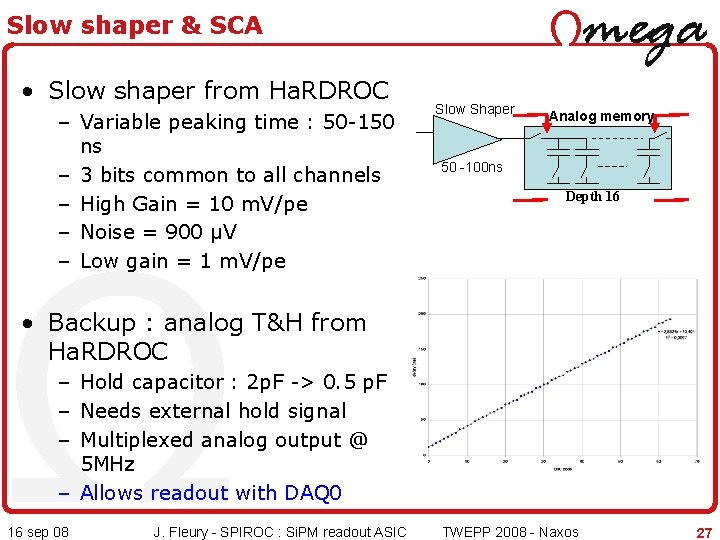

Slow shaper & SCA • Slow shaper from Ha. RDROC – Variable peaking time : 50 -150 ns – 3 bits common to all channels – High Gain = 10 m. V/pe – Noise = 900 µV – Low gain = 1 m. V/pe Slow Shaper Analog memory 50 -100 ns Depth 16 • Backup : analog T&H from Ha. RDROC – Hold capacitor : 2 p. F -> 0. 5 p. F – Needs external hold signal – Multiplexed analog output @ 5 MHz – Allows readout with DAQ 0 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 27

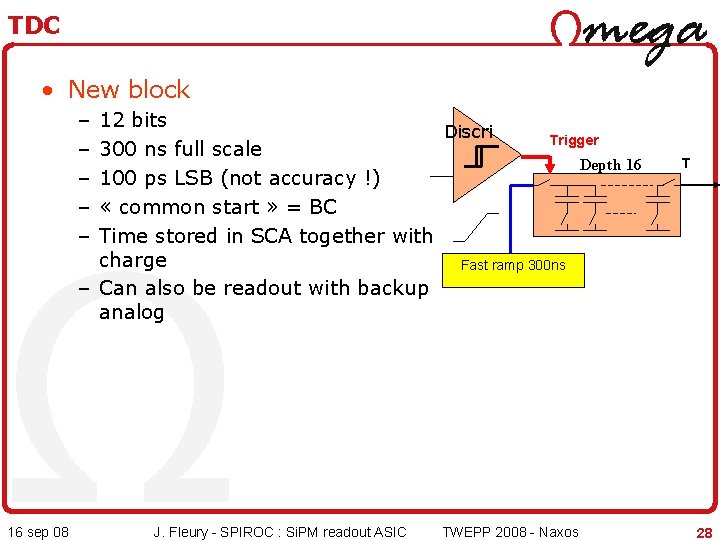

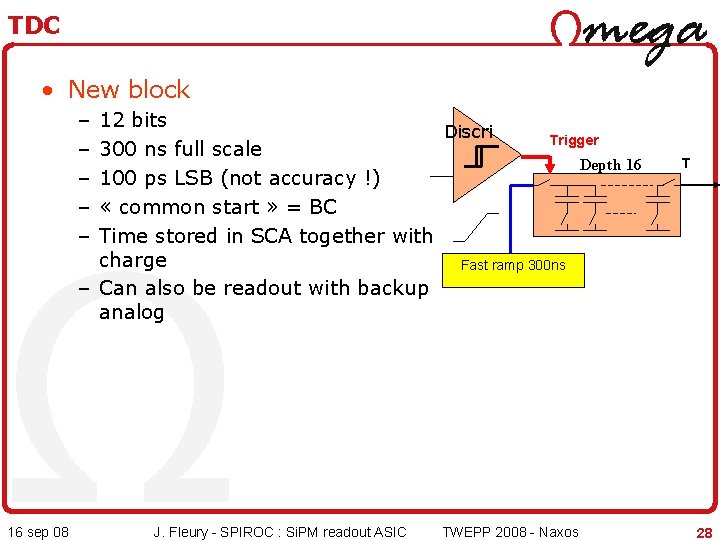

TDC • New block – – – 12 bits Discri Trigger 300 ns full scale Depth 16 100 ps LSB (not accuracy !) « common start » = BC Time stored in SCA together with charge Fast ramp 300 ns – Can also be readout with backup analog 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos T 28

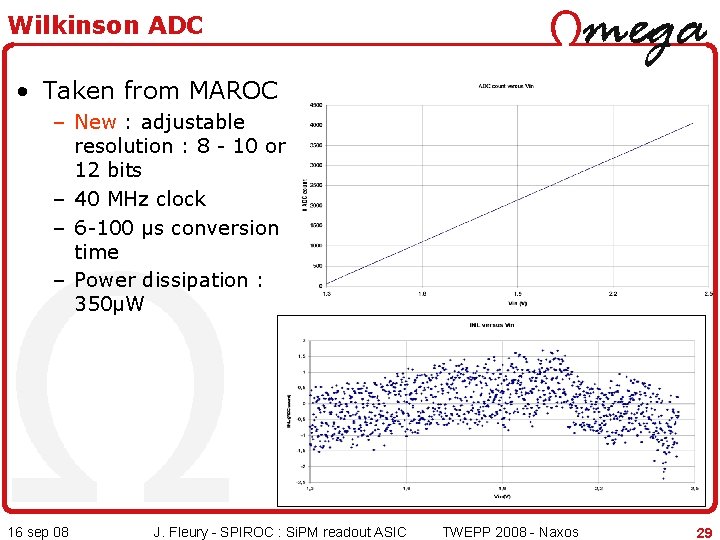

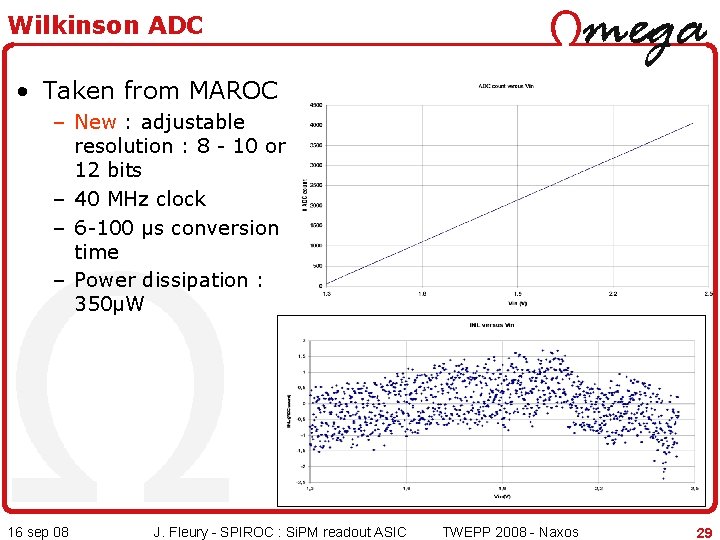

Wilkinson ADC • Taken from MAROC – New : adjustable resolution : 8 - 10 or 12 bits – 40 MHz clock – 6 -100 µs conversion time – Power dissipation : 350µW 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 29

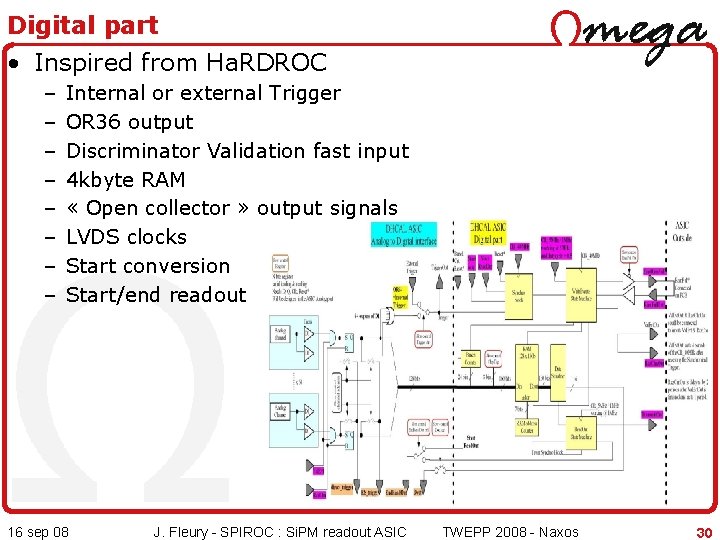

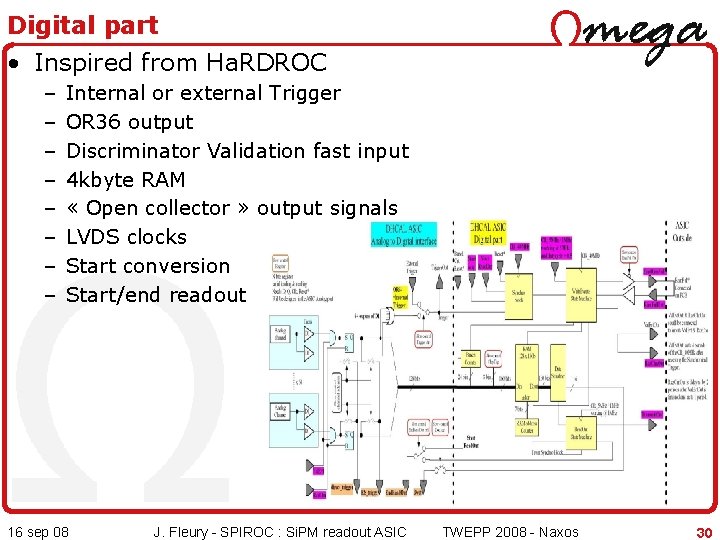

Digital part • Inspired from Ha. RDROC – – – – Internal or external Trigger OR 36 output Discriminator Validation fast input 4 kbyte RAM « Open collector » output signals LVDS clocks Start conversion Start/end readout 16 sep 08 J. Fleury - SPIROC : Si. PM readout ASIC TWEPP 2008 - Naxos 30