CSE 560 Computer Systems Architecture Exam 1 Review

- Slides: 13

CSE 560 Computer Systems Architecture Exam 1 Review

Logistics • Date and Time – Monday, Nov 2, during class time, 2: 30 to 4: 00 pm, starting at or before 2: 30 – Exam is timed for 80 mins from when you start • Delivery is via Gradescope – Link will be delivered ahead of 2: 30 pm on Nov 2 – 100% on-line – Use a browser with a decent screen size! – You can exit and restart, but timer is still running – Read questions carefully (e. g. , pipeline diagrams) • Alerts will be via Piazza and Email

More Logistics • Answer format is limited – ○ Circles (radio buttons) are “choose one” – □ Squares are “choose all that are correct” – Don’t add units where we ask you not to – “Show your work” is for partial credit – You might want pencil and paper available • Anything you write there won’t be graded! • Last question is for notes to us – Free-form option to tell us anything that we should know when grading the exam – Identify relevant question, please!

Style • Questions – Question 1 will be a collection of short answer things (e. g. , true/false, fill in the blank, quick definition) – Questions 2 through N will be longer (going more in depth on a particular subject) • Open book, open notes, NOT open neighbor! • One-page “crib sheet” is recommended – 8. 5 x 11 sheet, front and back, whatever you want to include (content-wise) • Calculator is allowed, but show your work

Instruction Set Architecture • Definition • Components – Machine instructions – Programmer-level memory model – Operating Modes • What isn’t included, e. g. , – Pipelined execution – Branch predictors – Caches

Qualities of a Good ISA • Programmability • Implementability • Compatibility

Specifics of ISAs • Instruction Format • Register File • Main Memory – Little endian, big endian • Addressing Modes • Conditional Branching – Condition Codes – Test and Branch • RISC vs. CISC

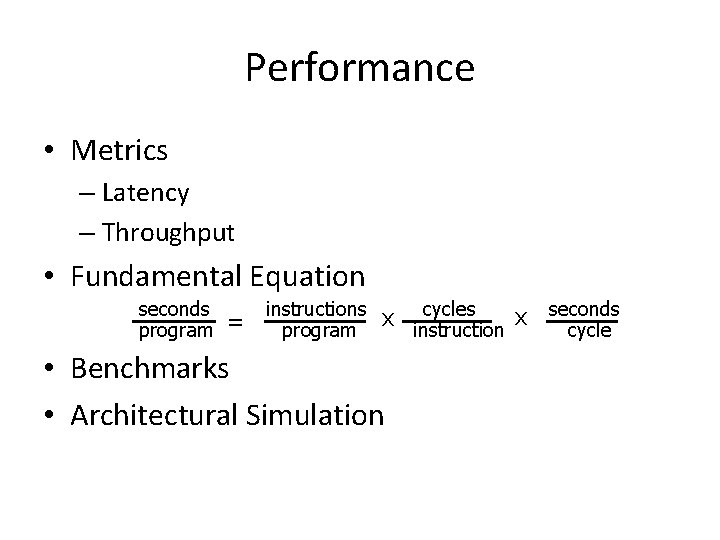

Performance • Metrics – Latency – Throughput • Fundamental Equation seconds program = instructions program cycles x seconds x instruction cycle • Benchmarks • Architectural Simulation

Technology • Moore’s Law • Transistor Properties – Implications of scaling • • Cost Speed Power and Energy Reliability

Pipelining • 5 -stage example pipeline – What happens where – Data dependencies – Hazards – Bypassing (forwarding) • Pipeline diagrams • Multi-cycle operations – Pipelined functional units (e. g. , multiplier)

Branch Prediction • Why? • How? – Classic types • Where? – Esp. in context of 5 -stage pipeline • Performance implications?

Parallel Pipelines • Superscalar – In-order execution – Out-of-order execution • Scheduling – In-order and out-of-order – Single issue and multiple issue – Loop unrolling • Pipeline diagrams – Both kinds

Time for Q&A • We’ll start right before (or at) 2: 30 pm • Open book, open notes, NOT open neighbor • One page “crib sheet” recommended (both sides), it does not have to be handwritten • Calculator OK • Read questions carefully (esp. pipeline diagrams)