CSE 3322 Computer Architecture Dr John Patterson 614

![Software Hierarchical Layers High Level Language g = h + A[8] Compiler Assembly Language Software Hierarchical Layers High Level Language g = h + A[8] Compiler Assembly Language](https://slidetodoc.com/presentation_image_h/2d4fe621513514980ad48a5d603c6f5a/image-33.jpg)

![Software Hierarchical Layers High Level Language Compiler Assembly Language g = h + A[8] Software Hierarchical Layers High Level Language Compiler Assembly Language g = h + A[8]](https://slidetodoc.com/presentation_image_h/2d4fe621513514980ad48a5d603c6f5a/image-34.jpg)

- Slides: 34

CSE 3322 Computer Architecture Dr. John Patterson 614 NH Office Hours: M , W 11 – 12 noon 817 -272 -3679 john. patterson@uta. edu Grading Policy: Project 25% Exam III 25% Homework 5% add on Turn in start of class – no late homework

CSE 3322 Computer Architecture Course WEB SITE crystal. uta. edu/~jpatters Read Chapter 1 Computer Organization and Design

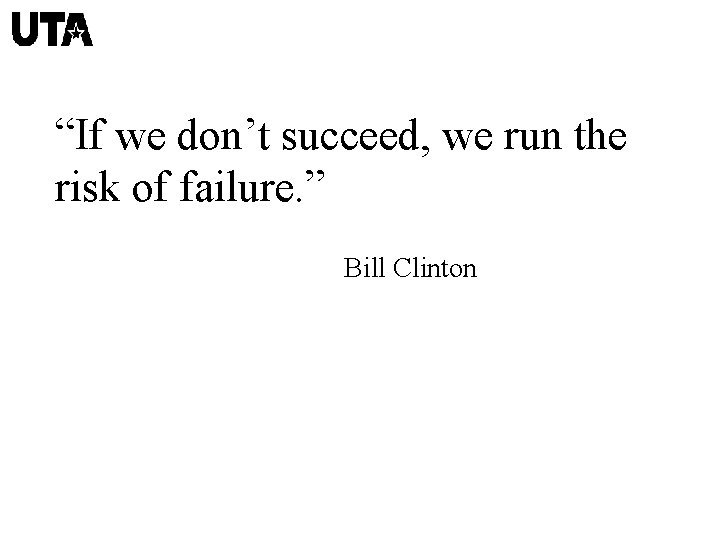

“If we don’t succeed, we run the risk of failure. ” Bill Clinton

CSE 3322 Computer Architecture The Low Level knowledge needed by High Level Programmers and Systems Designers

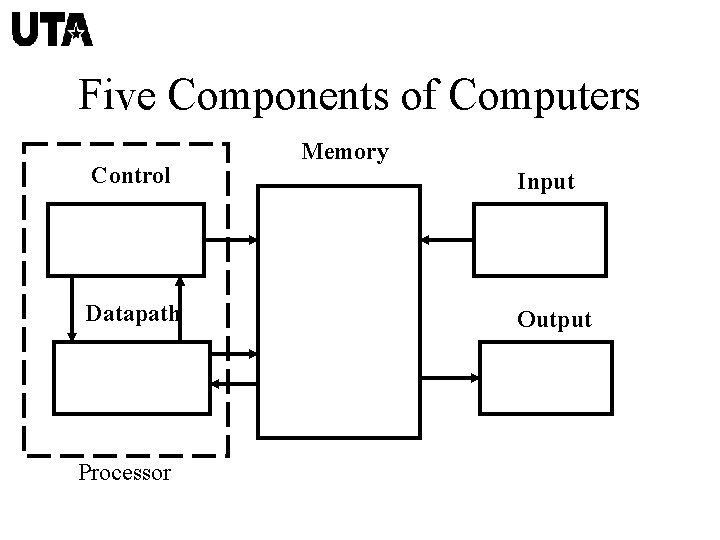

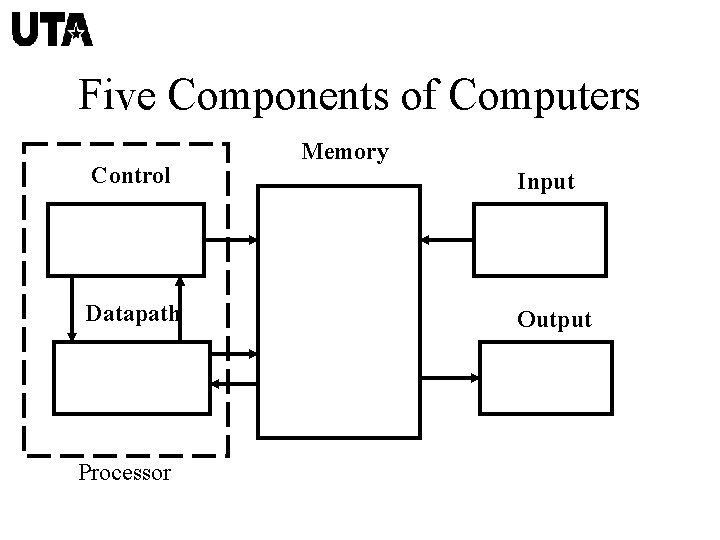

Five Components of Computers Control Datapath Processor Memory Input Output

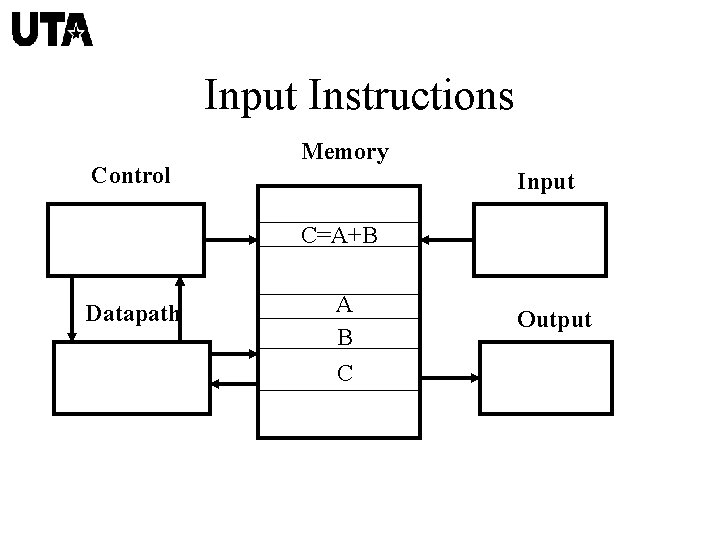

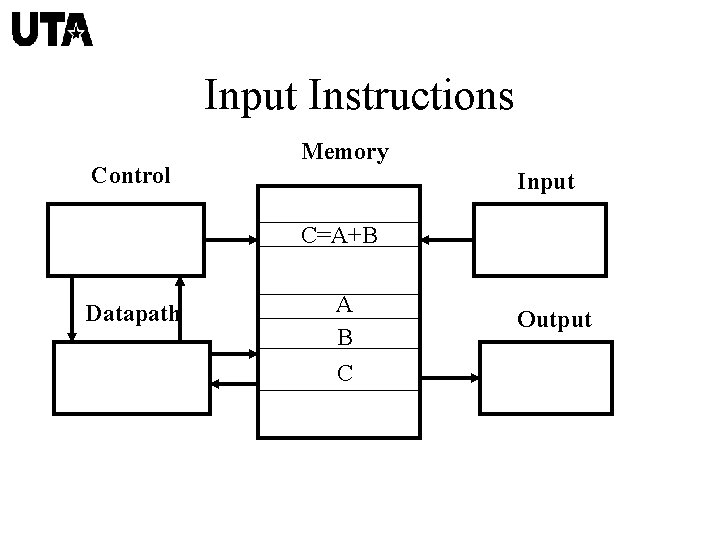

Input Instructions Control Memory Input C=A+B Datapath A B C Output

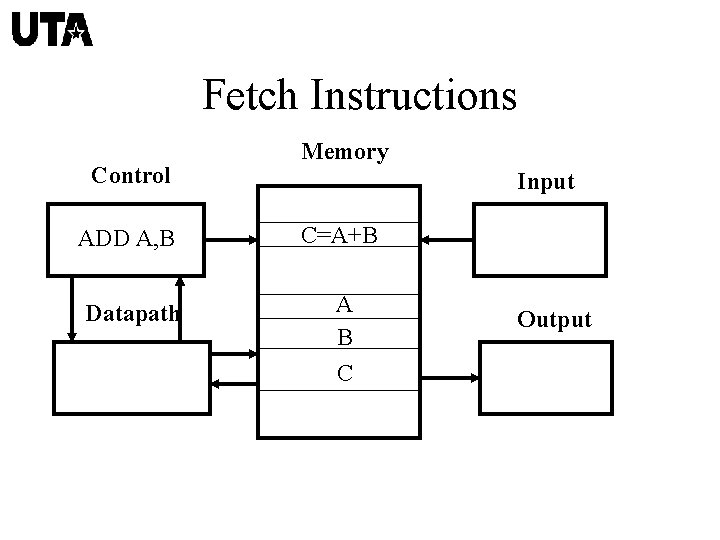

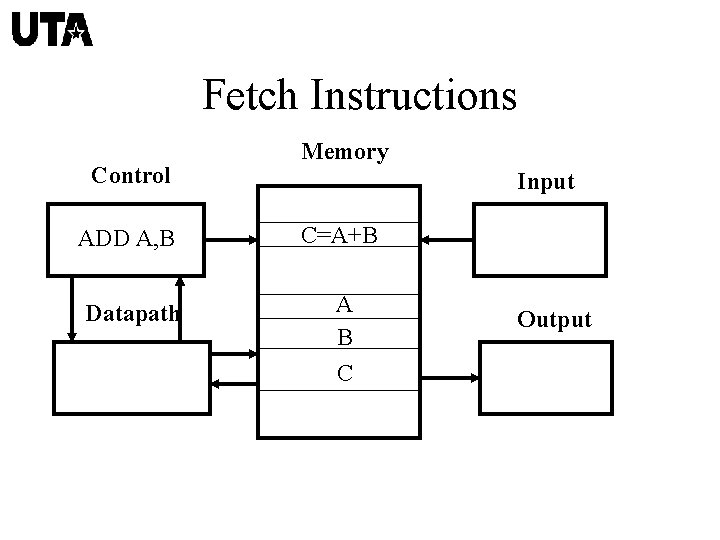

Fetch Instructions Control Memory Input ADD A, B C=A+B Datapath A B C Output

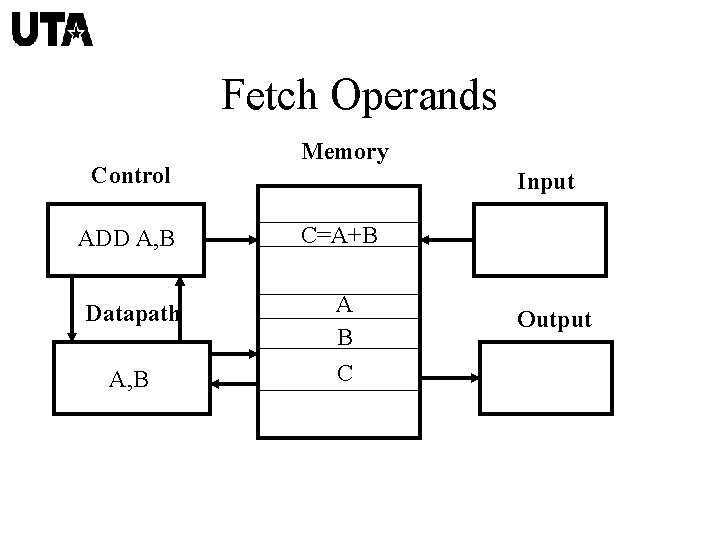

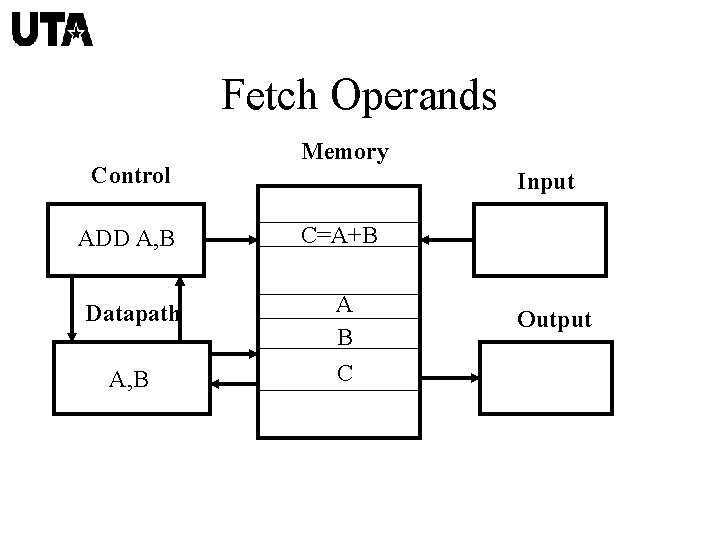

Fetch Operands Control Memory Input ADD A, B C=A+B Datapath A B C A, B Output

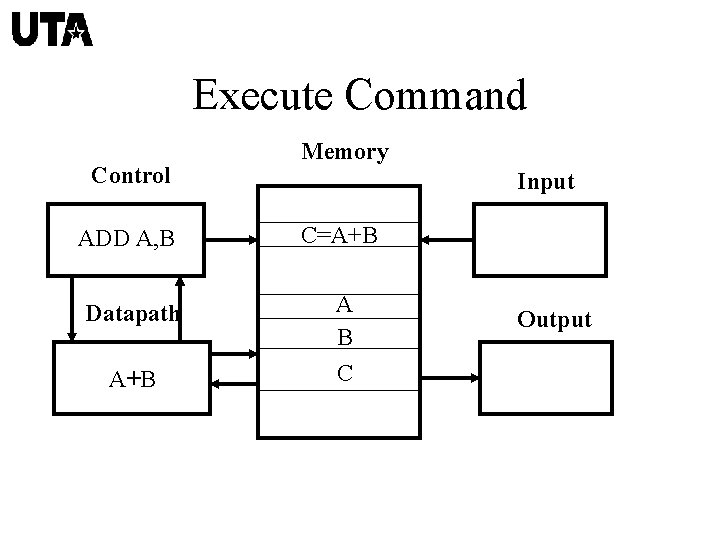

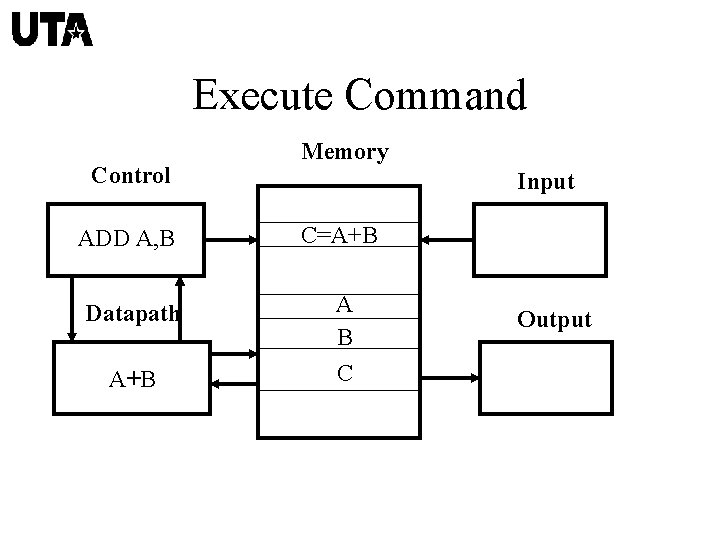

Execute Command Control Memory Input ADD A, B C=A+B Datapath A B C A+B Output

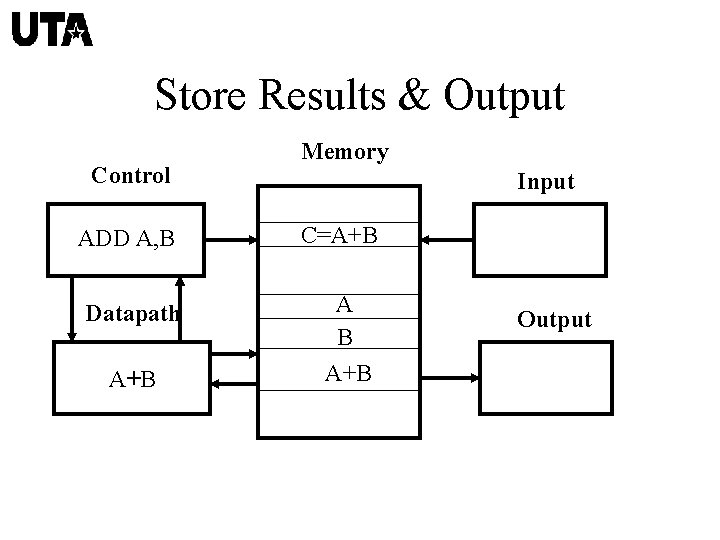

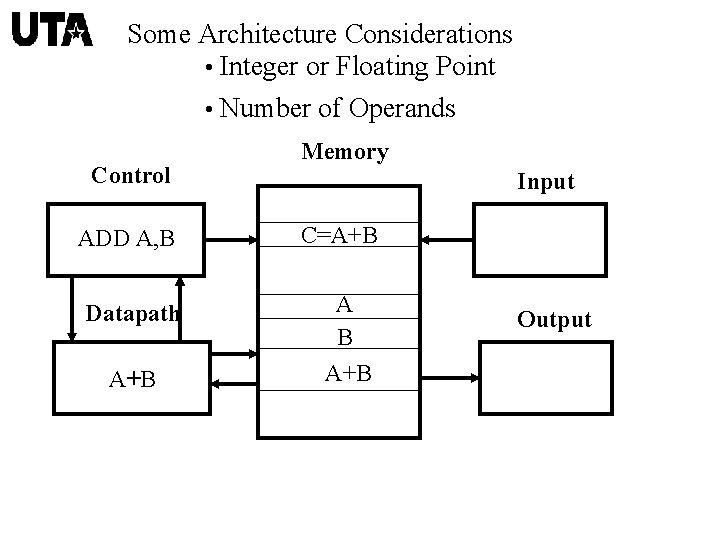

Store Results & Output Control Memory Input ADD A, B C=A+B Datapath A B A+B Output

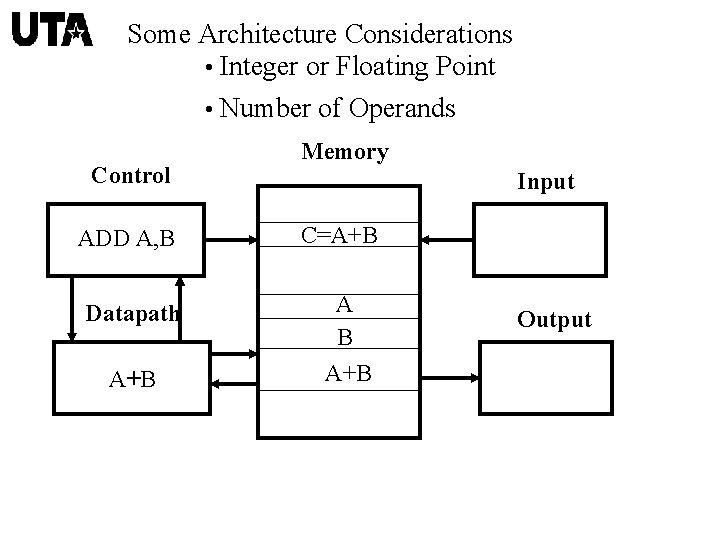

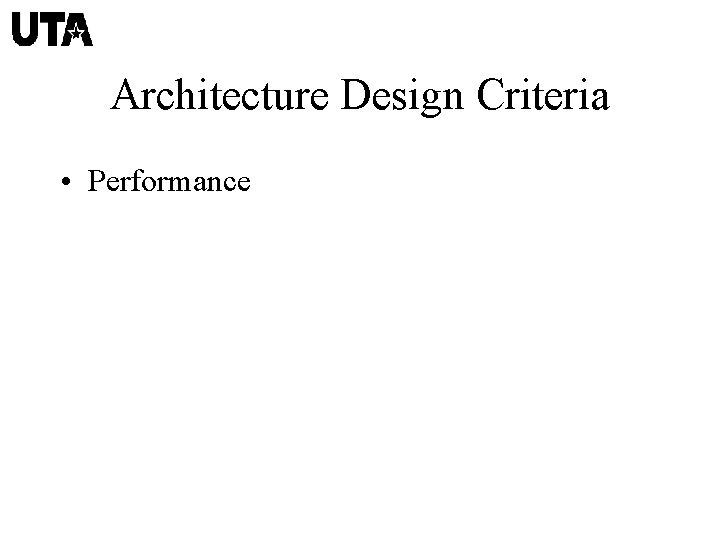

Some Architecture Considerations • Integer or Floating Point • Number of Operands Control Memory Input ADD A, B C=A+B Datapath A B A+B Output

Architecture Design Criteria • Performance

Architecture Design Criteria • Performance • Hardware Costs

Architecture Design Criteria • Performance • Hardware Costs Performance

Architecture Design Criteria • Performance • Hardware Costs Performance • Instruction Complexity

Architecture Design Criteria • Performance • Hardware Costs Performance • Instruction Complexity • Hardware Software Trade-Offs

Architecture Design Criteria • Performance • Hardware Costs Performance • Instruction Complexity • Hardware Software Trade-Offs • Etc. , Etc.

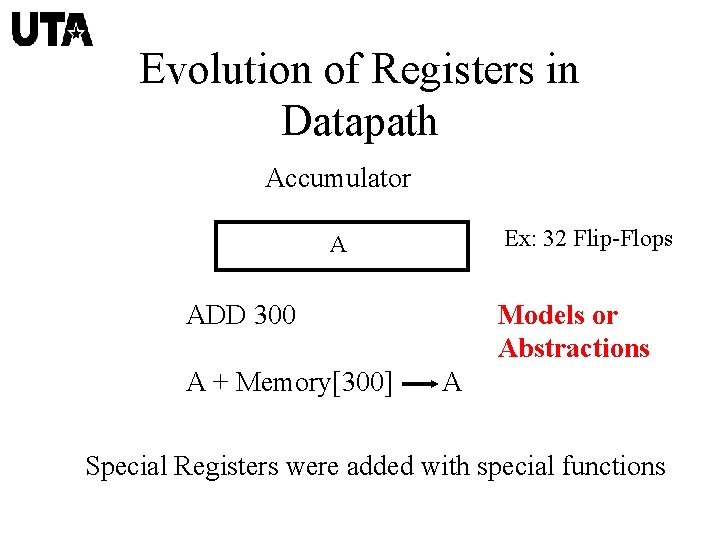

Evolution of Registers in Datapath Accumulator Ex: 32 Flip-Flops A ADD 300 Add the contents of memory location 300 to the Accumulator A + Memory[300] A

Evolution of Registers in Datapath Accumulator Ex: 32 Flip-Flops A ADD 300 A + Memory[300] A Special Registers were added with special functions

Evolution of Registers in Datapath Accumulator Ex: 32 Flip-Flops A ADD 300 A + Memory[300] Models or Abstractions A Special Registers were added with special functions

Evolution of Registers in Datapath • 32 General Purpose Registers

Evolution of Registers in Datapath • 32 General Purpose Registers • Called a Load-Store or Register-Register machine

Evolution of Registers in Datapath • 32 General Purpose Registers • Called a Load-Store or Register-Register machine • All Registers can be used for any purpose

Evolution of Registers in Datapath • 32 General Purpose Registers • Called a Load-Store or Register-Register machine • All Registers can be used for any purpose • Ex: Add any two Registers and put the result in a third Register

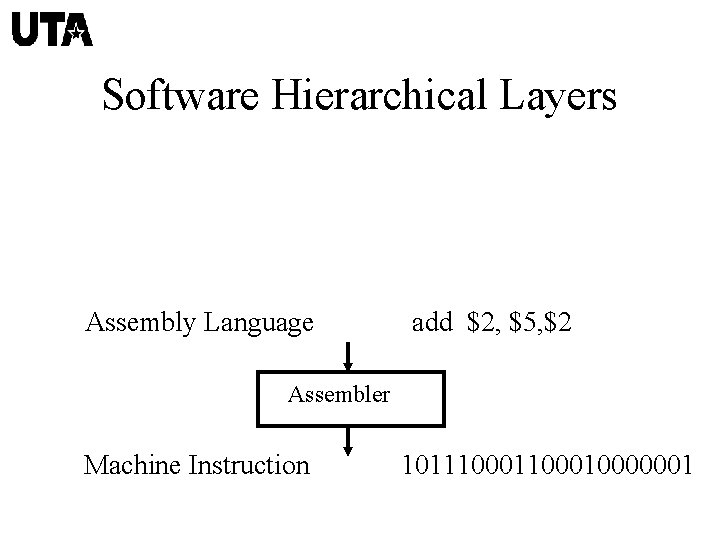

Instruction Set Architecture • Consists of All of the Instructions and How Each Works

Instruction Set Architecture • Consists of All of the Instructions and How Each Works Models or Abstractions

Instruction Set Architecture • Consists of All of the Instructions and How Each Works • Is the Interface Between Hardware and Software

Instruction Set Architecture • Consists of All of the Instructions and How Each Works • Is the Interface Between Hardware and Software • Defines the Functionality

Instruction Set Architecture • Consists of All of the Instructions and How Each Works • Is the Interface Between Hardware and Software • Defines the Functionality • Determines the Inherent Performance

Instruction Set Architecture • Consists of All of the Instructions and How Each Works • Is the Interface Between Hardware and Software • Defines the Functionality • Determines the Inherent Performance • Determines the Software Compatibility

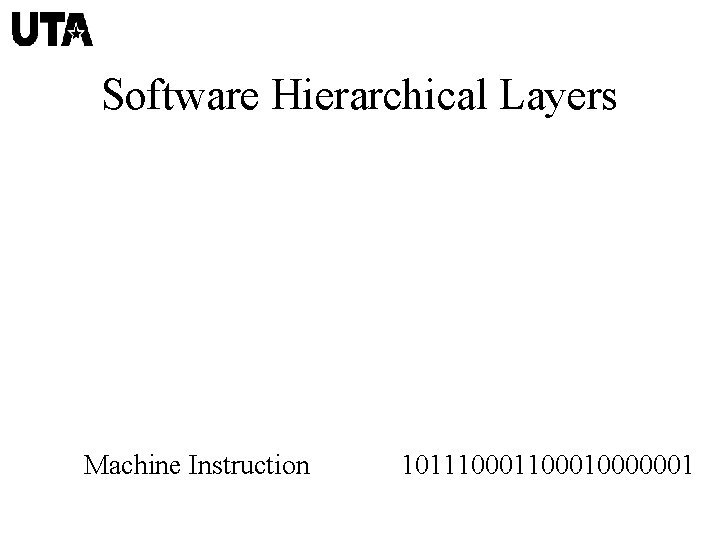

Software Hierarchical Layers Machine Instruction 1011100010000001

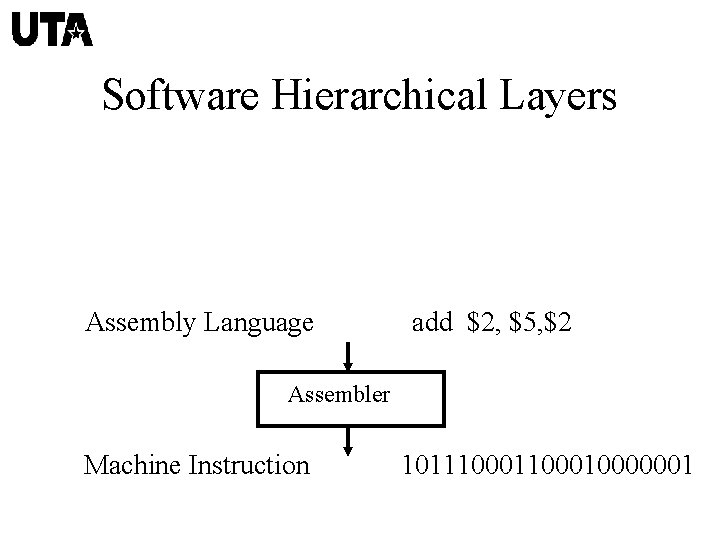

Software Hierarchical Layers Assembly Language add $2, $5, $2 Assembler Machine Instruction 1011100010000001

![Software Hierarchical Layers High Level Language g h A8 Compiler Assembly Language Software Hierarchical Layers High Level Language g = h + A[8] Compiler Assembly Language](https://slidetodoc.com/presentation_image_h/2d4fe621513514980ad48a5d603c6f5a/image-33.jpg)

Software Hierarchical Layers High Level Language g = h + A[8] Compiler Assembly Language add $2, $5, $2 Assembler Machine Instruction 1011100010000001

![Software Hierarchical Layers High Level Language Compiler Assembly Language g h A8 Software Hierarchical Layers High Level Language Compiler Assembly Language g = h + A[8]](https://slidetodoc.com/presentation_image_h/2d4fe621513514980ad48a5d603c6f5a/image-34.jpg)

Software Hierarchical Layers High Level Language Compiler Assembly Language g = h + A[8] Models or Abstractions add $2, $5, $2 Assembler Machine Instruction 1011100010000001