CSC255 Lecture 5 CPU StoredProgram Concept Program Execution

- Slides: 51

CSC-255 Lecture 5 CPU, Stored-Program Concept, Program Execution (Covers Brookshear Chapter 2) Modified by Ufuk Verun from Jim Janossy © 2002, De. Paul University CTI – Chicago and Brookshear © 2003 Pearson Education, Inc. CSC 255 -702/703 - CTI/De. Paul 1

Resources This Power. Point presentation is available for download at www. depaul. edu/~uverun/classes/CSC 255/fal l 2002/slides/Lecture_05. ppt Texbook: Chapter 2, Appendix C A Simple Machine Simulator: http: //wwwes. cs. utwente. nl/software/simpsim Print slides at 6 slides/page, avoid waste! Exams are based on slide content, homework and assigned readings CSC 255 -702/703 - CTI/De. Paul 2

Algorithmic Machine Must be able to: n n n Manipulate stored data Perform operations on data Coordinate sequence of operations Central Processing Unit (CPU) does it (in general) CSC 255 -702/703 - CTI/De. Paul 3

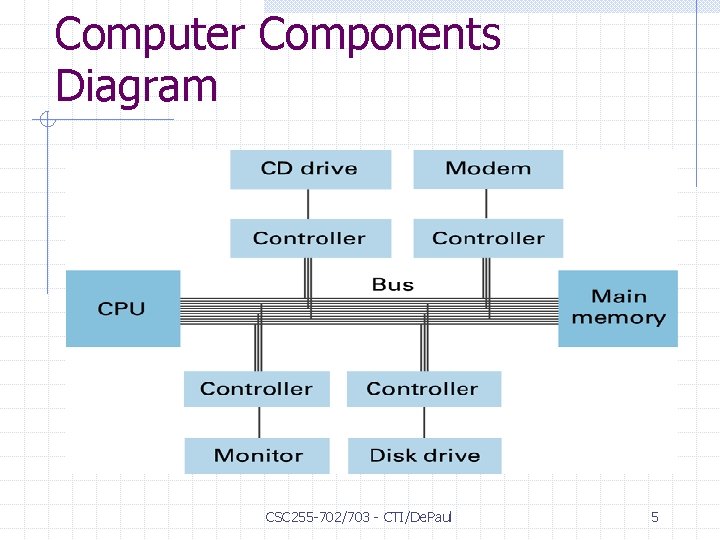

Basic Computer Components Overview Central Processing Unit (CPU ) Memory (RAM – Random Access Memory) CPU and RAM are installed on the main circuit board (motherboard) CPU and RAM communicate on bus Disk drive, motherboard, power supply There also devices such as graphics adaptor card, network interface card (NIC), sound card, etc. CSC 255 -702/703 - CTI/De. Paul 4

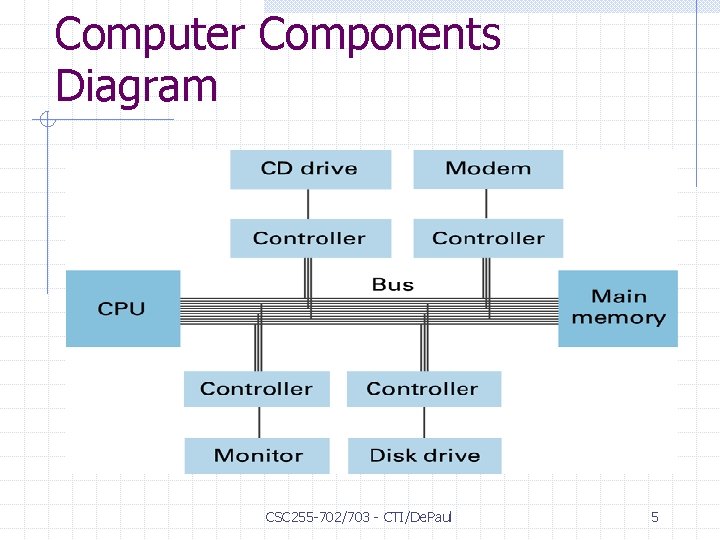

Computer Components Diagram CSC 255 -702/703 - CTI/De. Paul 5

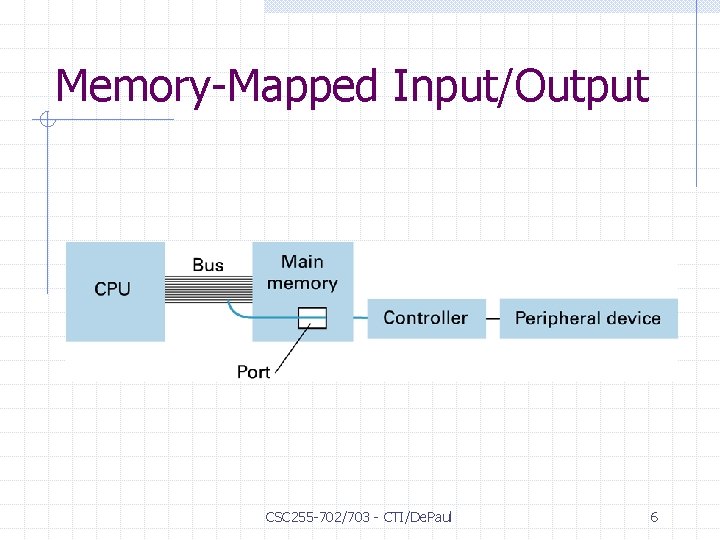

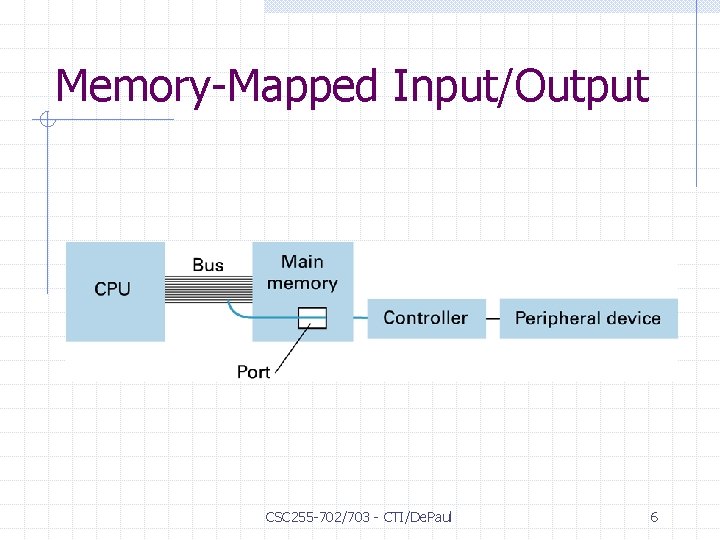

Memory-Mapped Input/Output CSC 255 -702/703 - CTI/De. Paul 6

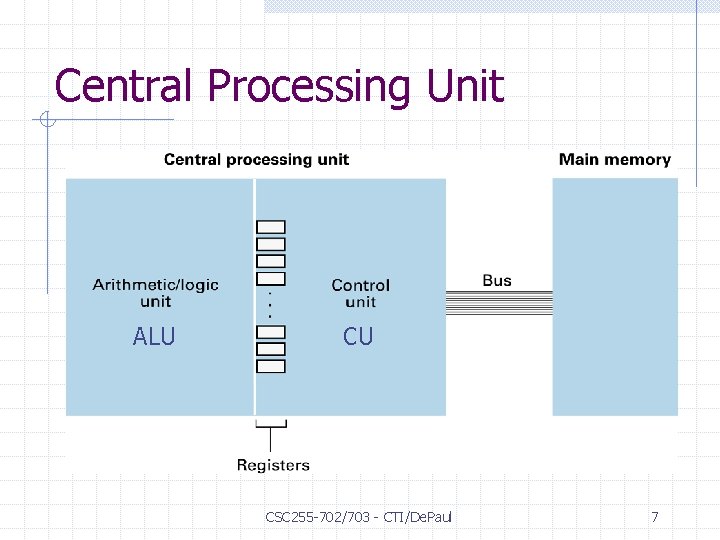

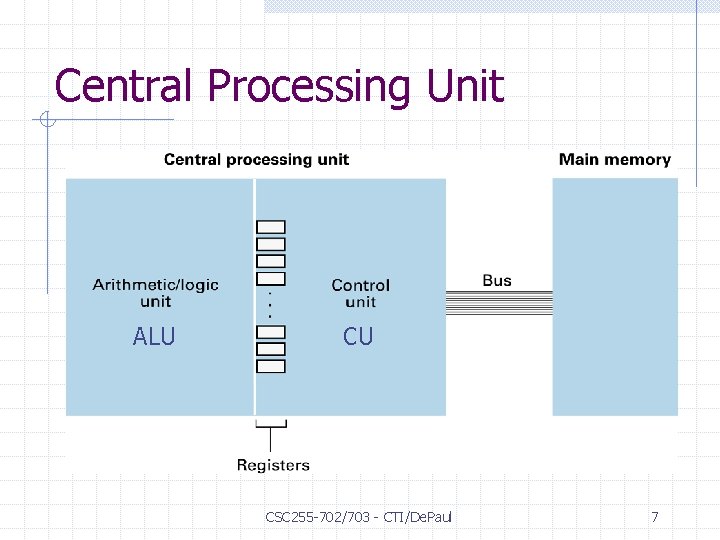

Central Processing Unit ALU CU CSC 255 -702/703 - CTI/De. Paul 7

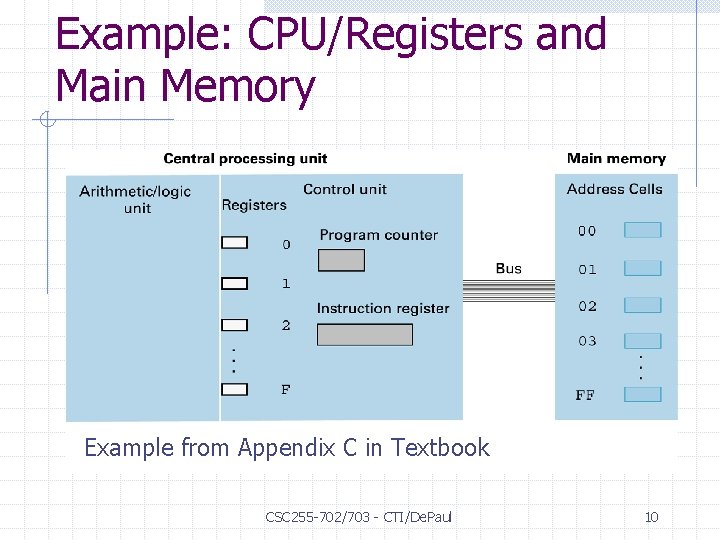

Registers Similar to memory cells, but with a lot faster access time n n Located as part of the CPU There is no bus transfer to access the register Usually limited number of registers n n CPU has a limited capacity for components, therefore cannot pack so many registers Usually 8, 16, or more (depending on the architecture) CSC 255 -702/703 - CTI/De. Paul 8

Registers… Temporary holding place for data being manipulated by the CPU and ALU operations In most architectures, ALU is not allowed to manipulate data directly in memory cells n Data in memory needs to be moved to a register first There are two types of registers: n n Special purpose (Program Counter -– PC, Instruction Register –- IR) General purpose (e. g. , R 0, R 1, R 2, …) CSC 255 -702/703 - CTI/De. Paul 9

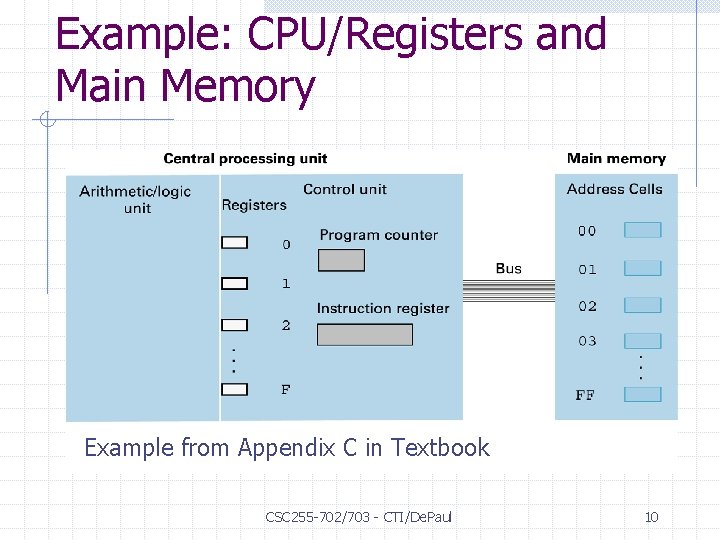

Example: CPU/Registers and Main Memory Example from Appendix C in Textbook CSC 255 -702/703 - CTI/De. Paul 10

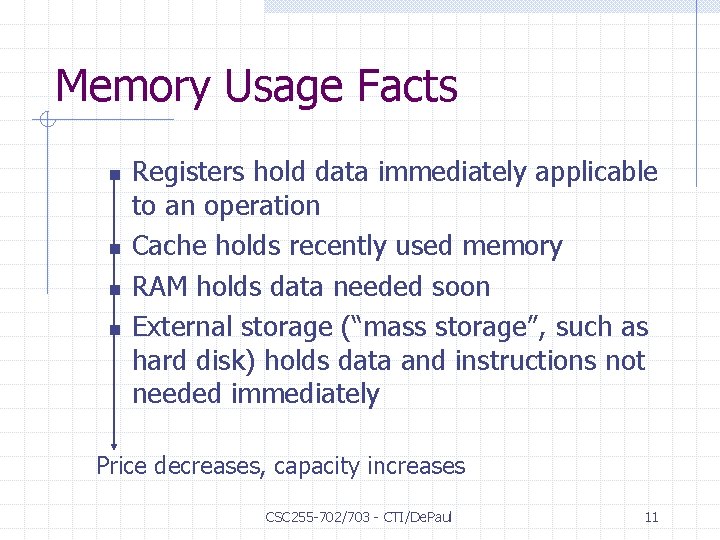

Memory Usage Facts n n Registers hold data immediately applicable to an operation Cache holds recently used memory RAM holds data needed soon External storage (“mass storage”, such as hard disk) holds data and instructions not needed immediately Price decreases, capacity increases CSC 255 -702/703 - CTI/De. Paul 11

Control Unit 1. Transfers data from memory to register 2. Tells ALU when and which register has data 3. Activates logic circuits in ALU 4. Tells ALU which register to put result in 5. Transfers data from register to memory (if asked) Speed is usually measured in MIPs (millions of instructions per second) CSC 255 -702/703 - CTI/De. Paul 12

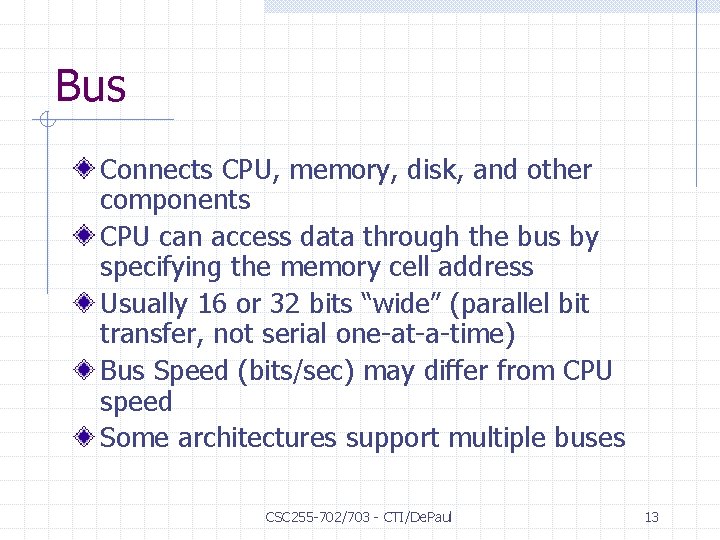

Bus Connects CPU, memory, disk, and other components CPU can access data through the bus by specifying the memory cell address Usually 16 or 32 bits “wide” (parallel bit transfer, not serial one-at-a-time) Bus Speed (bits/sec) may differ from CPU speed Some architectures support multiple buses CSC 255 -702/703 - CTI/De. Paul 13

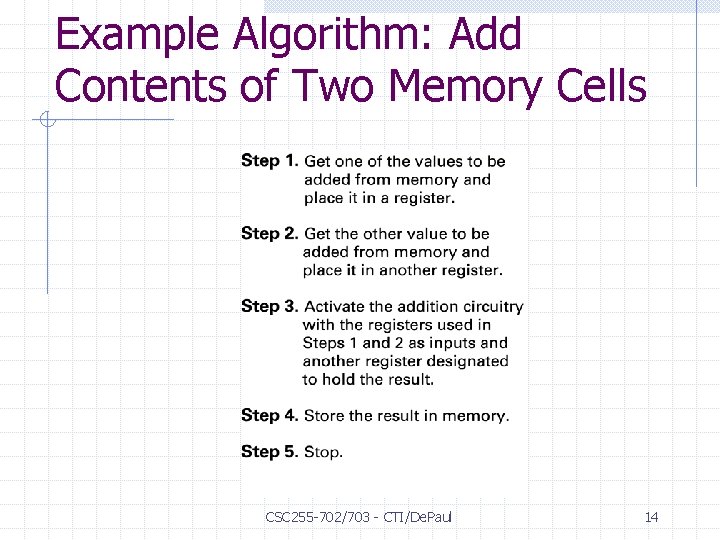

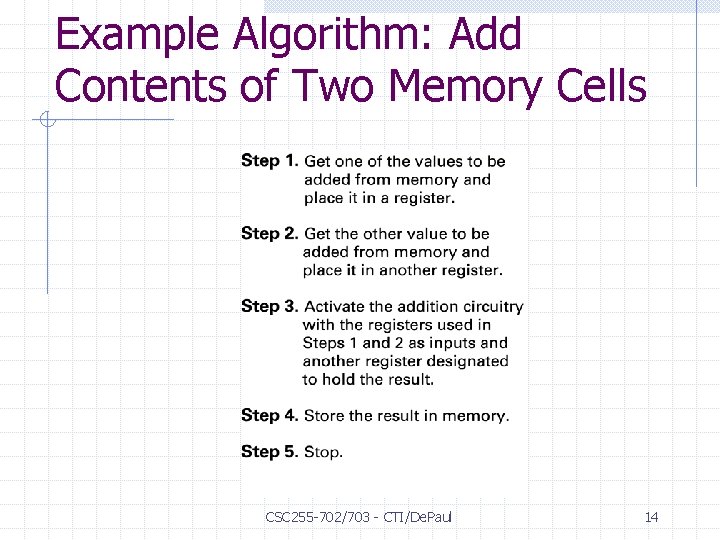

Example Algorithm: Add Contents of Two Memory Cells CSC 255 -702/703 - CTI/De. Paul 14

Machine Instruction Types Just a few instructions are sufficient for basic operations Three main categories: n n n Data transfer Arithmetic/Logic Control Each instruction type is represented by a bit pattern CSC 255 -702/703 - CTI/De. Paul 15

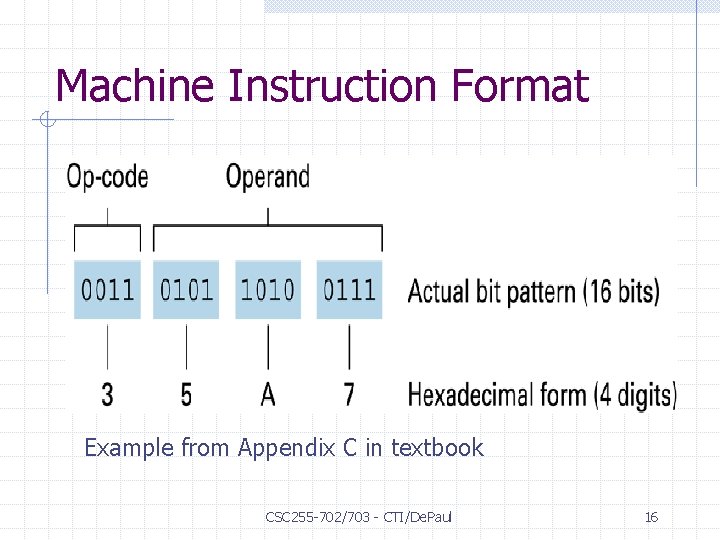

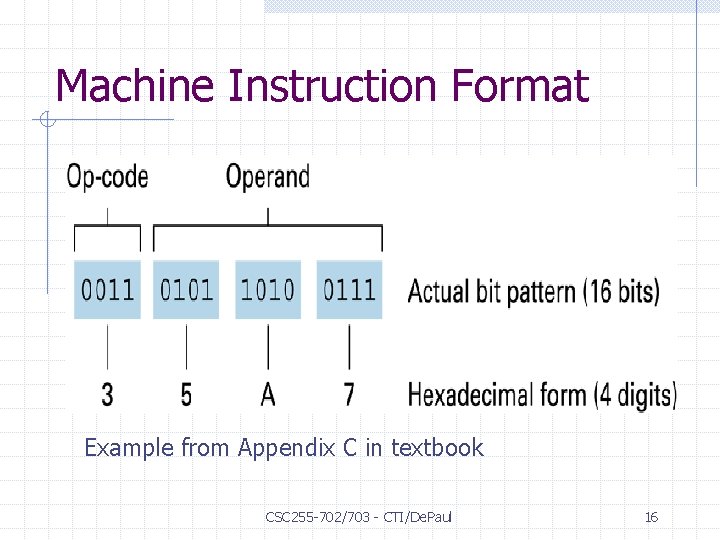

Machine Instruction Format Example from Appendix C in textbook CSC 255 -702/703 - CTI/De. Paul 16

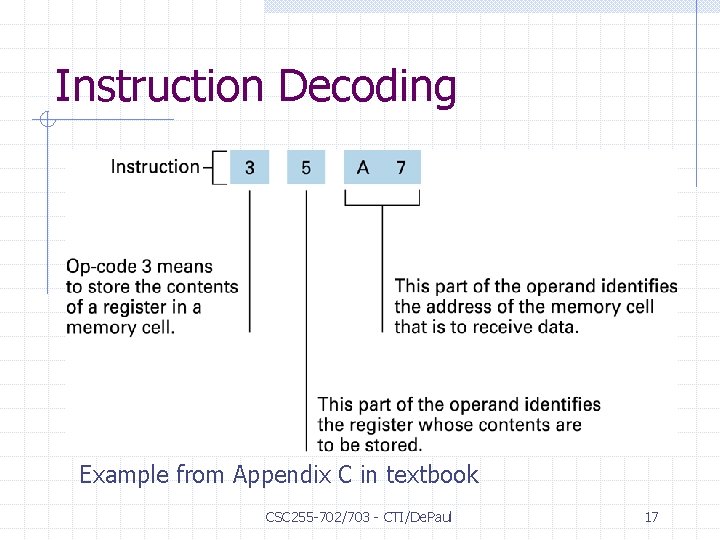

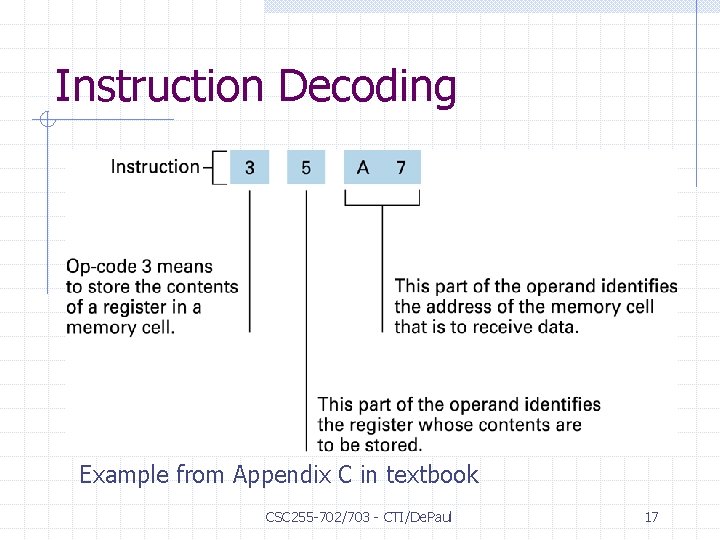

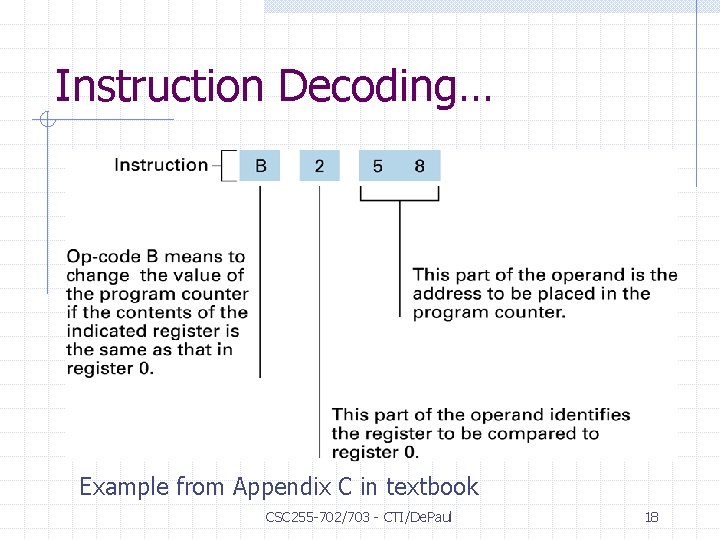

Instruction Decoding Example from Appendix C in textbook CSC 255 -702/703 - CTI/De. Paul 17

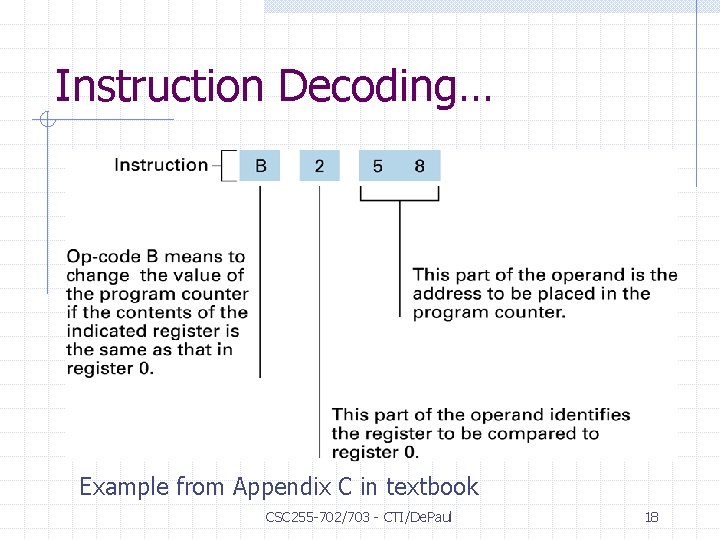

Instruction Decoding… Example from Appendix C in textbook CSC 255 -702/703 - CTI/De. Paul 18

Machine Architectures vs Instruction Set Reduced Instruction Set Computer (RISC) n n Relatively few basic instructions only Complex instructions have to be implemented by using basic instructions Complex Instruction Set Computer (CISC) n n Large number of instructions Instructions provided for complex tasks as well as simple tasks Both used in practice n n RISC: Motorola/IBM Power. PC, Sun SPARC CISC: Intel CSC 255 -702/703 - CTI/De. Paul 19

Data Transfer Instructions associated with the transfer of data, such as: n LOAD register, address w Copy bit pattern from memory cell (specified by address) to register n STORE register, address w Copy bit pattern from register to memory cell (specified by address) n MOVE register 1, register 2 w Copy bit pattern from register 1 to register 2 CSC 255 -702/703 - CTI/De. Paul 20

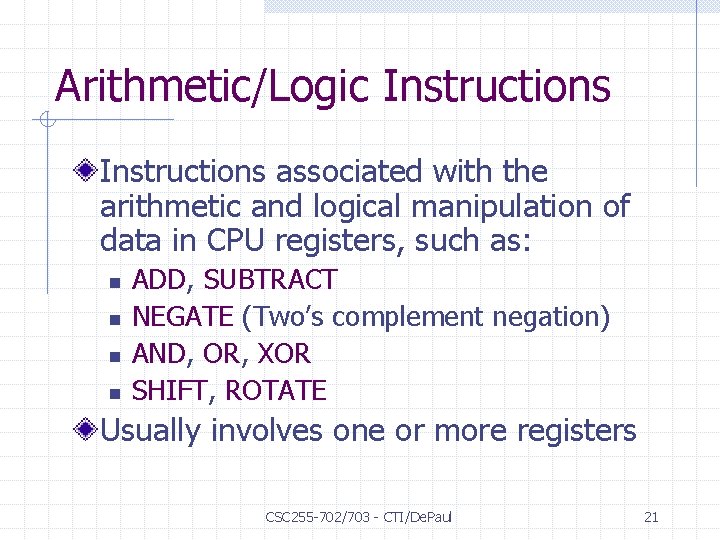

Arithmetic/Logic Instructions associated with the arithmetic and logical manipulation of data in CPU registers, such as: n n ADD, SUBTRACT NEGATE (Two’s complement negation) AND, OR, XOR SHIFT, ROTATE Usually involves one or more registers CSC 255 -702/703 - CTI/De. Paul 21

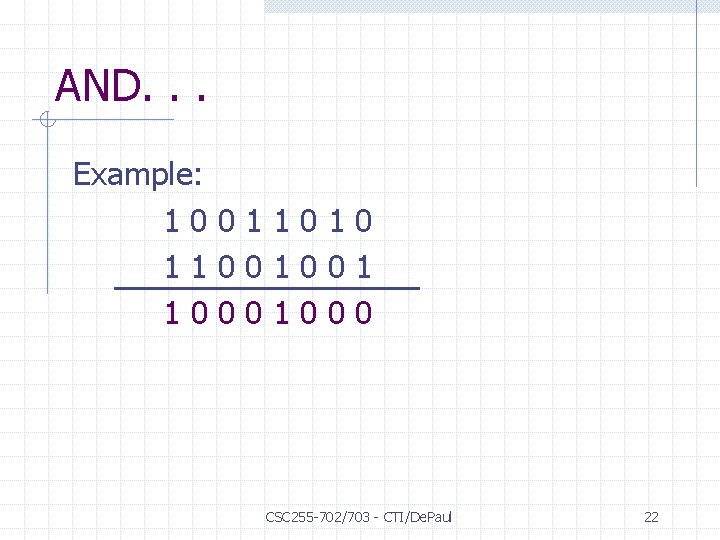

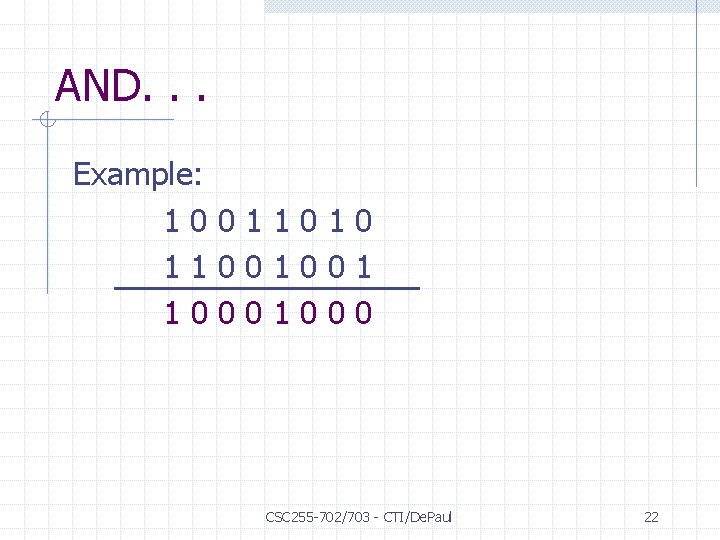

AND. . . Example: 10011010 11001001 1000 CSC 255 -702/703 - CTI/De. Paul 22

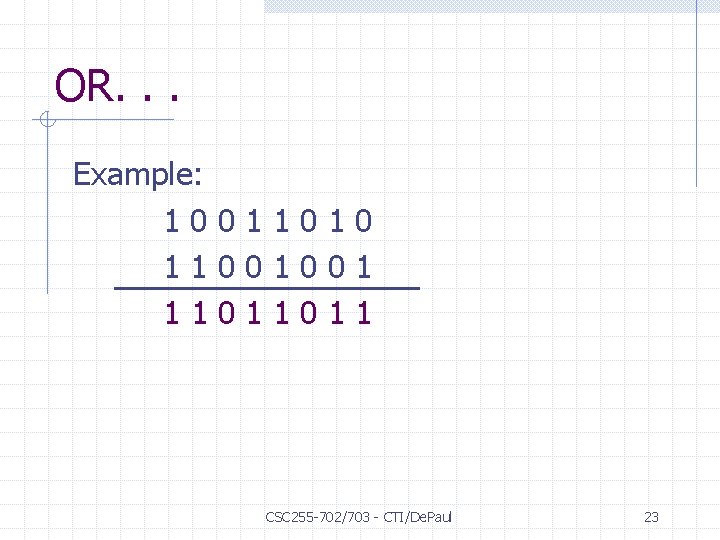

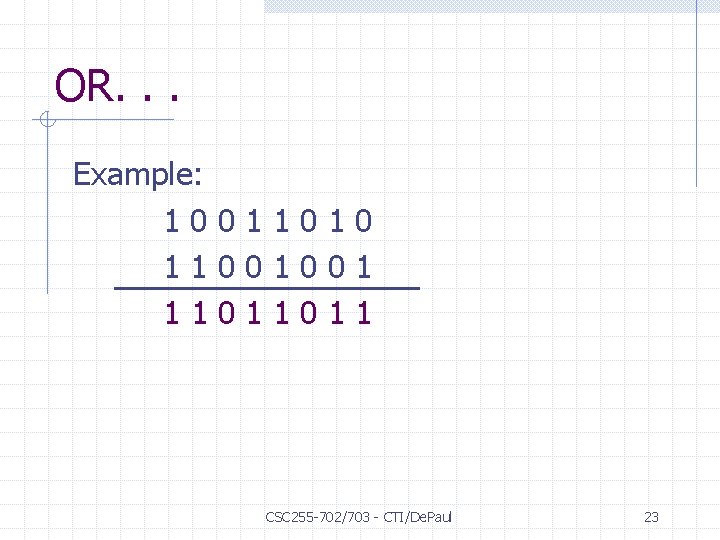

OR. . . Example: 10011010 11001001 11011011 CSC 255 -702/703 - CTI/De. Paul 23

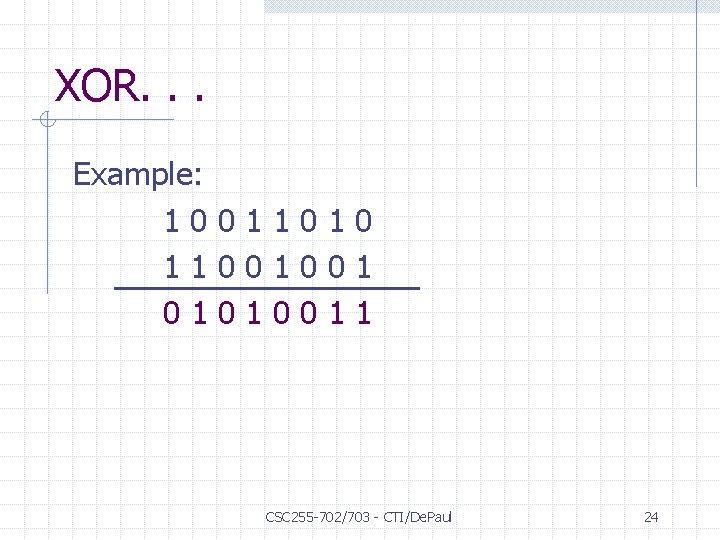

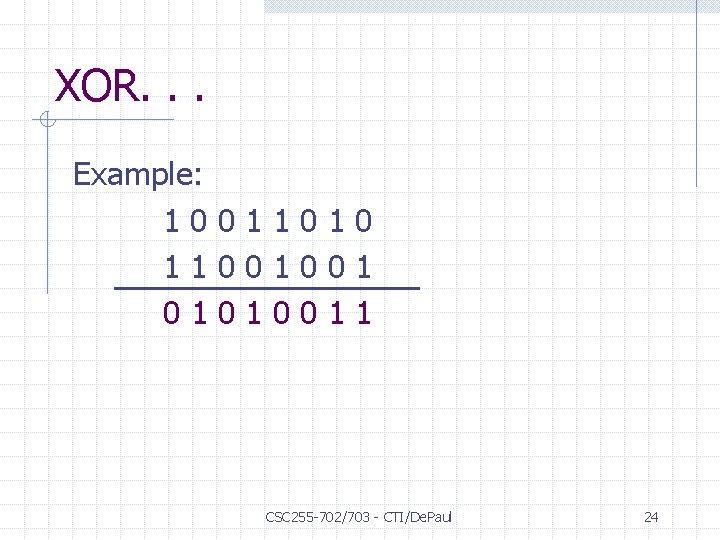

XOR. . . Example: 10011010 11001001 01010011 CSC 255 -702/703 - CTI/De. Paul 24

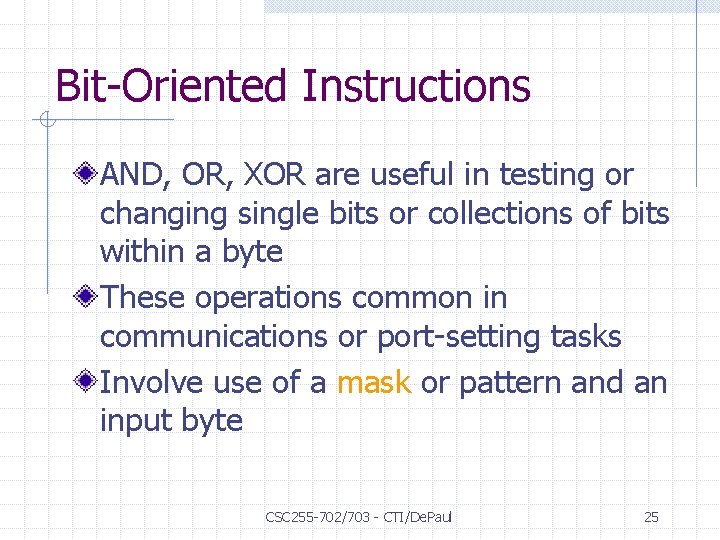

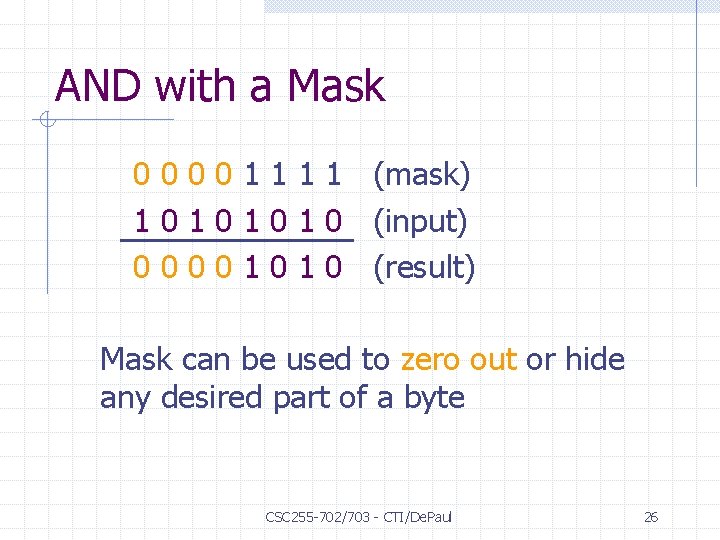

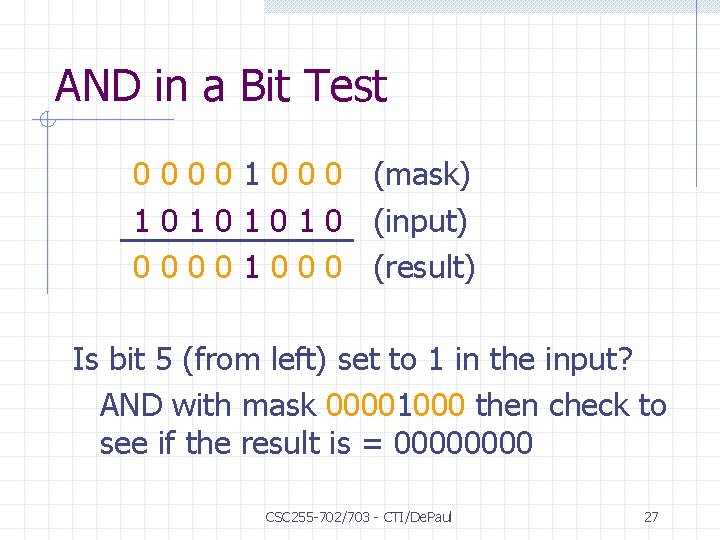

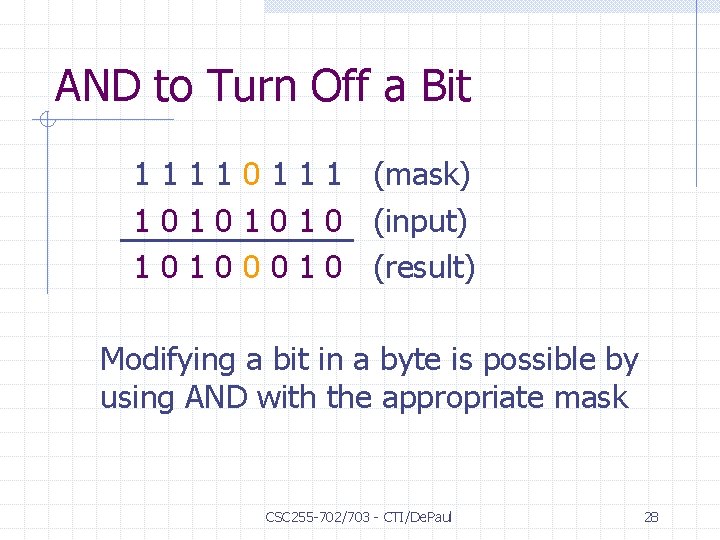

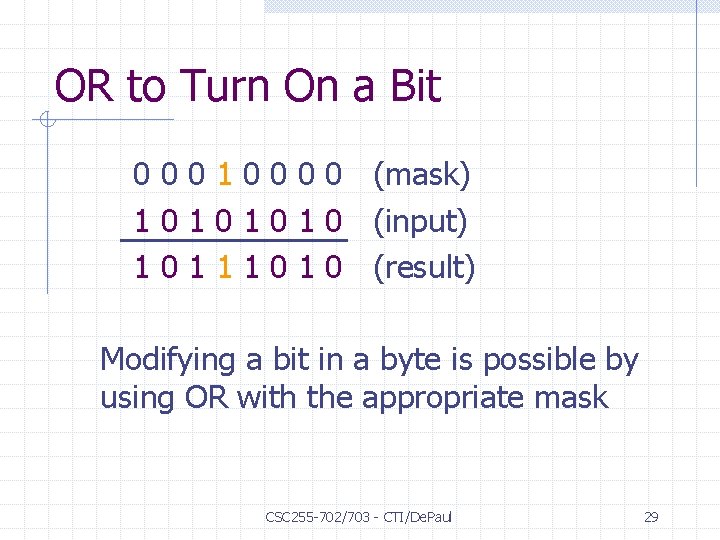

Bit-Oriented Instructions AND, OR, XOR are useful in testing or changing single bits or collections of bits within a byte These operations common in communications or port-setting tasks Involve use of a mask or pattern and an input byte CSC 255 -702/703 - CTI/De. Paul 25

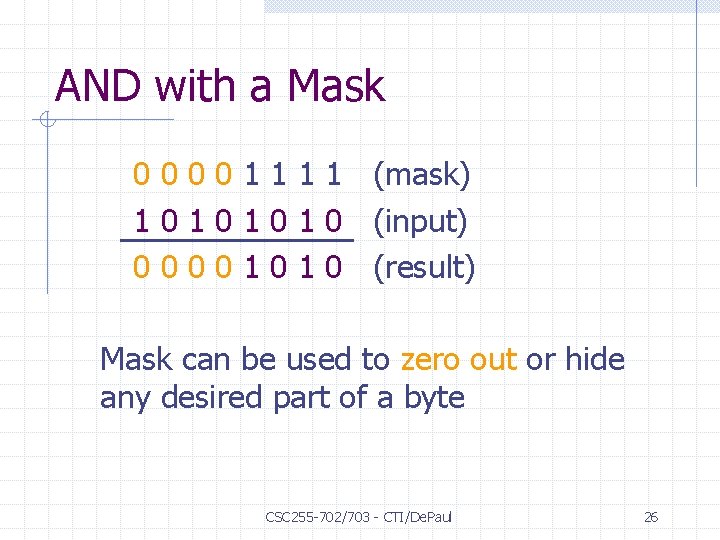

AND with a Mask 0 0 1 1 (mask) 1 0 1 0 (input) 0 0 1 0 (result) Mask can be used to zero out or hide any desired part of a byte CSC 255 -702/703 - CTI/De. Paul 26

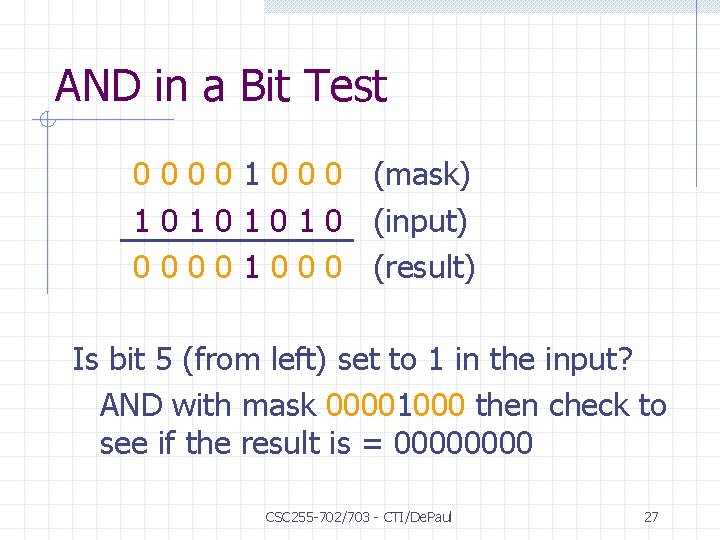

AND in a Bit Test 0 0 1 0 0 0 (mask) 1 0 1 0 (input) 0 0 1 0 0 0 (result) Is bit 5 (from left) set to 1 in the input? AND with mask 00001000 then check to see if the result is = 0000 CSC 255 -702/703 - CTI/De. Paul 27

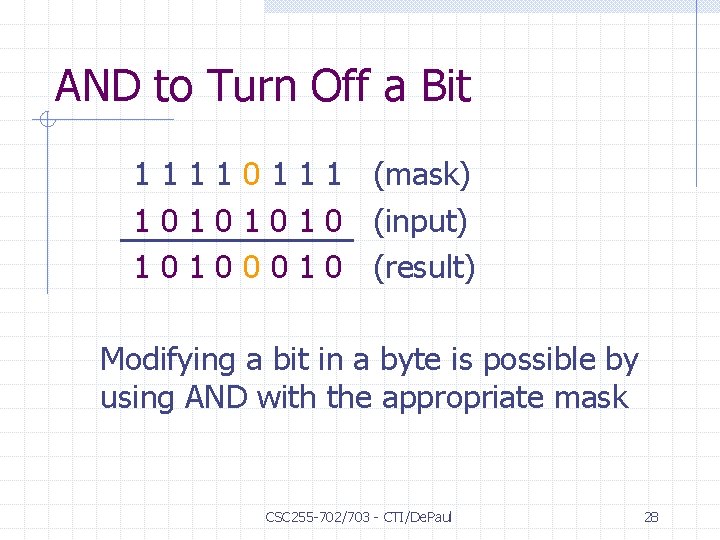

AND to Turn Off a Bit 1 1 0 1 1 1 (mask) 1 0 1 0 (input) 1 0 0 0 1 0 (result) Modifying a bit in a byte is possible by using AND with the appropriate mask CSC 255 -702/703 - CTI/De. Paul 28

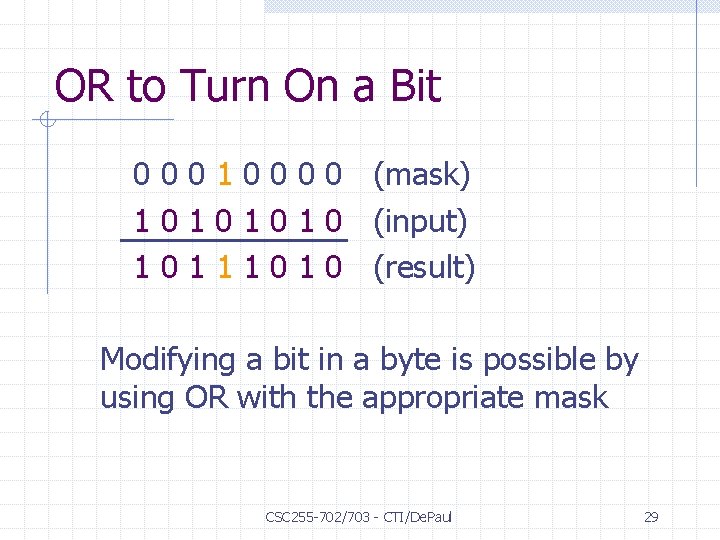

OR to Turn On a Bit 0 0 0 1 0 0 (mask) 1 0 1 0 (input) 1 0 1 1 1 0 (result) Modifying a bit in a byte is possible by using OR with the appropriate mask CSC 255 -702/703 - CTI/De. Paul 29

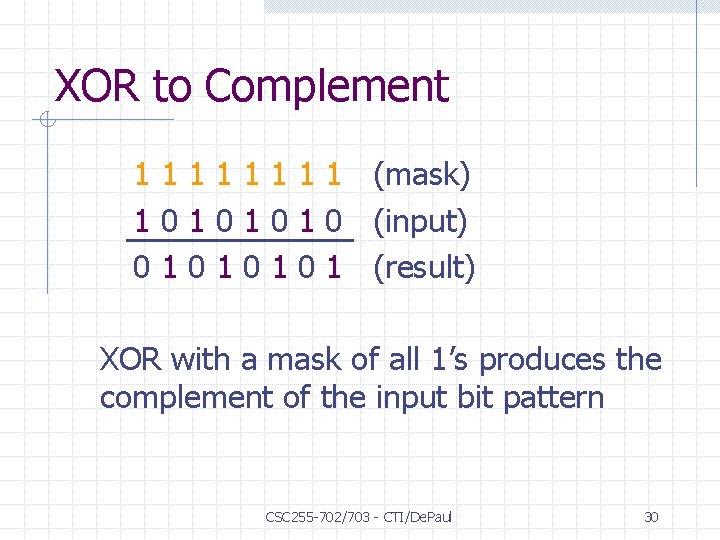

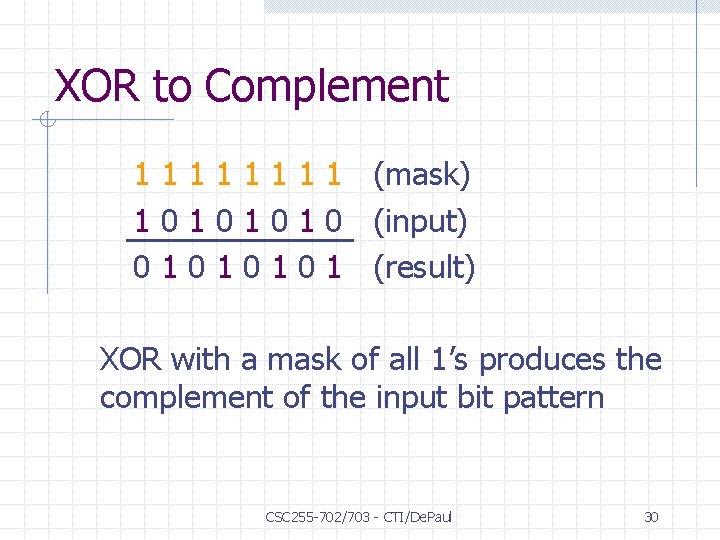

XOR to Complement 1 1 1 1 (mask) 1 0 1 0 (input) 0 1 0 1 (result) XOR with a mask of all 1’s produces the complement of the input bit pattern CSC 255 -702/703 - CTI/De. Paul 30

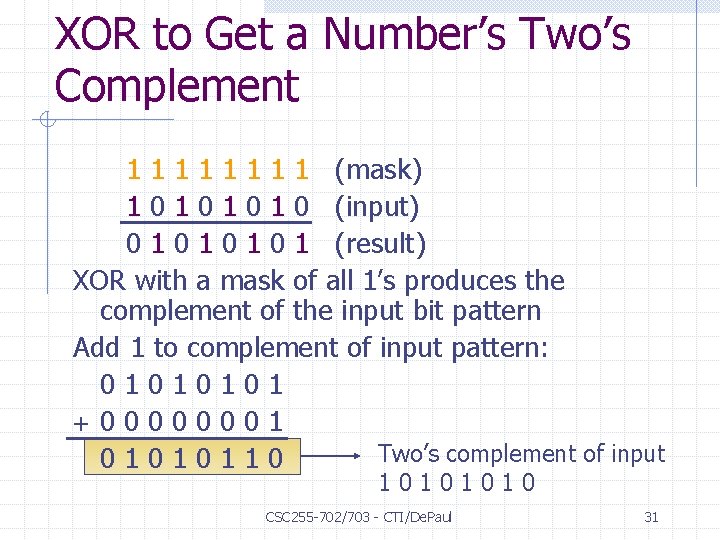

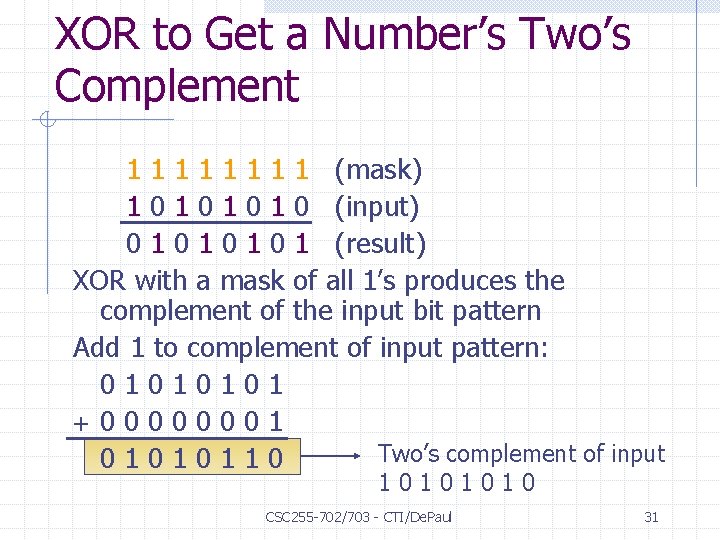

XOR to Get a Number’s Two’s Complement 1 1 1 1 (mask) 1 0 1 0 (input) 0 1 0 1 (result) XOR with a mask of all 1’s produces the complement of the input bit pattern Add 1 to complement of input pattern: 0101 + 00000001 Two’s complement of input 01010110 1010 CSC 255 -702/703 - CTI/De. Paul 31

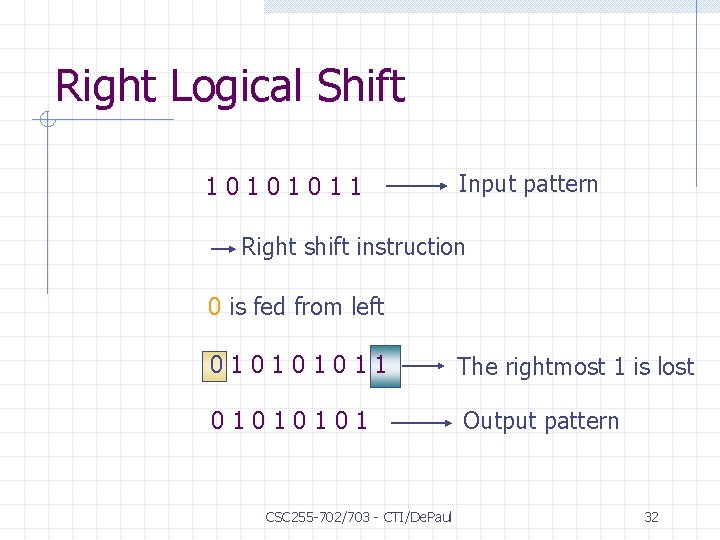

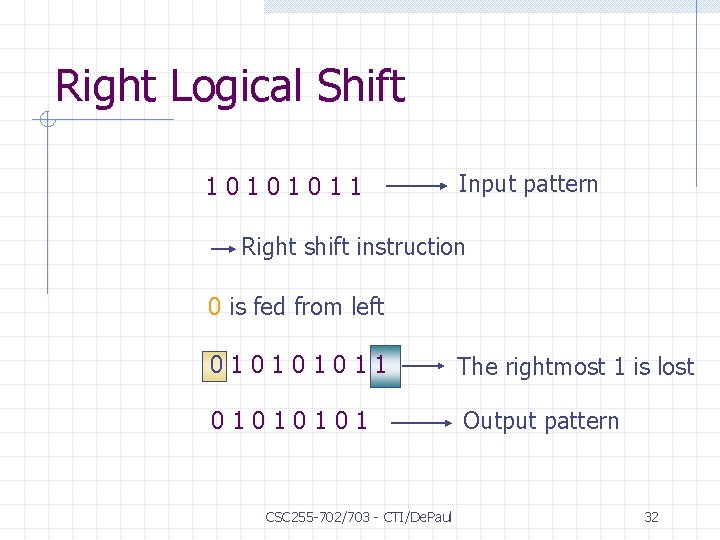

Right Logical Shift 10101011 Input pattern Right shift instruction 0 is fed from left 01011 The rightmost 1 is lost 0101 Output pattern CSC 255 -702/703 - CTI/De. Paul 32

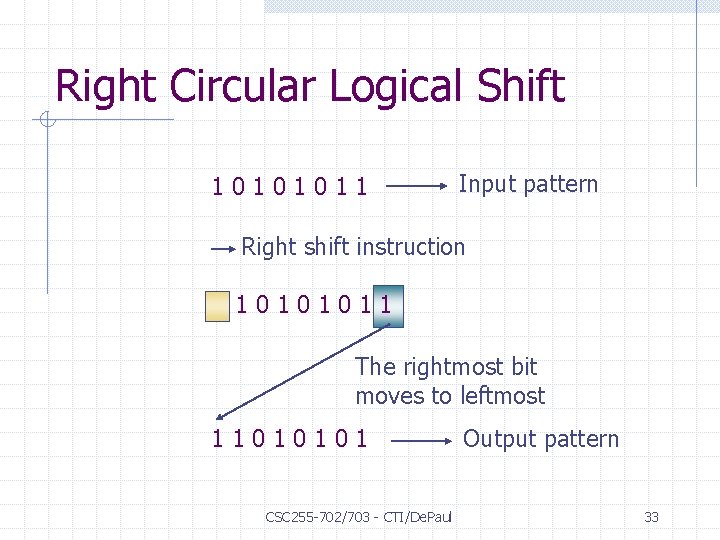

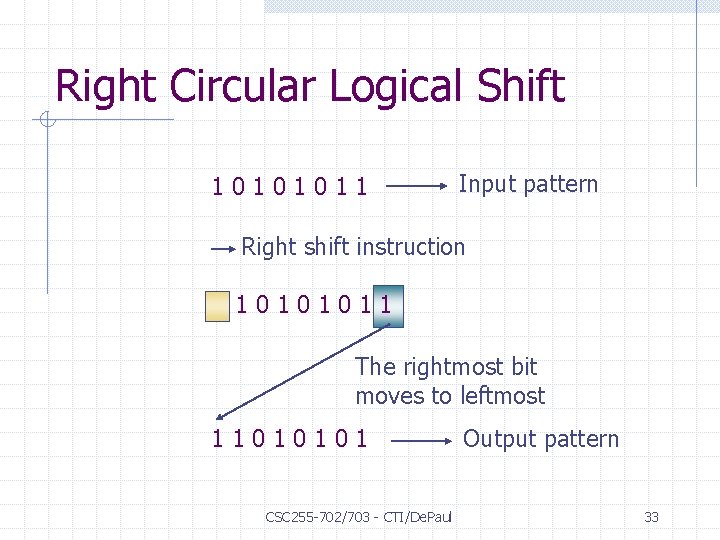

Right Circular Logical Shift 10101011 Input pattern Right shift instruction 10101011 The rightmost bit moves to leftmost 11010101 CSC 255 -702/703 - CTI/De. Paul Output pattern 33

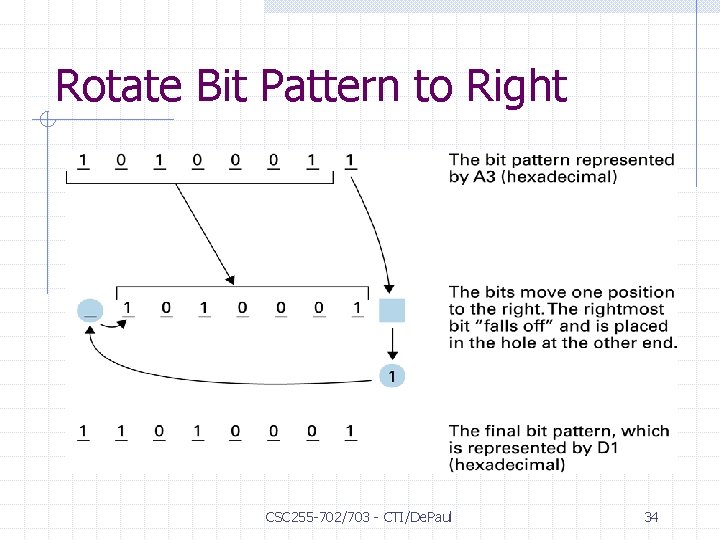

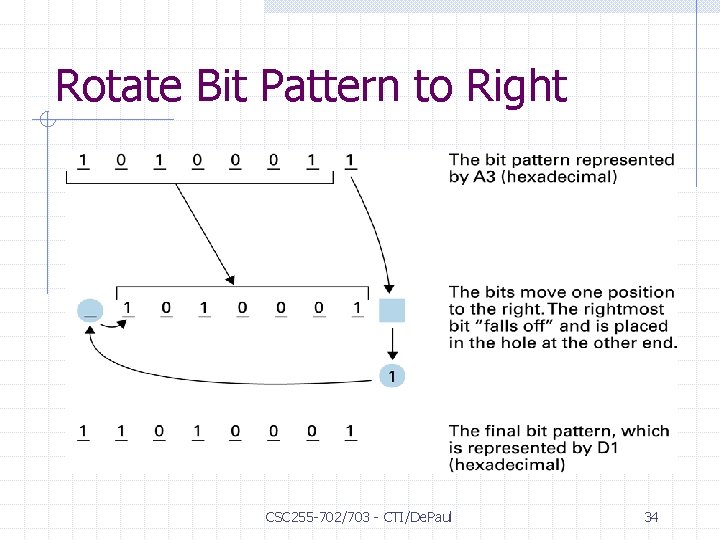

Rotate Bit Pattern to Right CSC 255 -702/703 - CTI/De. Paul 34

Shift Definitions Circular shifts are also called rotations Two types of shifts: left and right Logical shifts lose bits at end moved to Circular shifts circulate bits to front Arithmetic shifts preserve sign bit (don’t involve it in shifts), the most significant bit CSC 255 -702/703 - CTI/De. Paul 35

Control Instructions associated with program flow control, such as: n n n GO address JUMP address SKIP address GOIF - “GO IF (condition)” address STOP, HALT, QUIT CSC 255 -702/703 - CTI/De. Paul 36

Stored-Program Concept Von-Neumann machine Program is in memory cells like data Control unit extracts instructions from memory, decodes, executes Machine language is in bit patterns Chapter 2 and Appendix C in textbook describe a simulator CSC 255 -702/703 - CTI/De. Paul 37

Programs vs. Data There is no difference in appearance between programs and data n n Both are stored as 0’s and 1’s Both are housed in memory Who keeps track of what is what? n Answer: you (the programmer) must CSC 255 -702/703 - CTI/De. Paul 38

Program Execution Control Unit handles it Program Counter contains memory cell address of next instruction Instruction Register contains the current instruction (the instruction now being executed) CSC 255 -702/703 - CTI/De. Paul 39

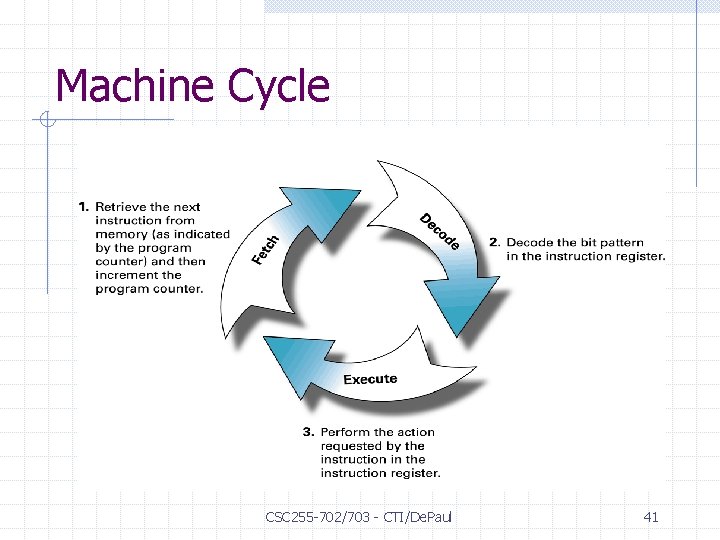

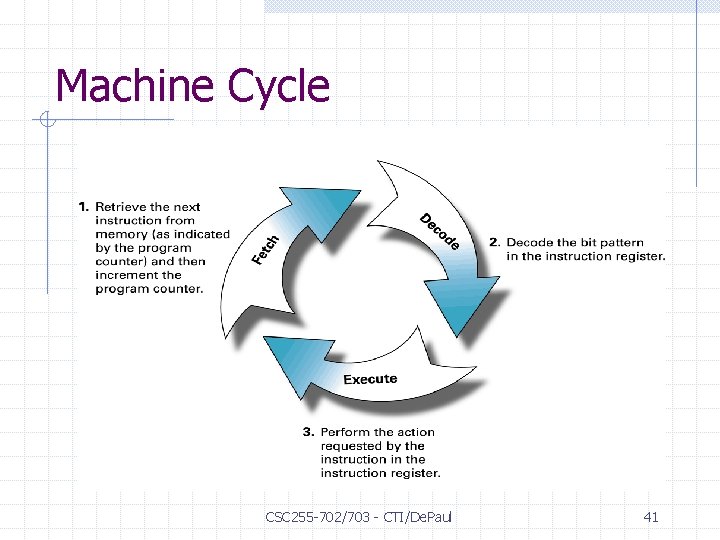

Machine Cycle Fetch n n Bring next instruction from memory to CU Increment the program counter (depending on how many bytes the instruction has) Decode n Interpret instruction in instruction register Execute n Activate appropriate circuitry for instruction CSC 255 -702/703 - CTI/De. Paul 40

Machine Cycle CSC 255 -702/703 - CTI/De. Paul 41

Machine Cycle Timing Controlled by an oscillator called “clock” Clock ticks at a very fast rate (such as 1. 8 GHz) Circuits in CU that actually Fetch, Decode, Execute are triggered by clock Each instruction execution might take one or more clock cycles to complete n Depends on how complicated the instruction is CSC 255 -702/703 - CTI/De. Paul 42

General Program Startup Program counter is initialized to 0 (points to first memory cell as place to get next instruction) Fetch brings instruction in cell 0 (the one that is currently referenced by the program Counter) to instruction register in CU Program execution starts and continues until a termination instruction (such as halt) is reached CSC 255 -702/703 - CTI/De. Paul 43

How to Handle Jump (Branch/Go/Skip) Instruction? Branching instruction is interesting n Basic form: jmp address All it does is put the address contained in the instruction into the Program Counter On next machine cycle, Fetch gets the instruction in the cell that the Program Counter points to CSC 255 -702/703 - CTI/De. Paul 44

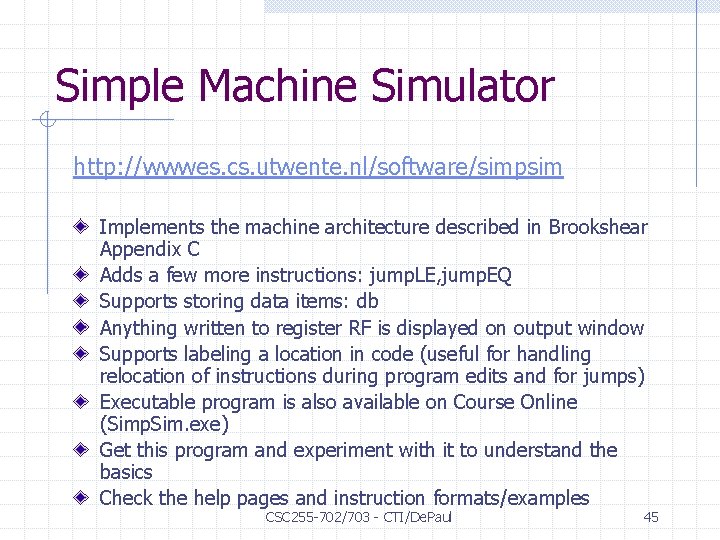

Simple Machine Simulator http: //wwwes. cs. utwente. nl/software/simpsim Implements the machine architecture described in Brookshear Appendix C Adds a few more instructions: jump. LE, jump. EQ Supports storing data items: db Anything written to register RF is displayed on output window Supports labeling a location in code (useful for handling relocation of instructions during program edits and for jumps) Executable program is also available on Course Online (Simp. Sim. exe) Get this program and experiment with it to understand the basics Check the help pages and instruction formats/examples CSC 255 -702/703 - CTI/De. Paul 45

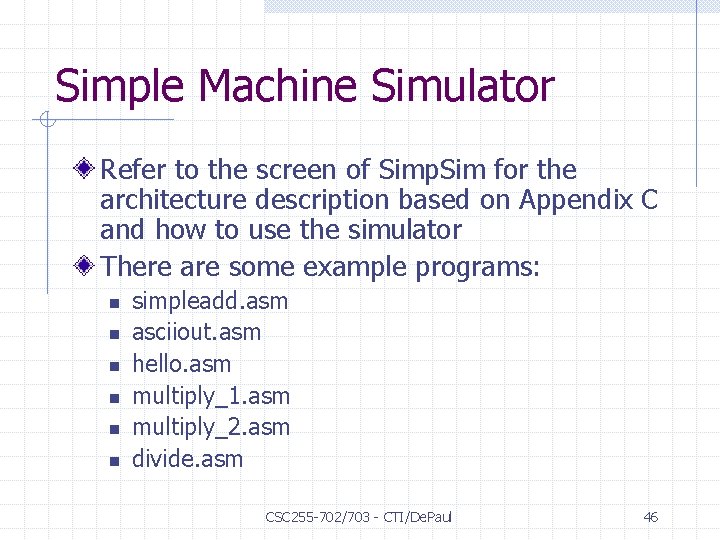

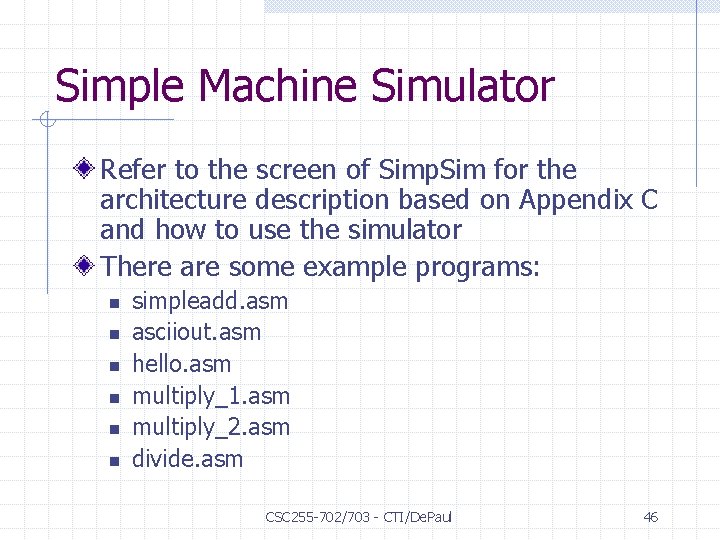

Simple Machine Simulator Refer to the screen of Simp. Sim for the architecture description based on Appendix C and how to use the simulator There are some example programs: n n n simpleadd. asm asciiout. asm hello. asm multiply_1. asm multiply_2. asm divide. asm CSC 255 -702/703 - CTI/De. Paul 46

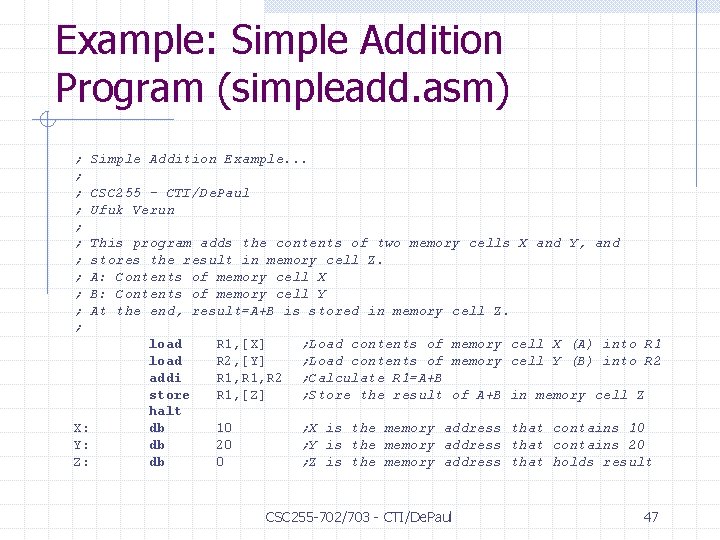

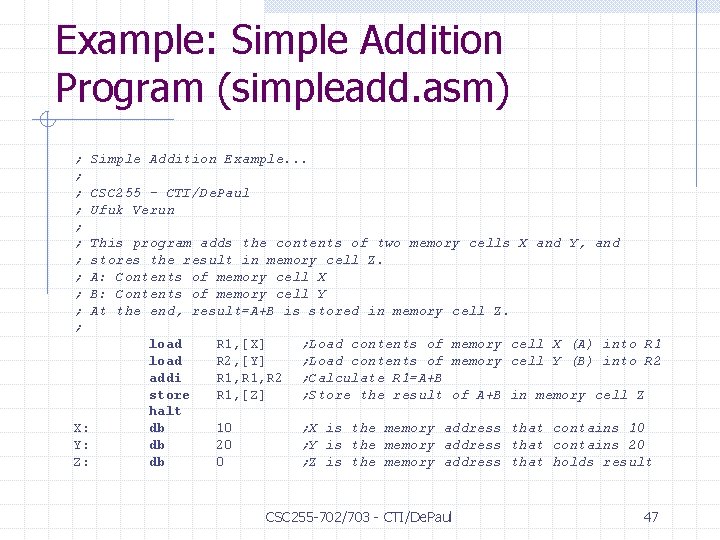

Example: Simple Addition Program (simpleadd. asm) ; ; ; Simple Addition Example. . . CSC 255 - CTI/De. Paul Ufuk Verun This program adds the contents of two memory cells X and Y, and stores the result in memory cell Z. A: Contents of memory cell X B: Contents of memory cell Y At the end, result=A+B is stored in memory cell Z. X: Y: Z: load addi store halt db db db R 1, [X] R 2, [Y] R 1, R 2 R 1, [Z] ; Load contents of memory cell X (A) into R 1 ; Load contents of memory cell Y (B) into R 2 ; Calculate R 1=A+B ; Store the result of A+B in memory cell Z 10 20 0 ; X is the memory address that contains 10 ; Y is the memory address that contains 20 ; Z is the memory address that holds result CSC 255 -702/703 - CTI/De. Paul 47

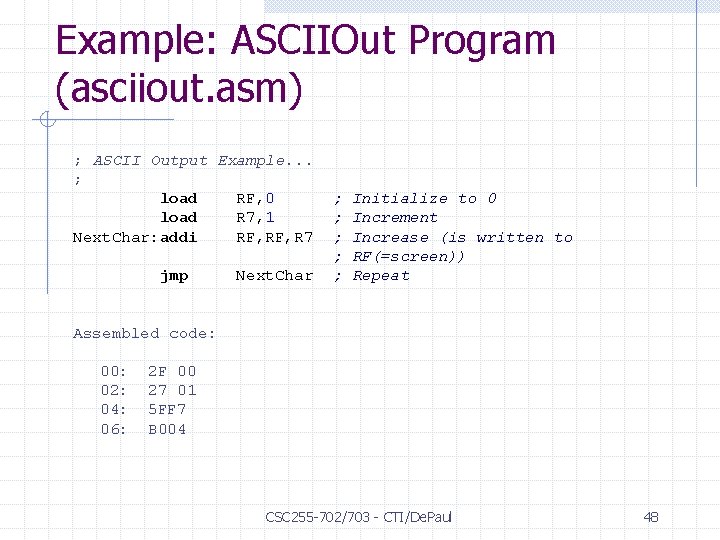

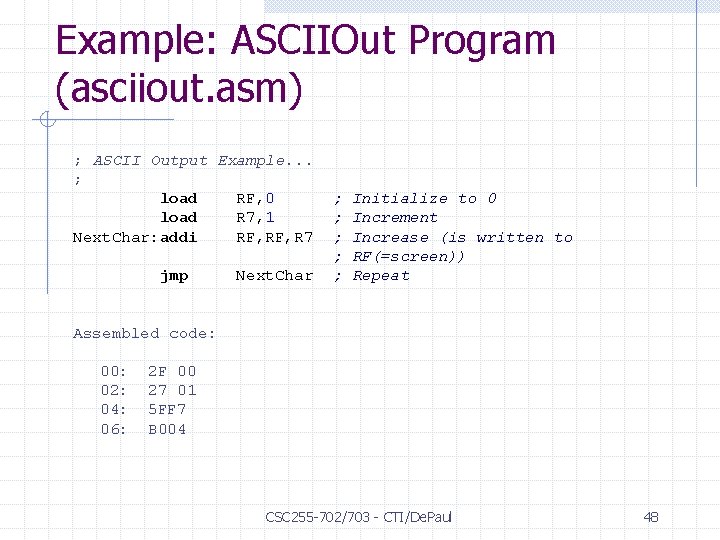

Example: ASCIIOut Program (asciiout. asm) ; ASCII Output Example. . . ; load RF, 0 load R 7, 1 Next. Char: addi RF, R 7 jmp Next. Char ; ; ; Initialize to 0 Increment Increase (is written to RF(=screen)) Repeat Assembled code: 00: 02: 04: 06: 2 F 00 27 01 5 FF 7 B 004 CSC 255 -702/703 - CTI/De. Paul 48

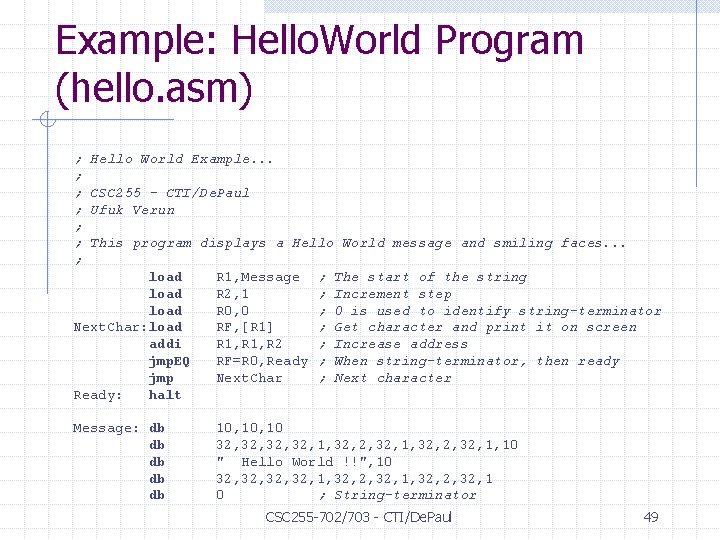

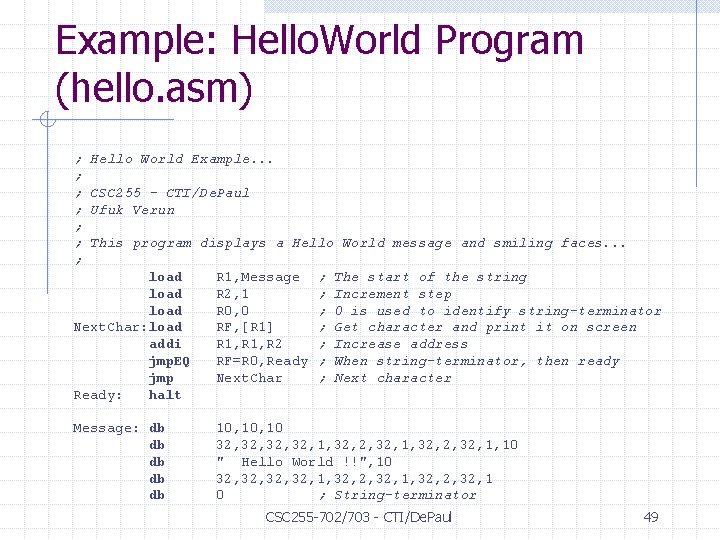

Example: Hello. World Program (hello. asm) ; ; ; ; Hello World Example. . . CSC 255 - CTI/De. Paul Ufuk Verun This program displays a Hello World message and smiling faces. . . load Next. Char: load addi jmp. EQ jmp Ready: halt R 1, Message R 2, 1 R 0, 0 RF, [R 1] R 1, R 2 RF=R 0, Ready Next. Char ; ; ; ; The start of the string Increment step 0 is used to identify string-terminator Get character and print it on screen Increase address When string-terminator, then ready Next character Message: db db db 10, 10 32, 32, 1, 32, 2, 32, 1, 10 " Hello World !!", 10 32, 32, 1, 32, 2, 32, 1 0 ; String-terminator CSC 255 -702/703 - CTI/De. Paul 49

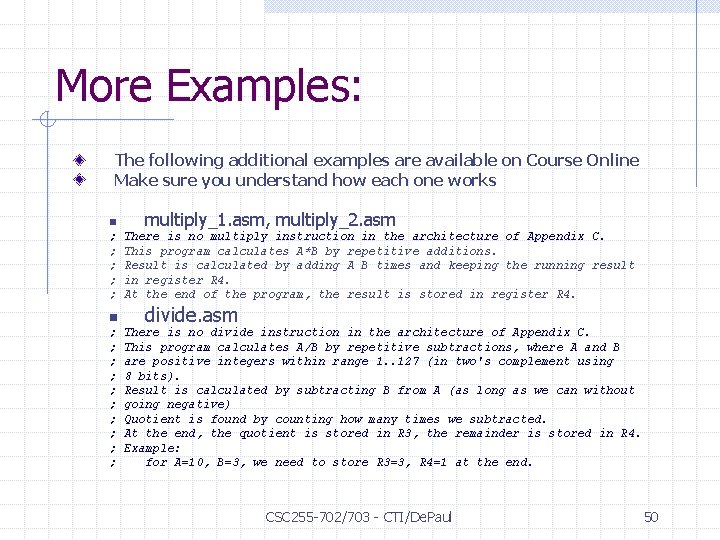

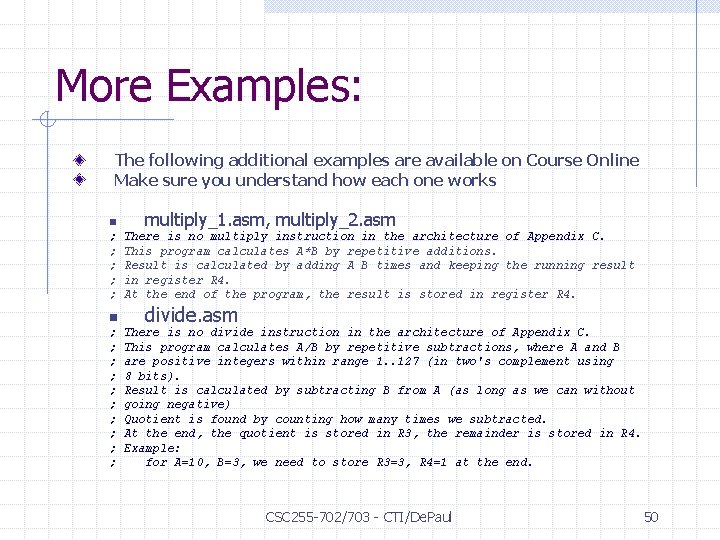

More Examples: The following additional examples are available on Course Online Make sure you understand how each one works n ; ; ; ; multiply_1. asm, multiply_2. asm There is no multiply instruction in the architecture of Appendix C. This program calculates A*B by repetitive additions. Result is calculated by adding A B times and keeping the running result in register R 4. At the end of the program, the result is stored in register R 4. divide. asm There is no divide instruction in the architecture of Appendix C. This program calculates A/B by repetitive subtractions, where A and B are positive integers within range 1. . 127 (in two's complement using 8 bits). Result is calculated by subtracting B from A (as long as we can without going negative) Quotient is found by counting how many times we subtracted. At the end, the quotient is stored in R 3, the remainder is stored in R 4. Example: for A=10, B=3, we need to store R 3=3, R 4=1 at the end. CSC 255 -702/703 - CTI/De. Paul 50

Multiple Programs in Memory Several programs can be in memory at the same time Running a program just means setting the Program Counter to point to the cell with the program’s first instruction The operating system (for example Windows XP) manages memory management and processing of programs CSC 255 -702/703 - CTI/De. Paul 51