CS447 Computer Architecture Lecture 17 Review October 20

CS-447– Computer Architecture Lecture 17 Review October 20, 2008 www. qatar. cmu. edu/~msakr/15447 -f 08/ 15 -447 Computer Architecture Fall 2008 ©

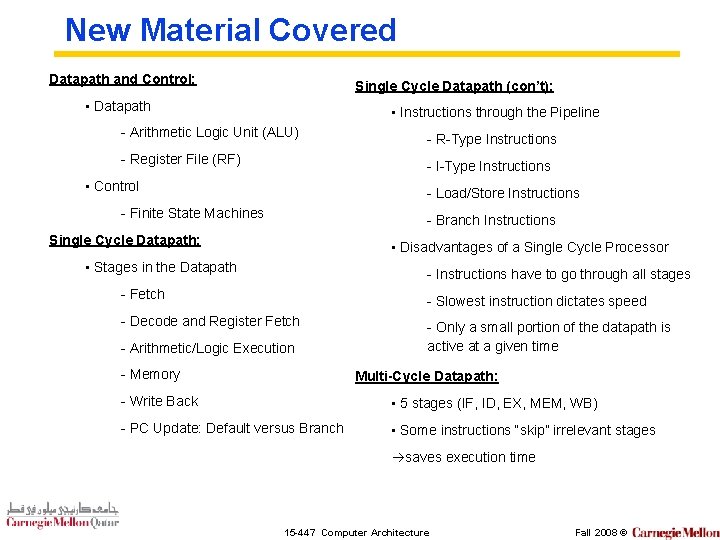

New Material Covered Datapath and Control: Single Cycle Datapath (con’t): • Datapath • Instructions through the Pipeline - Arithmetic Logic Unit (ALU) - R-Type Instructions - Register File (RF) - I-Type Instructions • Control - Load/Store Instructions - Finite State Machines - Branch Instructions Single Cycle Datapath: • Disadvantages of a Single Cycle Processor • Stages in the Datapath - Instructions have to go through all stages - Fetch - Slowest instruction dictates speed - Decode and Register Fetch - Only a small portion of the datapath is active at a given time - Arithmetic/Logic Execution - Memory Multi-Cycle Datapath: - Write Back • 5 stages (IF, ID, EX, MEM, WB) - PC Update: Default versus Branch • Some instructions “skip” irrelevant stages àsaves execution time 15 -447 Computer Architecture Fall 2008 ©

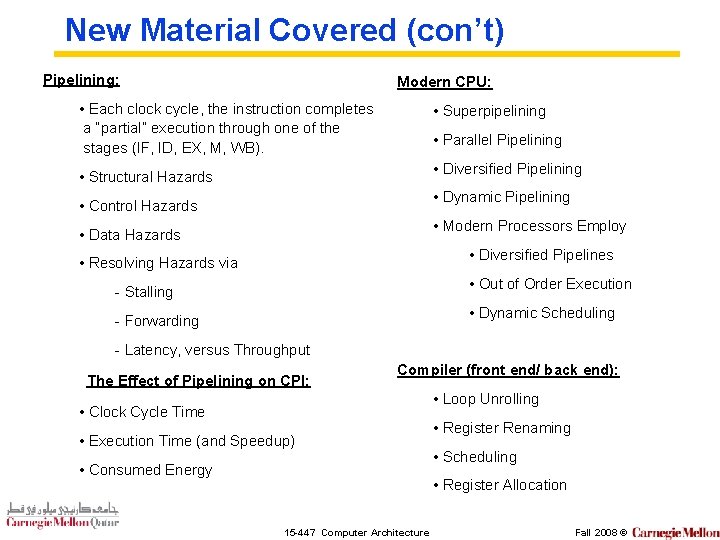

New Material Covered (con’t) Pipelining: Modern CPU: • Each clock cycle, the instruction completes a “partial” execution through one of the stages (IF, ID, EX, M, WB). • Superpipelining • Parallel Pipelining • Diversified Pipelining • Structural Hazards • Dynamic Pipelining • Control Hazards • Modern Processors Employ • Data Hazards • Diversified Pipelines • Resolving Hazards via • Out of Order Execution - Stalling • Dynamic Scheduling - Forwarding - Latency, versus Throughput The Effect of Pipelining on CPI: Compiler (front end/ back end): • Loop Unrolling • Clock Cycle Time • Execution Time (and Speedup) • Consumed Energy • Register Renaming • Scheduling • Register Allocation 15 -447 Computer Architecture Fall 2008 ©

- Slides: 3