CS 61 C Great Ideas in Computer Architecture

![Haswell Front-End [Kanter] Fall 2012 -- Lecture #38 9 Haswell Front-End [Kanter] Fall 2012 -- Lecture #38 9](https://slidetodoc.com/presentation_image_h2/c9145d2e18c852a57e8a161fff3d5c76/image-9.jpg)

![Haswell Rename/Reorder [Kanter] Fall 2012 -- Lecture #38 10 Haswell Rename/Reorder [Kanter] Fall 2012 -- Lecture #38 10](https://slidetodoc.com/presentation_image_h2/c9145d2e18c852a57e8a161fff3d5c76/image-10.jpg)

![Haswell Execution [Kanter] ALU Memory Fall 2012 -- Lecture #38 11 Haswell Execution [Kanter] ALU Memory Fall 2012 -- Lecture #38 11](https://slidetodoc.com/presentation_image_h2/c9145d2e18c852a57e8a161fff3d5c76/image-11.jpg)

![Apple A 6 and A 6 X (32 nm) [Chipworks. com, 2012] Fall 2012 Apple A 6 and A 6 X (32 nm) [Chipworks. com, 2012] Fall 2012](https://slidetodoc.com/presentation_image_h2/c9145d2e18c852a57e8a161fff3d5c76/image-26.jpg)

![Apple A 6 X [chipworks. com] In i. Pad 4 76. 8 GFLOPS Peak! Apple A 6 X [chipworks. com] In i. Pad 4 76. 8 GFLOPS Peak!](https://slidetodoc.com/presentation_image_h2/c9145d2e18c852a57e8a161fff3d5c76/image-27.jpg)

- Slides: 28

CS 61 C: Great Ideas in Computer Architecture Case Studies: Server and Cellphone microprocessors Instructors: Krste Asanovic, Randy H. Katz http: //inst. eecs. Berkeley. edu/~cs 61 c/fa 12 Fall 2012 -- Lecture #38 1

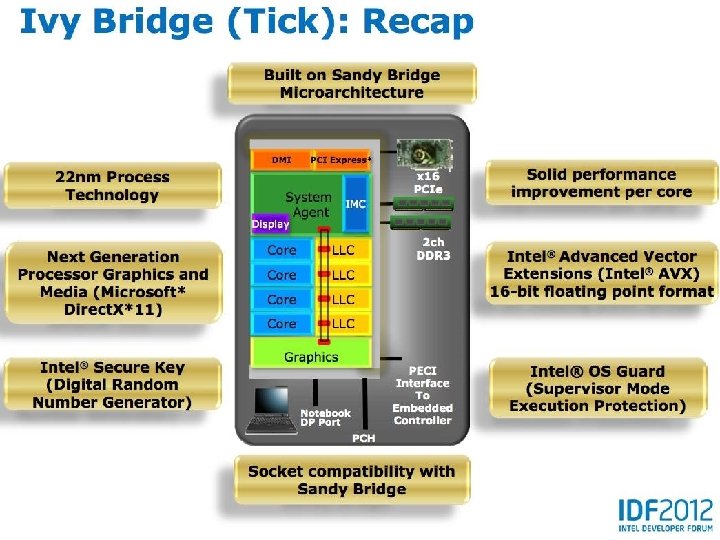

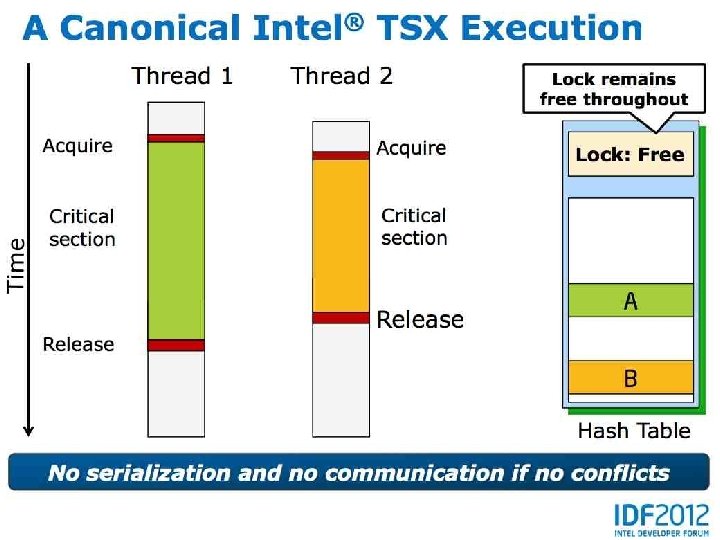

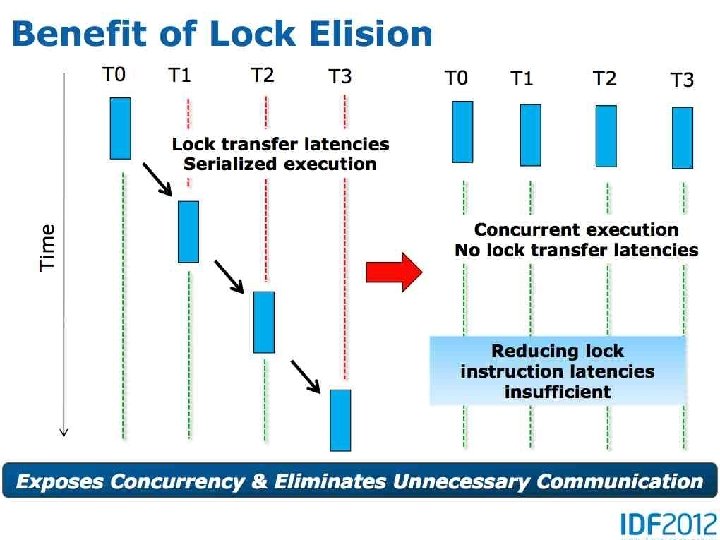

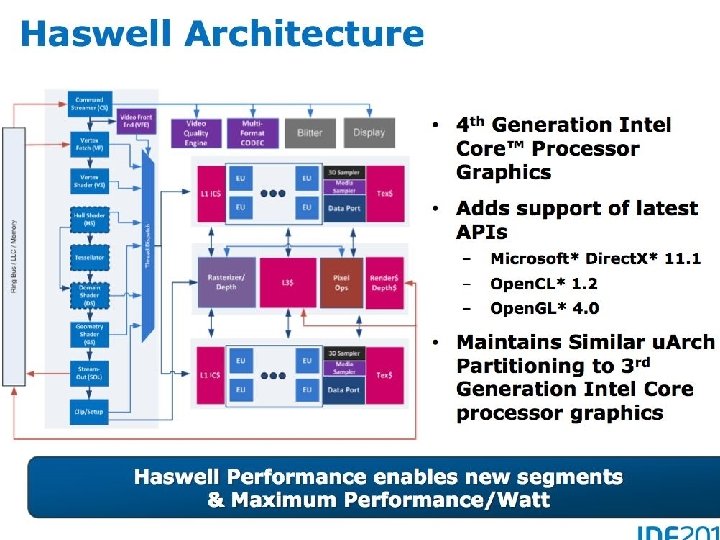

Today: Intel Haswell and smartphone/tablet processors • This material is not on final exam! • Intended for you to see modern day computer architectures. Fall 2012 -- Lecture #38 2

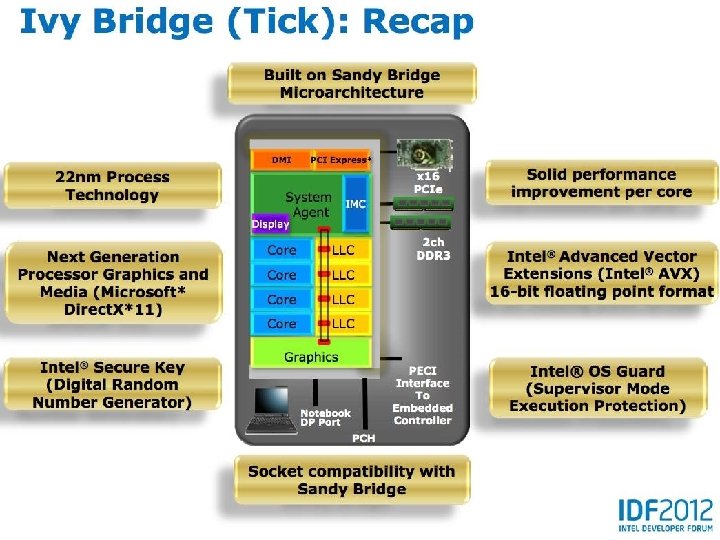

Intel Haswell Core • Not yet in production, the next core after Ivy Bridge! • Acknowledgements: Slides include material from Intel and David Kanter at Real World Technologies – Recommend site realworldtech. com for reading about new microprocessor architectures 3

Fall 2012 -- Lecture #38 4

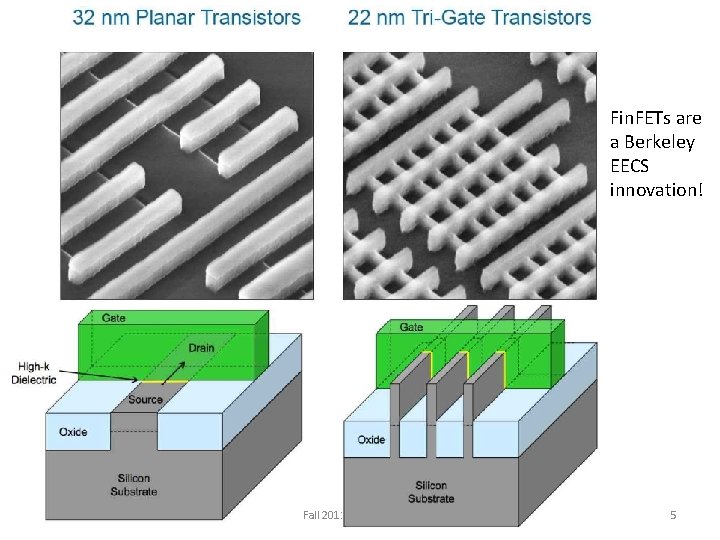

Fin. FETs are a Berkeley EECS innovation! Fall 2012 -- Lecture #38 5

Fall 2012 -- Lecture #38 6

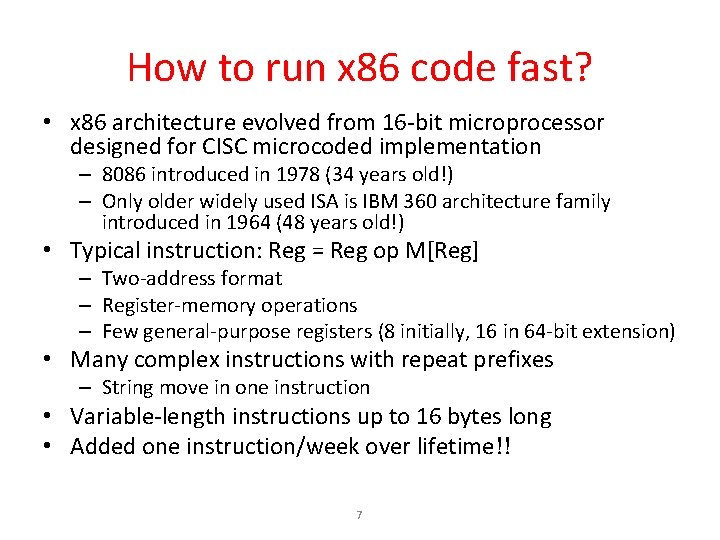

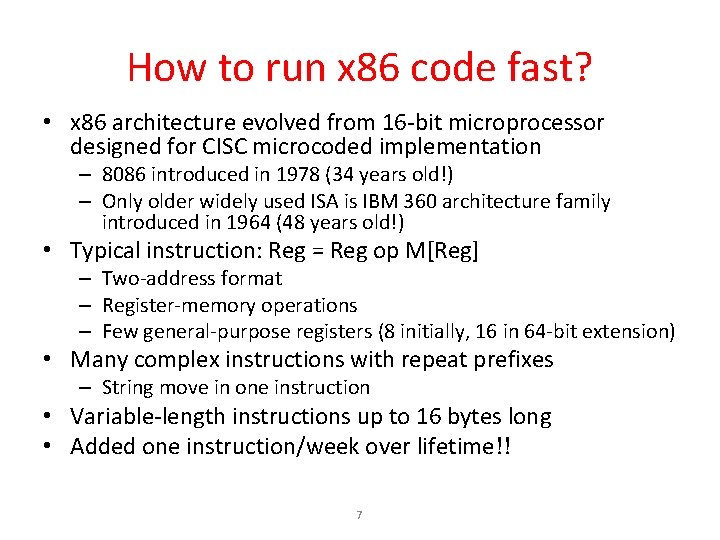

How to run x 86 code fast? • x 86 architecture evolved from 16 -bit microprocessor designed for CISC microcoded implementation – 8086 introduced in 1978 (34 years old!) – Only older widely used ISA is IBM 360 architecture family introduced in 1964 (48 years old!) • Typical instruction: Reg = Reg op M[Reg] – Two-address format – Register-memory operations – Few general-purpose registers (8 initially, 16 in 64 -bit extension) • Many complex instructions with repeat prefixes – String move in one instruction • Variable-length instructions up to 16 bytes long • Added one instruction/week over lifetime!! 7

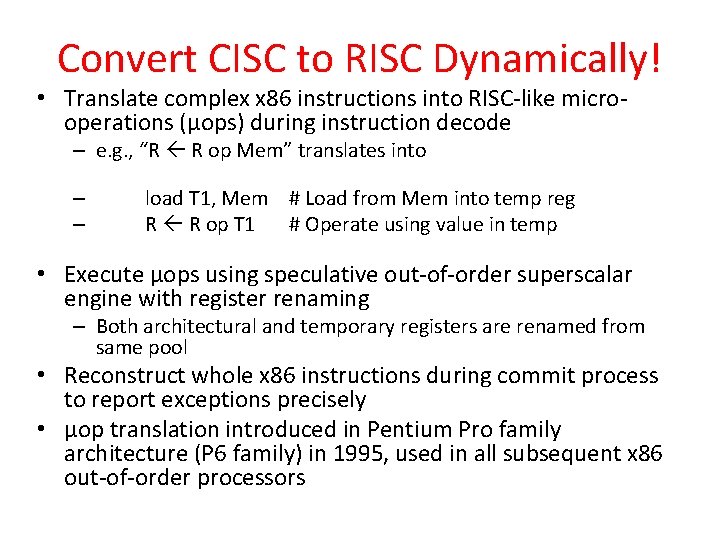

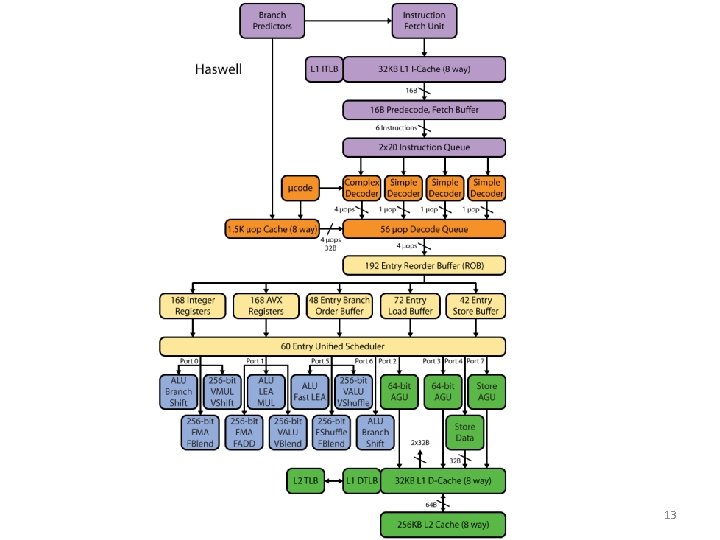

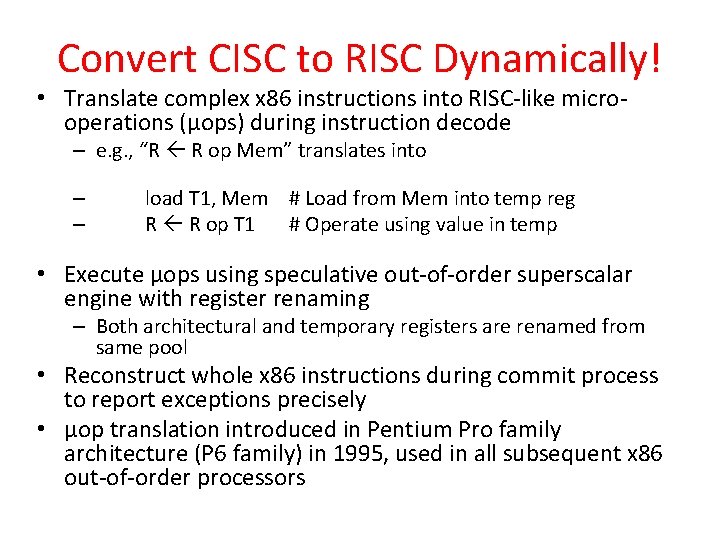

Convert CISC to RISC Dynamically! • Translate complex x 86 instructions into RISC-like microoperations (µops) during instruction decode – e. g. , “R R op Mem” translates into – – load T 1, Mem # Load from Mem into temp reg R R op T 1 # Operate using value in temp • Execute µops using speculative out-of-order superscalar engine with register renaming – Both architectural and temporary registers are renamed from same pool • Reconstruct whole x 86 instructions during commit process to report exceptions precisely • µop translation introduced in Pentium Pro family architecture (P 6 family) in 1995, used in all subsequent x 86 out-of-order processors

![Haswell FrontEnd Kanter Fall 2012 Lecture 38 9 Haswell Front-End [Kanter] Fall 2012 -- Lecture #38 9](https://slidetodoc.com/presentation_image_h2/c9145d2e18c852a57e8a161fff3d5c76/image-9.jpg)

Haswell Front-End [Kanter] Fall 2012 -- Lecture #38 9

![Haswell RenameReorder Kanter Fall 2012 Lecture 38 10 Haswell Rename/Reorder [Kanter] Fall 2012 -- Lecture #38 10](https://slidetodoc.com/presentation_image_h2/c9145d2e18c852a57e8a161fff3d5c76/image-10.jpg)

Haswell Rename/Reorder [Kanter] Fall 2012 -- Lecture #38 10

![Haswell Execution Kanter ALU Memory Fall 2012 Lecture 38 11 Haswell Execution [Kanter] ALU Memory Fall 2012 -- Lecture #38 11](https://slidetodoc.com/presentation_image_h2/c9145d2e18c852a57e8a161fff3d5c76/image-11.jpg)

Haswell Execution [Kanter] ALU Memory Fall 2012 -- Lecture #38 11

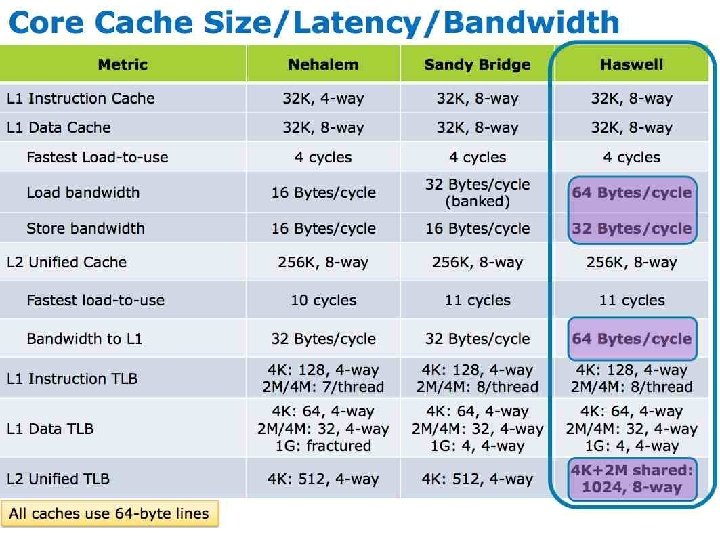

Fall 2012 -- Lecture #38 12

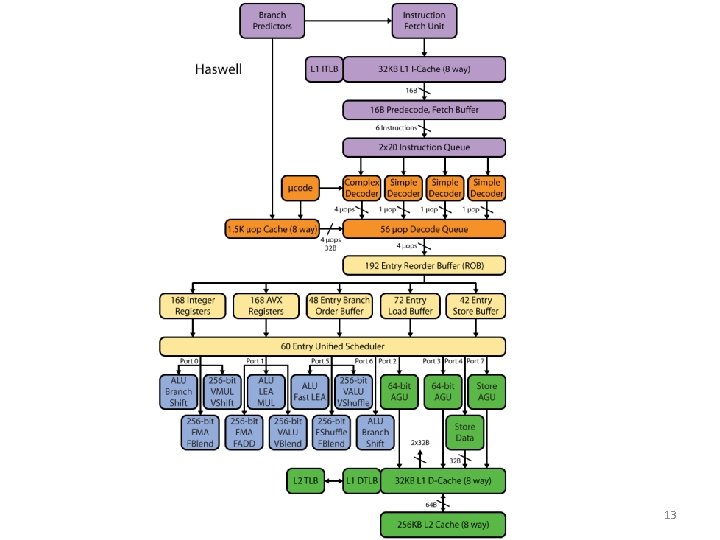

Fall 2012 -- Lecture #38 13

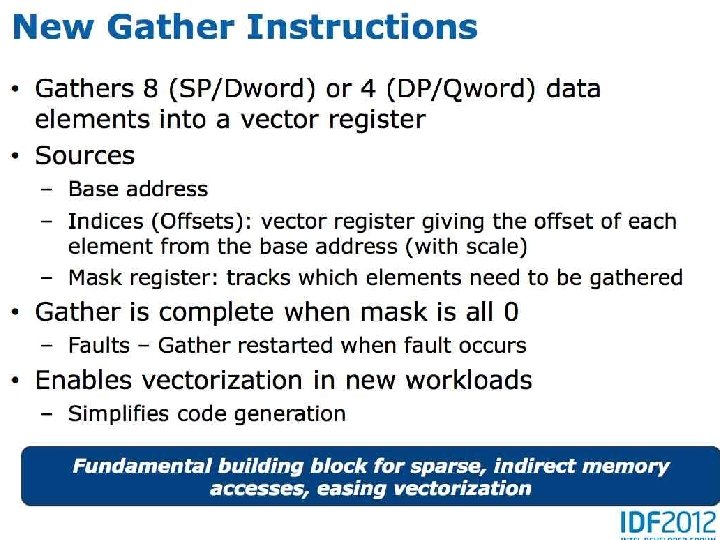

Fall 2012 -- Lecture #38 14

Fall 2012 -- Lecture #38 15

Fall 2012 -- Lecture #38 16

Fall 2012 -- Lecture #38 17

Fall 2012 -- Lecture #38 18

Administrivia • Final review session with TAs – Wednesday December 5 – 12: 00 pm-3: 00 pm – 1 Pimentel Fall 2012 -- Lecture #38 19

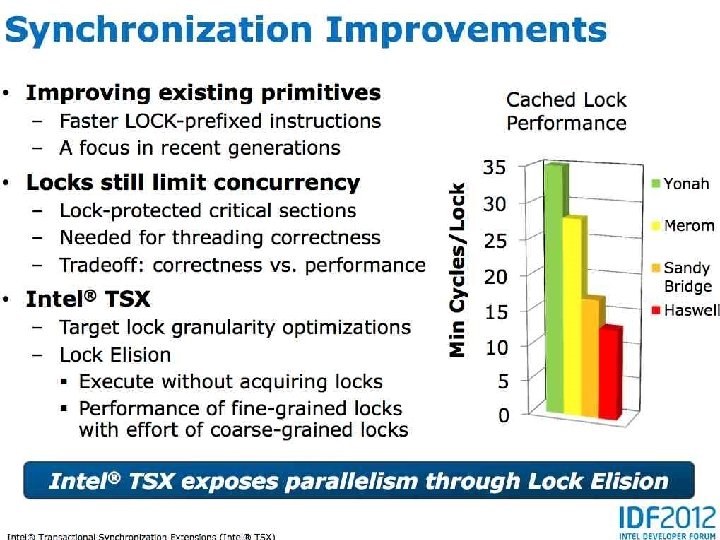

Smartphone Processors • Many companies and parts but some common features: – ARM ISA for application processors – Lots of dedicated accelerator blocks, especially image processors for cameras and GPUs for graphics – Only ~2 W max power dissipation! Fall 2012 -- Lecture #38 20

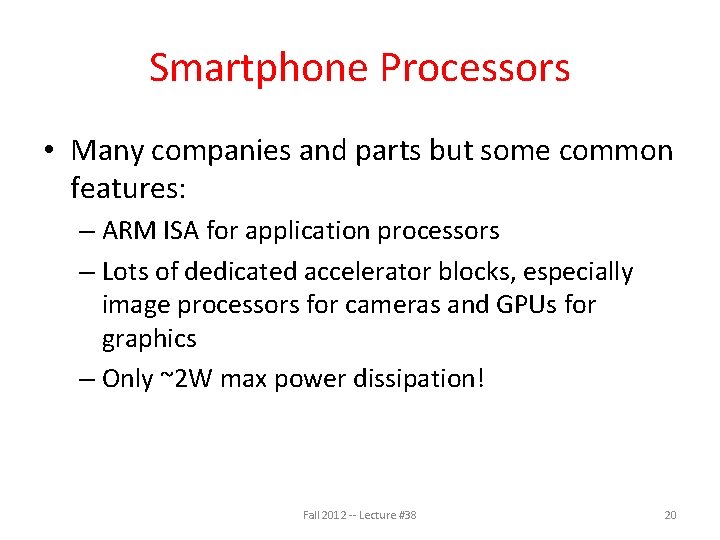

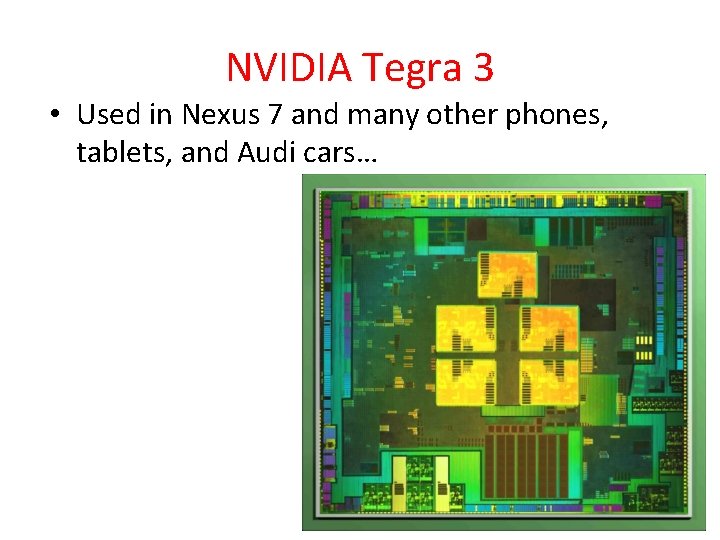

NVIDIA Tegra 3 • Used in Nexus 7 and many other phones, tablets, and Audi cars… Fall 2012 -- Lecture #38 21

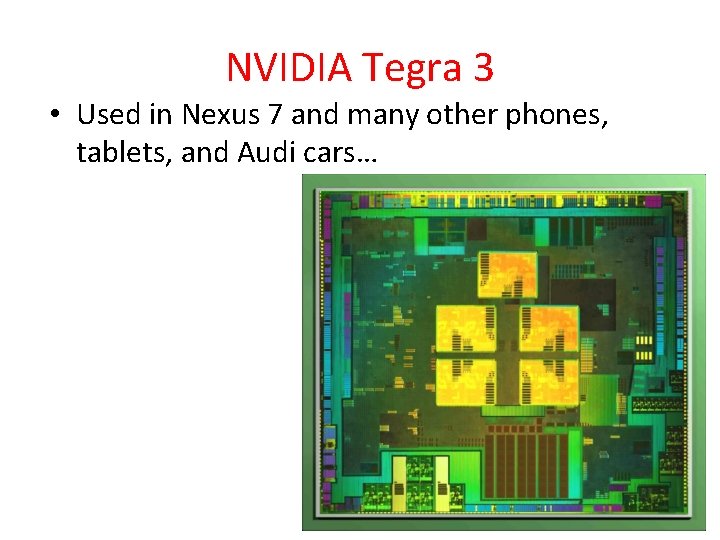

Tegra 3 Block Diagram Fall 2012 -- Lecture #38 22

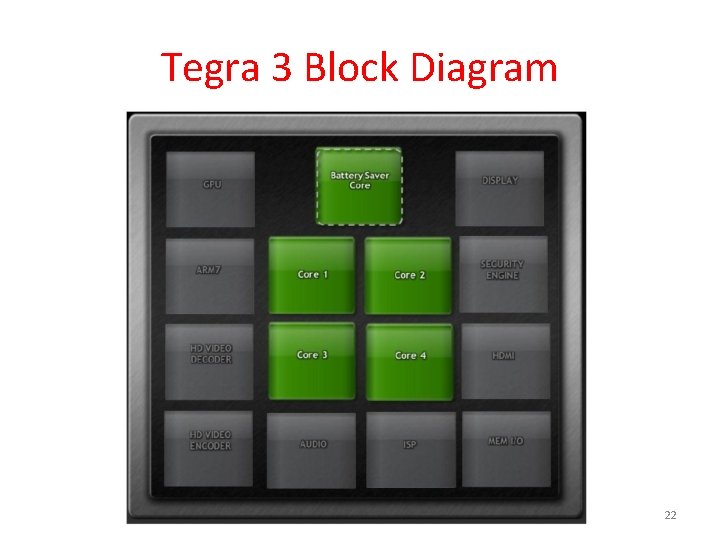

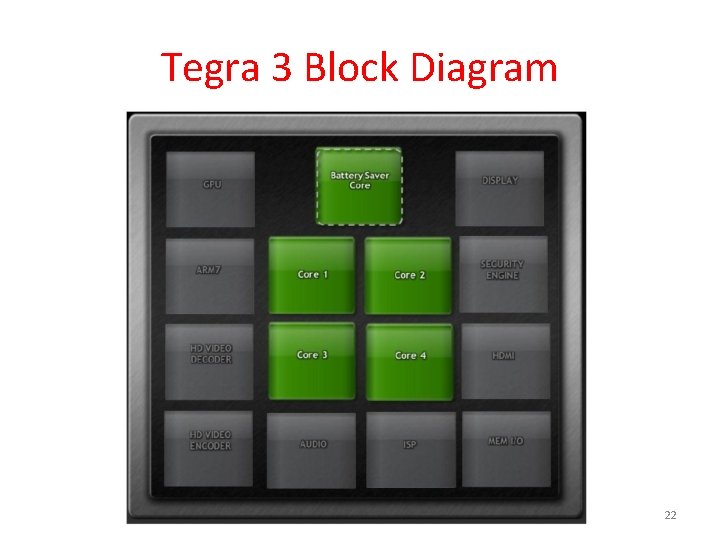

Tegra 3 “ 4 plus 1” operation Fall 2012 -- Lecture #38 23

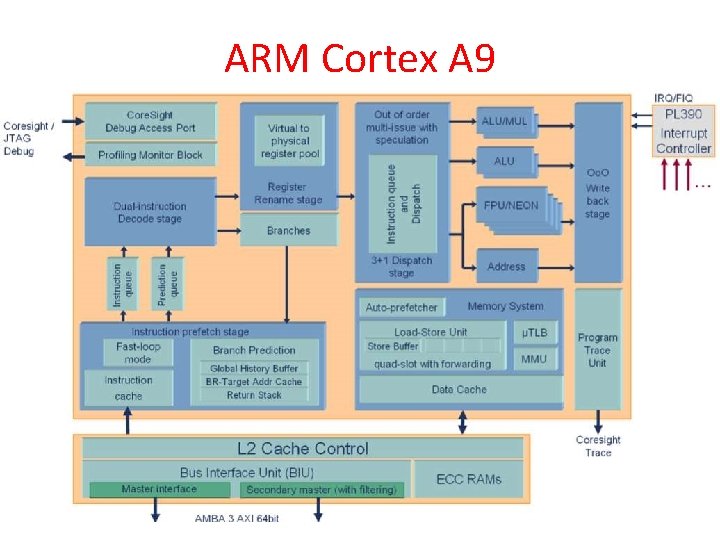

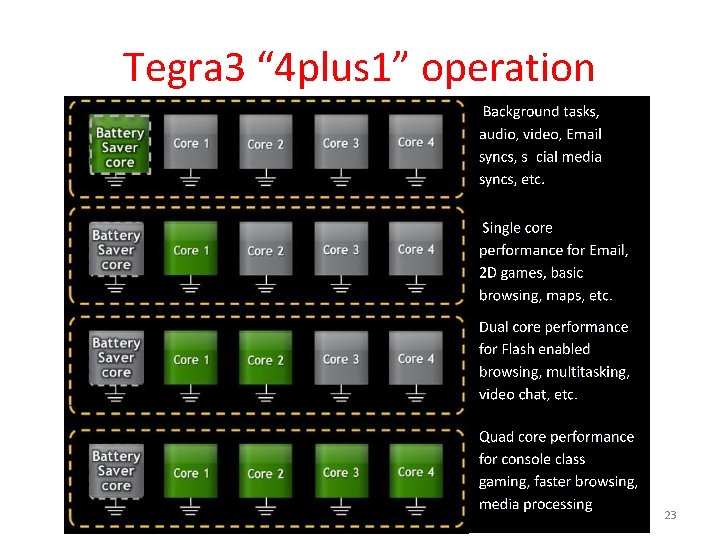

ARM Cortex A 9 Fall 2012 -- Lecture #38 24

Qualcomm Snapdragon MSM 8960 Fall 2012 -- Lecture #38 25

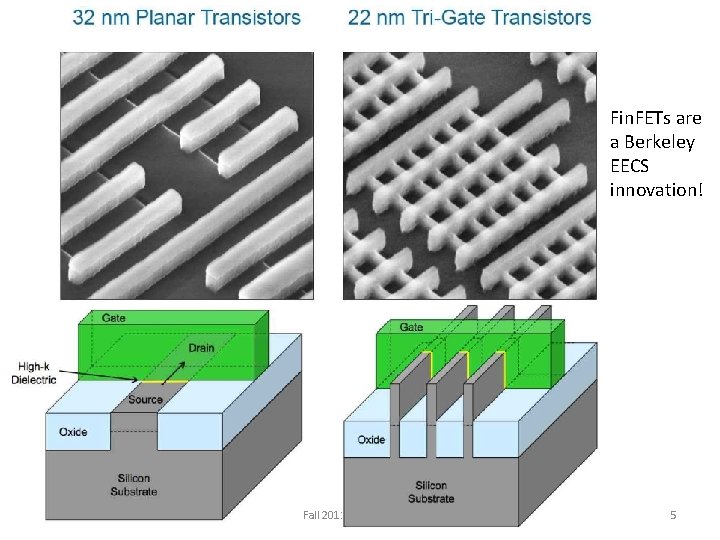

![Apple A 6 and A 6 X 32 nm Chipworks com 2012 Fall 2012 Apple A 6 and A 6 X (32 nm) [Chipworks. com, 2012] Fall 2012](https://slidetodoc.com/presentation_image_h2/c9145d2e18c852a57e8a161fff3d5c76/image-26.jpg)

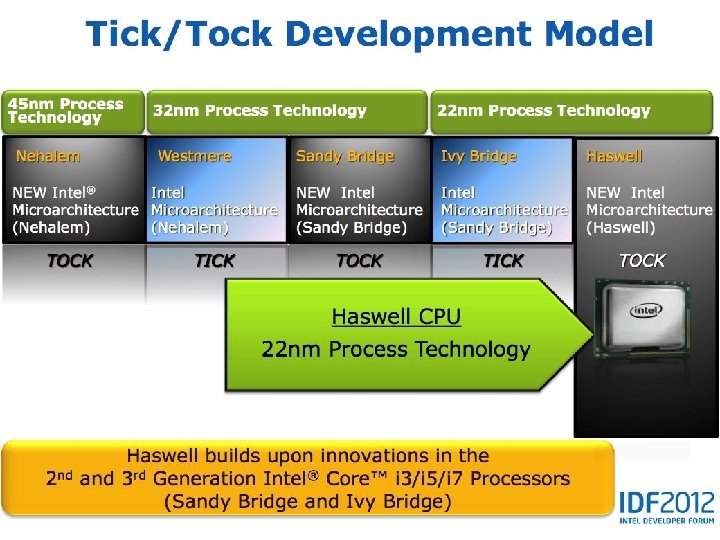

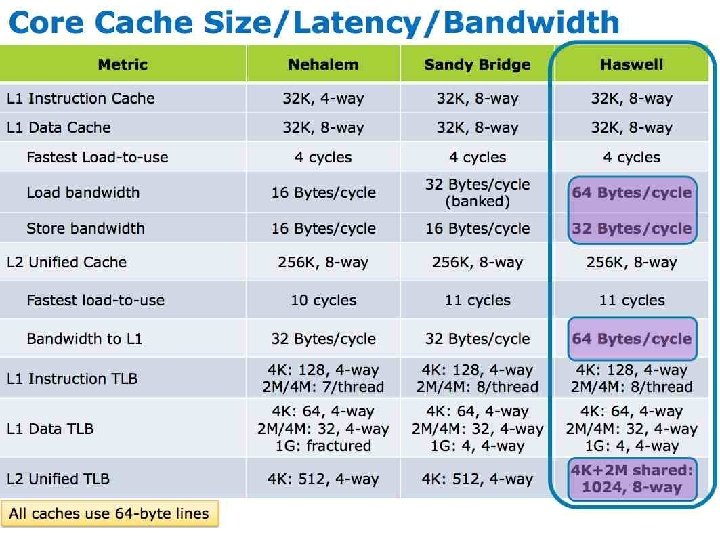

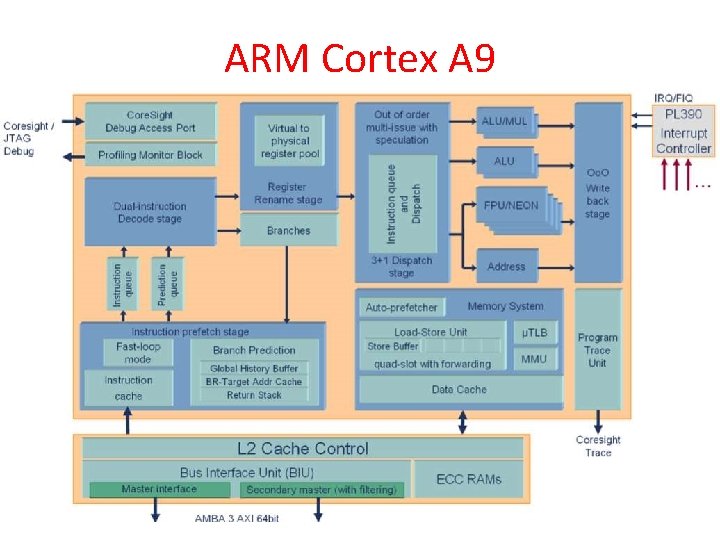

Apple A 6 and A 6 X (32 nm) [Chipworks. com, 2012] Fall 2012 -- Lecture #38 26

![Apple A 6 X chipworks com In i Pad 4 76 8 GFLOPS Peak Apple A 6 X [chipworks. com] In i. Pad 4 76. 8 GFLOPS Peak!](https://slidetodoc.com/presentation_image_h2/c9145d2e18c852a57e8a161fff3d5c76/image-27.jpg)

Apple A 6 X [chipworks. com] In i. Pad 4 76. 8 GFLOPS Peak! Fall 2012 -- Lecture #38 27

Summary • Continual rapid change in architecture – Mobile and server processors include large and increasing number of processors on single chip – More specialized processors common – New architectural concepts (transactional memory) • Covered basic ideas behind architectures in CS 61 C, but to learn more take CS 152 Fall 2012 -- Lecture #38 28