CS 301 Fall 2001 Chapter 1 Slides by

CS 301 Fall 2001 – Chapter 1 Slides by Prof. Hartman, following “IBM PC Assembly Language Programming” by Peter Abel 11/24/2020 1

Bits, Bytes, and Words A bit (binary digit) is 0 or 1 n byte = 8 bits n word = 2 bytes (16 -bit) n doubleword = 2 words (32 -bit) n quadword = 4 words (64 -bit) n kilobyte (K) = 210 (1024) bytes n megabyte (M) = 220 (1048576) bytes n 11/24/2020 2

Binary numbers Bit # 7 6 5 4 3 n Value: 128 64 32 16 8 n n 2 4 1 2 0 1 Example: 01000101 = 69 11/24/2020 3

Negative Binary Numbers n n One’s complement: flip the bits – 1 becomes 0, 0 becomes 1. Two’s complement: take one’s complement, then add one. This is how the computer represents the negative. Why? Because it works. Try -0, -1, and -13. (Check that adding -13 to 13 gives you 0) Actually, it works because when you add anything to its one’s complement, you get all ones. Adding one to that gives you 0 (with a carry out). 11/24/2020 4

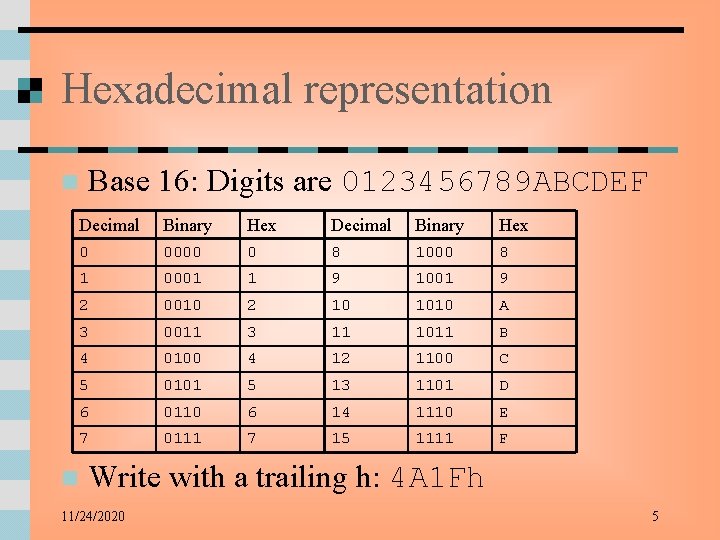

Hexadecimal representation n Base 16: Digits are 0123456789 ABCDEF Decimal Binary Hex 0 0000 0 8 1000 8 1 0001 1 9 1001 9 2 0010 2 10 1010 A 3 0011 3 11 1011 B 4 0100 4 12 1100 C 5 0101 5 13 1101 D 6 0110 6 14 1110 E 7 0111 7 15 1111 F n Write with a trailing h: 4 A 1 Fh 11/24/2020 5

Hex and Binary Arithmetic Just as decimal. Add corresponding columns, if the result is higher than the base, then carry. n To subtract, either use two’s complement to find the negative and then add, or do as in base 10 (“borrow” instead of “carry”) n 11/24/2020 6

ASCII code 01000001 – Is it 65 or A? n However you look at it. n Appendix B in the text n 11/24/2020 7

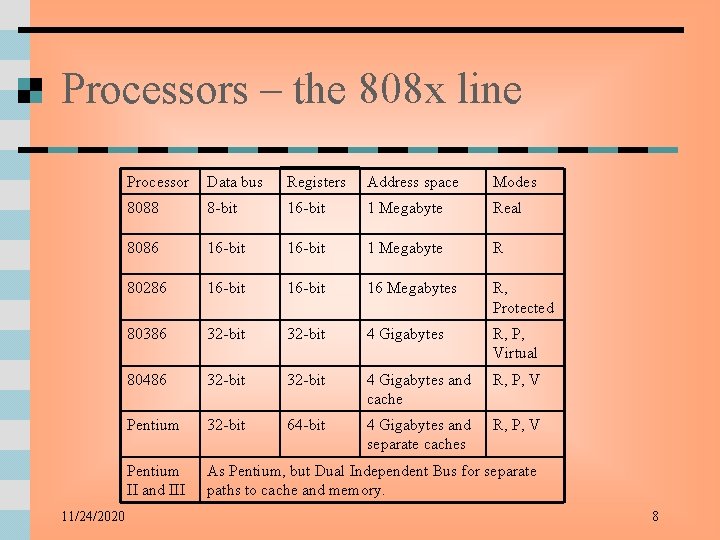

Processors – the 808 x line 11/24/2020 Processor Data bus Registers Address space Modes 8088 8 -bit 16 -bit 1 Megabyte Real 8086 16 -bit 1 Megabyte R 80286 16 -bit 16 Megabytes R, Protected 80386 32 -bit 4 Gigabytes R, P, Virtual 80486 32 -bit 4 Gigabytes and cache R, P, V Pentium 32 -bit 64 -bit 4 Gigabytes and separate caches R, P, V Pentium II and III As Pentium, but Dual Independent Bus for separate paths to cache and memory. 8

Pipelining and other speedups Each more advanced processor does more at once (pipelining) n Branch prediction (because processors are faster than memory) n 11/24/2020 9

Execution Unit and Bus Interface Unit Execution Unit: registers, control unit (CU), arithmetic and logic unit (ALU) – executes instructions n BIU: brings instructions to EU, manages segment registers and instruction queue. n 11/24/2020 10

Internal Memory RAM – random access memory n ROM – read only memory n 808 x processors that handle more than one byte at a time store the most significant byte in the high memory address and the low order byte in the low address. n 11/24/2020 11

Segments and Addressing n In real mode three main segments are 1) 2) 3) 11/24/2020 Code Segment – instructions. Indexed by the CS register. Data Segment – contains data, constants, and work areas. Indexed by the DS register. Stack Segment – contains data and addresses to be temporarily saved, or for use by called subroutines. Indexed by the SS register. 12

Segment Boundaries n n A segment register is 16 bits and contains the starting address of a segment – besides CS, DS, SS, others are ES (extra segment), and (on 80386 and later) FS and GS. Because segments begin on “paragraph” boundaries (divisible by 10 H) the designers didn’t store the smallest byte in the segment register, so if DS is 9 FAH then the data segment begins at 9 FA 0 H. 11/24/2020 13

Segment Offsets n All memory locations within a segment are relative to the segment’s starting address. The distance in bytes is expressed as an offset. In real mode, an offset is two bytes. Consider a data segment beginning at 38 E 0 H. The DS contains 38 EH. If an instruction references a location with an offset of 32 H bytes (0032 H), the processor adds: 38 E[0]H + 0032 H = 3912 H and looks in address 3912 H. 11/24/2020 14

Segment Registers n n n 8086/8088 – segment registers are 16 -bit and operate in real mode. FFFF[0]H is 1 megabyte. 80286 – Real mode is same as 8086. In protected mode, 24 -bit addressing provides addresses up to FFFFF[0]H, or 16 megabytes by using segment register as index into memory that points at segment. 80386/486/Pentium – Real mode again same as 8086. In protected mode, 48 -bit addresses can address up to 4 gigabytes by using segment register as index into memory that points at segment. 11/24/2020 15

Segment Registers 2 CS register – contains starting address of the code segment. Along with IP, [CS: IP] gives the address of the instruction to be fetched for execution. n DS register – contains starting address of the data segment. Used with offsets included in instructions. n 11/24/2020 16

![Segment Registers 3 SS register – For the stack segment, used as [SS: SP]. Segment Registers 3 SS register – For the stack segment, used as [SS: SP].](http://slidetodoc.com/presentation_image_h/91f91a6b34c825866516472e4537aa0f/image-17.jpg)

Segment Registers 3 SS register – For the stack segment, used as [SS: SP]. Also (in subroutines) [SS: BP]. n ES register – Used (as [ES: DI]) by some string operations to handle memory addressing. n FS and GS registers – Additional extra segment registers introduced with 80386 processor. n 11/24/2020 17

Pointer Registers The 32 bit pointer registers are EIP, ESP, and EBP. Their rightmost 16 bits are called IP, SP, and BP. n Pointer registers are offsets to be combined with segment registers. IP is used with CS, SP and BP are used with SS. n 11/24/2020 18

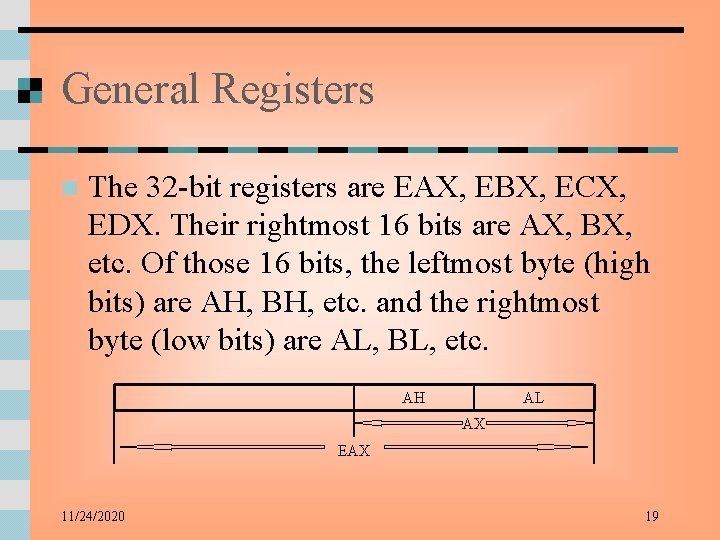

General Registers n The 32 -bit registers are EAX, EBX, ECX, EDX. Their rightmost 16 bits are AX, BX, etc. Of those 16 bits, the leftmost byte (high bits) are AH, BH, etc. and the rightmost byte (low bits) are AL, BL, etc. AH AL AX EAX 11/24/2020 19

General Registers 2 n n AX – the primary accumulator is used for I/O and most arithmetic (such as multiply, divide, and translate). Many instructions generate more efficient machine code if the reference AX rather than some other register. BX – the base register. BX is the only general purpose register that can be used as an index to extend addressing. BX is also often used for computation and with SI or SI as a base register. 11/24/2020 20

General Registers 3 CX is called the count register. It is often used as a loop index, or a value to shift bits left or right. n DX is called the data register. Some I/O operations require it, and large multiplication and division operations use it along with AX as a pair. n 11/24/2020 21

Index Registers ESI and EDI are the 32 -bit index registers, their rightmost 16 bits are SI and DI respectively. n SI is the “source index register” associated with DS for some string operations n DI is the “destination index register” associated with ES for some string operations. n 11/24/2020 22

Flag Register n The 32 -bit EFLAGS contains bits indicating the status of various activities. The rightmost 16 bits of EFLAGS is the FLAGS register, nine of its 16 bits indicate the status and results of processing. Many instructions change the status of these flags, other instructions test the flags to determine later action. 11/24/2020 23

Flag bits 1 OF (overflow) Indicates overflow of the leftmost bit during arithmetic. n DF (direction) Indicates left or right for moving or comparing string data. n IF (interrupt) Indicates whether external interrupts are being processed or ignored. n TF (trap) Permits operation of the processor in single step mode. n 11/24/2020 24

Flag bits 2 SF (sign) Contains the resulting sign of an arithmetic operation (1=negative) n ZF (zero) Indicates when the result of arithmetic or a comparison is zero. (1=yes) n AF (auxiliary carry) Contains carry out of bit 3 into bit 4 for specialized arithmetic. n PF (parity) Indicates the number of 1 bits that result from an operation. n 11/24/2020 25

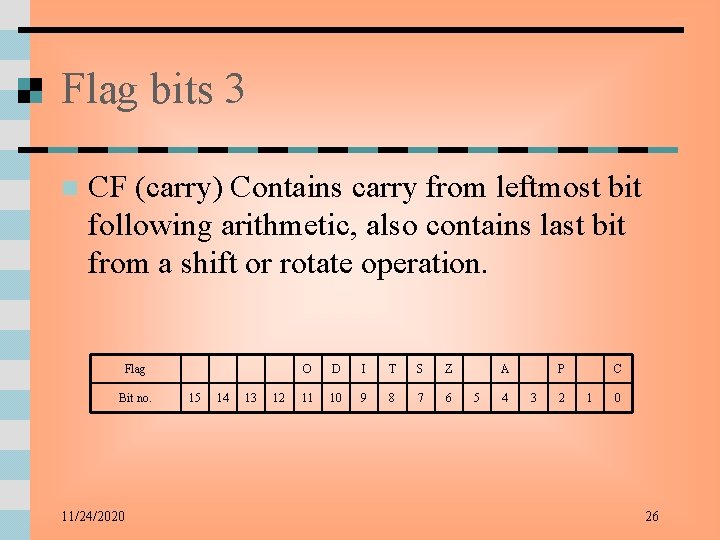

Flag bits 3 n CF (carry) Contains carry from leftmost bit following arithmetic, also contains last bit from a shift or rotate operation. Flag Bit no. 11/24/2020 15 14 13 12 O D I T S Z 11 10 9 8 7 6 A 5 4 P 3 2 C 1 0 26

Hardware Interrupts n Some events cause the processor to stop what it is doing and act immediately on something else. Usually these are normal such as keyboard input, but sometimes they are critical, such as divide by zero. There also software interrupts, such as a request by the program to display data on the screen. After an interrupt is processed the processor returns to what it was doing. 11/24/2020 27

- Slides: 27