CS 258 Parallel Computer Architecture Lecture 15 Sequential

- Slides: 23

CS 258 Parallel Computer Architecture Lecture 15 Sequential Consistency and Snoopy Protocols March 17, 2008 Prof John D. Kubiatowicz http: //www. cs. berkeley. edu/~kubitron/cs 258

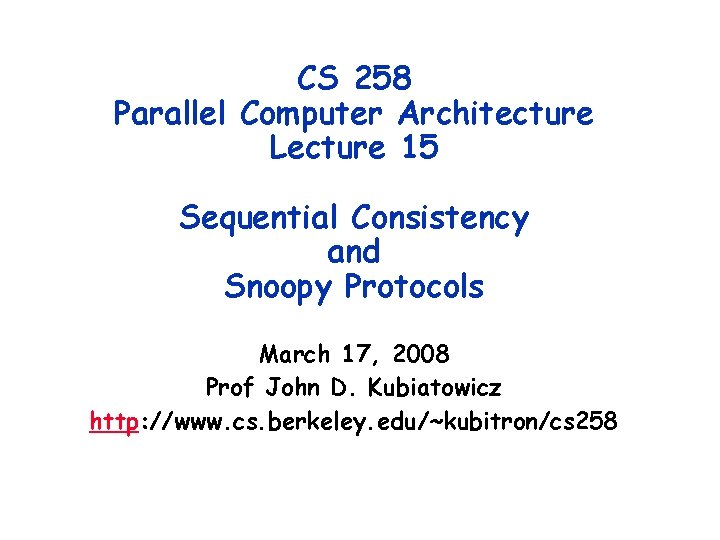

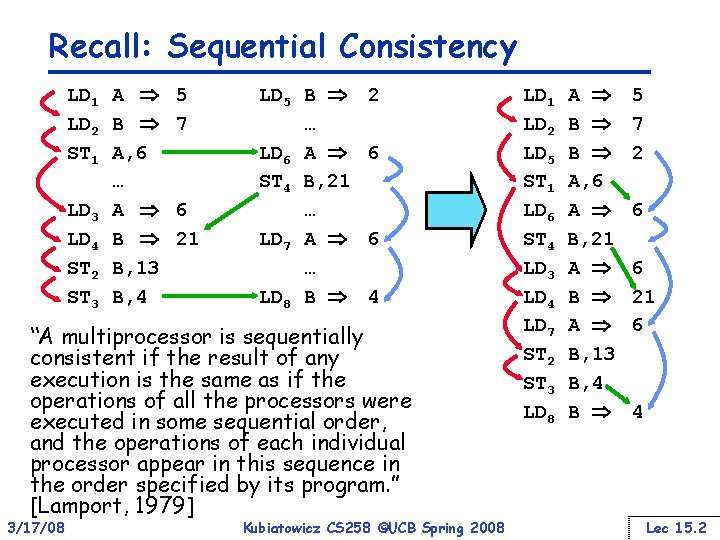

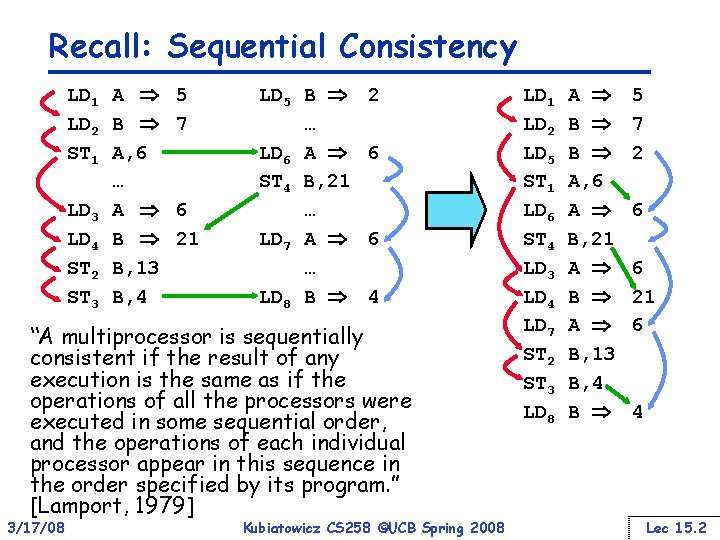

Recall: Sequential Consistency LD 1 A LD 2 B ST 1 A, 6 … LD 3 A LD 4 B ST 2 B, 13 ST 3 B, 4 5 7 6 21 LD 5 B … LD 6 A ST 4 B, 21 … LD 7 A … LD 8 B 2 6 6 4 “A multiprocessor is sequentially consistent if the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program. ” [Lamport, 1979] 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 LD 1 LD 2 LD 5 ST 1 LD 6 ST 4 LD 3 LD 4 LD 7 ST 2 ST 3 LD 8 A B B A, 6 A B, 21 A B, 13 B, 4 B 5 7 2 6 6 21 6 4 Lec 15. 2

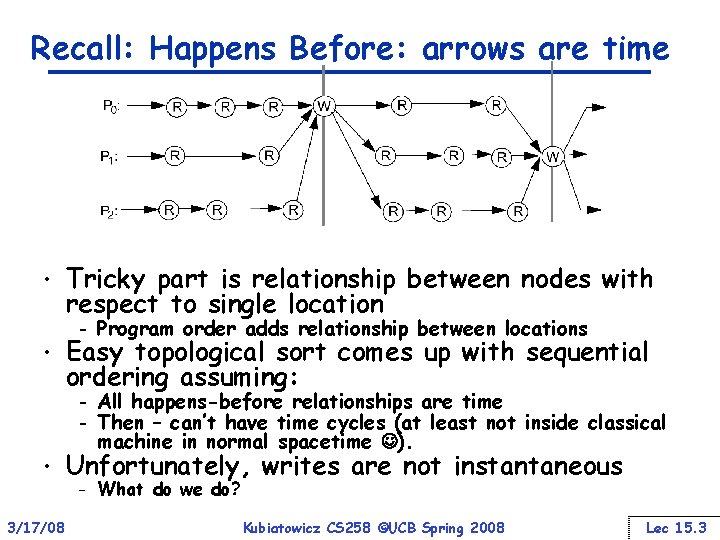

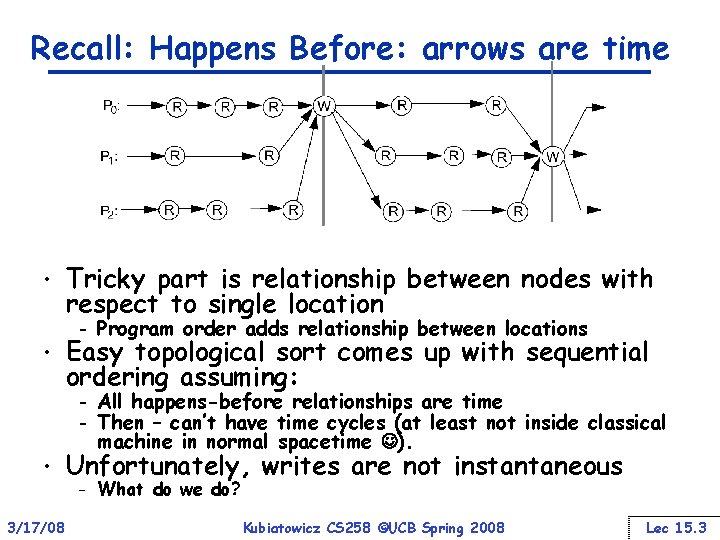

Recall: Happens Before: arrows are time • • • 3/17/08 Tricky part is relationship between nodes with respect to single location – Program order adds relationship between locations – – All happens-before relationships are time Then – can’t have time cycles (at least not inside classical machine in normal spacetime ). Easy topological sort comes up with sequential ordering assuming: Unfortunately, writes are not instantaneous – What do we do? Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 3

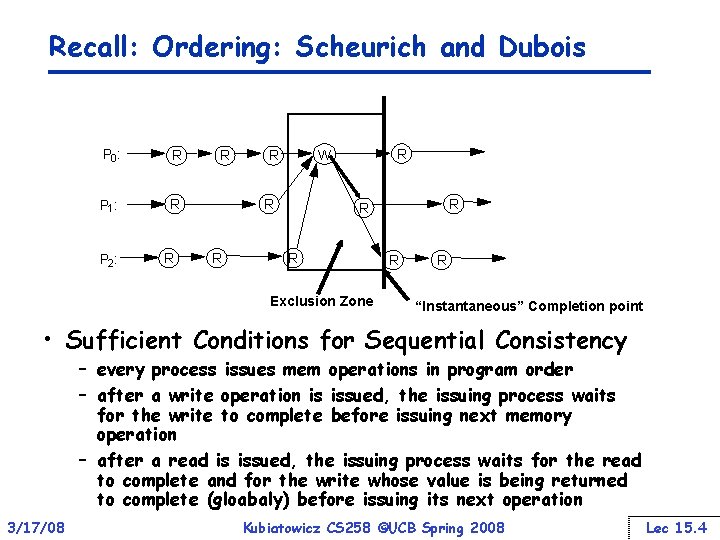

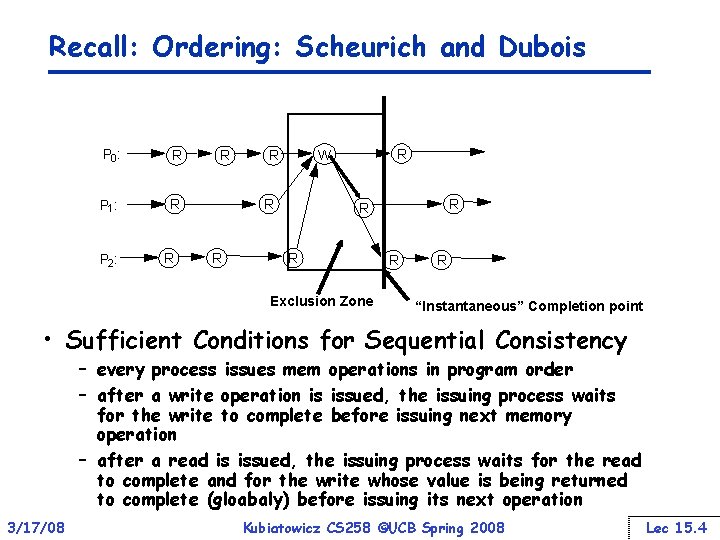

Recall: Ordering: Scheurich and Dubois P 0: R P 1: R P 2: R R R W R R Exclusion Zone R R “Instantaneous” Completion point • Sufficient Conditions for Sequential Consistency – every process issues mem operations in program order – after a write operation is issued, the issuing process waits for the write to complete before issuing next memory operation – after a read is issued, the issuing process waits for the read to complete and for the write whose value is being returned to complete (gloabaly) before issuing its next operation 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 4

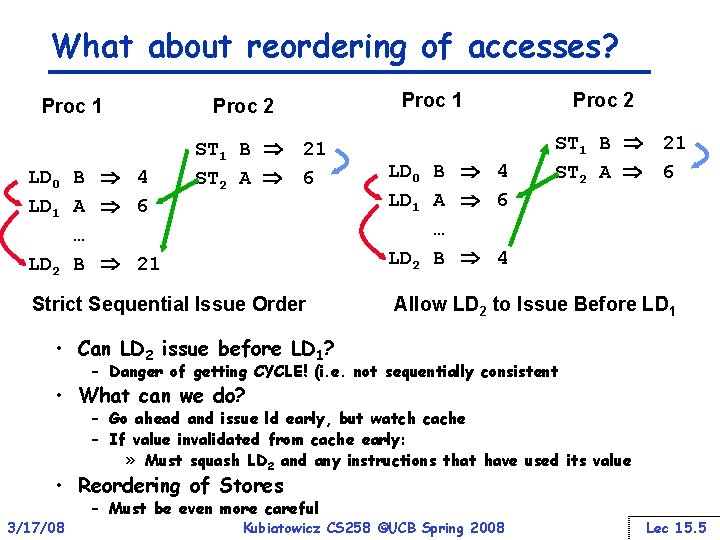

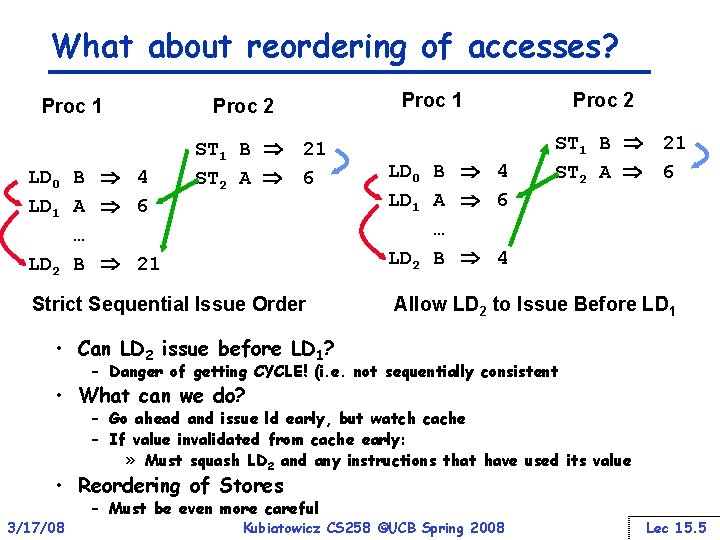

What about reordering of accesses? Proc 1 LD 0 B 4 LD 1 A 6 … LD 2 B 21 Proc 2 ST 1 B ST 2 A 21 6 Strict Sequential Issue Order LD 0 B 4 LD 1 A 6 … LD 2 B 4 Proc 2 ST 1 B ST 2 A 21 6 Allow LD 2 to Issue Before LD 1 • Can LD 2 issue before LD 1? – Danger of getting CYCLE! (i. e. not sequentially consistent • What can we do? – Go ahead and issue ld early, but watch cache – If value invalidated from cache early: » Must squash LD 2 and any instructions that have used its value • Reordering of Stores 3/17/08 – Must be even more careful Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 5

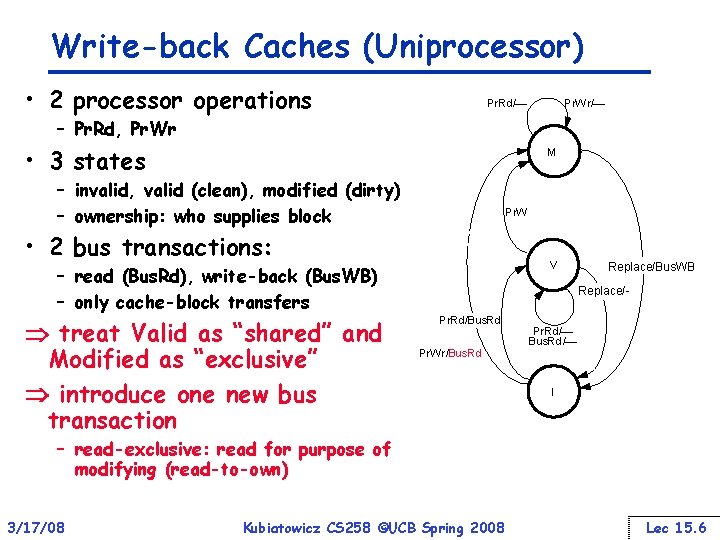

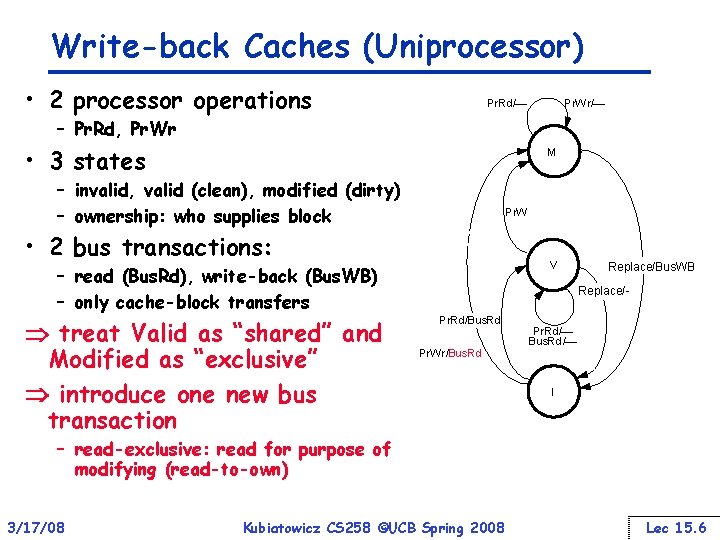

Write-back Caches (Uniprocessor) • 2 processor operations Pr. Rd/— Pr. Wr/— – Pr. Rd, Pr. Wr • 3 states M – invalid, valid (clean), modified (dirty) – ownership: who supplies block Pr. W • 2 bus transactions: V – read (Bus. Rd), write-back (Bus. WB) – only cache-block transfers treat Valid as “shared” and Modified as “exclusive” introduce one new bus transaction Replace/Bus. WB Replace/- Pr. Rd/Bus. Rd Pr. Wr/Bus. Rd Pr. Rd/— Bus. Rd/— I – read-exclusive: read for purpose of modifying (read-to-own) 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 6

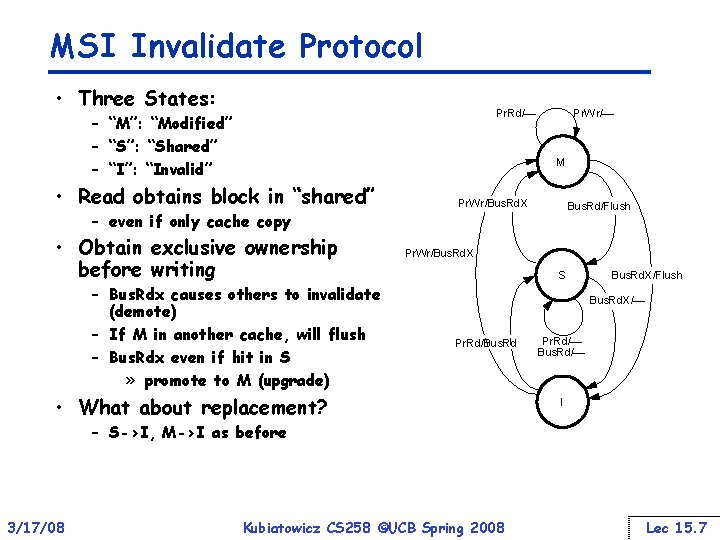

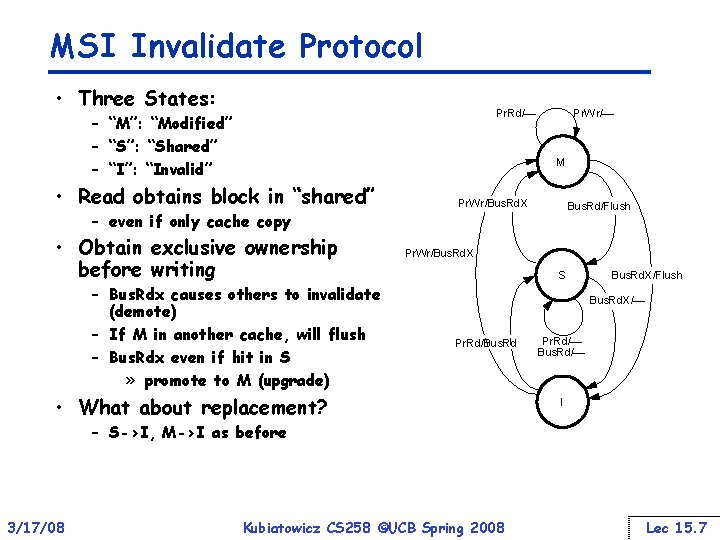

MSI Invalidate Protocol • Three States: Pr. Rd/— – “M”: “Modified” – “S”: “Shared” – “I”: “Invalid” Pr. Wr/— M • Read obtains block in “shared” – even if only cache copy • Obtain exclusive ownership before writing – Bus. Rdx causes others to invalidate (demote) – If M in another cache, will flush – Bus. Rdx even if hit in S » promote to M (upgrade) Pr. Wr/Bus. Rd. X Bus. Rd/Flush Pr. Wr/Bus. Rd. X S Bus. Rd. X/Flush Bus. Rd. X/— Pr. Rd/Bus. Rd • What about replacement? Pr. Rd/— Bus. Rd/— I – S->I, M->I as before 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 7

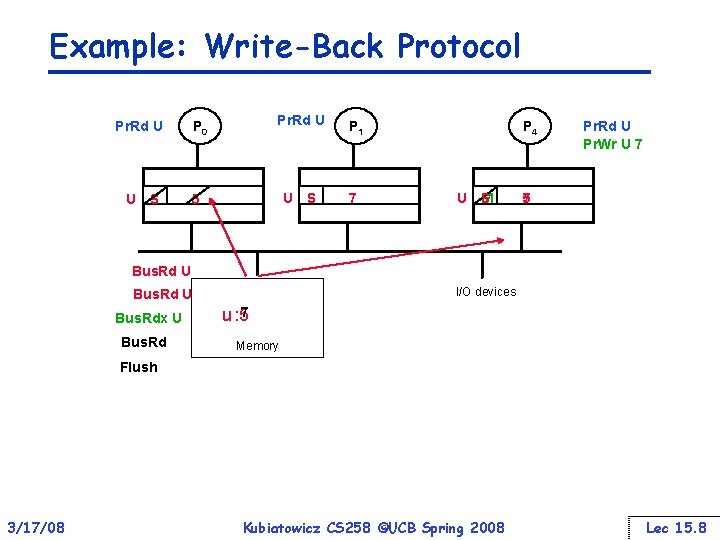

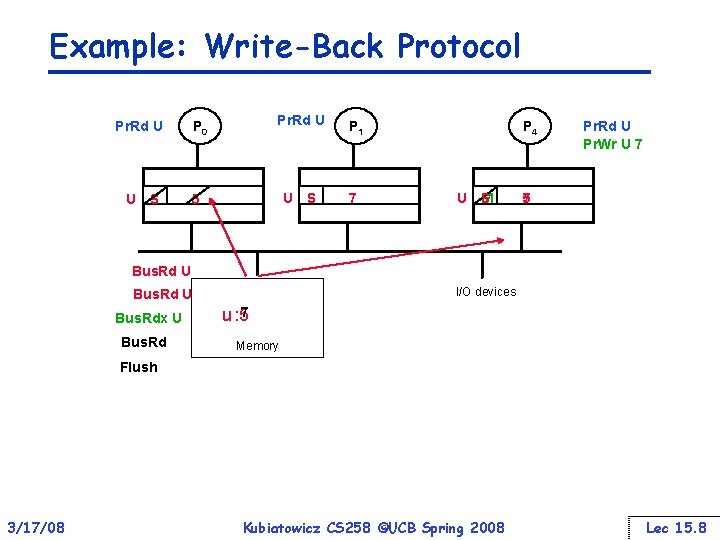

Example: Write-Back Protocol Pr. Rd U P 0 Pr. Rd U P 1 U S 5 U S 7 P 4 U S M Pr. Rd U Pr. Wr U 7 5 7 Bus. Rd U I/O devices Bus. Rd U Bus. Rdx U Bus. Rd u : 57 Memory Flush 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 8

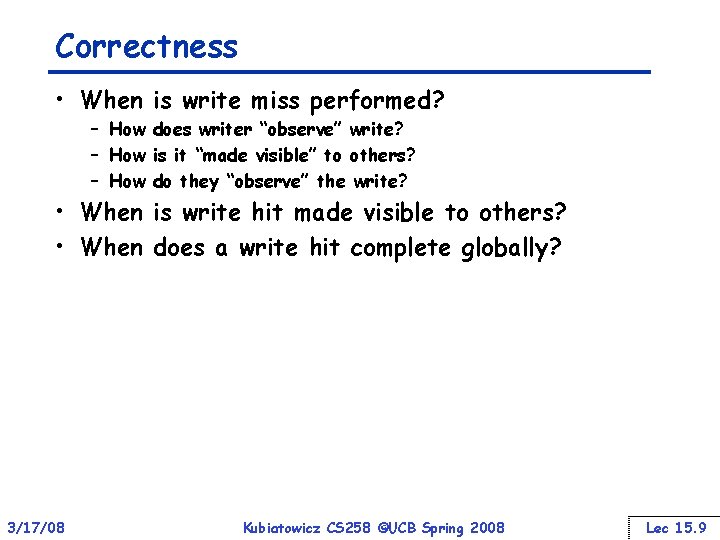

Correctness • When is write miss performed? – How does writer “observe” write? – How is it “made visible” to others? – How do they “observe” the write? • When is write hit made visible to others? • When does a write hit complete globally? 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 9

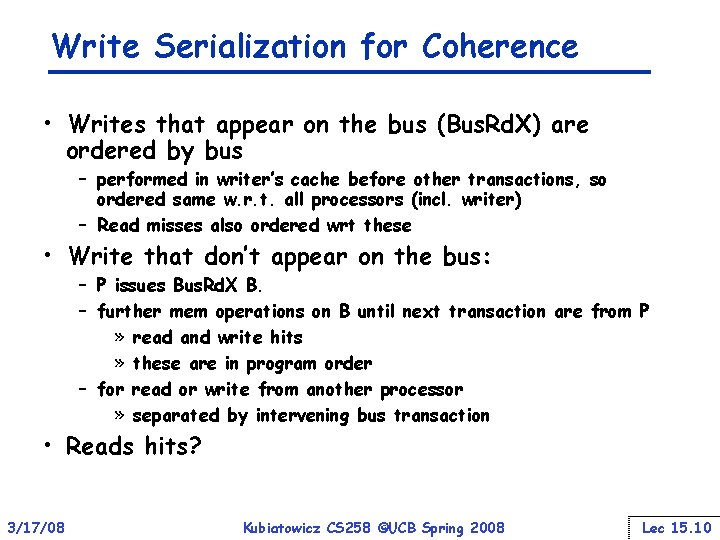

Write Serialization for Coherence • Writes that appear on the bus (Bus. Rd. X) are ordered by bus – performed in writer’s cache before other transactions, so ordered same w. r. t. all processors (incl. writer) – Read misses also ordered wrt these • Write that don’t appear on the bus: – P issues Bus. Rd. X B. – further mem operations on B until next transaction are from P » read and write hits » these are in program order – for read or write from another processor » separated by intervening bus transaction • Reads hits? 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 10

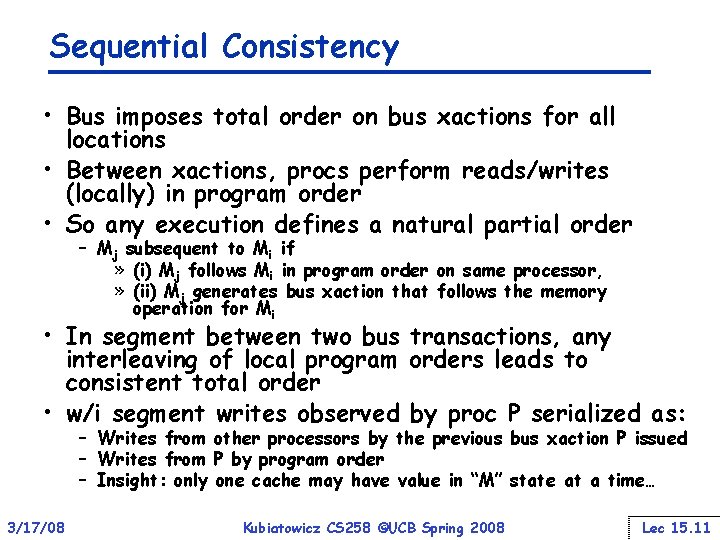

Sequential Consistency • Bus imposes total order on bus xactions for all locations • Between xactions, procs perform reads/writes (locally) in program order • So any execution defines a natural partial order – Mj subsequent to Mi if » (i) Mj follows Mi in program order on same processor, » (ii) Mj generates bus xaction that follows the memory operation for Mi • In segment between two bus transactions, any interleaving of local program orders leads to consistent total order • w/i segment writes observed by proc P serialized as: – Writes from other processors by the previous bus xaction P issued – Writes from P by program order – Insight: only one cache may have value in “M” state at a time… 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 11

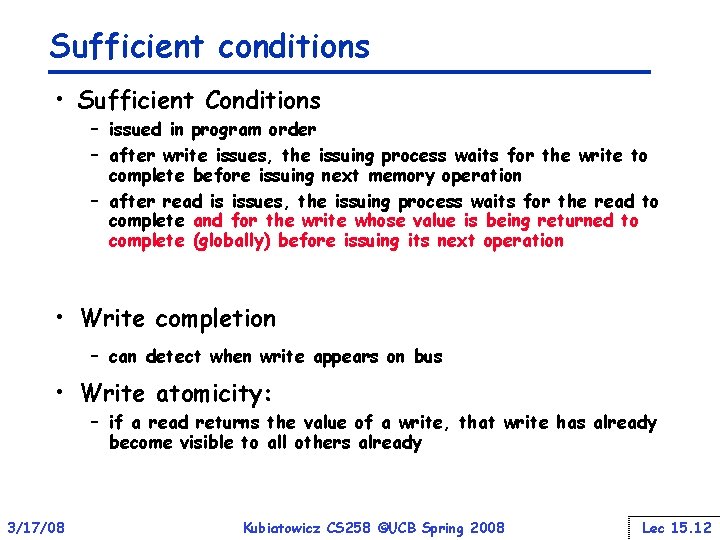

Sufficient conditions • Sufficient Conditions – issued in program order – after write issues, the issuing process waits for the write to complete before issuing next memory operation – after read is issues, the issuing process waits for the read to complete and for the write whose value is being returned to complete (globally) before issuing its next operation • Write completion – can detect when write appears on bus • Write atomicity: – if a read returns the value of a write, that write has already become visible to all others already 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 12

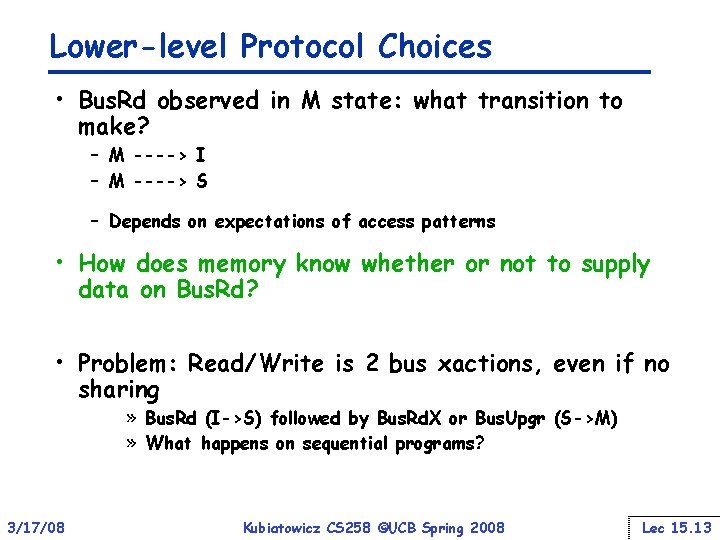

Lower-level Protocol Choices • Bus. Rd observed in M state: what transition to make? – M ----> I – M ----> S – Depends on expectations of access patterns • How does memory know whether or not to supply data on Bus. Rd? • Problem: Read/Write is 2 bus xactions, even if no sharing » Bus. Rd (I->S) followed by Bus. Rd. X or Bus. Upgr (S->M) » What happens on sequential programs? 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 13

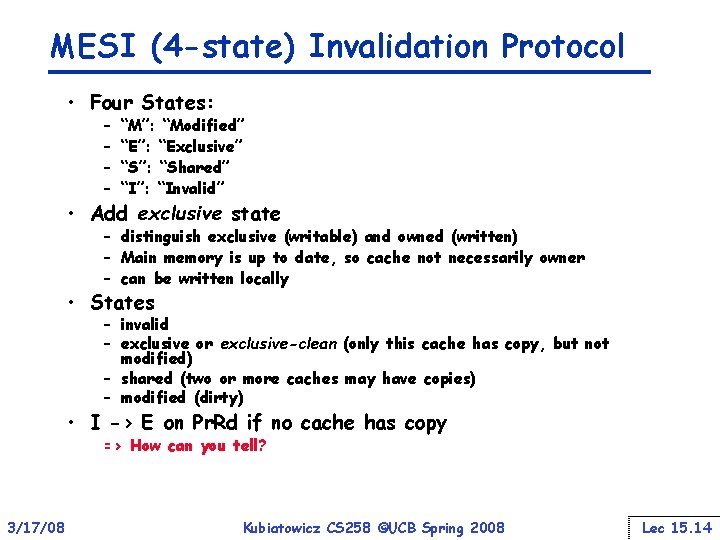

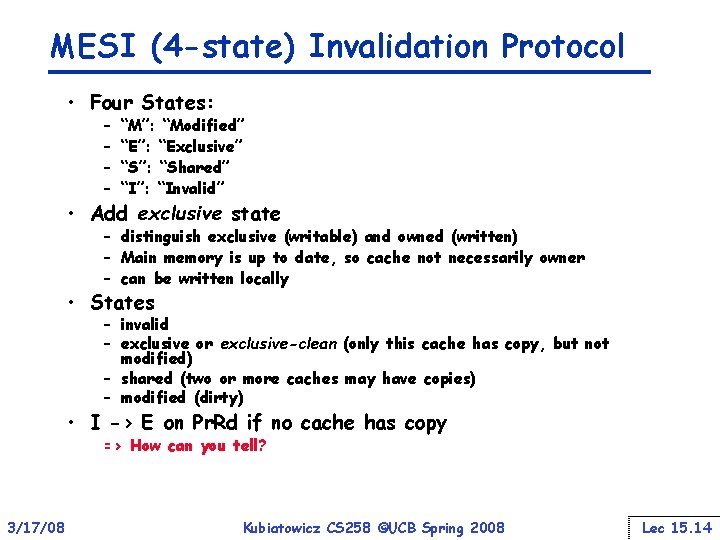

MESI (4 -state) Invalidation Protocol • Four States: – – “M”: “Modified” “E”: “Exclusive” “S”: “Shared” “I”: “Invalid” • Add exclusive state – distinguish exclusive (writable) and owned (written) – Main memory is up to date, so cache not necessarily owner – can be written locally • States – invalid – exclusive or exclusive-clean (only this cache has copy, but not modified) – shared (two or more caches may have copies) – modified (dirty) • I -> E on Pr. Rd if no cache has copy => How can you tell? 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 14

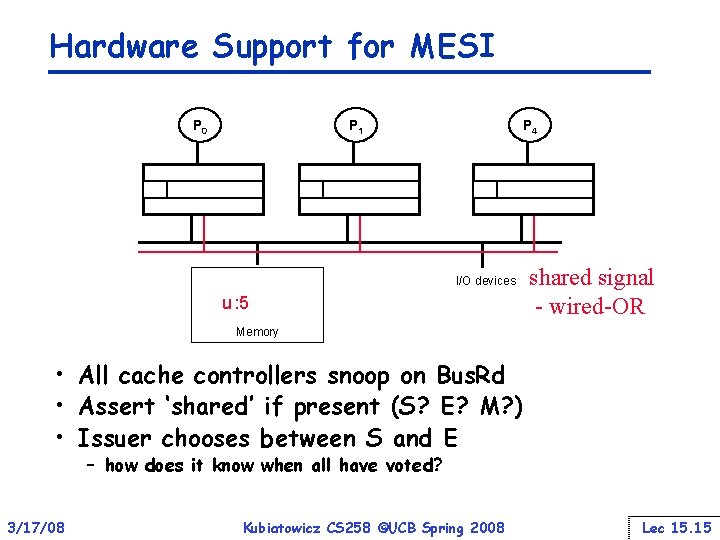

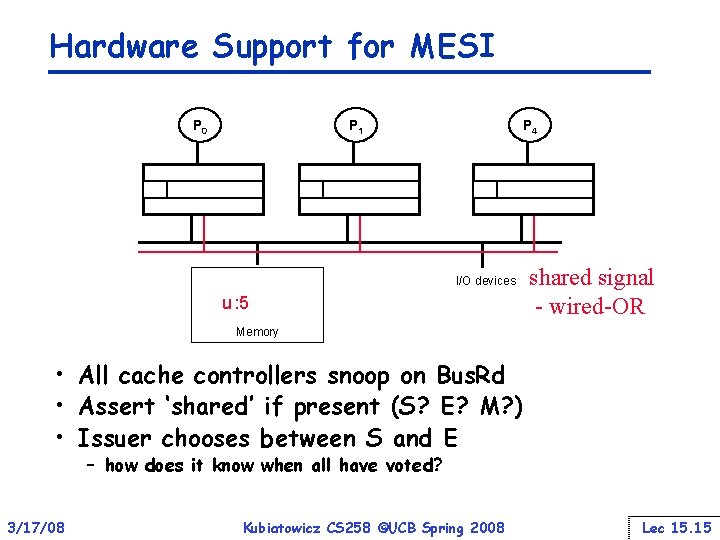

Hardware Support for MESI P 0 P 1 P 4 I/O devices u : 5 shared signal - wired-OR Memory • All cache controllers snoop on Bus. Rd • Assert ‘shared’ if present (S? E? M? ) • Issuer chooses between S and E – how does it know when all have voted? 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 15

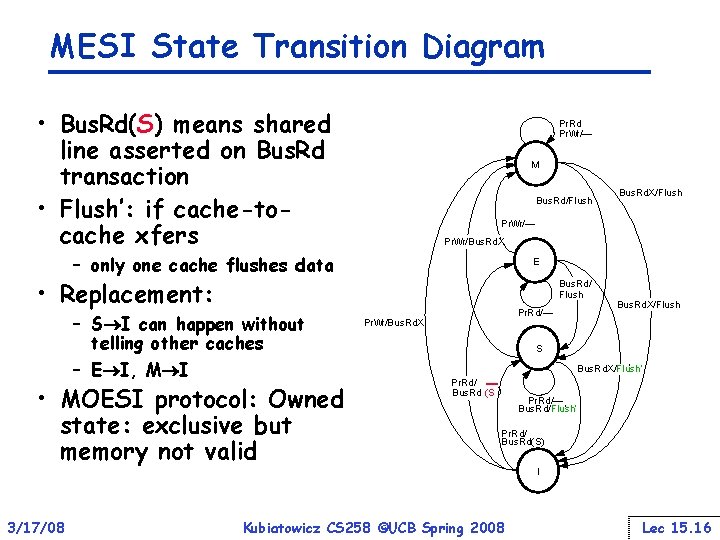

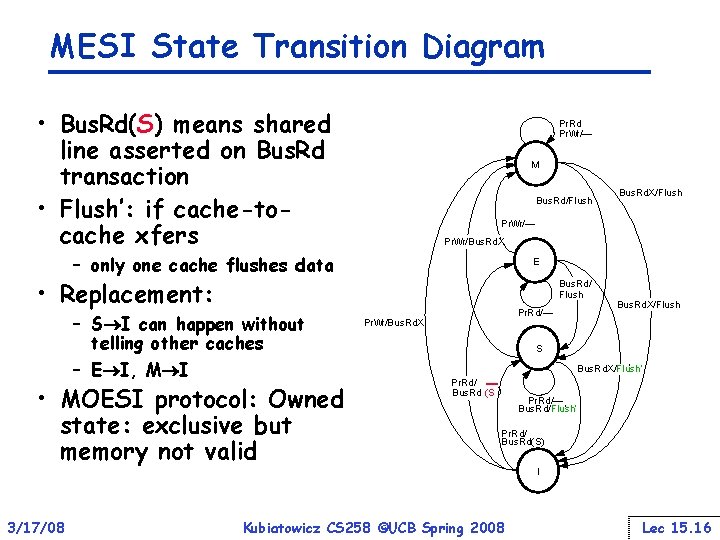

MESI State Transition Diagram • Bus. Rd(S) means shared line asserted on Bus. Rd transaction • Flush’: if cache-tocache xfers Pr. Rd Pr. Wr/— M Bus. Rd/Flush Pr. Wr/— Pr. Wr/Bus. Rd. X – only one cache flushes data E • Replacement: Bus. Rd/ Flush – S I can happen without telling other caches – E I, M I • MOESI protocol: Owned state: exclusive but memory not valid 3/17/08 Bus. Rd. X/Flush Pr. Rd/— Pr. Wr/Bus. Rd. X/Flush S ¢ Bus. Rd. X/Flush’ Pr. Rd/ Bus. Rd (S ) Pr. Rd/— ¢ Bus. Rd/Flush’ Pr. Rd/ Bus. Rd(S) Kubiatowicz CS 258 ©UCB Spring 2008 I Lec 15. 16

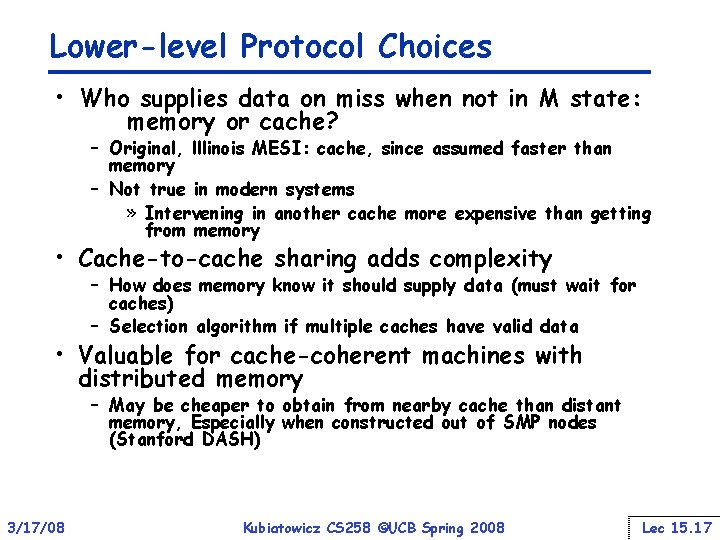

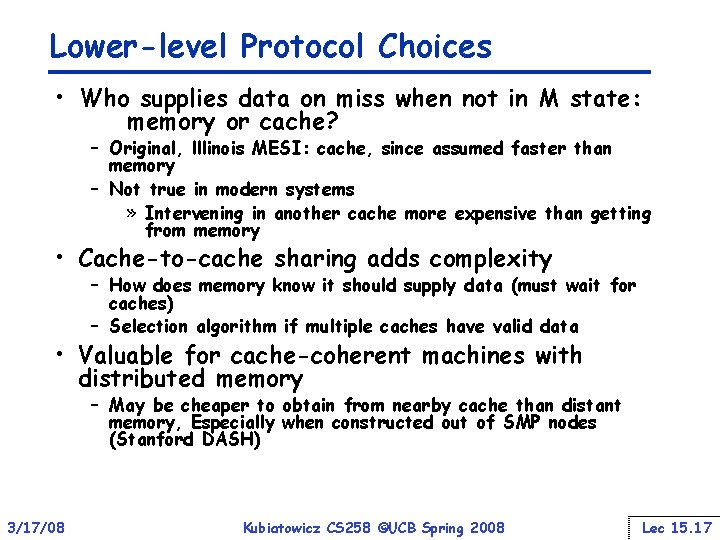

Lower-level Protocol Choices • Who supplies data on miss when not in M state: memory or cache? – Original, lllinois MESI: cache, since assumed faster than memory – Not true in modern systems » Intervening in another cache more expensive than getting from memory • Cache-to-cache sharing adds complexity – How does memory know it should supply data (must wait for caches) – Selection algorithm if multiple caches have valid data • Valuable for cache-coherent machines with distributed memory – May be cheaper to obtain from nearby cache than distant memory, Especially when constructed out of SMP nodes (Stanford DASH) 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 17

Update Protocols • If data is to be communicated between processors, invalidate protocols seem inefficient • consider shared flag – p 0 waits for it to be zero, then does work and sets it one – p 1 waits for it to be one, then does work and sets it zero • how many transactions? 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 18

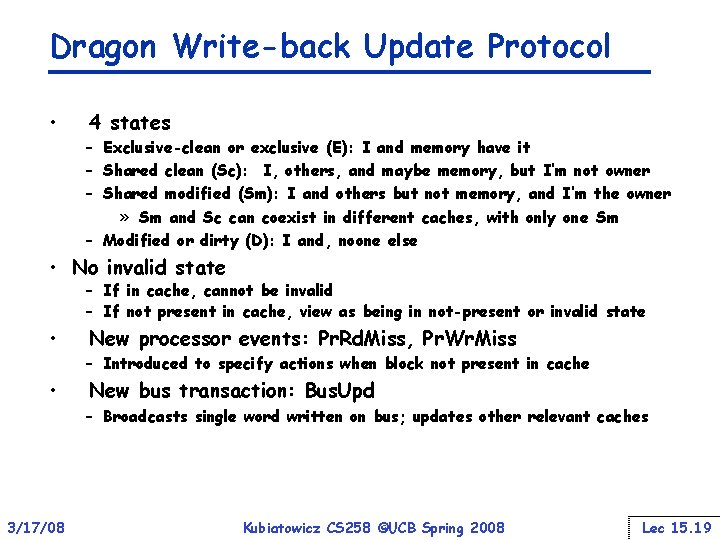

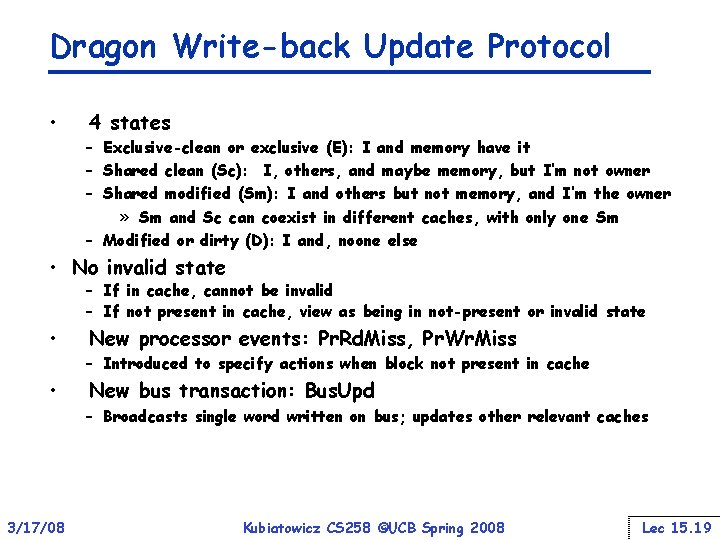

Dragon Write-back Update Protocol • 4 states – Exclusive-clean or exclusive (E): I and memory have it – Shared clean (Sc): I, others, and maybe memory, but I’m not owner – Shared modified (Sm): I and others but not memory, and I’m the owner » Sm and Sc can coexist in different caches, with only one Sm – Modified or dirty (D): I and, noone else • No invalid state – If in cache, cannot be invalid – If not present in cache, view as being in not-present or invalid state • New processor events: Pr. Rd. Miss, Pr. Wr. Miss – Introduced to specify actions when block not present in cache • New bus transaction: Bus. Upd – Broadcasts single word written on bus; updates other relevant caches 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 19

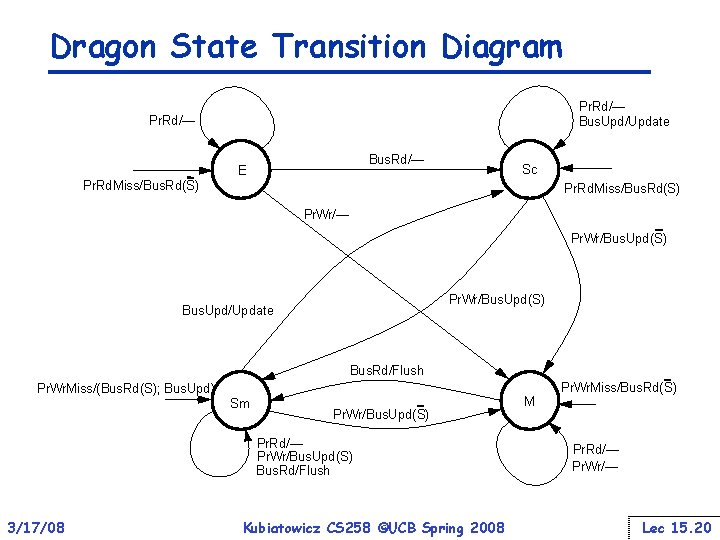

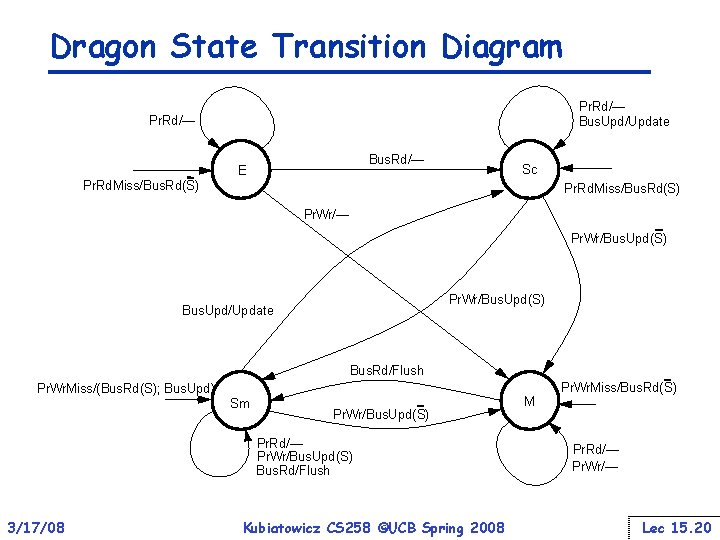

Dragon State Transition Diagram Pr. Rd/— Bus. Upd/Update Pr. Rd/— Bus. Rd/— E Sc Pr. Rd. Miss/Bus. Rd(S) Pr. Wr/— Pr. Wr/Bus. Upd(S) Bus. Upd/Update Bus. Rd/Flush Pr. Wr. Miss/(Bus. Rd(S); Bus. Upd) Sm Pr. Wr/Bus. Upd(S) Pr. Rd/— Pr. Wr/Bus. Upd(S) Bus. Rd/Flush 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 M Pr. Wr. Miss/Bus. Rd(S) Pr. Rd/— Pr. Wr/— Lec 15. 20

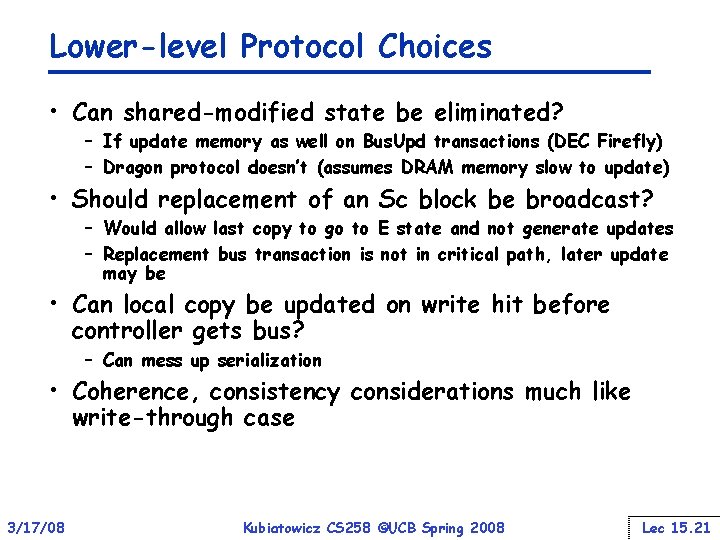

Lower-level Protocol Choices • Can shared-modified state be eliminated? – If update memory as well on Bus. Upd transactions (DEC Firefly) – Dragon protocol doesn’t (assumes DRAM memory slow to update) • Should replacement of an Sc block be broadcast? – Would allow last copy to go to E state and not generate updates – Replacement bus transaction is not in critical path, later update may be • Can local copy be updated on write hit before controller gets bus? – Can mess up serialization • Coherence, consistency considerations much like write-through case 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 21

Assessing Protocol Tradeoffs • Tradeoffs affected by technology characteristics and design complexity • Part and part science – Art: experience, intuition and aesthetics of designers – Science: Workload-driven evaluation for cost-performance » want a balanced system: no expensive resource heavily underutilized 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 22

Summary • Shared-memory machine – All communication is implicit, through loads and stores – Parallelism introduces a bunch of overheads over uniprocessor • Memory Coherence: – Writes to a given location eventually propagated – Writes to a given location seen in same order by everyone • Memory Consistency: – Constraints on ordering between processors and locations • Sequential Consistency: – For every parallel execution, there exists a serial interleaving 3/17/08 Kubiatowicz CS 258 ©UCB Spring 2008 Lec 15. 23