CS 203 Advanced Computer Architecture Simulators Why use

- Slides: 15

CS 203 – Advanced Computer Architecture Simulators

Why use simulators? Designing and fabricating chips are expensive Would take years to test new microarchitecture design Abstract performance/queuing models are simplistic Require a middle-ground Fast, accurate, configurable 2

Why use simulators? Leverage faster, more flexible S/W development cycles Permits more design space exploration Facilitates validation before H/W becomes available Level of abstraction can be throttled to design task Possible to increase/improve system instrumentation Adapted from Simple. Scalar Tutorial 3

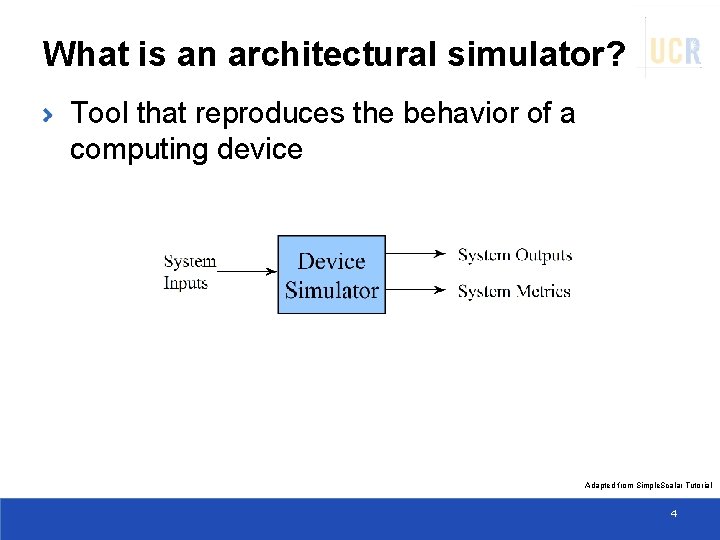

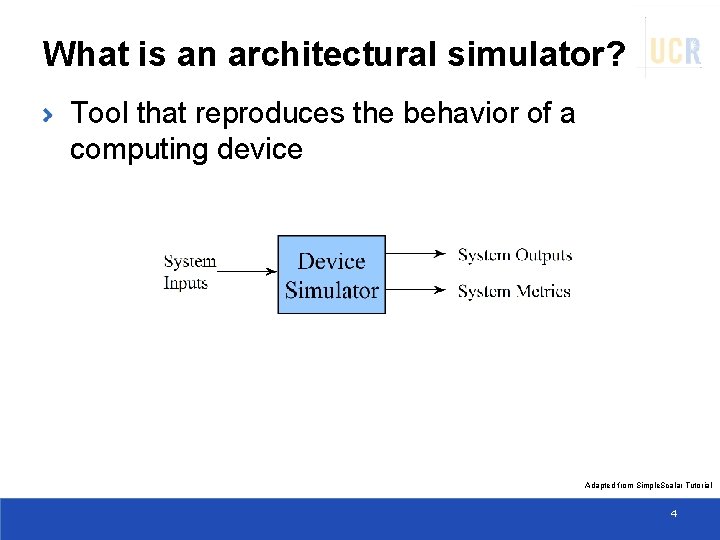

What is an architectural simulator? Tool that reproduces the behavior of a computing device Adapted from Simple. Scalar Tutorial 4

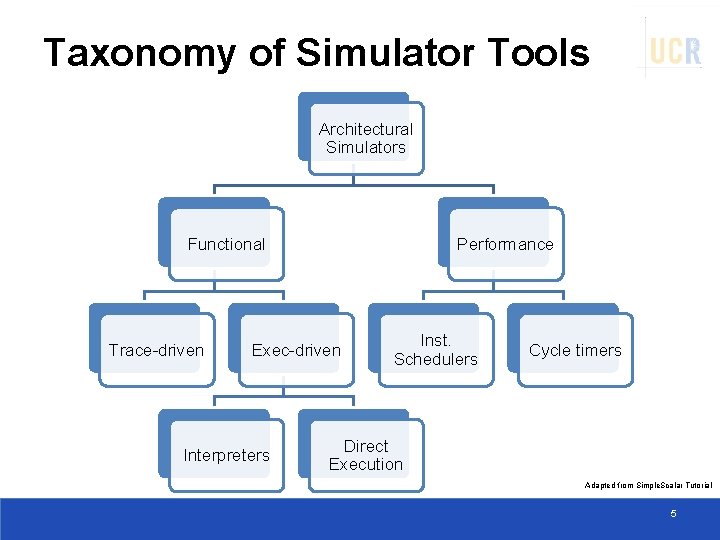

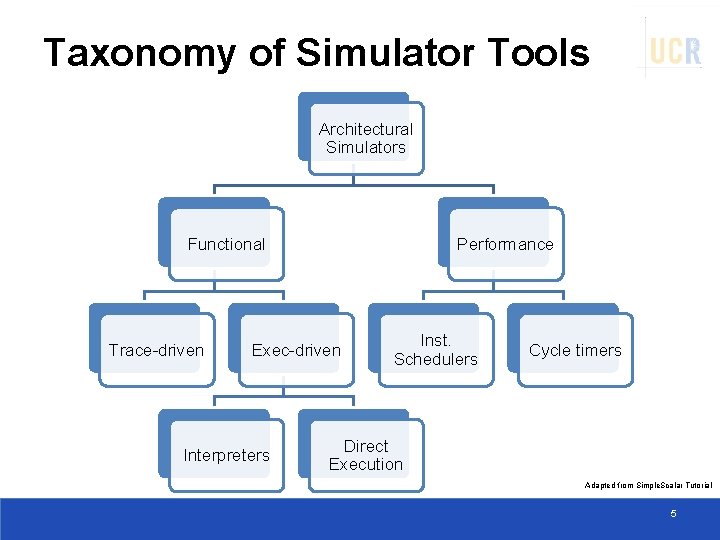

Taxonomy of Simulator Tools Architectural Simulators Functional Trace-driven Performance Exec-driven Interpreters Inst. Schedulers Cycle timers Direct Execution Adapted from Simple. Scalar Tutorial 5

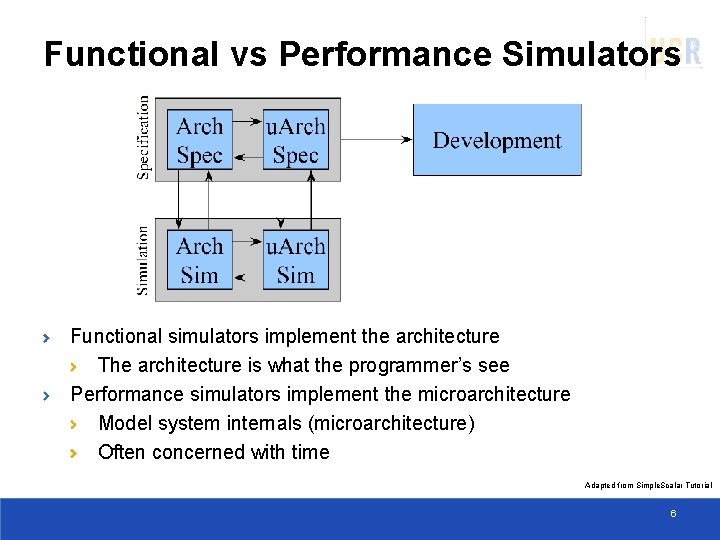

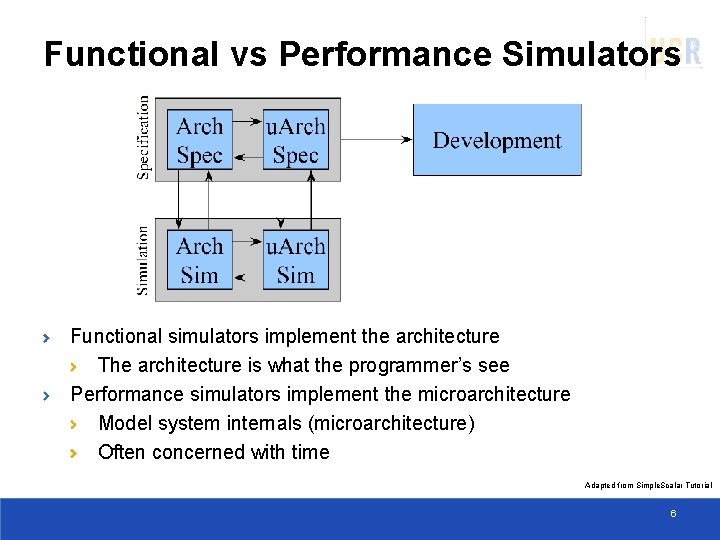

Functional vs Performance Simulators Functional simulators implement the architecture The architecture is what the programmer’s see Performance simulators implement the microarchitecture Model system internals (microarchitecture) Often concerned with time Adapted from Simple. Scalar Tutorial 6

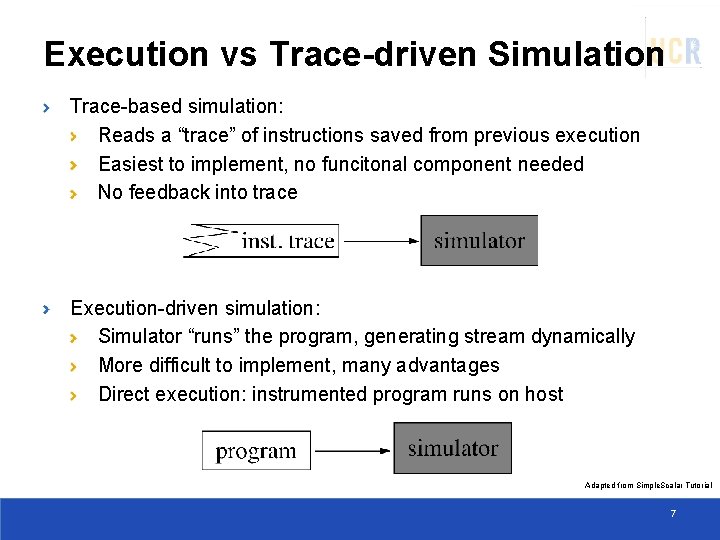

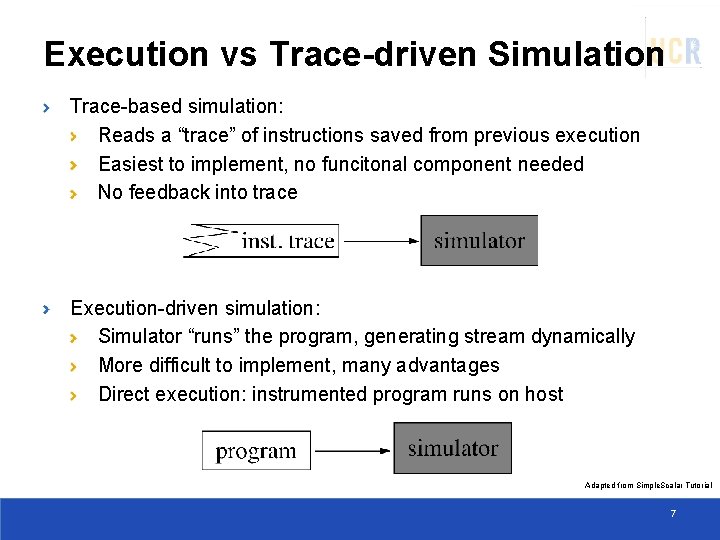

Execution vs Trace-driven Simulation Trace-based simulation: Reads a “trace” of instructions saved from previous execution Easiest to implement, no funcitonal component needed No feedback into trace Execution-driven simulation: Simulator “runs” the program, generating stream dynamically More difficult to implement, many advantages Direct execution: instrumented program runs on host Adapted from Simple. Scalar Tutorial 7

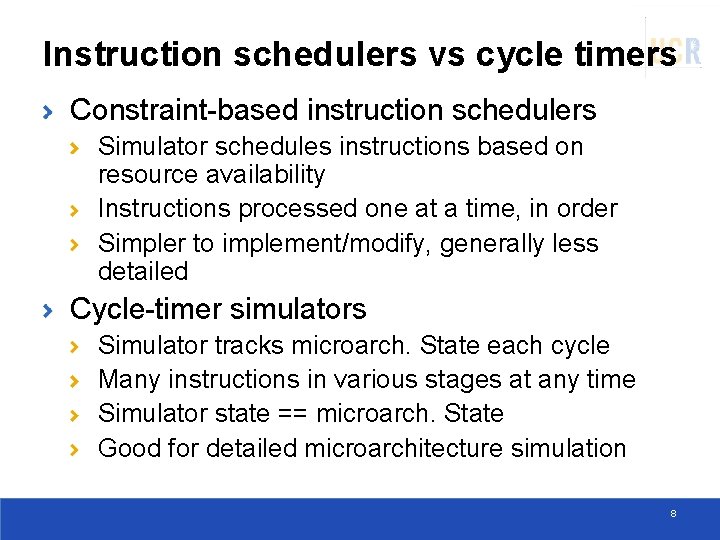

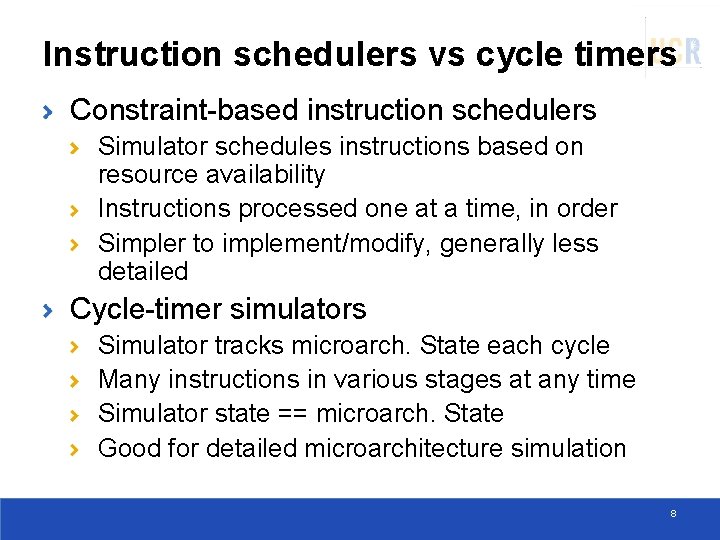

Instruction schedulers vs cycle timers Constraint-based instruction schedulers Simulator schedules instructions based on resource availability Instructions processed one at a time, in order Simpler to implement/modify, generally less detailed Cycle-timer simulators Simulator tracks microarch. State each cycle Many instructions in various stages at any time Simulator state == microarch. State Good for detailed microarchitecture simulation 8

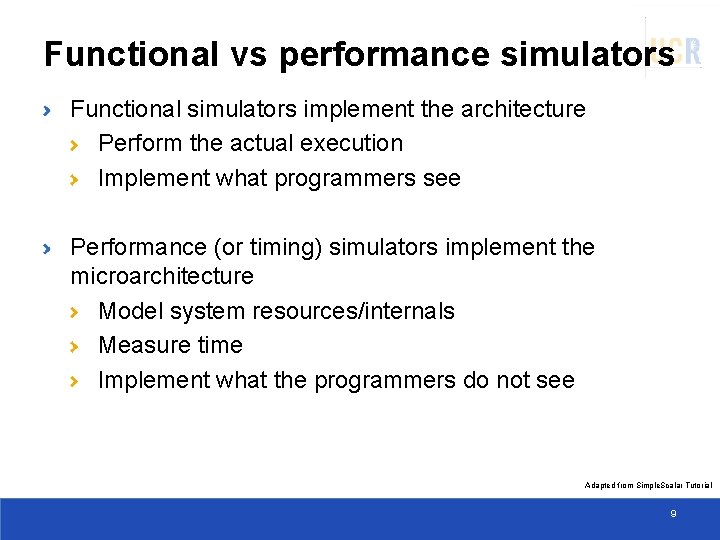

Functional vs performance simulators Functional simulators implement the architecture Perform the actual execution Implement what programmers see Performance (or timing) simulators implement the microarchitecture Model system resources/internals Measure time Implement what the programmers do not see Adapted from Simple. Scalar Tutorial 9

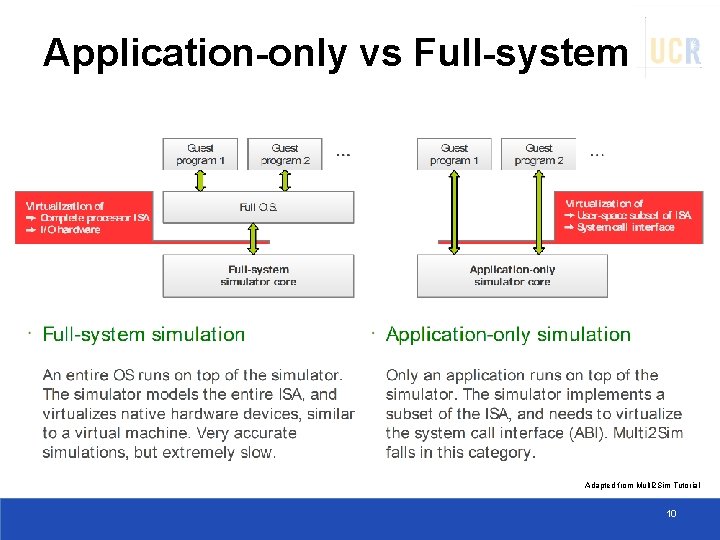

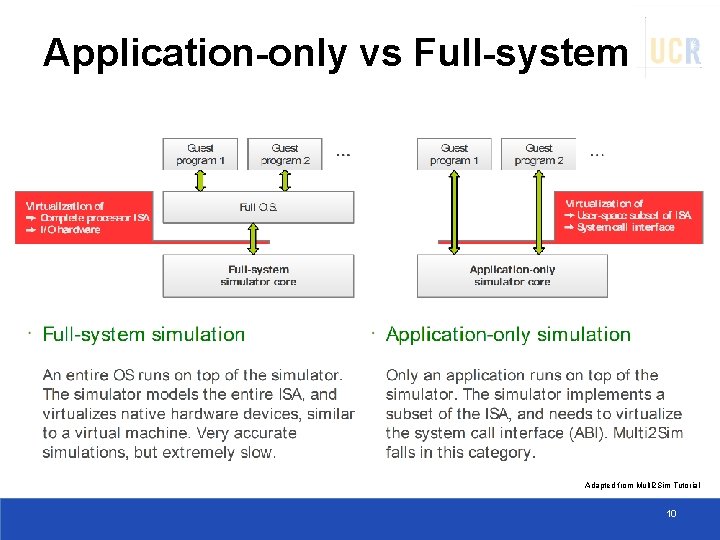

Application-only vs Full-system Adapted from Multi 2 Sim Tutorial 10

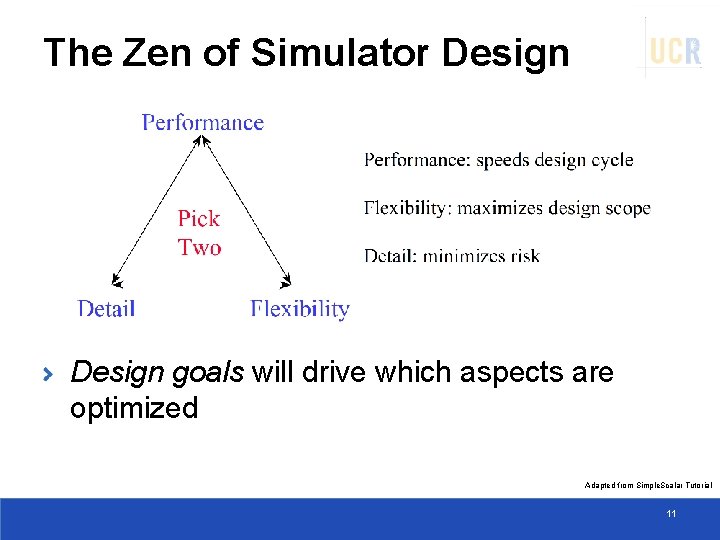

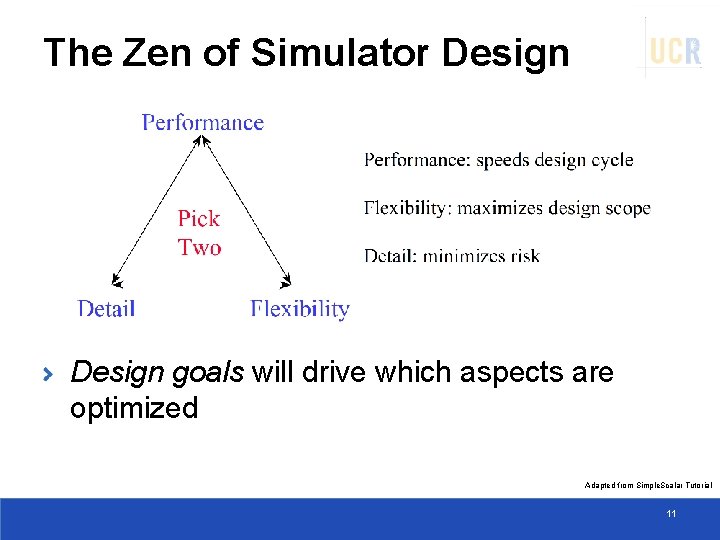

The Zen of Simulator Design goals will drive which aspects are optimized Adapted from Simple. Scalar Tutorial 11

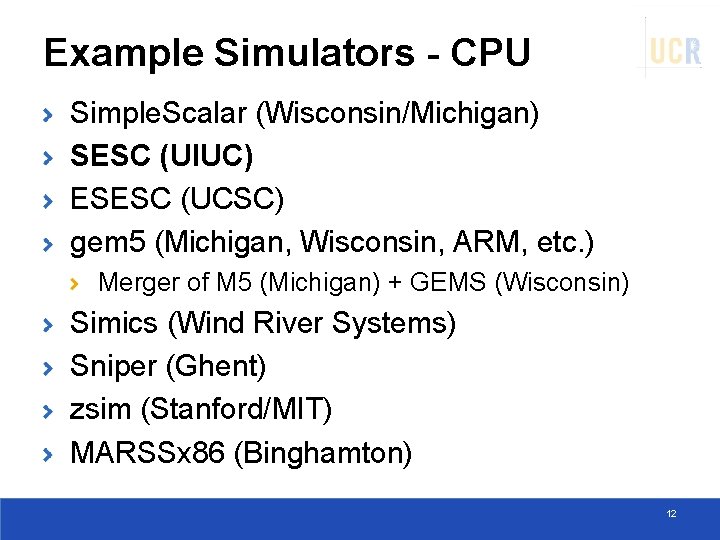

Example Simulators - CPU Simple. Scalar (Wisconsin/Michigan) SESC (UIUC) ESESC (UCSC) gem 5 (Michigan, Wisconsin, ARM, etc. ) Merger of M 5 (Michigan) + GEMS (Wisconsin) Simics (Wind River Systems) Sniper (Ghent) zsim (Stanford/MIT) MARSSx 86 (Binghamton) 12

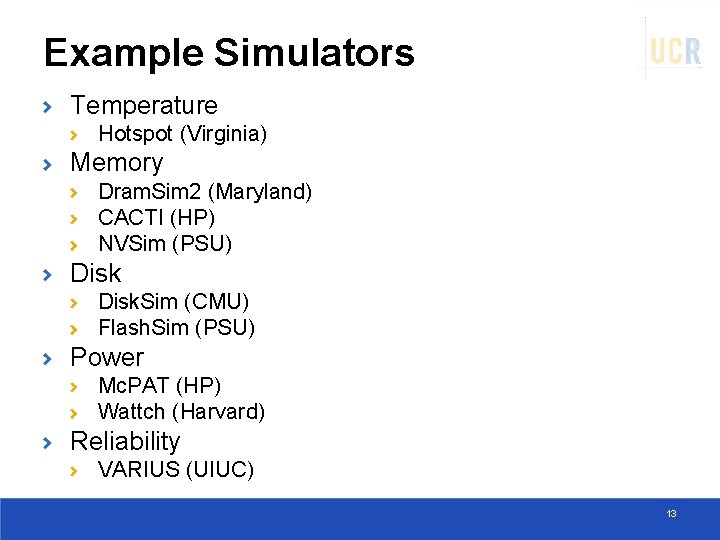

Example Simulators Temperature Hotspot (Virginia) Memory Dram. Sim 2 (Maryland) CACTI (HP) NVSim (PSU) Disk. Sim (CMU) Flash. Sim (PSU) Power Mc. PAT (HP) Wattch (Harvard) Reliability VARIUS (UIUC) 13

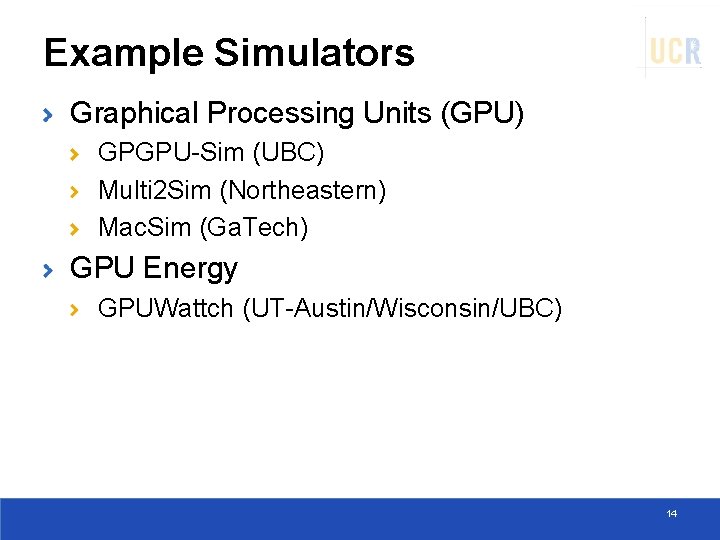

Example Simulators Graphical Processing Units (GPU) GPGPU-Sim (UBC) Multi 2 Sim (Northeastern) Mac. Sim (Ga. Tech) GPU Energy GPUWattch (UT-Austin/Wisconsin/UBC) 14

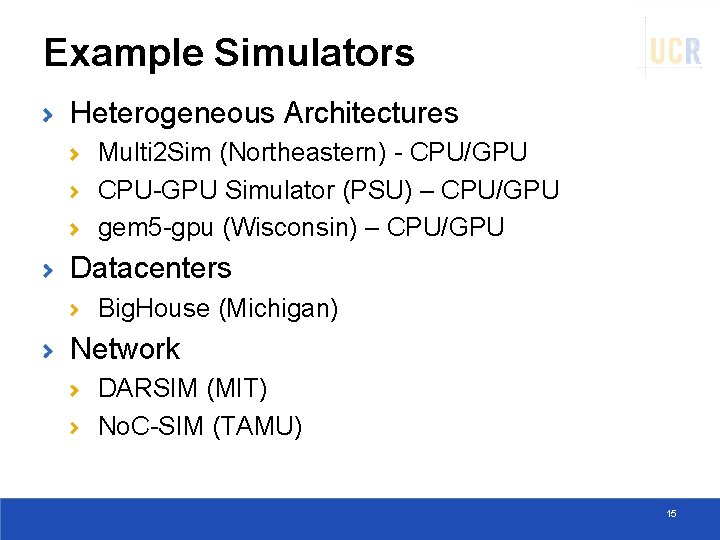

Example Simulators Heterogeneous Architectures Multi 2 Sim (Northeastern) - CPU/GPU CPU-GPU Simulator (PSU) – CPU/GPU gem 5 -gpu (Wisconsin) – CPU/GPU Datacenters Big. House (Michigan) Network DARSIM (MIT) No. C-SIM (TAMU) 15