CS 194 Mishali Naik Advisor Professor Glenn D

![Prior Work Thread migration techniques [1] Ways of enhancing the performance of virtual machines Prior Work Thread migration techniques [1] Ways of enhancing the performance of virtual machines](https://slidetodoc.com/presentation_image_h2/034fa09fb14a2921f40cf87d4d2558e5/image-6.jpg)

- Slides: 13

CS 194 Mishali Naik Advisor: Professor Glenn D. Reinman

Motivation Chip multiprocessors being the emerging trend in technology, need to find alternative ways of integrating hardware and software. Extending the concept of “Virtualization” to hardware. Virtualization – to design an interface by hiding the underlying resources.

Diverse range of applications, that have varying demands for hardware resources. Computation intensive applications. Applications with big memory foot print. Applications with high ILP.

Introduction To find optimal mappings between statically partitioned hardware resources and software threads that: Satisfies the performance of various applications. Minimizes power consumption and heat dissipation.

Problems Utilization of a particular chip resource varies from application to application, and also varies between phases of application. Overhead of maintaining and implementing the mapping should not be significant.

![Prior Work Thread migration techniques 1 Ways of enhancing the performance of virtual machines Prior Work Thread migration techniques [1] Ways of enhancing the performance of virtual machines](https://slidetodoc.com/presentation_image_h2/034fa09fb14a2921f40cf87d4d2558e5/image-6.jpg)

Prior Work Thread migration techniques [1] Ways of enhancing the performance of virtual machines [2] Helper Engines [3]

STUDY First step – to build simulator infrastructure. Second step – explore the various hardware configurations. Third step – map the resources to the applications.

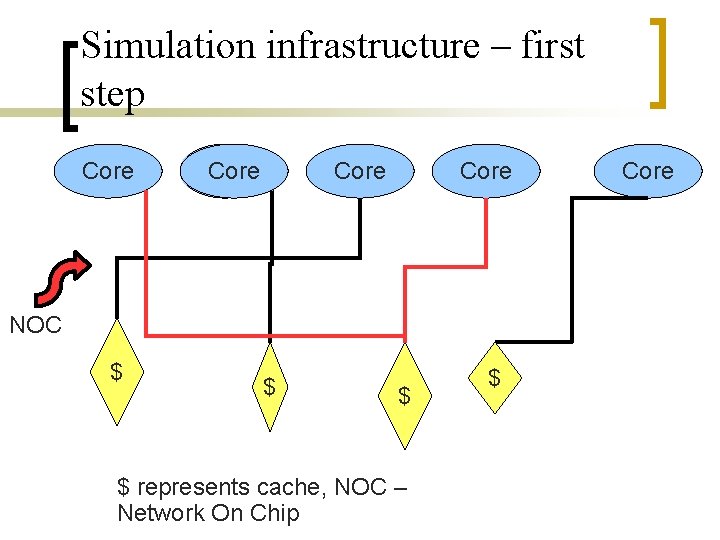

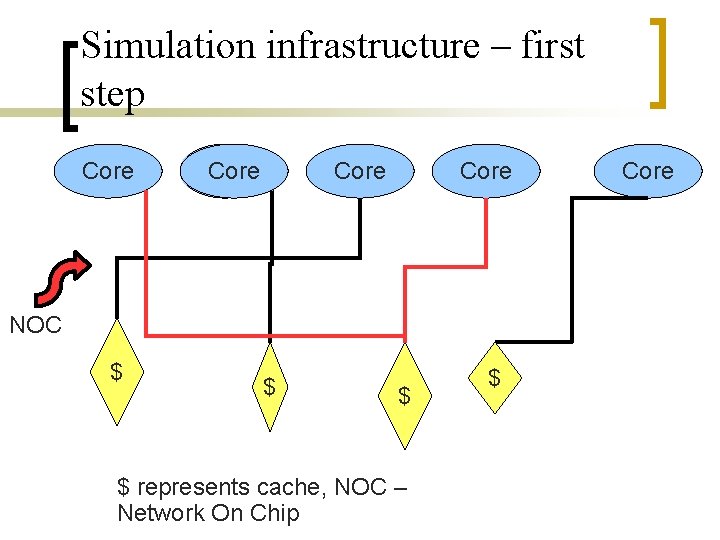

Simulation infrastructure – first step Core e Core NOC $ $ represents cache, NOC – Network On Chip $ Core

Second step This infrastructure will be used to explore the hardware configurations required for different sets of applications. Various configurations of hardware resources can be explored, for example - size and associativity of cache.

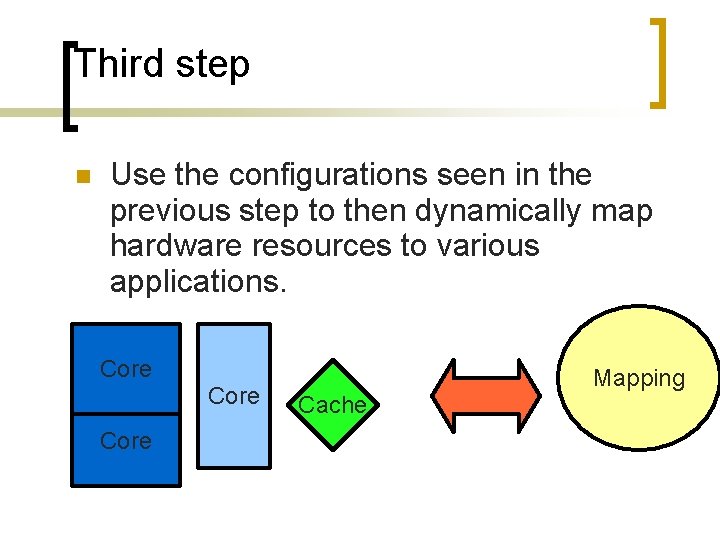

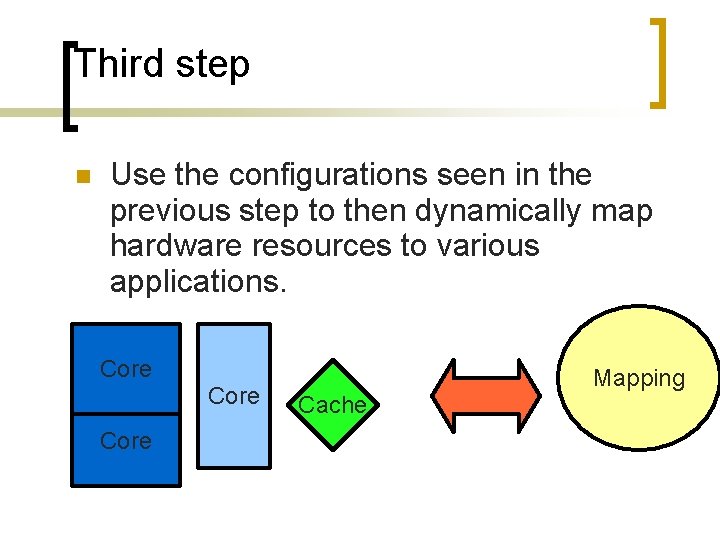

Third step Use the configurations seen in the previous step to then dynamically map hardware resources to various applications. Core Mapping Cache

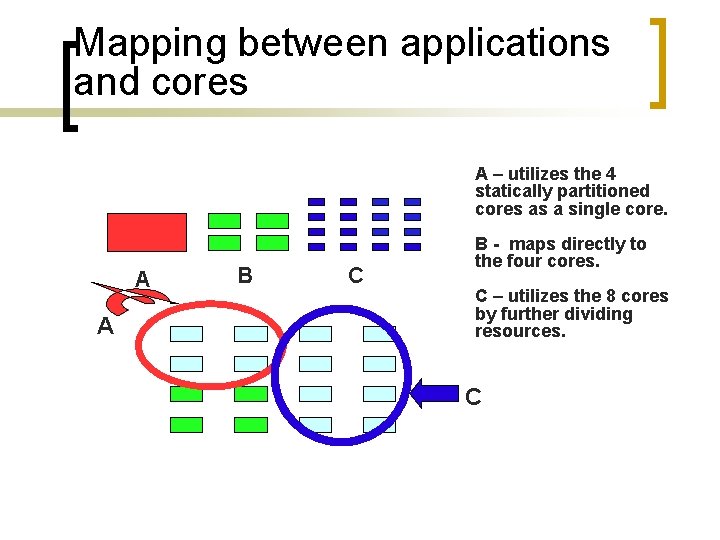

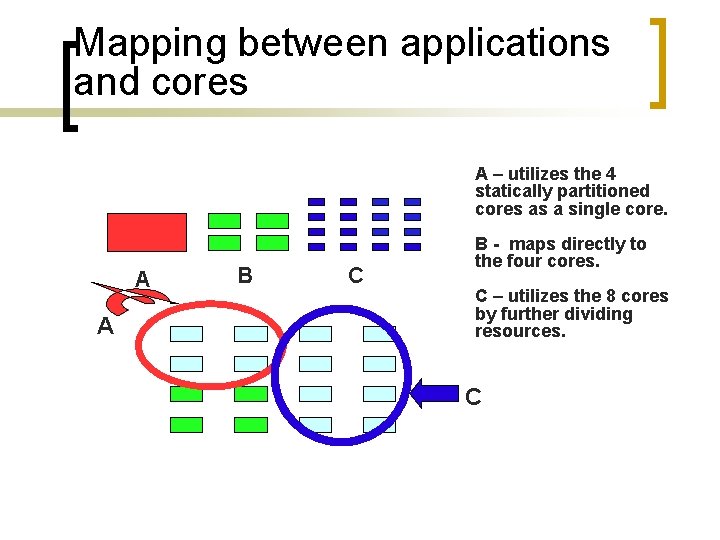

Mapping between applications and cores A – utilizes the 4 statically partitioned cores as a single core. A A B C B - maps directly to the four cores. C – utilizes the 8 cores by further dividing resources. C

Tools and Benchmarks SESC – microprocessor architectural simulator, includes a cycle accurate timing model SPLASH – Scientific applications SPEC CPU Commercial applications

References Koushik Chakraborty, Philip Wells, Gurindar Sohi, Computation Spreading: Employing Hardware Migration to Specialize CMO Cores On-the-fly, ASPLOS 2006. Shiliang Hu, James Smith, Reducing Startup Time in Co-Designed Virtual Machines, ISCA 2006. Anahita Shayesteh, Glenn Reinman, Norm Jouppi, Suleyman Sair, and Tim Sherwood. Improving the Performance and Power Efficiency of Shared Helpers in CMPs. International Conference on Compilers, Architecture, and Synthesis for Embedded Systems, Oct 2006.