CS 184 b Computer Architecture Single Threaded Architecture

![CS 184 b: Computer Architecture [Single Threaded Architecture: abstractions, quantification, and optimizations] Day 5: CS 184 b: Computer Architecture [Single Threaded Architecture: abstractions, quantification, and optimizations] Day 5:](https://slidetodoc.com/presentation_image_h/cb6f4f6b2d667a70d5fdff92a5f42908/image-1.jpg)

CS 184 b: Computer Architecture [Single Threaded Architecture: abstractions, quantification, and optimizations] Day 5: January 17, 2000 Pipelining ISA Processor Execution Caltech CS 184 b Winter 2001 -De. Hon 1

Today • Pipelined Processor Issue – Hazards • structural • data • control (next time) – accommodating – impact • RISC/CISC wrapup (maybe) • Admin question: this time good next term? Caltech CS 184 b Winter 2001 -De. Hon 2

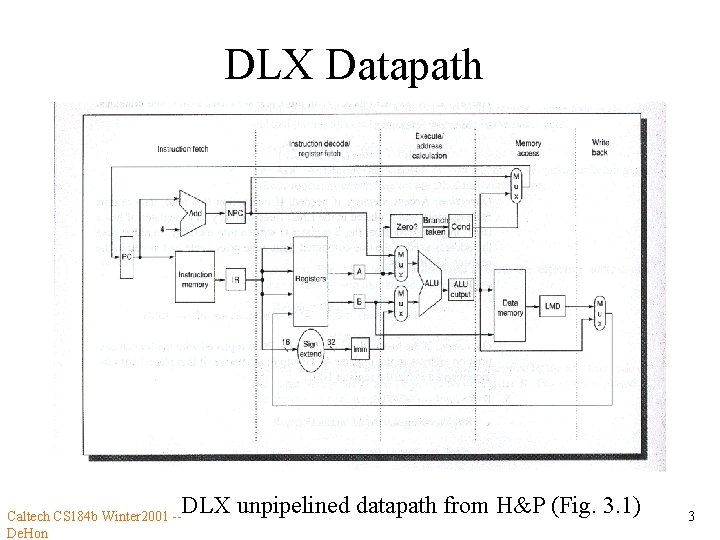

DLX Datapath DLX unpipelined datapath from H&P (Fig. 3. 1) Caltech CS 184 b Winter 2001 -De. Hon 3

DLX Model Behavior • • Read Registers Perform primitive ALU Op Read/Write memory Write register result Caltech CS 184 b Winter 2001 -De. Hon 4

Pipeline? Caltech CS 184 b Winter 2001 -De. Hon 5

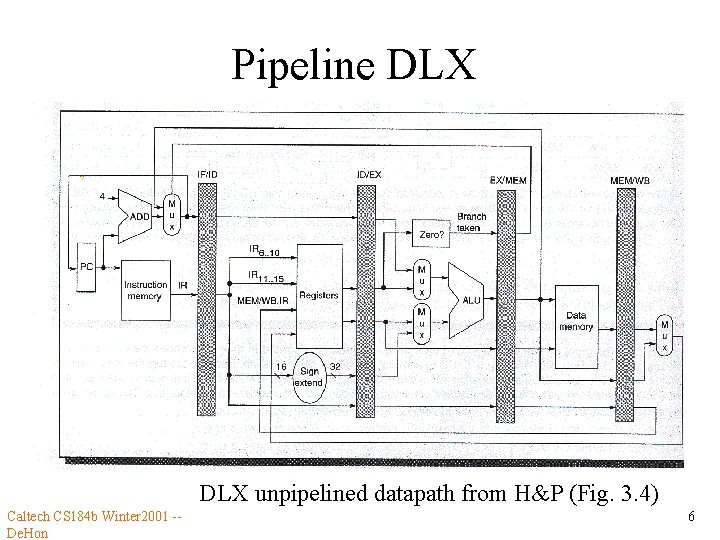

Pipeline DLX unpipelined datapath from H&P (Fig. 3. 4) Caltech CS 184 b Winter 2001 -De. Hon 6

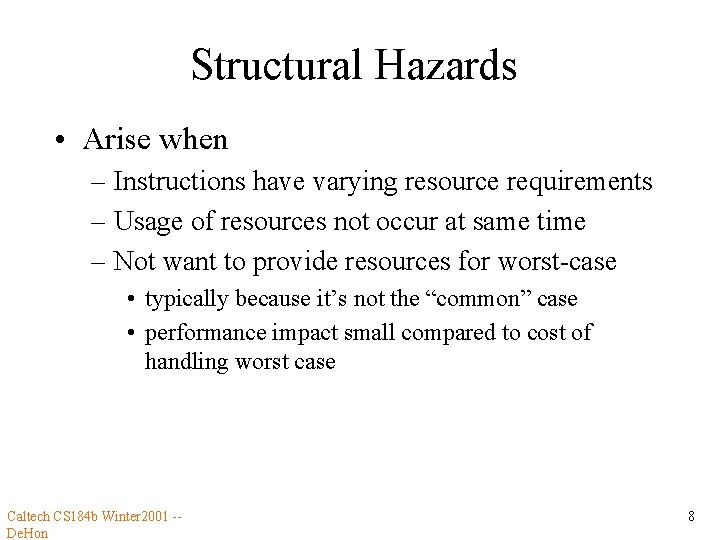

Hazards • Structural (resource bound) • Data (value timing) • Control (knowing where to go next) Caltech CS 184 b Winter 2001 -De. Hon 7

Structural Hazards • Arise when – Instructions have varying resource requirements – Usage of resources not occur at same time – Not want to provide resources for worst-case • typically because it’s not the “common” case • performance impact small compared to cost of handling worst case Caltech CS 184 b Winter 2001 -De. Hon 8

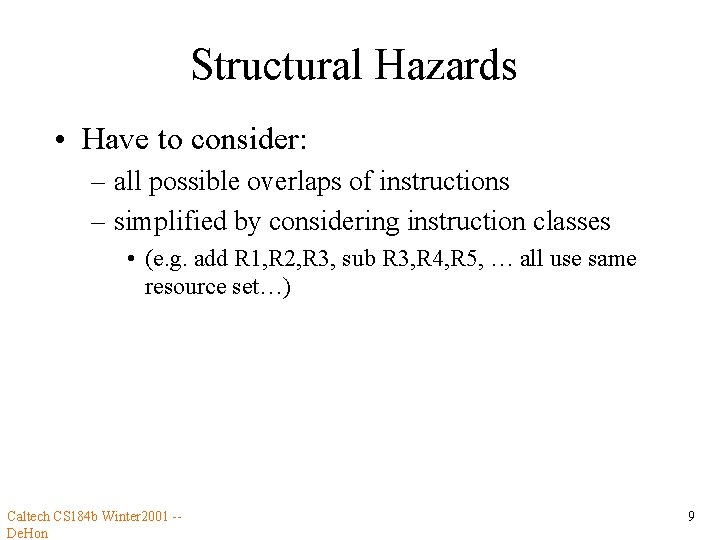

Structural Hazards • Have to consider: – all possible overlaps of instructions – simplified by considering instruction classes • (e. g. add R 1, R 2, R 3, sub R 3, R 4, R 5, … all use same resource set…) Caltech CS 184 b Winter 2001 -De. Hon 9

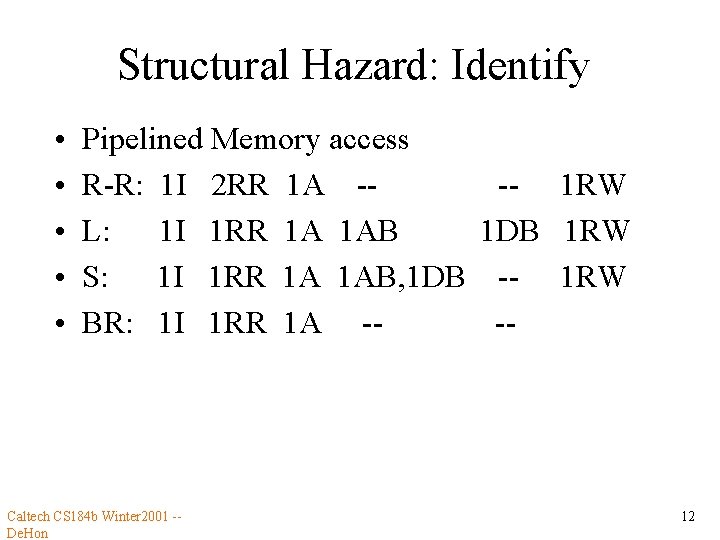

Structural Hazard: Identify • Identify by: – looking at instruction (class) resource usage in pipeline • Register-Register Op: – IF - I-mem port – ID - 2 register read ports – EXU - ALU – MEM - --– WB - 1 register write port Caltech CS 184 b Winter 2001 -De. Hon 10

Structural Hazard: Identify • R-R: 1 I 2 RR 1 A -1 RW • L/S: 1 I 1 RR 1 A 1 AB, 1 DB 1 RW • BR: 1 I 1 RR 1 A -- • Conflicts: – standard DLX – RF has 1 R, 1 RW port Caltech CS 184 b Winter 2001 -De. Hon 11

Structural Hazard: Identify • • • Pipelined Memory access R-R: 1 I 2 RR 1 A --- 1 RW L: 1 I 1 RR 1 A 1 AB 1 DB 1 RW S: 1 I 1 RR 1 A 1 AB, 1 DB -- 1 RW BR: 1 I 1 RR 1 A --- Caltech CS 184 b Winter 2001 -De. Hon 12

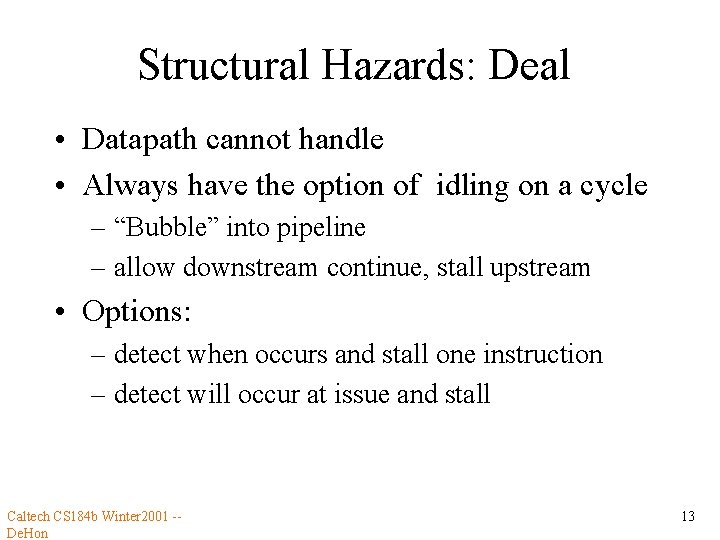

Structural Hazards: Deal • Datapath cannot handle • Always have the option of idling on a cycle – “Bubble” into pipeline – allow downstream continue, stall upstream • Options: – detect when occurs and stall one instruction – detect will occur at issue and stall Caltech CS 184 b Winter 2001 -De. Hon 13

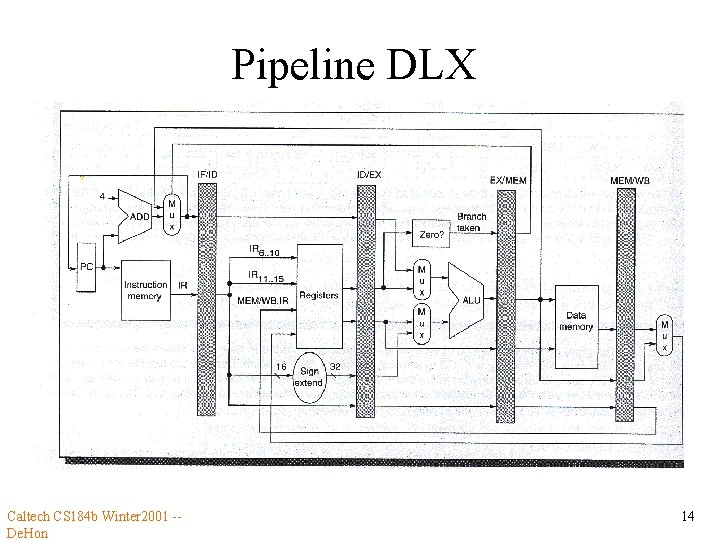

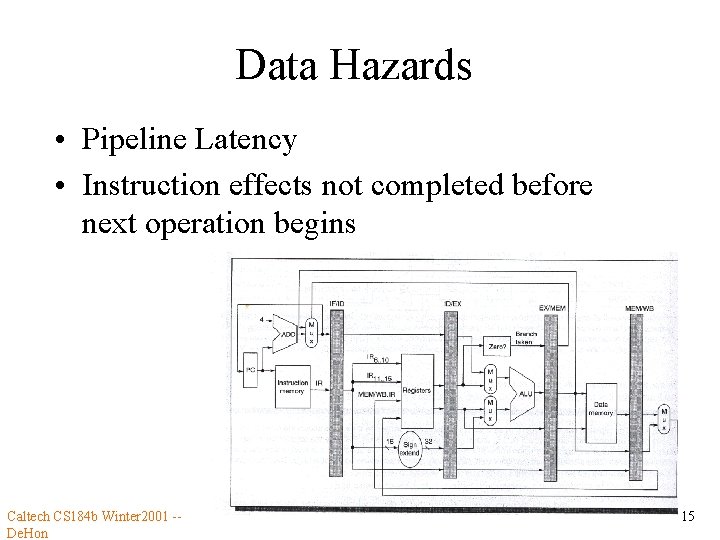

Pipeline DLX Caltech CS 184 b Winter 2001 -De. Hon 14

Data Hazards • Pipeline Latency • Instruction effects not completed before next operation begins Caltech CS 184 b Winter 2001 -De. Hon 15

Data Hazard: Example • ADD R 1, R 2, R 3 • XOR R 4, R 1, R 5 Caltech CS 184 b Winter 2001 -De. Hon 16

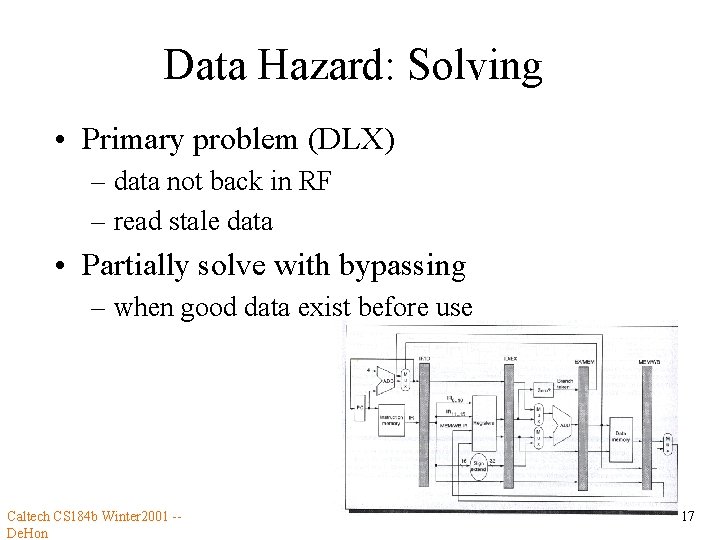

Data Hazard: Solving • Primary problem (DLX) – data not back in RF – read stale data • Partially solve with bypassing – when good data exist before use Caltech CS 184 b Winter 2001 -De. Hon 17

![Data Hazard: Solving • [todo: draw DP with bypass muxes] Caltech CS 184 b Data Hazard: Solving • [todo: draw DP with bypass muxes] Caltech CS 184 b](http://slidetodoc.com/presentation_image_h/cb6f4f6b2d667a70d5fdff92a5f42908/image-18.jpg)

Data Hazard: Solving • [todo: draw DP with bypass muxes] Caltech CS 184 b Winter 2001 -De. Hon 18

Data Hazard • Note: since ops may stall, interrupt, resume – cannot decide how to set bypass muxes in ID stages – have to determine based on state of pipeline Caltech CS 184 b Winter 2001 -De. Hon 19

Data Hazard • Not all cases can bypass – if data not available anywhere, yet. . . – e. g. • LW R 1, 4(R 2) • ADD R 3, R 1, R 4 Caltech CS 184 b Winter 2001 -De. Hon 20

Model/Common Case • Common/simple case • Implementation transparency • Could have slowed the initiation interval for all ops • OR could have said can’t use value for number of cycles • But, only few sequences/cases problematic – let rest run faster Caltech CS 184 b Winter 2001 -De. Hon 21

Types of Data Hazards • RAW (example seen) • WAW – order of writes transposed going to memory – leave wrong value in memory • WAR – read gets value computed “after” it should have completed Caltech CS 184 b Winter 2001 -De. Hon 22

Compiler • Instruction Scheduling can try to avoid – (making some assumptions about implementation) • Schedule instructions in delay slot – possible when have parallelism/independent tasks • another example where optimize across larger block give tighter results Caltech CS 184 b Winter 2001 -De. Hon 23

Big Ideas • Preserve the (simple, stable) model • While providing high-performance implementation Caltech CS 184 b Winter 2001 -De. Hon 24

Big Ideas • • Ops with different requirements Some cases can run faster than others Fast in simple, common cases Correct in others Caltech CS 184 b Winter 2001 -De. Hon 25

- Slides: 25