CS 121 Digital Logic Design Chapter 3 GateLevel

- Slides: 27

CS 121 Digital Logic Design Chapter 3 Gate-Level Minimization

Outline 3. 1 Introduction 3. 2 The Map Method 3. 3 Four-Variable Map 3. 4 Product of sums simplification 3. 5 Don‘t Care Conditions 3. 7 NAND and NOR Implementaion 3. 8 Other Two-Level Implementaion 3. 9 Exclusive-OR function

3. 7 NAND and NOR Implementation (1 -15) Digital circuits are frequently constructed with NAND or NOR gates rather than with AND and OR gates.

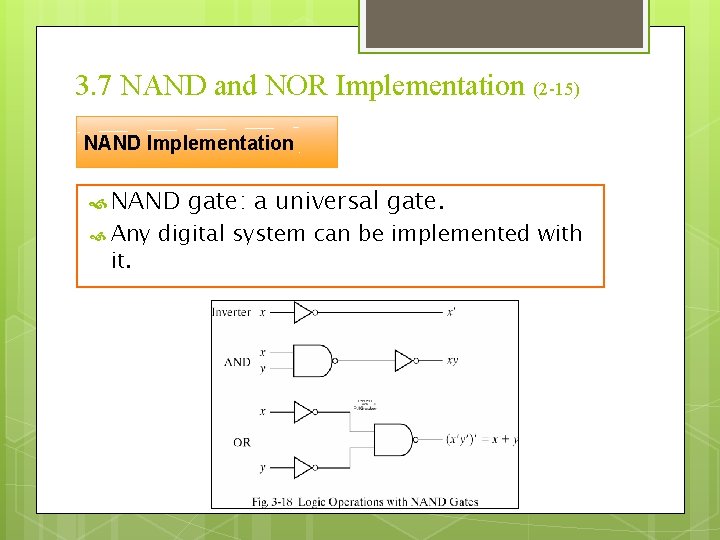

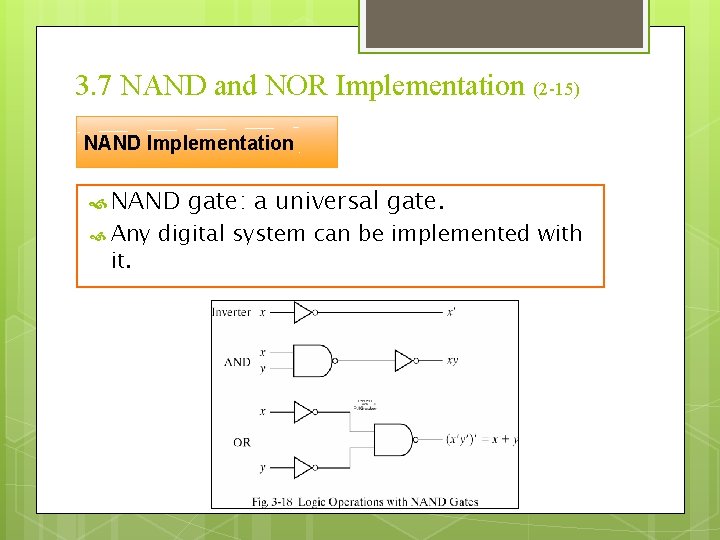

3. 7 NAND and NOR Implementation (2 -15) NAND Implementation NAND Any it. gate: a universal gate. digital system can be implemented with

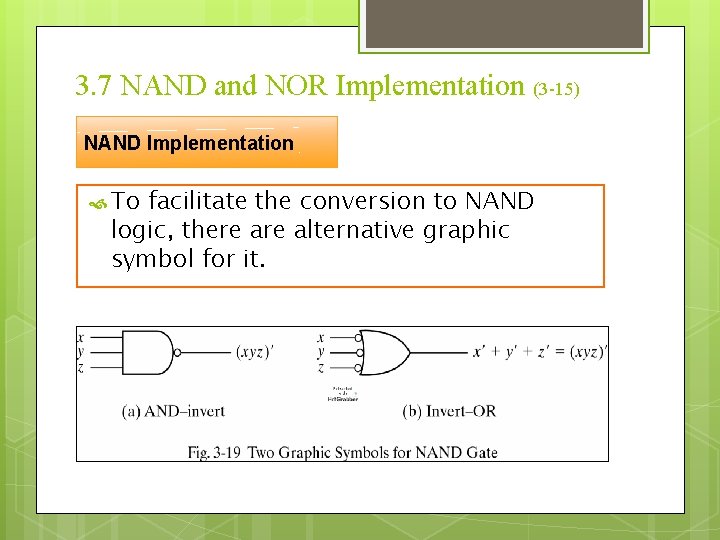

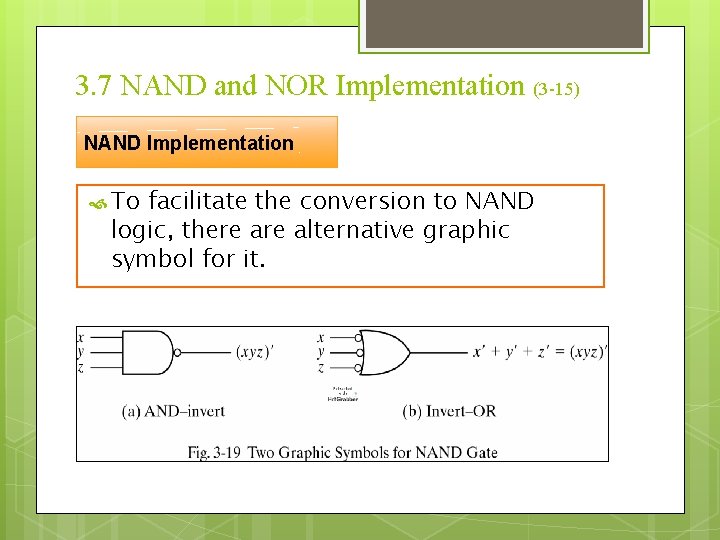

3. 7 NAND and NOR Implementation (3 -15) NAND Implementation To facilitate the conversion to NAND logic, there alternative graphic symbol for it.

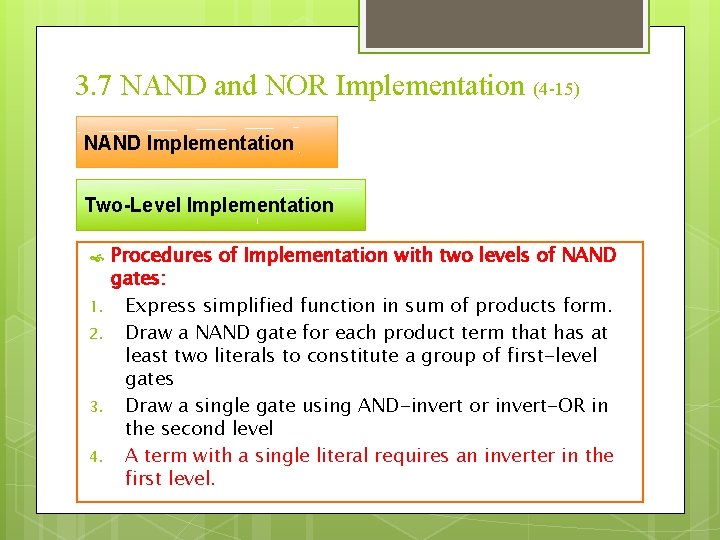

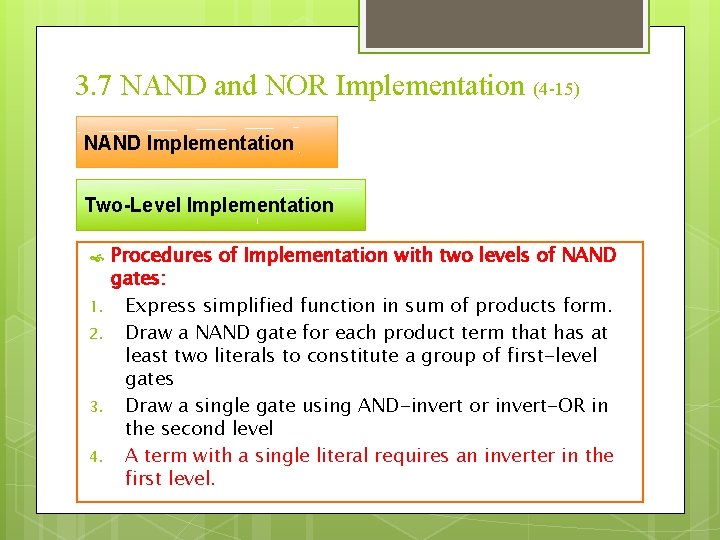

3. 7 NAND and NOR Implementation (4 -15) NAND Implementation Two-Level Implementation 1. 2. 3. 4. Procedures of Implementation with two levels of NAND gates: Express simplified function in sum of products form. Draw a NAND gate for each product term that has at least two literals to constitute a group of first-level gates Draw a single gate using AND-invert or invert-OR in the second level A term with a single literal requires an inverter in the first level.

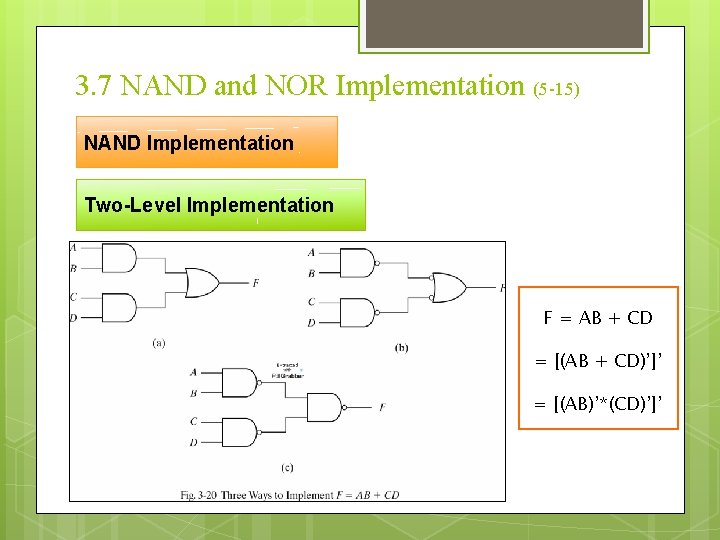

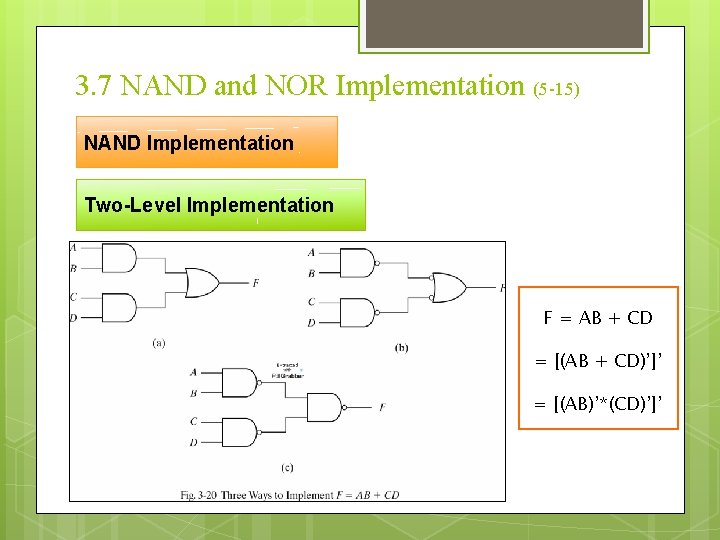

3. 7 NAND and NOR Implementation (5 -15) NAND Implementation Two-Level Implementation F = AB + CD = [(AB + CD)’]’ = [(AB)’*(CD)’]’

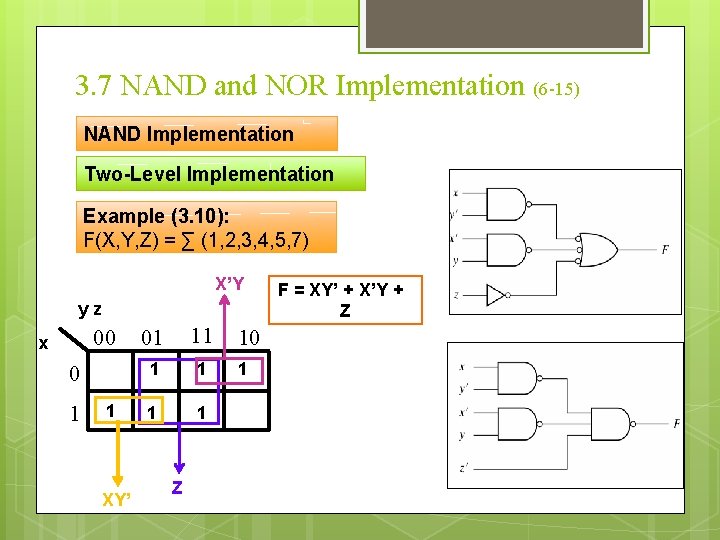

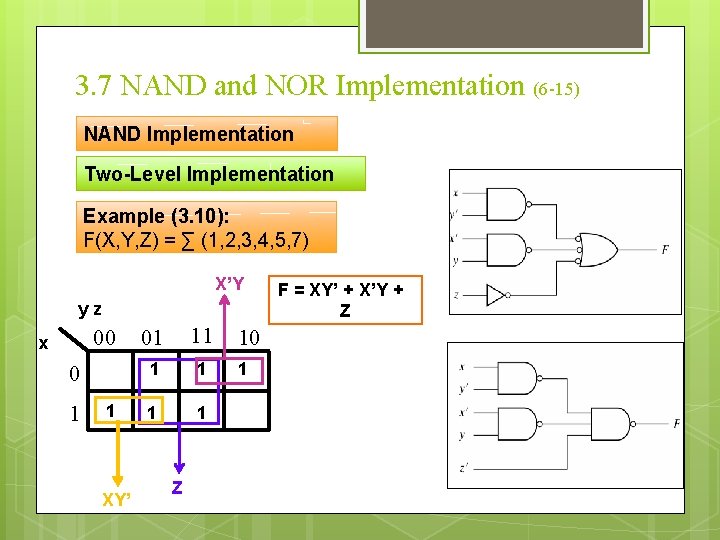

3. 7 NAND and NOR Implementation (6 -15) NAND Implementation Two-Level Implementation Example (3. 10): F(X, Y, Z) = ∑ (1, 2, 3, 4, 5, 7) X’Y yz 00 x 0 1 1 XY’ 01 11 1 1 Z 10 1 F = XY’ + X’Y + Z

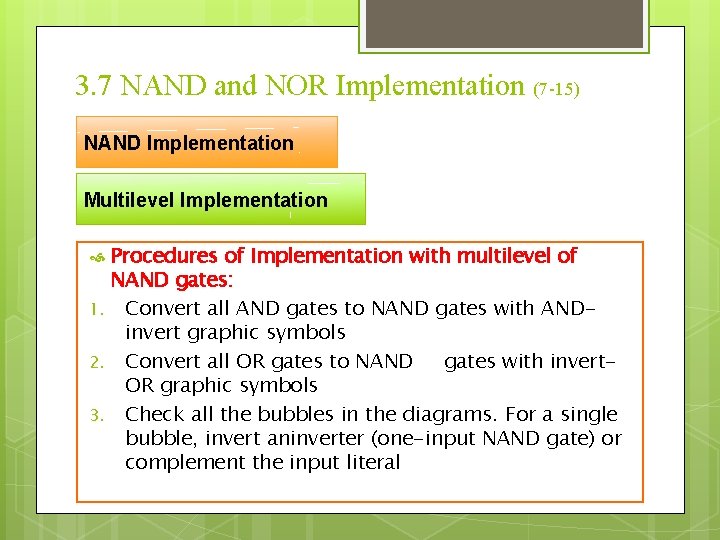

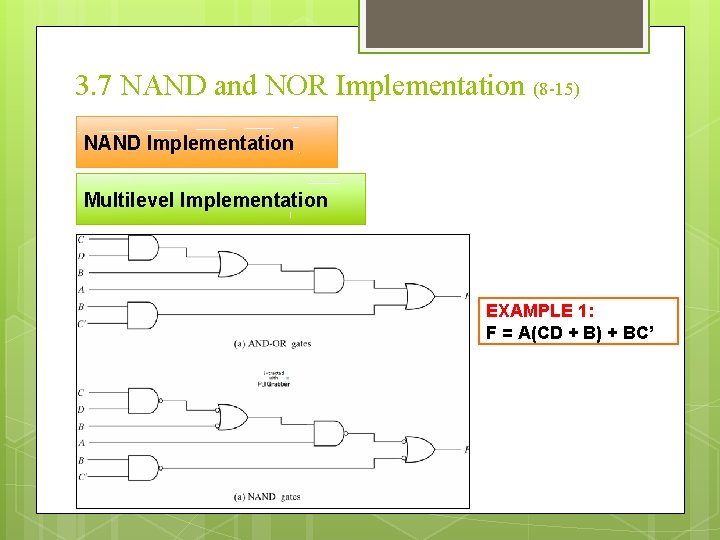

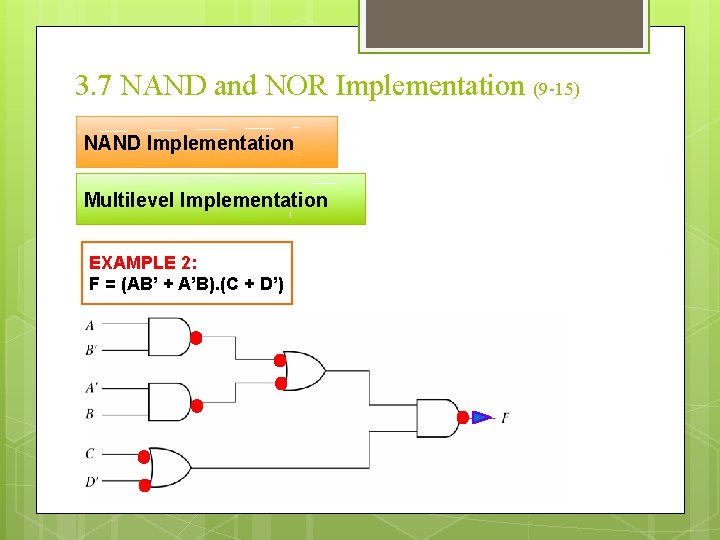

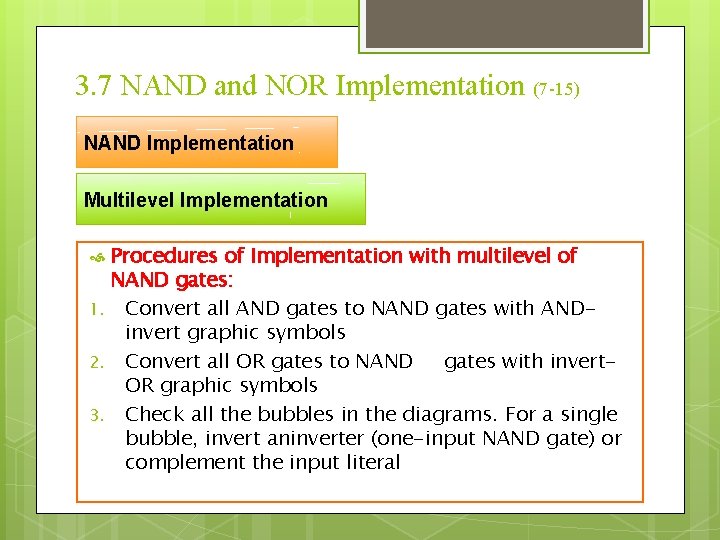

3. 7 NAND and NOR Implementation (7 -15) NAND Implementation Multilevel Implementation 1. 2. 3. Procedures of Implementation with multilevel of NAND gates: Convert all AND gates to NAND gates with ANDinvert graphic symbols Convert all OR gates to NAND gates with invert. OR graphic symbols Check all the bubbles in the diagrams. For a single bubble, invert aninverter (one-input NAND gate) or complement the input literal

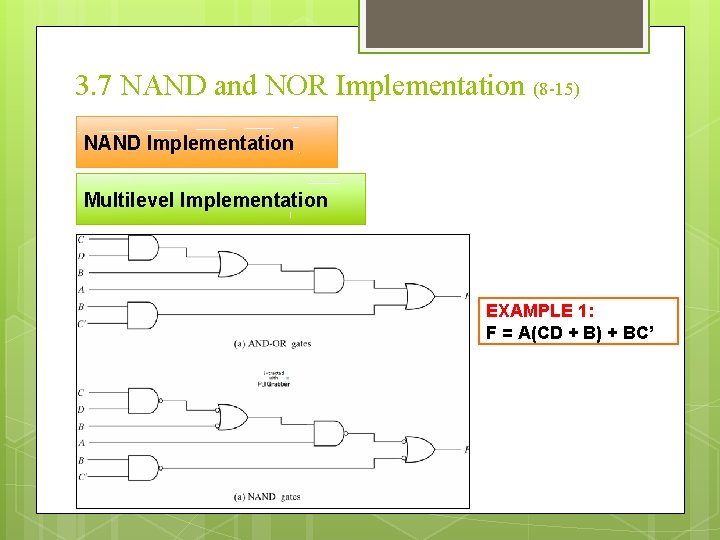

3. 7 NAND and NOR Implementation (8 -15) NAND Implementation Multilevel Implementation EXAMPLE 1: F = A(CD + B) + BC’

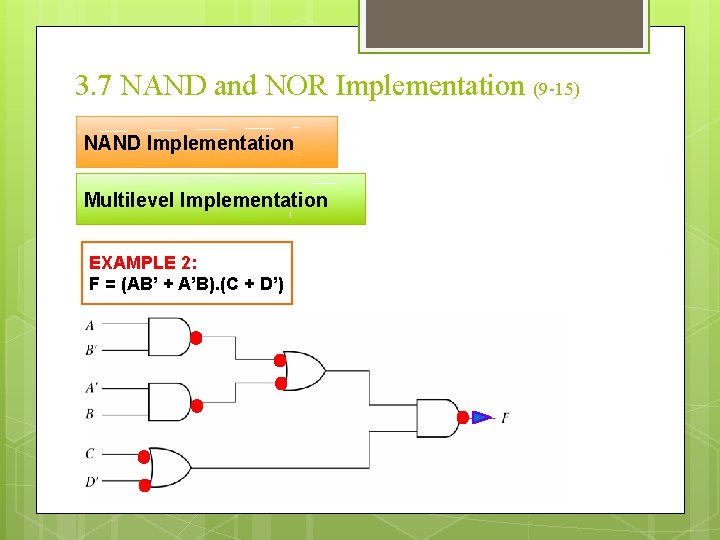

3. 7 NAND and NOR Implementation (9 -15) NAND Implementation Multilevel Implementation EXAMPLE 2: F = (AB’ + A’B). (C + D’)

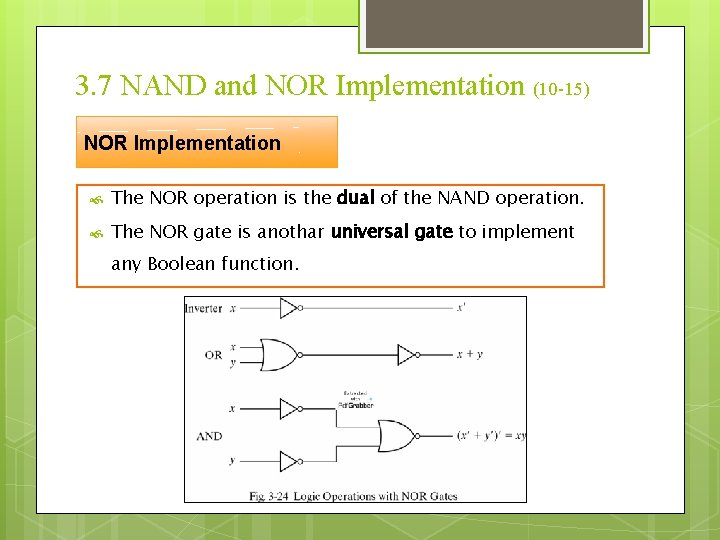

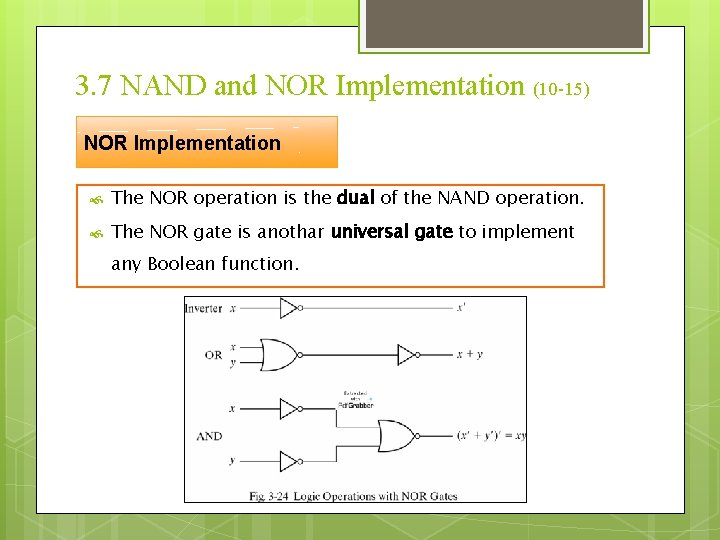

3. 7 NAND and NOR Implementation (10 -15) NOR Implementation The NOR operation is the dual of the NAND operation. The NOR gate is anothar universal gate to implement any Boolean function.

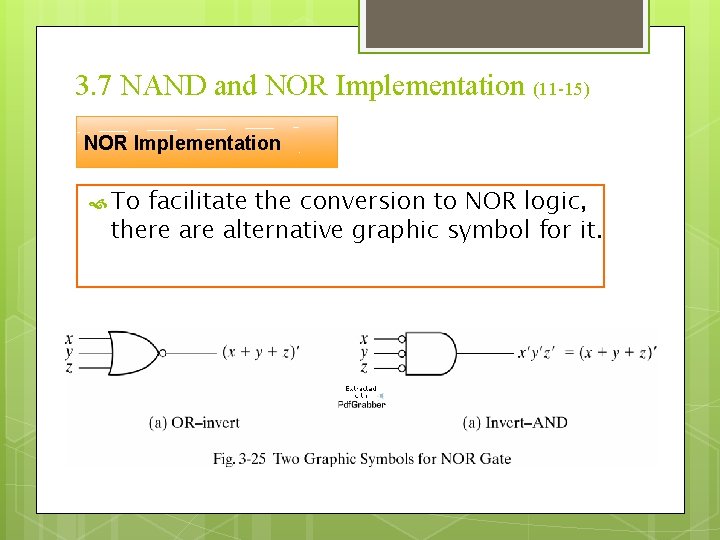

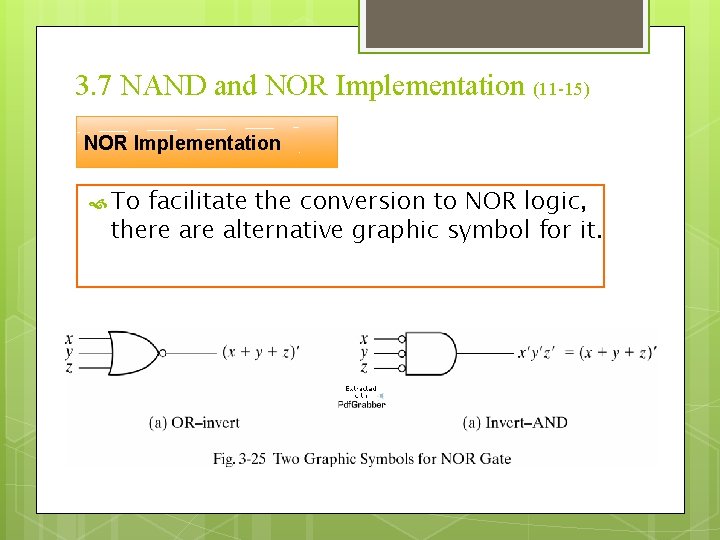

3. 7 NAND and NOR Implementation (11 -15) NOR Implementation To facilitate the conversion to NOR logic, there alternative graphic symbol for it.

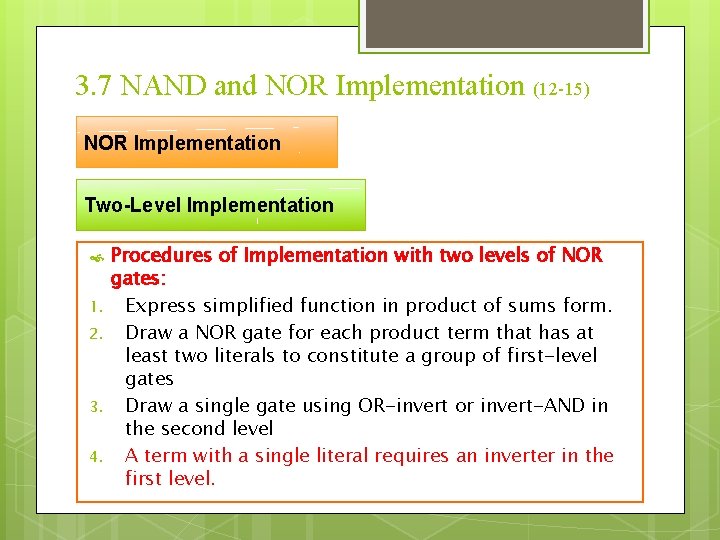

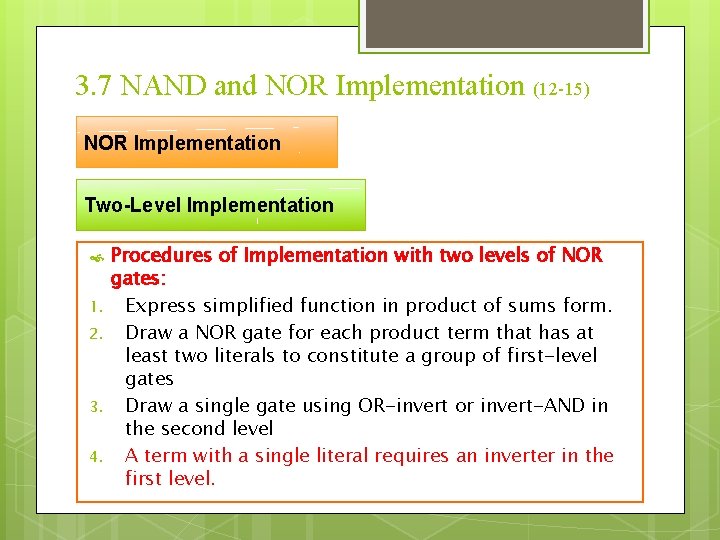

3. 7 NAND and NOR Implementation (12 -15) NOR Implementation Two-Level Implementation 1. 2. 3. 4. Procedures of Implementation with two levels of NOR gates: Express simplified function in product of sums form. Draw a NOR gate for each product term that has at least two literals to constitute a group of first-level gates Draw a single gate using OR-invert or invert-AND in the second level A term with a single literal requires an inverter in the first level.

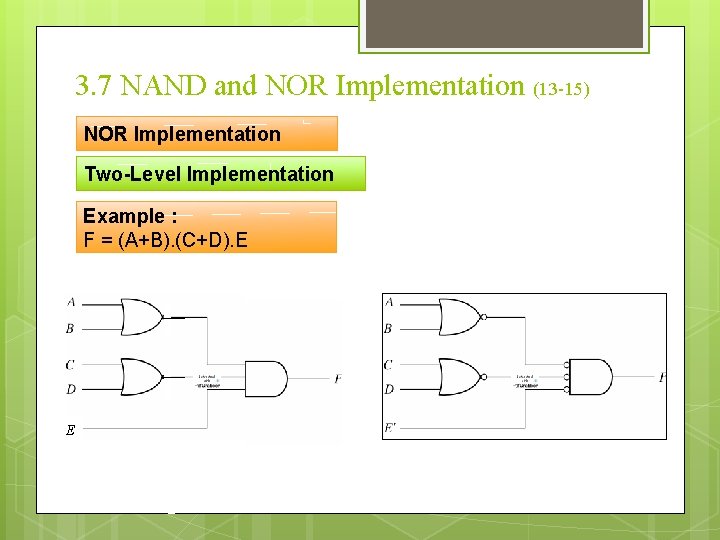

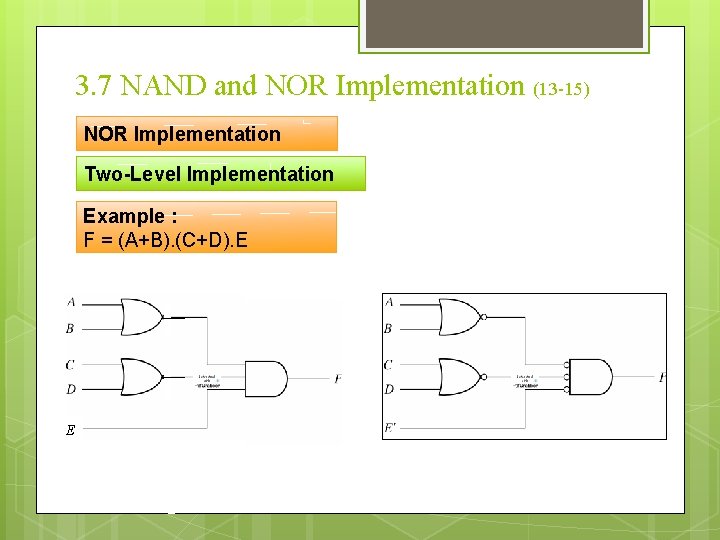

3. 7 NAND and NOR Implementation (13 -15) NOR Implementation Two-Level Implementation Example : F = (A+B). (C+D). E E

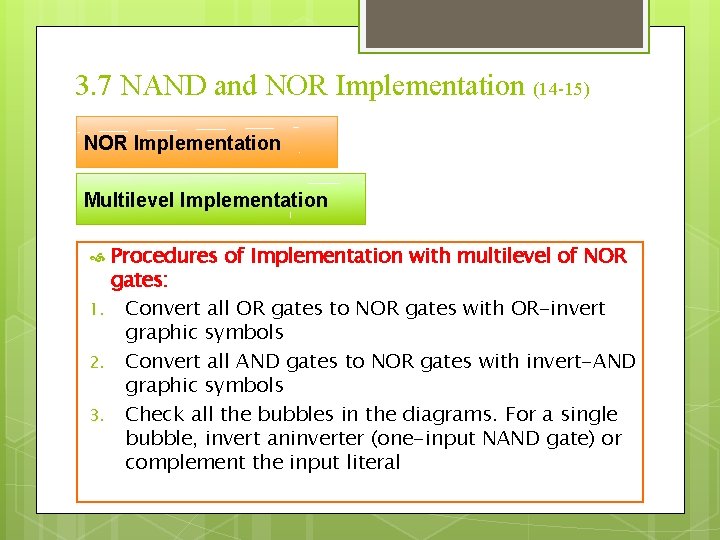

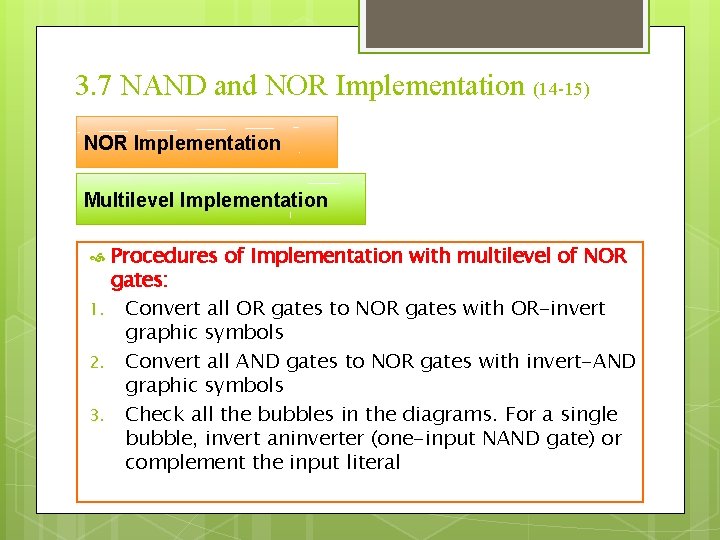

3. 7 NAND and NOR Implementation (14 -15) NOR Implementation Multilevel Implementation 1. 2. 3. Procedures of Implementation with multilevel of NOR gates: Convert all OR gates to NOR gates with OR-invert graphic symbols Convert all AND gates to NOR gates with invert-AND graphic symbols Check all the bubbles in the diagrams. For a single bubble, invert aninverter (one-input NAND gate) or complement the input literal

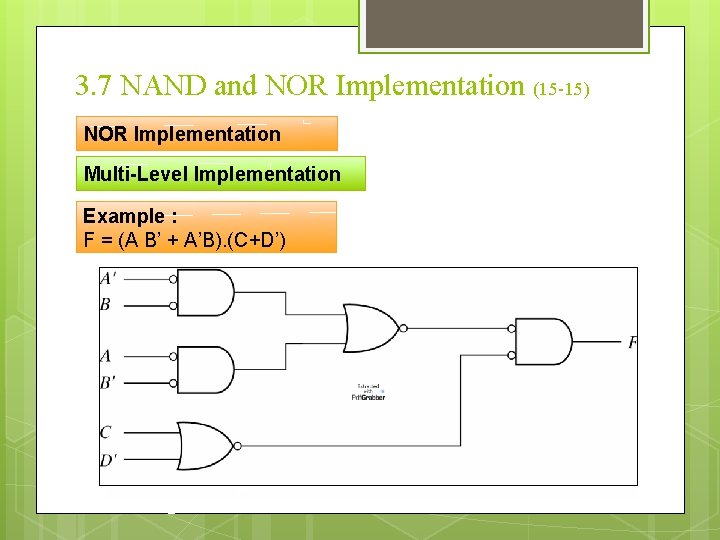

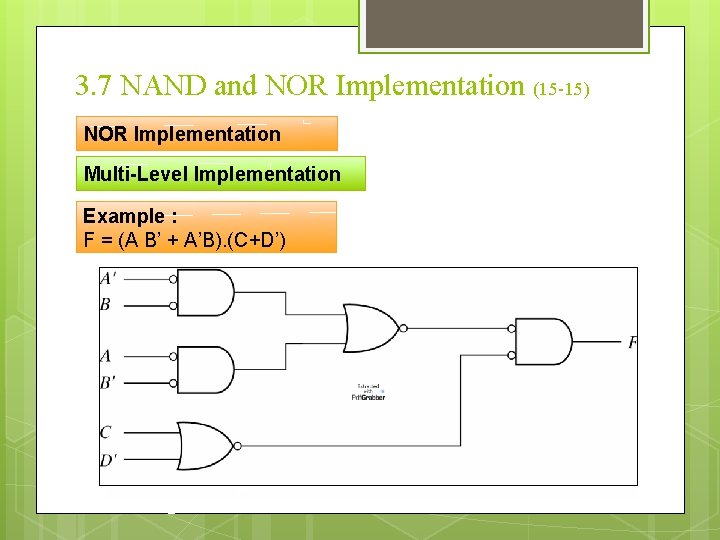

3. 7 NAND and NOR Implementation (15 -15) NOR Implementation Multi-Level Implementation Example : F = (A B’ + A’B). (C+D’) A B’ A’ B

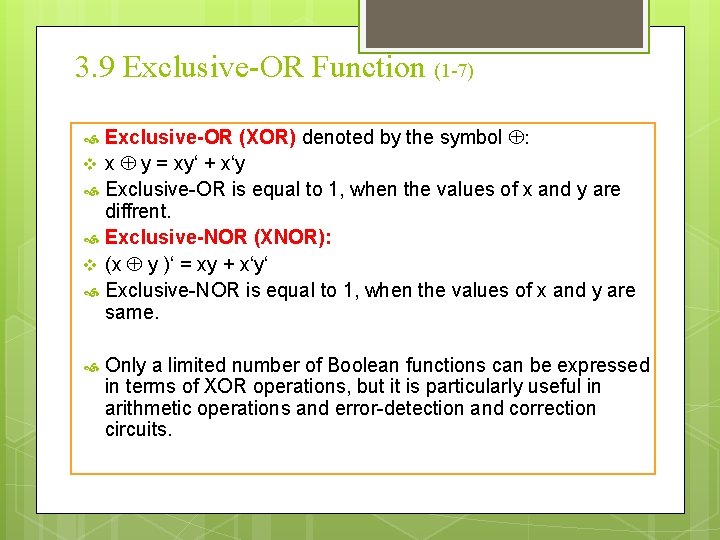

3. 9 Exclusive-OR Function (1 -7) Exclusive-OR (XOR) denoted by the symbol : v x y = xy‘ + x‘y Exclusive-OR is equal to 1, when the values of x and y are diffrent. Exclusive-NOR (XNOR): v (x y )‘ = xy + x‘y‘ Exclusive-NOR is equal to 1, when the values of x and y are same. Only a limited number of Boolean functions can be expressed in terms of XOR operations, but it is particularly useful in arithmetic operations and error-detection and correction circuits.

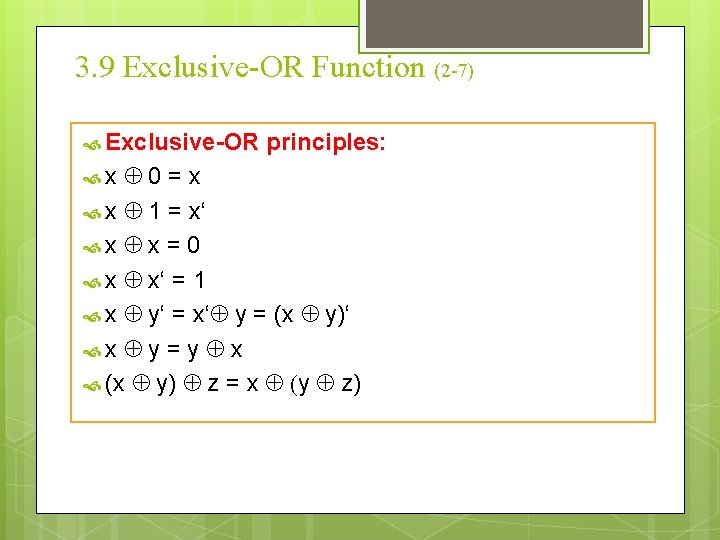

3. 9 Exclusive-OR Function (2 -7) Exclusive-OR principles: 0=x x 1 = x‘ x x = 0 x x‘ = 1 x y‘ = x‘ y = (x y)‘ x y = y x (x y) z = x (y z) x

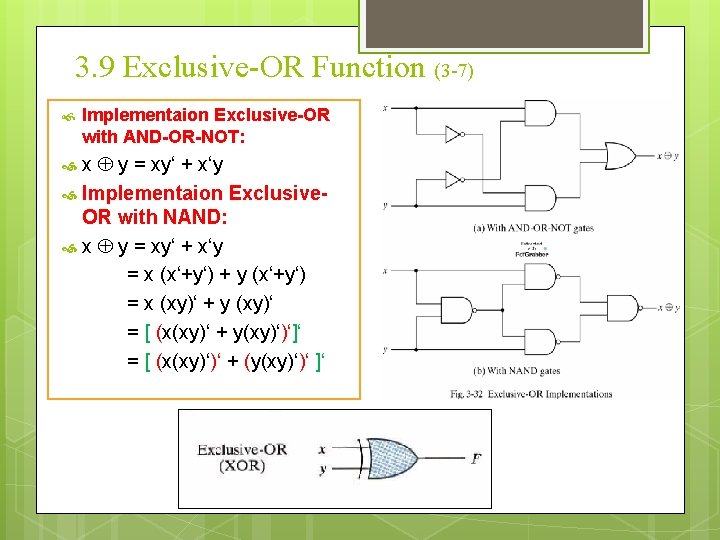

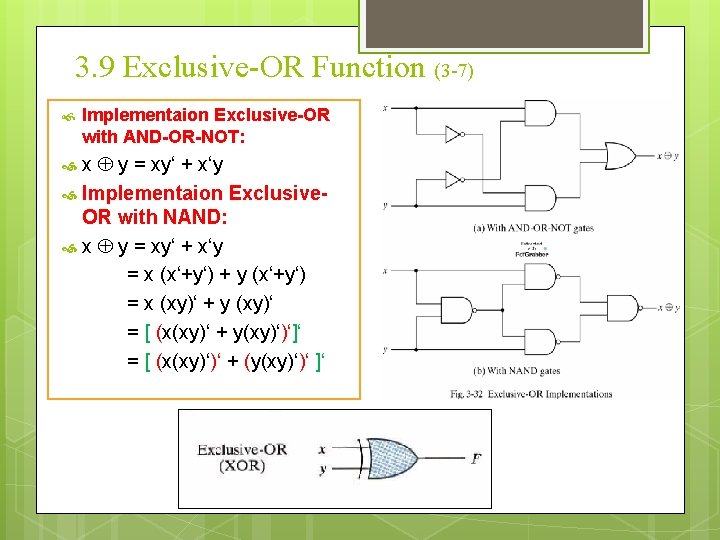

3. 9 Exclusive-OR Function (3 -7) Implementaion Exclusive-OR with AND-OR-NOT: x y = xy‘ + x‘y Implementaion Exclusive. OR with NAND: x y = xy‘ + x‘y = x (x‘+y‘) + y (x‘+y‘) = x (xy)‘ + y (xy)‘ = [ (x(xy)‘ + y(xy)‘)‘]‘ = [ (x(xy)‘)‘ + (y(xy)‘)‘ ]‘

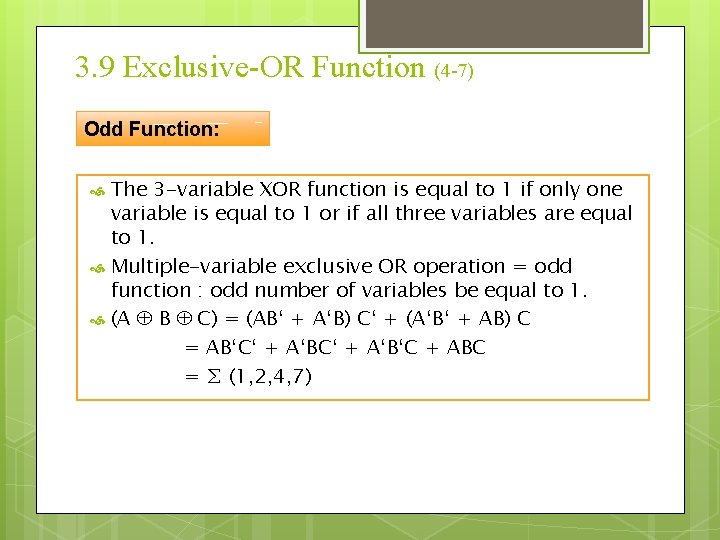

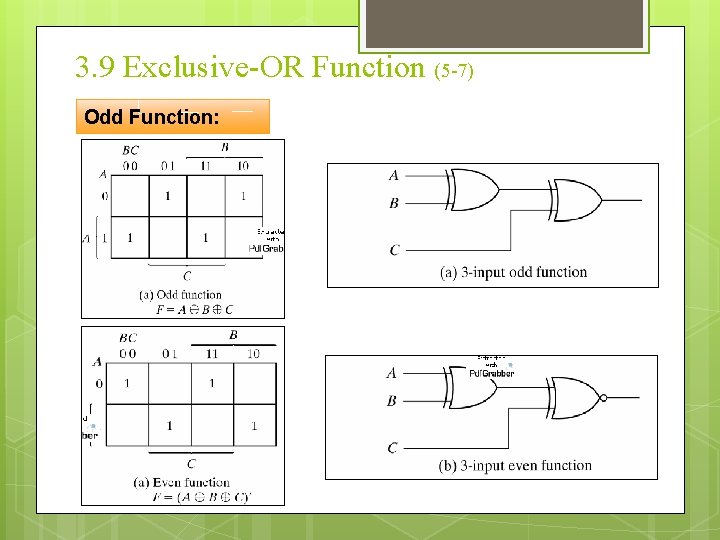

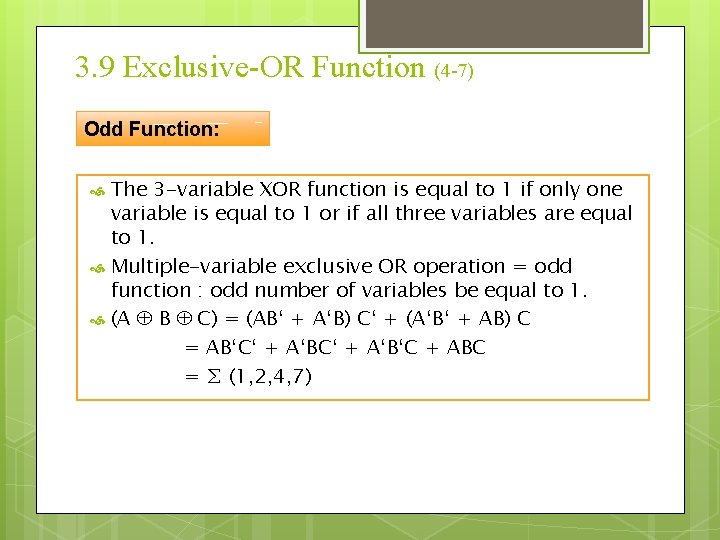

3. 9 Exclusive-OR Function (4 -7) Odd Function: The 3 -variable XOR function is equal to 1 if only one variable is equal to 1 or if all three variables are equal to 1. Multiple-variable exclusive OR operation = odd function : odd number of variables be equal to 1. (A B C) = (AB‘ + A‘B) C‘ + (A‘B‘ + AB) C = AB‘C‘ + A‘B‘C + ABC = ∑ (1, 2, 4, 7)

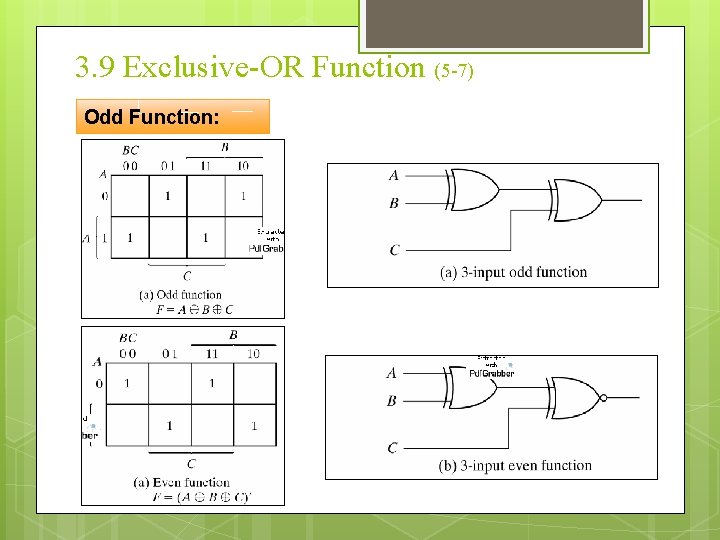

3. 9 Exclusive-OR Function (5 -7) Odd Function:

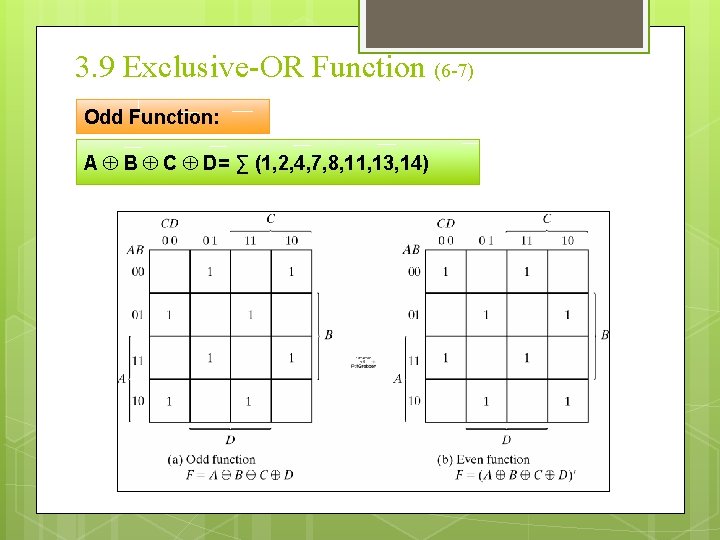

3. 9 Exclusive-OR Function (6 -7) Odd Function: A B C D= ∑ (1, 2, 4, 7, 8, 11, 13, 14)

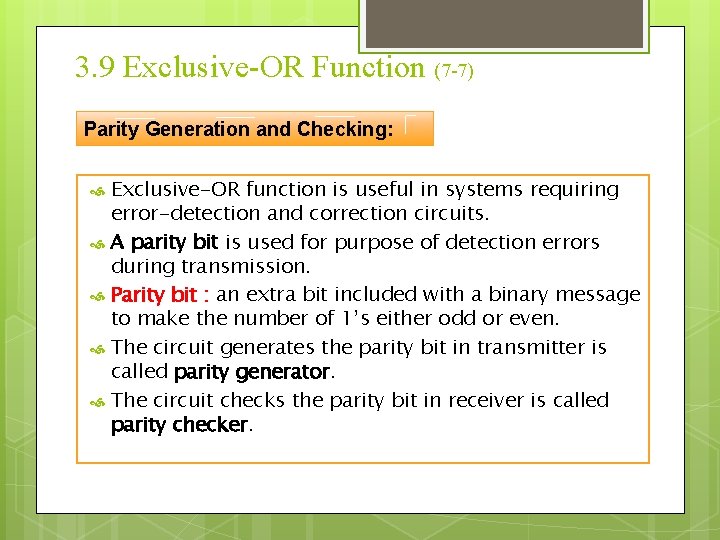

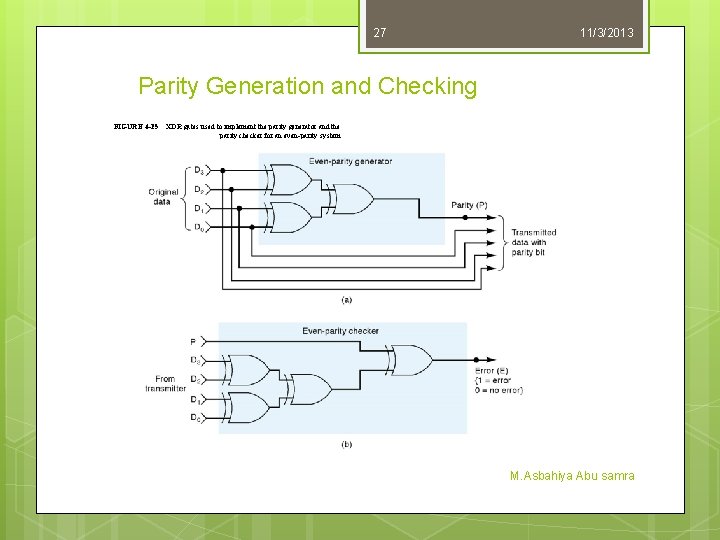

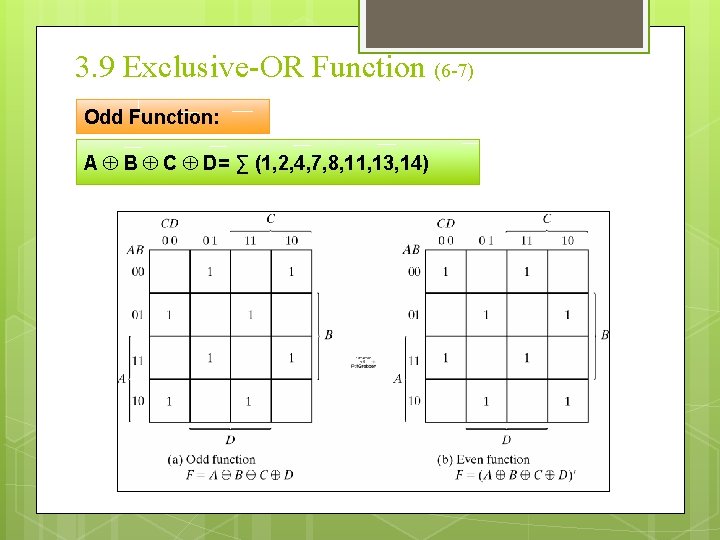

3. 9 Exclusive-OR Function (7 -7) Parity Generation and Checking: Exclusive-OR function is useful in systems requiring error-detection and correction circuits. A parity bit is used for purpose of detection errors during transmission. Parity bit : an extra bit included with a binary message to make the number of 1’s either odd or even. The circuit generates the parity bit in transmitter is called parity generator. The circuit checks the parity bit in receiver is called parity checker.

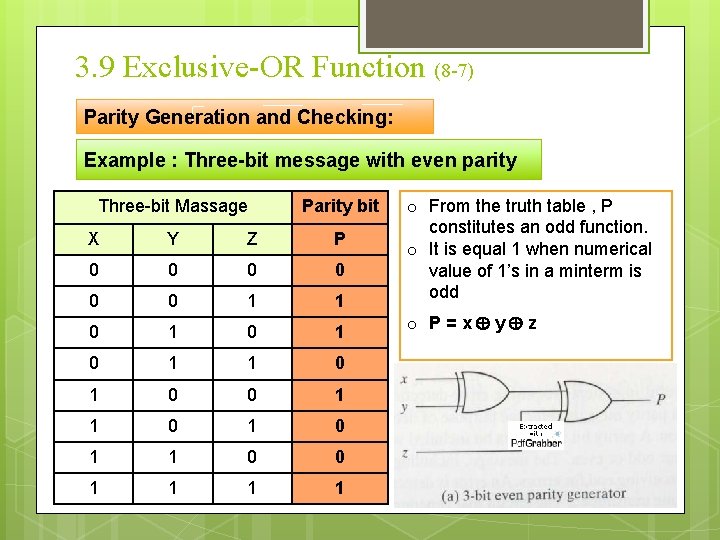

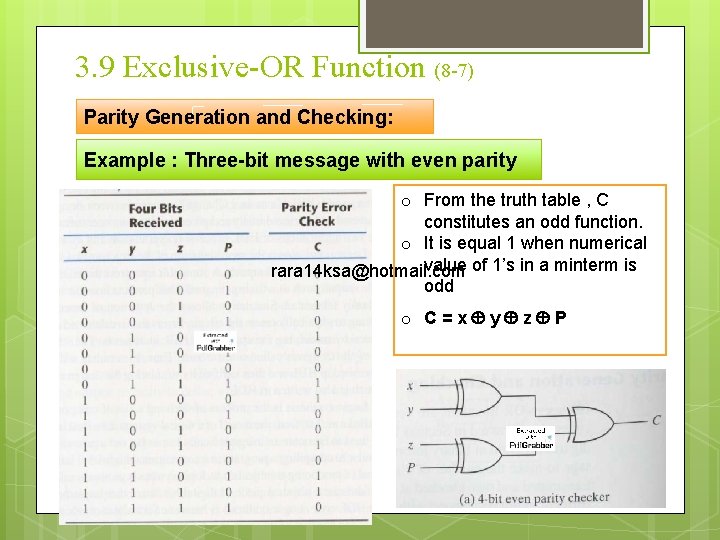

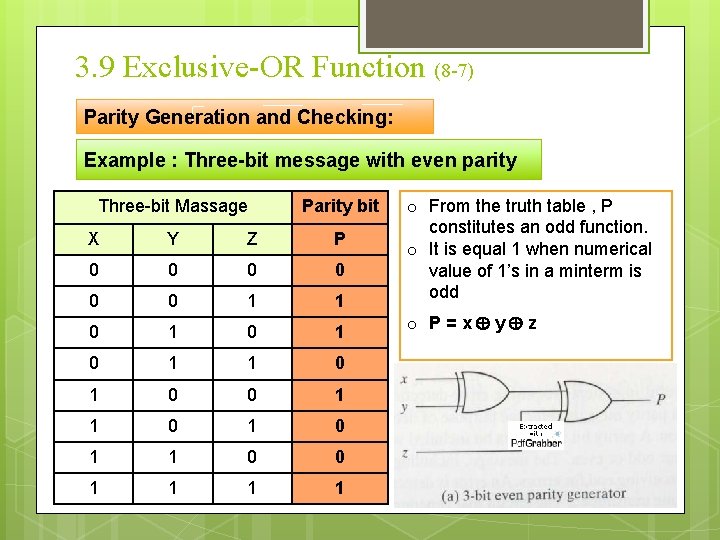

3. 9 Exclusive-OR Function (8 -7) Parity Generation and Checking: Example : Three-bit message with even parity Three-bit Massage Parity bit X Y Z P 0 0 0 1 1 0 1 0 1 0 0 1 1 0 0 1 1 o From the truth table , P constitutes an odd function. o It is equal 1 when numerical value of 1’s in a minterm is odd o P=x y z

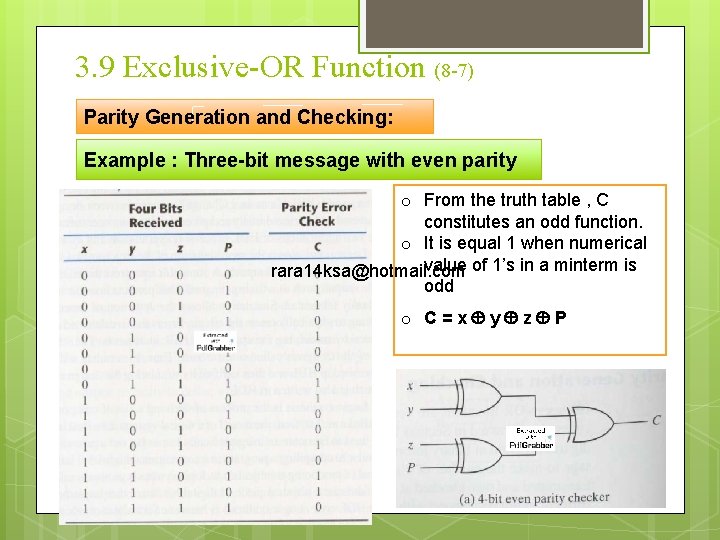

3. 9 Exclusive-OR Function (8 -7) Parity Generation and Checking: Example : Three-bit message with even parity o From the truth table , C constitutes an odd function. o It is equal 1 when numerical value of 1’s in a minterm is rara 14 ksa@hotmail. com odd o C=x y z P

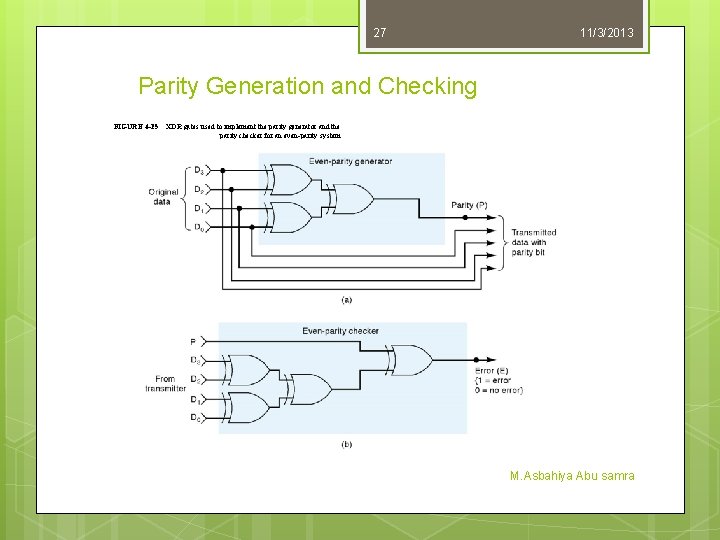

27 11/3/2013 Parity Generation and Checking FIGURE 4 -25 XOR gates used to implement the parity generator and the parity checker for an even-parity system. M. Asbahiya Abu samra