CS 101 Sept 25 Continue Chapter 5 Review

- Slides: 13

CS 101 – Sept. 25 Continue Chapter 5 • Review of pipelined instruction execution • Memory system – Limited memory on chip – Main memory (RAM) – Secondary memory (e. g. disk)

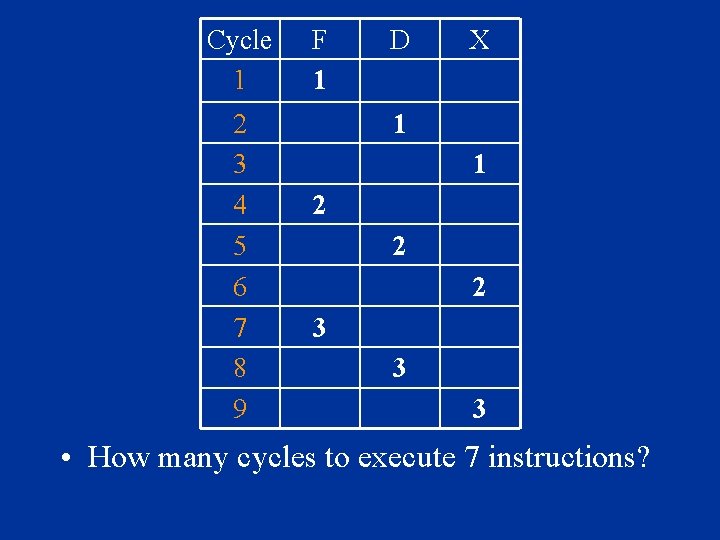

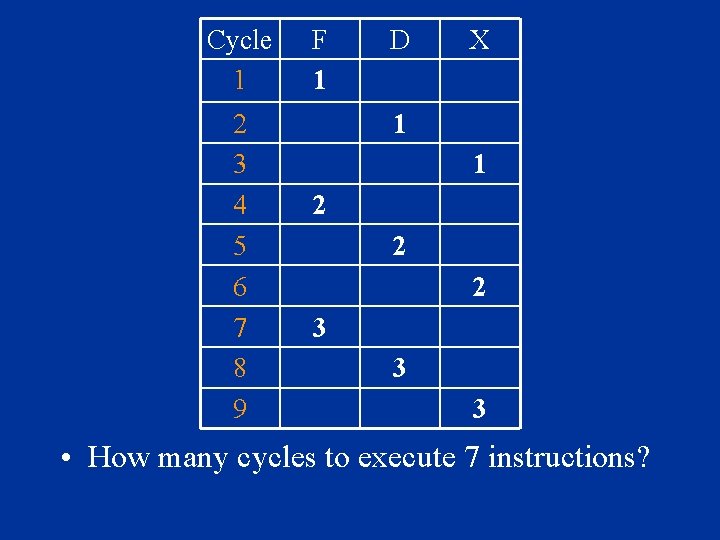

Cycle 1 2 3 4 5 6 7 8 9 F 1 D X 1 1 2 2 2 3 3 3 • How many cycles to execute 7 instructions?

Cycle 1 2 3 4 5 6 7 8 9 F 1 2 3 4 5 6 7 D 1 2 3 4 5 6 7 X 1 2 3 4 5 6 7 Better approach: • Technique is called “Pipelining” • On each cycle, try to do several jobs at once. • Like an assembly line.

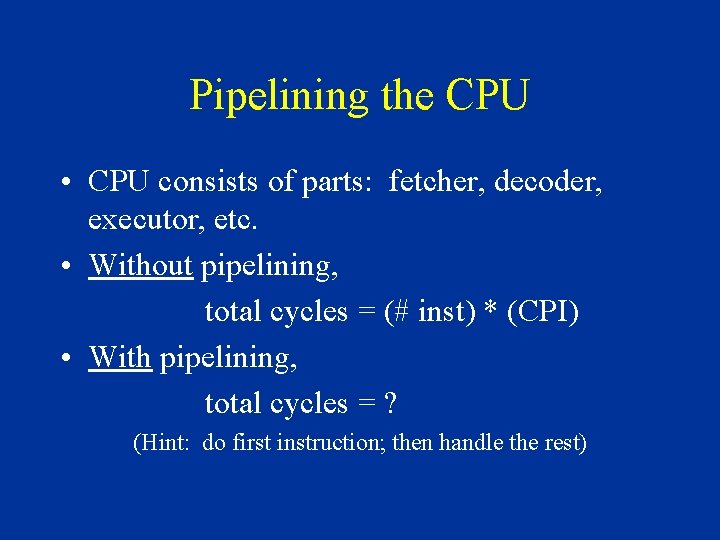

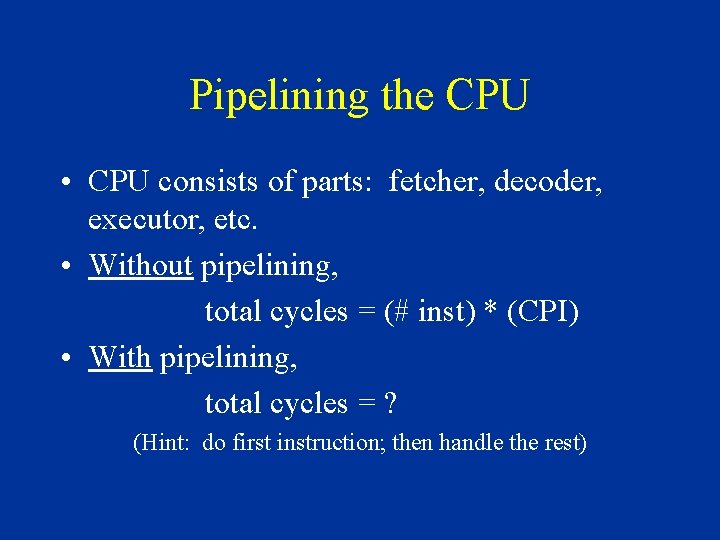

Pipelining the CPU • CPU consists of parts: fetcher, decoder, executor, etc. • Without pipelining, total cycles = (# inst) * (CPI) • With pipelining, total cycles = ? (Hint: do first instruction; then handle the rest)

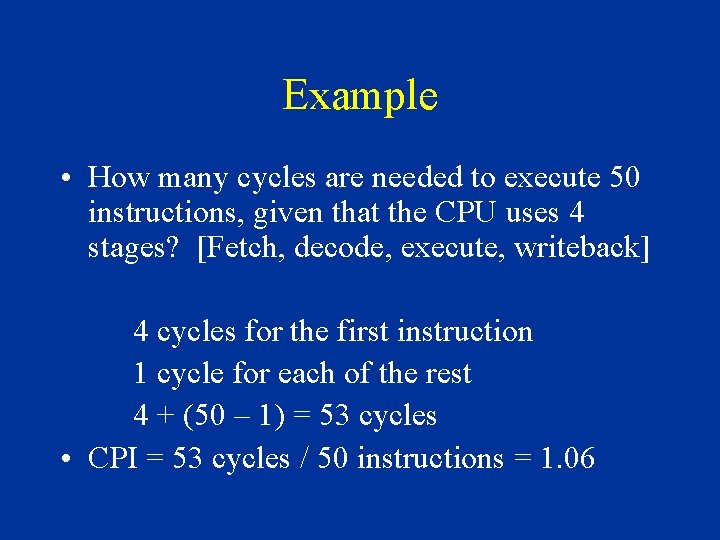

Example • How many cycles are needed to execute 50 instructions, given that the CPU uses 4 stages? [Fetch, decode, execute, writeback] 4 cycles for the first instruction 1 cycle for each of the rest 4 + (50 – 1) = 53 cycles • CPI = 53 cycles / 50 instructions = 1. 06

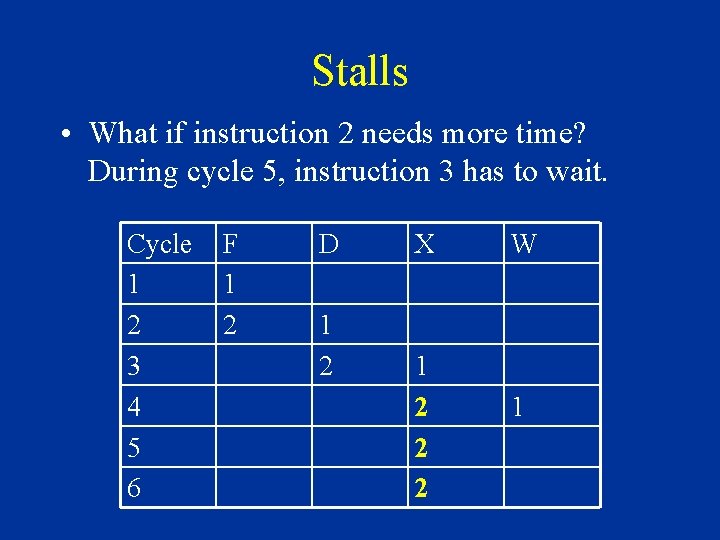

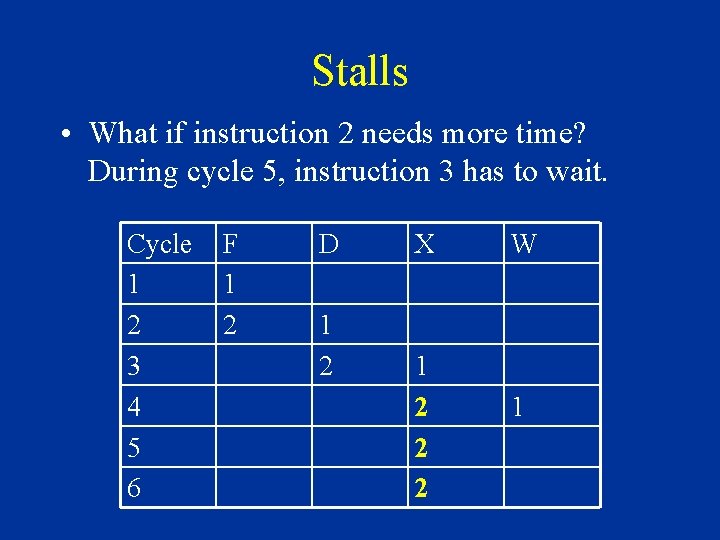

Stalls • What if instruction 2 needs more time? During cycle 5, instruction 3 has to wait. Cycle 1 2 3 4 5 6 F 1 2 D 1 2 X 1 2 2 2 W 1

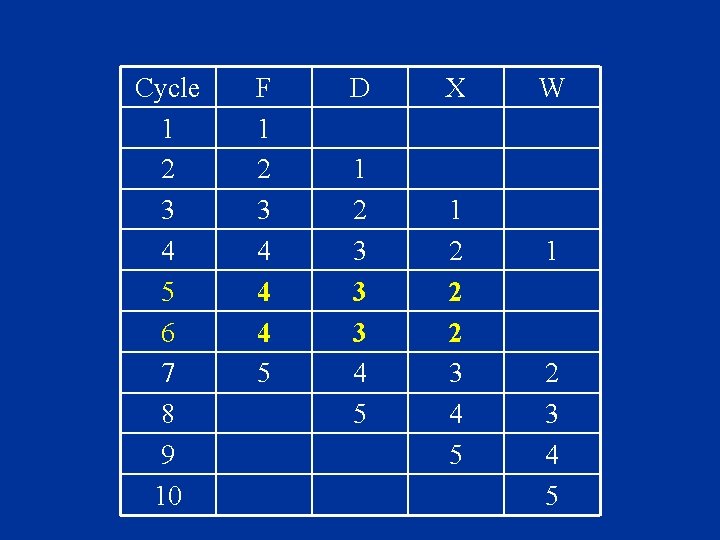

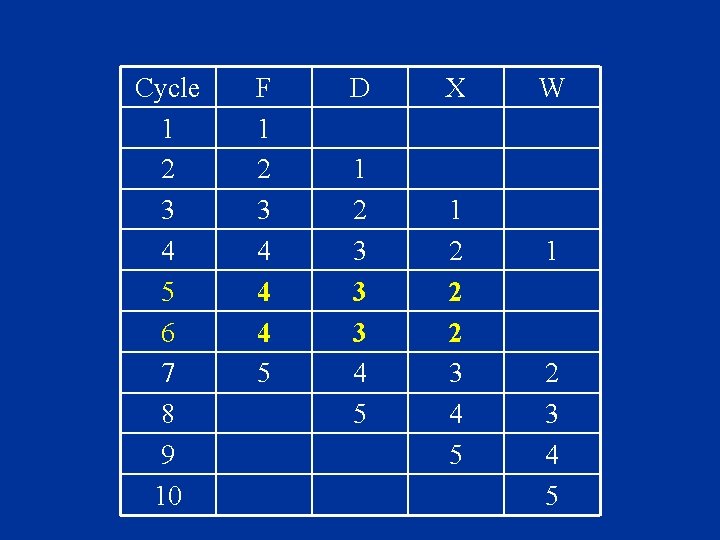

Cycle 1 2 3 4 5 6 7 8 9 10 F 1 2 3 4 4 4 5 D 1 2 3 3 3 4 5 X 1 2 2 2 3 4 5 W 1 2 3 4 5

Deli pipeline! • Five stages in deli to make sandwich: – Place order – Get right bread and slice – Put meat on bread – Add condiments – Cashier and pickup. • What are some possible stalls?

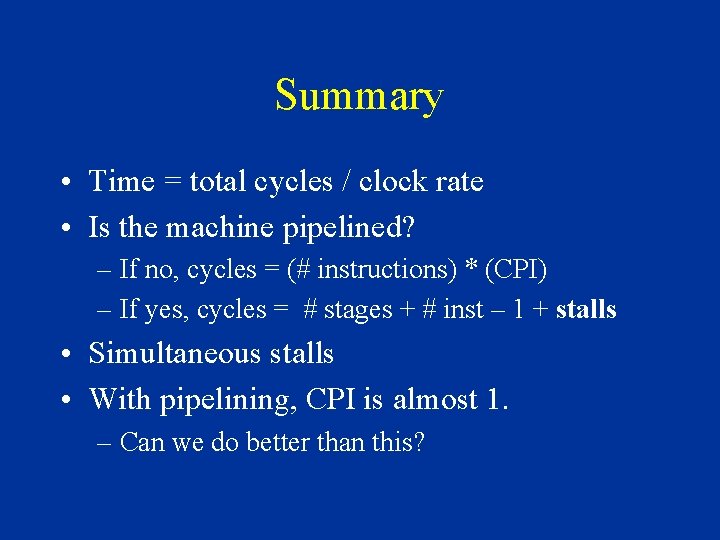

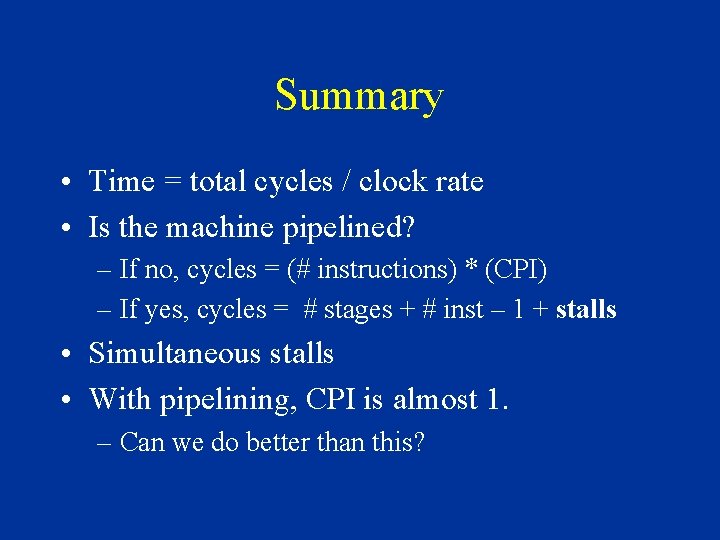

Summary • Time = total cycles / clock rate • Is the machine pipelined? – If no, cycles = (# instructions) * (CPI) – If yes, cycles = # stages + # inst – 1 + stalls • Simultaneous stalls • With pipelining, CPI is almost 1. – Can we do better than this?

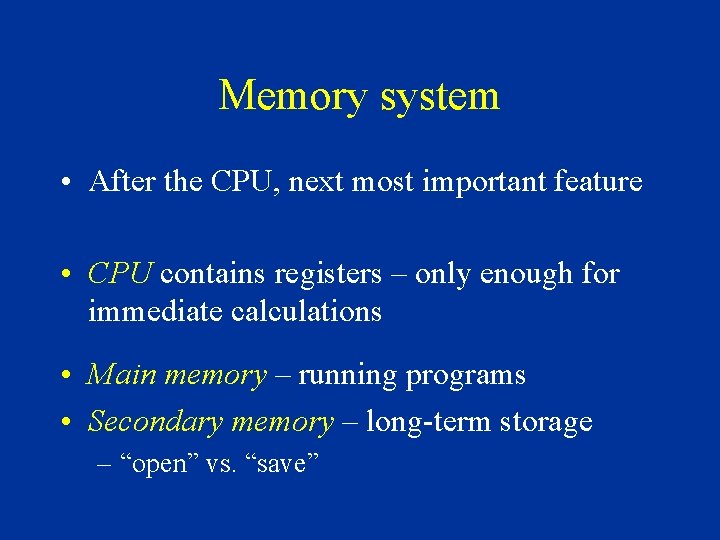

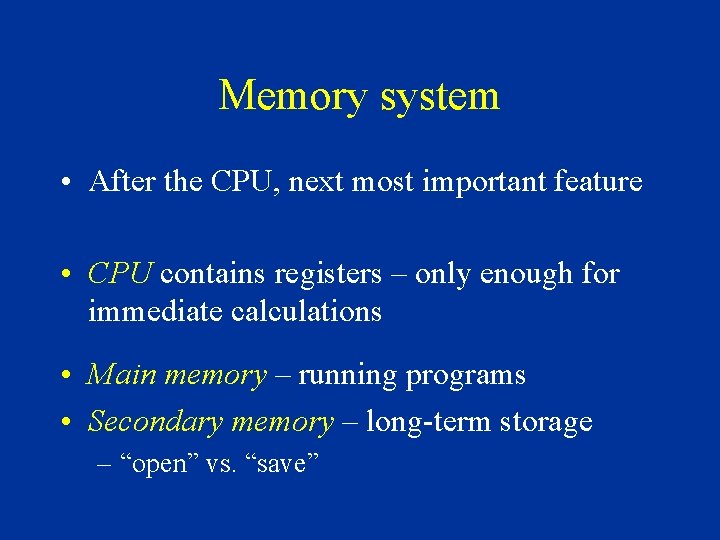

Memory system • After the CPU, next most important feature • CPU contains registers – only enough for immediate calculations • Main memory – running programs • Secondary memory – long-term storage – “open” vs. “save”

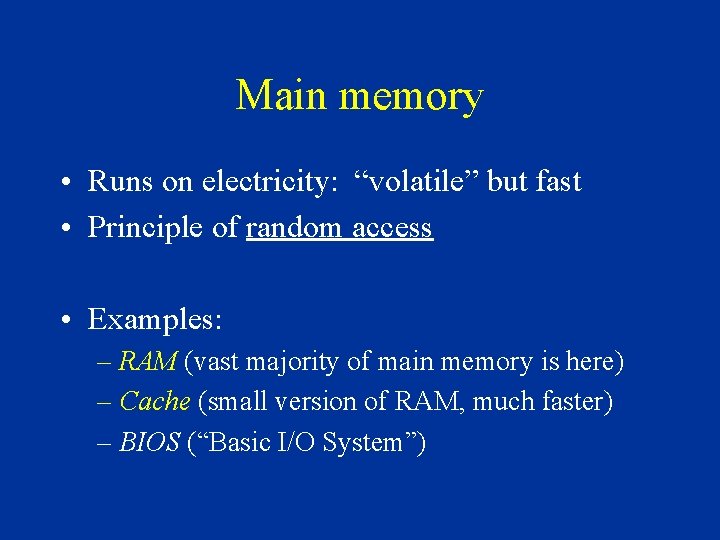

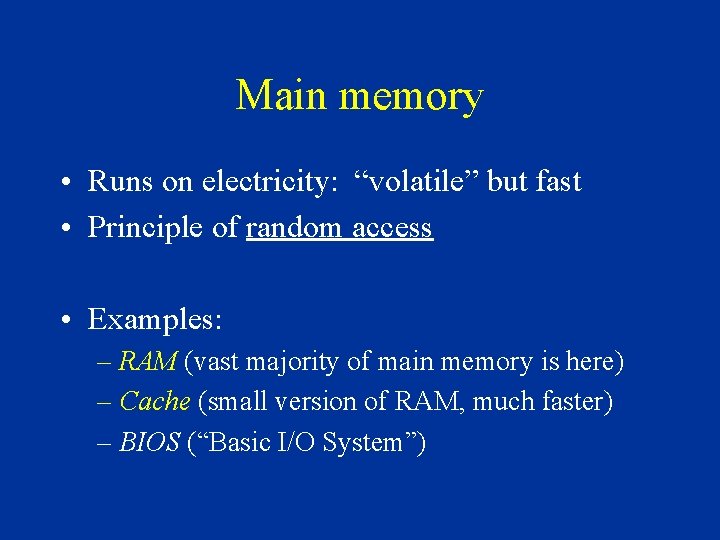

Main memory • Runs on electricity: “volatile” but fast • Principle of random access • Examples: – RAM (vast majority of main memory is here) – Cache (small version of RAM, much faster) – BIOS (“Basic I/O System”)

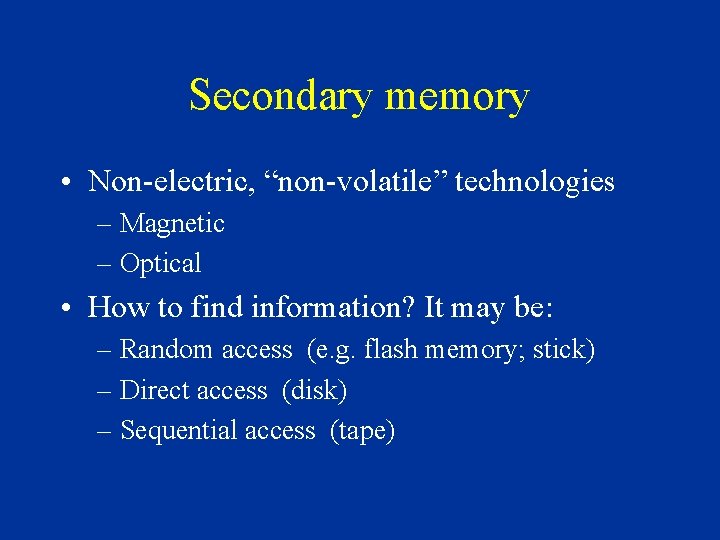

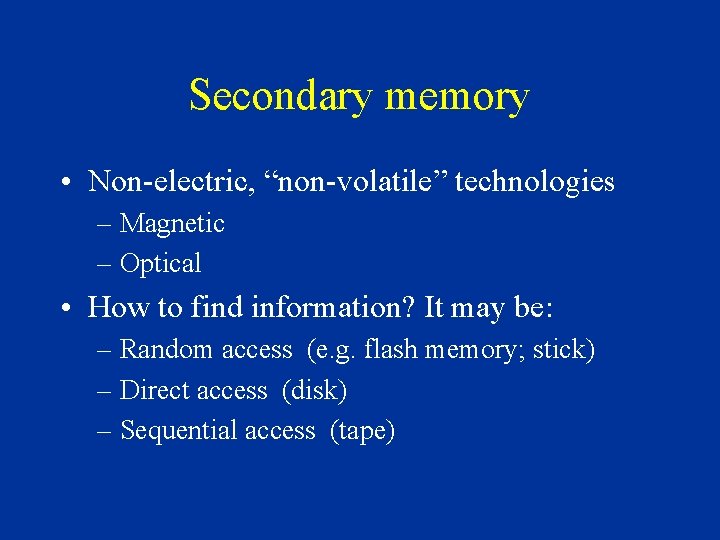

Secondary memory • Non-electric, “non-volatile” technologies – Magnetic – Optical • How to find information? It may be: – Random access (e. g. flash memory; stick) – Direct access (disk) – Sequential access (tape)

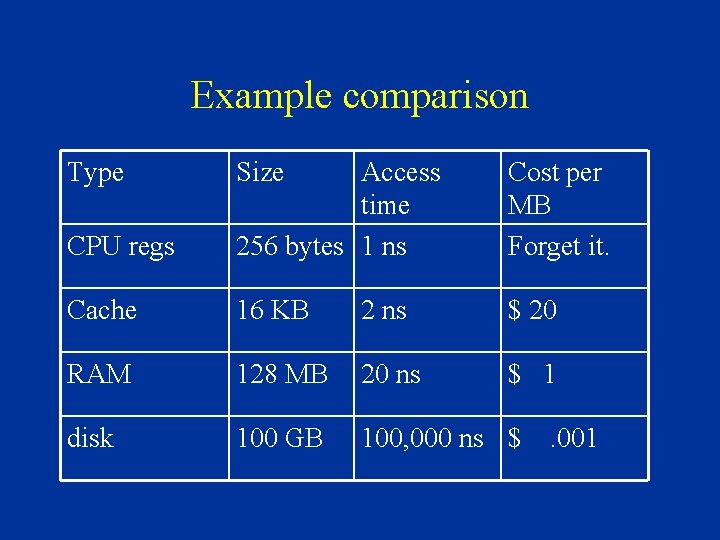

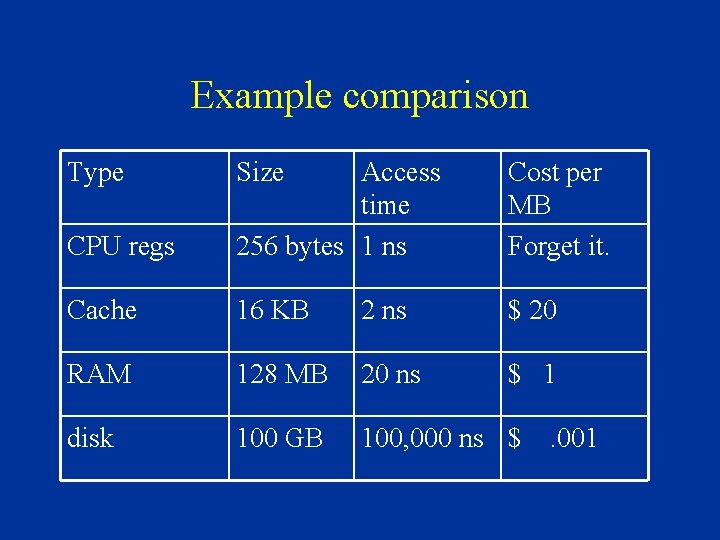

Example comparison Type Size CPU regs Access time 256 bytes 1 ns Cost per MB Forget it. Cache 16 KB 2 ns $ 20 RAM 128 MB 20 ns $ 1 disk 100 GB 100, 000 ns $ . 001