CRYO A Waveform DigitizerSerializer for TPC Experiments Prototype

- Slides: 12

CRYO: A Waveform Digitizer/Serializer for TPC Experiments Prototype Tests Status June 17 th, 2019 A. Pena Perez, D. Doering, A. Dragone* (* dragone@slac. Stanford. edu) TID-AIR Integrated Circuits

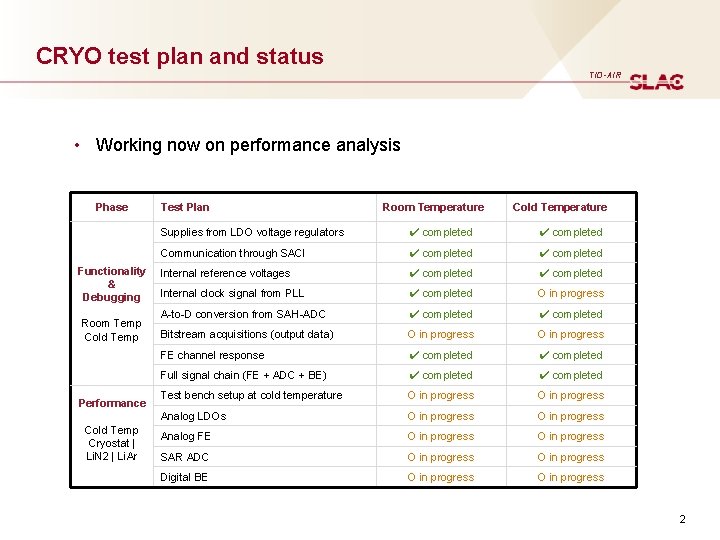

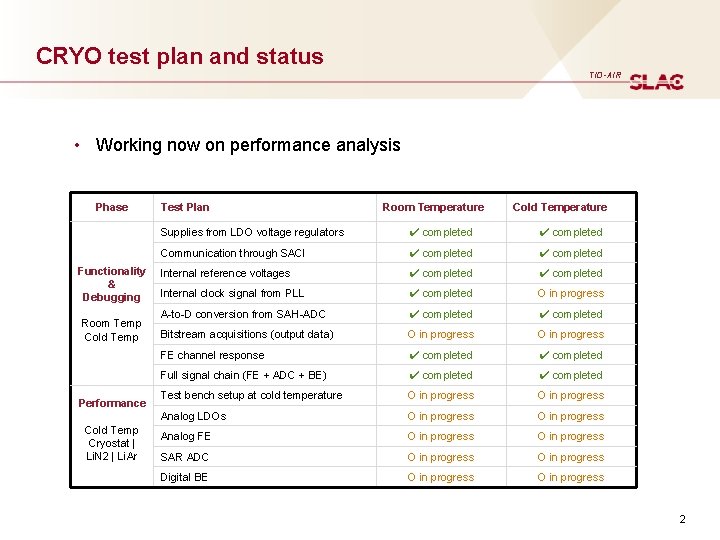

CRYO test plan and status TID-AIR • Working now on performance analysis Phase Functionality & Debugging Room Temp Cold Temp Performance Cold Temp Cryostat | Li. N 2 | Li. Ar Test Plan Room Temperature Cold Temperature Supplies from LDO voltage regulators ✔ completed Communication through SACI ✔ completed Internal reference voltages ✔ completed Internal clock signal from PLL ✔ completed Ο in progress A-to-D conversion from SAH-ADC ✔ completed Bitstream acquisitions (output data) Ο in progress FE channel response ✔ completed Full signal chain (FE + ADC + BE) ✔ completed Test bench setup at cold temperature Ο in progress Analog LDOs Ο in progress Analog FE Ο in progress SAR ADC Ο in progress Digital BE Ο in progress 2

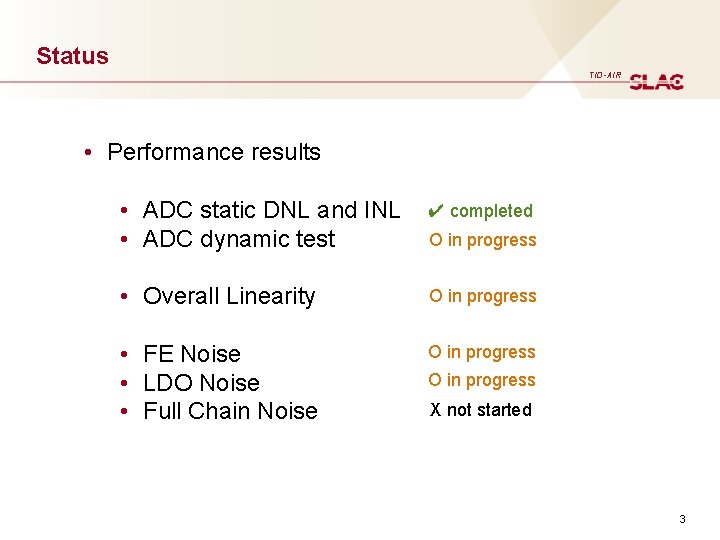

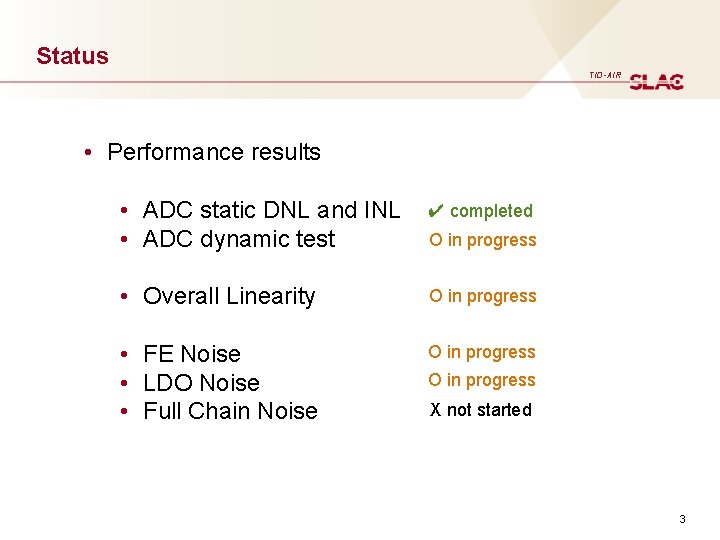

Status TID-AIR • Performance results • ADC static DNL and INL • ADC dynamic test ✔ completed • Overall Linearity Ο in progress • FE Noise • LDO Noise • Full Chain Noise Ο in progress X not started 3

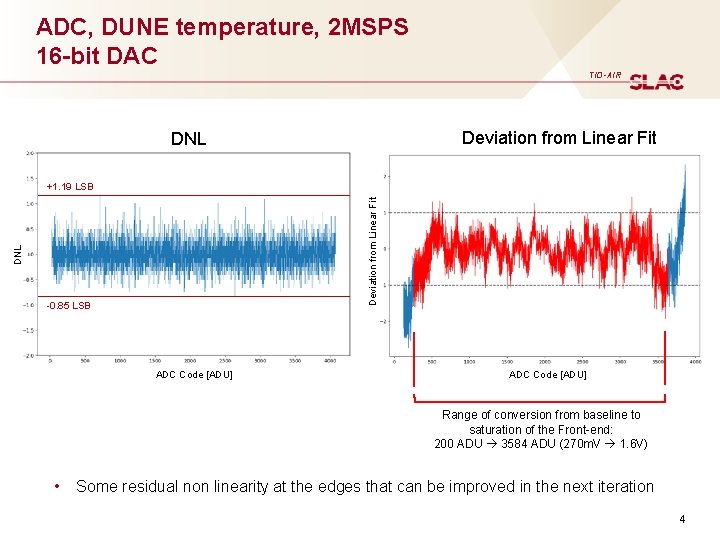

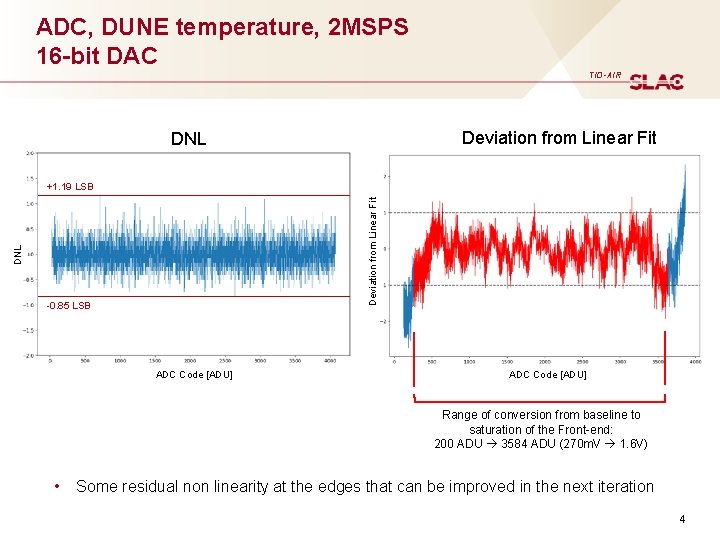

ADC, DUNE temperature, 2 MSPS 16 -bit DAC TID-AIR Deviation from Linear Fit DNL Deviation from Linear Fit +1. 19 LSB -0. 85 LSB ADC Code [ADU] Range of conversion from baseline to saturation of the Front-end: 200 ADU 3584 ADU (270 m. V 1. 6 V) • Some residual non linearity at the edges that can be improved in the next iteration 4

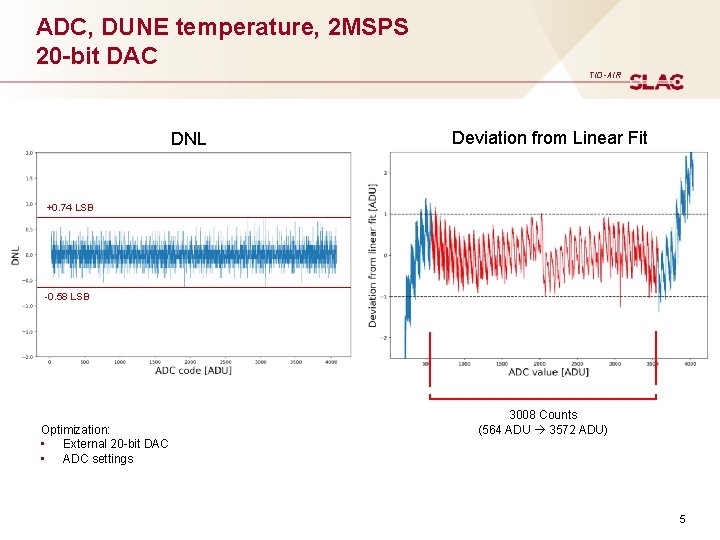

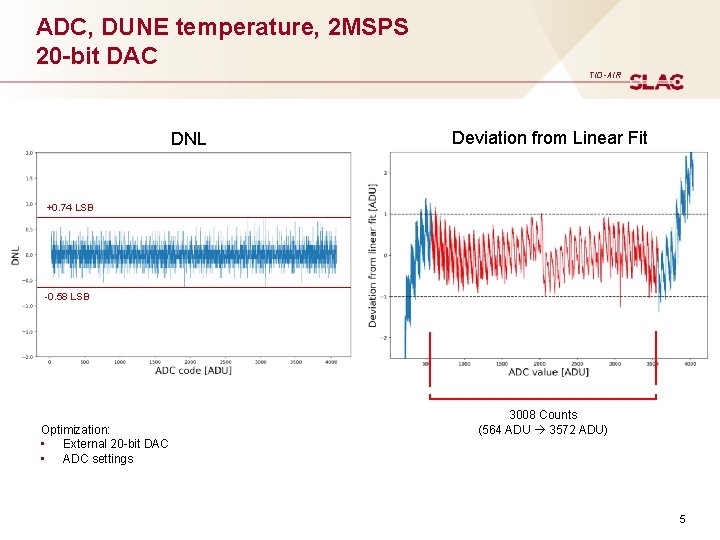

ADC, DUNE temperature, 2 MSPS 20 -bit DAC TID-AIR DNL Deviation from Linear Fit +0. 74 LSB -0. 58 LSB Optimization: • External 20 -bit DAC • ADC settings 3008 Counts (564 ADU 3572 ADU) 5

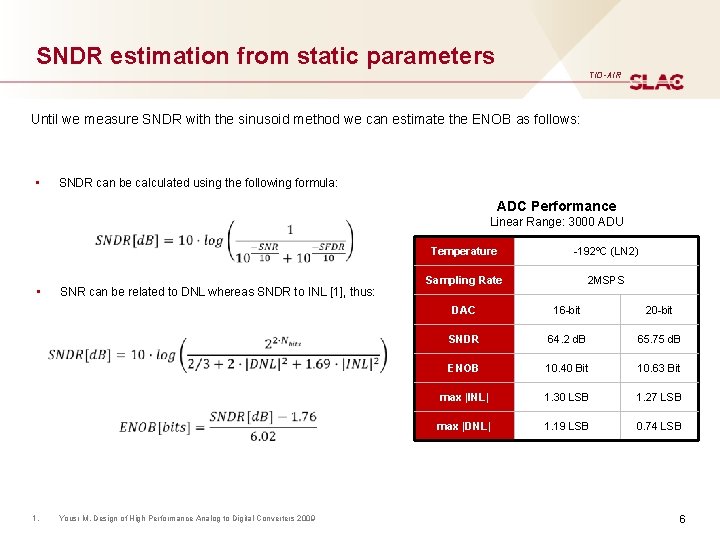

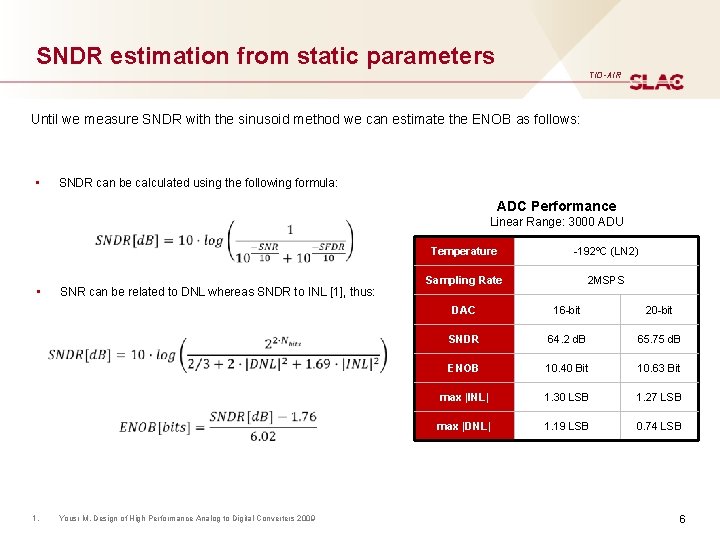

SNDR estimation from static parameters TID-AIR Until we measure SNDR with the sinusoid method we can estimate the ENOB as follows: • SNDR can be calculated using the following formula: ADC Performance Linear Range: 3000 ADU • 1. SNR can be related to DNL whereas SNDR to INL [1], thus: Yousr M. Design of High Performance Analog to Digital Converters 2009 Temperature -192ºC (LN 2) Sampling Rate 2 MSPS DAC 16 -bit 20 -bit SNDR 64. 2 d. B 65. 75 d. B ENOB 10. 40 Bit 10. 63 Bit max |INL| 1. 30 LSB 1. 27 LSB max |DNL| 1. 19 LSB 0. 74 LSB 6

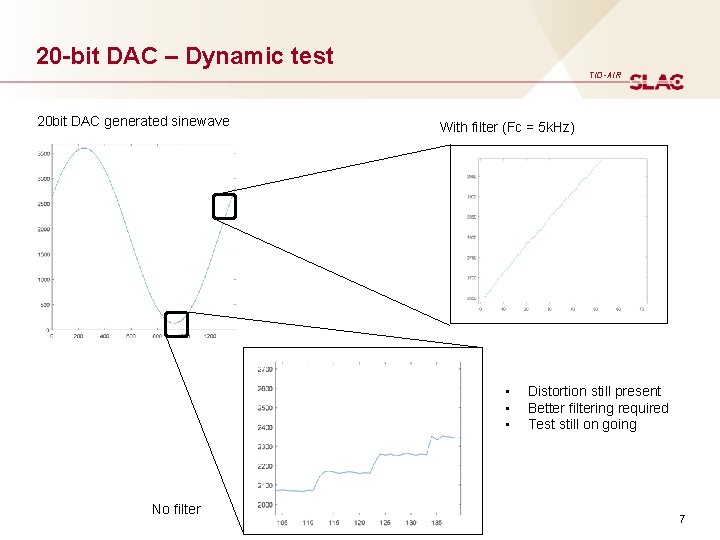

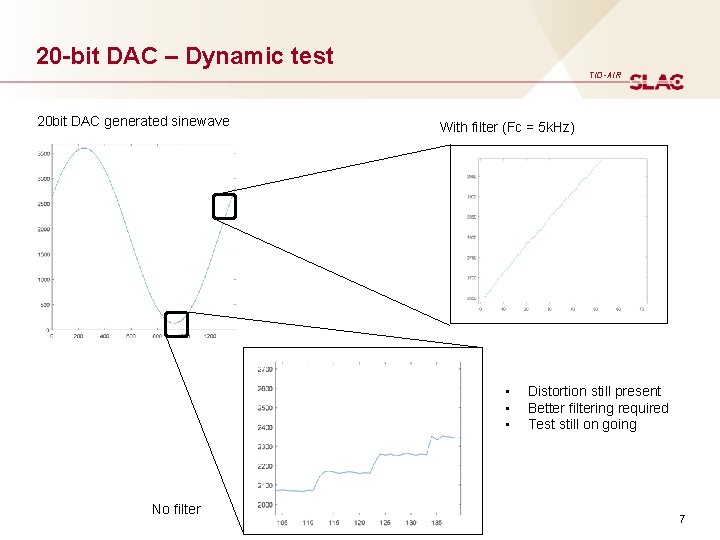

20 -bit DAC – Dynamic test TID-AIR 20 bit DAC generated sinewave With filter (Fc = 5 k. Hz) • • • No filter Distortion still present Better filtering required Test still on going 7

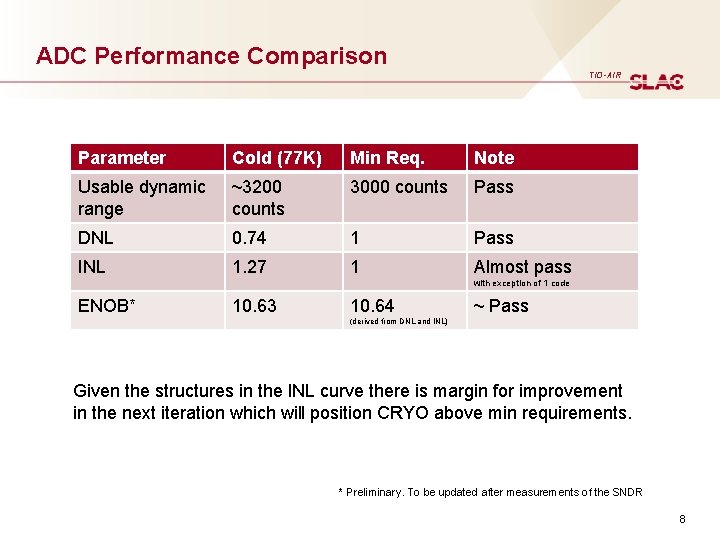

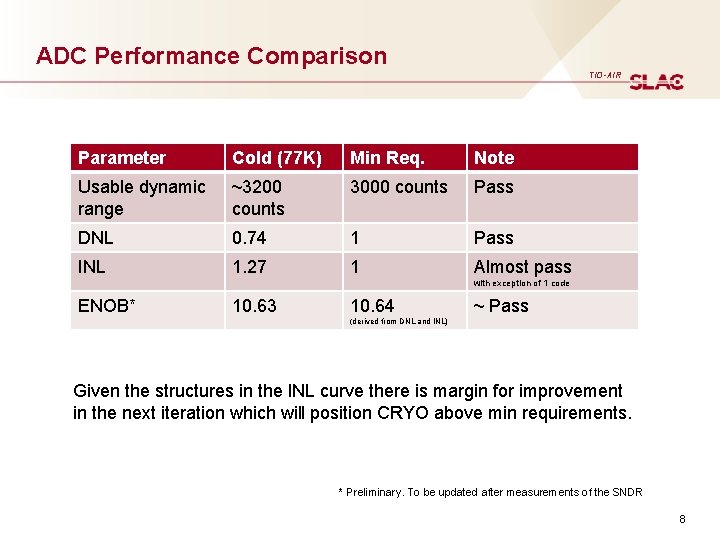

ADC Performance Comparison TID-AIR Parameter Cold (77 K) Min Req. Note Usable dynamic range ~3200 counts 3000 counts Pass DNL 0. 74 1 Pass INL 1. 27 1 Almost pass with exception of 1 code ENOB* 10. 63 10. 64 ~ Pass (derived from DNL and INL) Given the structures in the INL curve there is margin for improvement in the next iteration which will position CRYO above min requirements. * Preliminary. To be updated after measurements of the SNDR 8

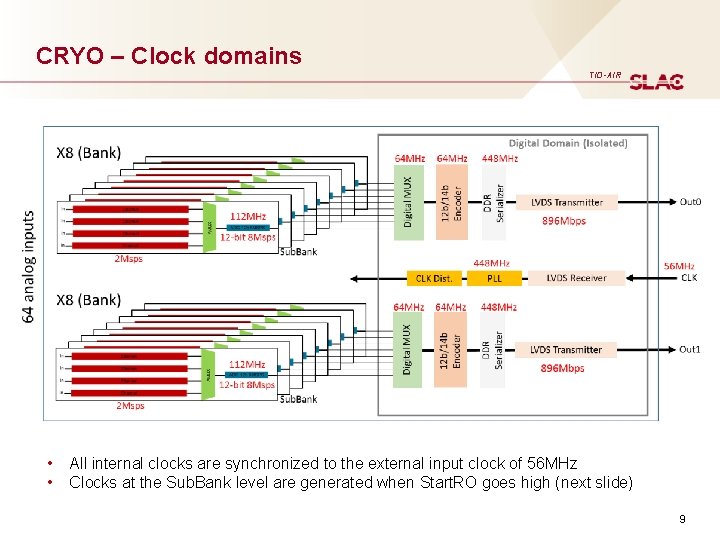

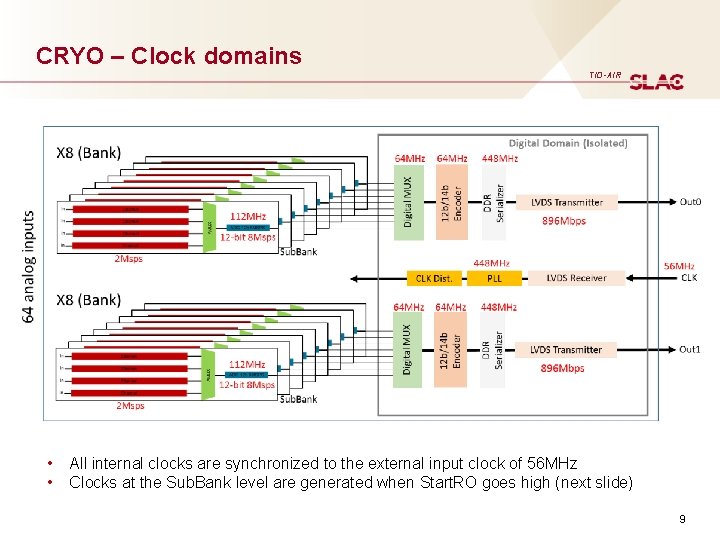

CRYO – Clock domains TID-AIR • • All internal clocks are synchronized to the external input clock of 56 MHz Clocks at the Sub. Bank level are generated when Start. RO goes high (next slide) 9

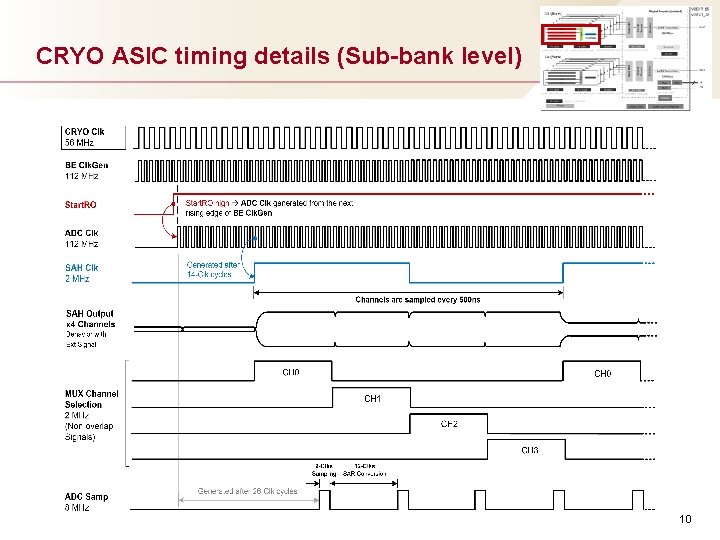

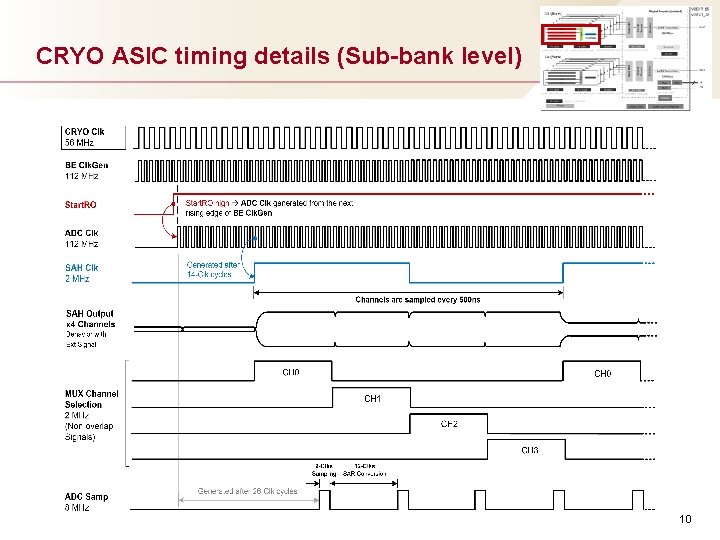

CRYO ASIC timing details (Sub-bank level) TID-AIR 10

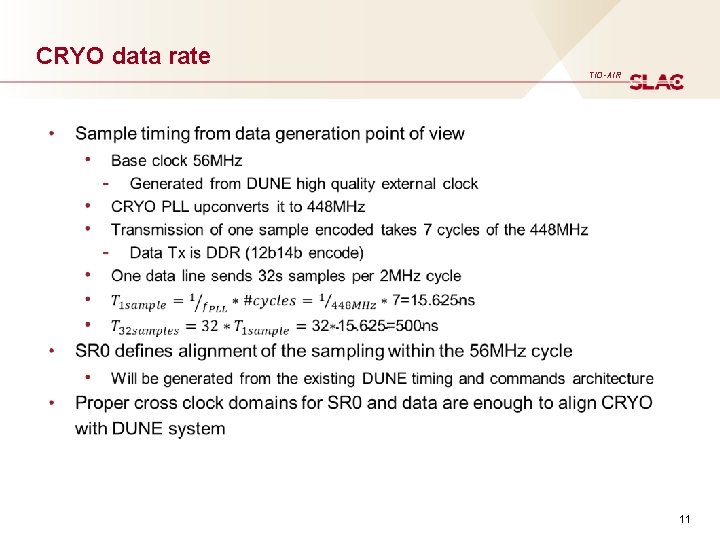

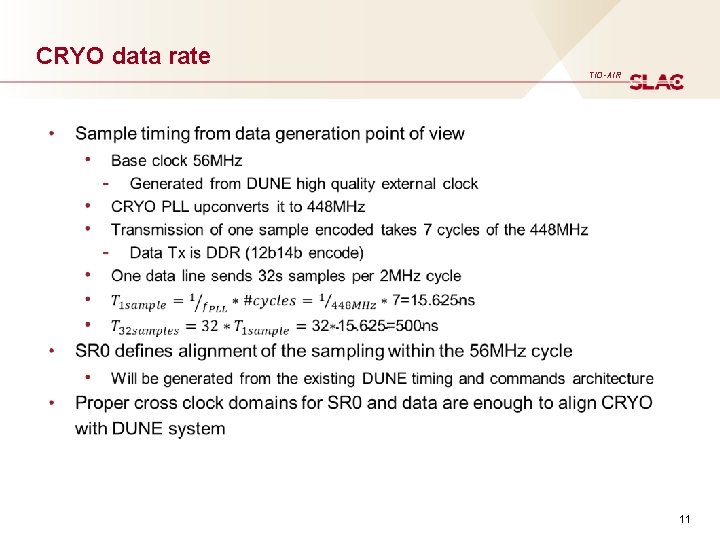

CRYO data rate TID-AIR 11

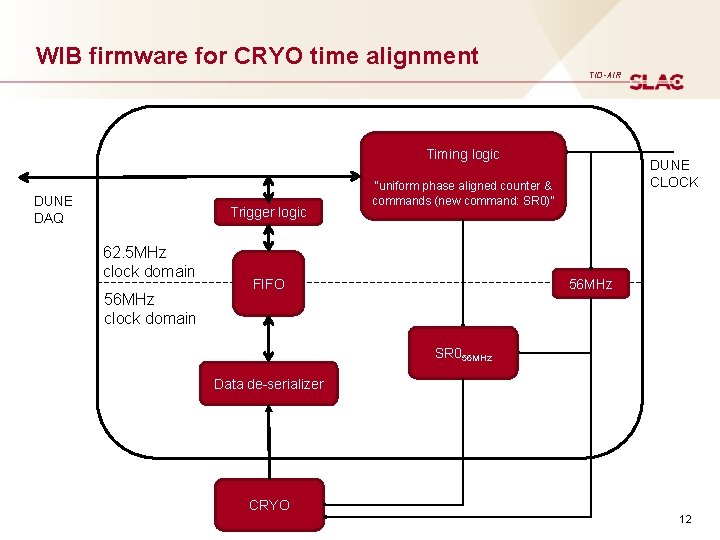

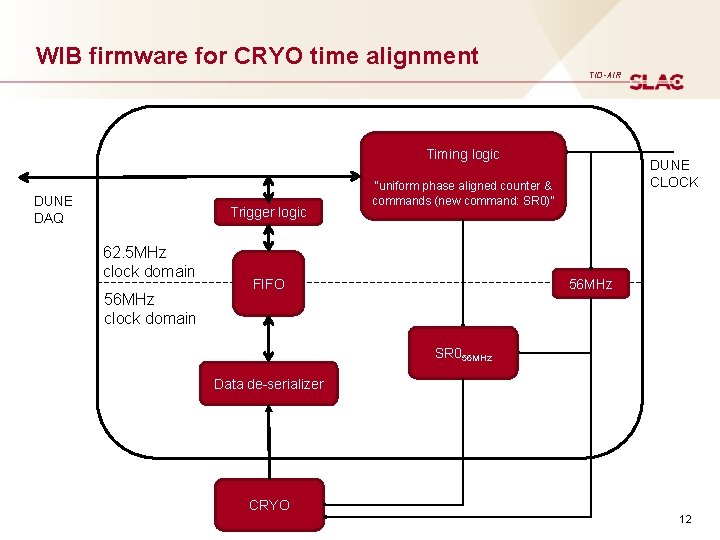

WIB firmware for CRYO time alignment TID-AIR Timing logic DUNE DAQ Trigger logic 62. 5 MHz clock domain 56 MHz clock domain DUNE CLOCK “uniform phase aligned counter & commands (new command: SR 0)” 56 MHz FIFO SR 056 MHz Data de-serializer CRYO 12