CRU Firmware User Logic Interface Specification Erno DAVID

- Slides: 6

CRU Firmware User Logic Interface Specification Erno DAVID Wigner Research Center for Physics (HU) 30 March, 2016

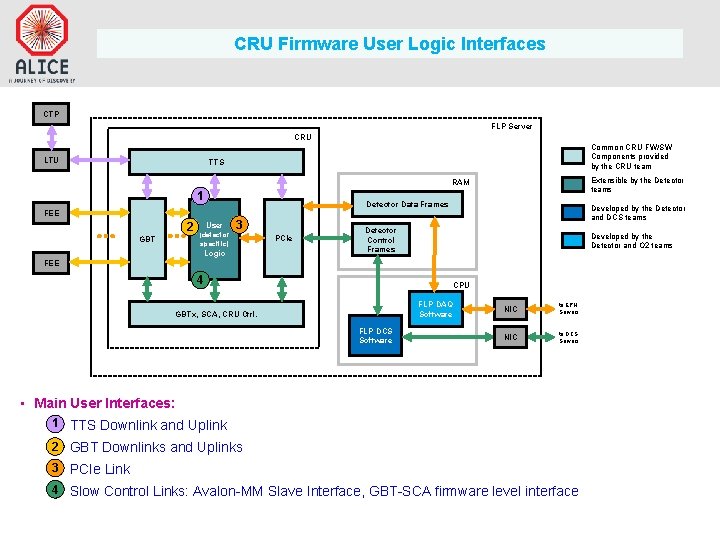

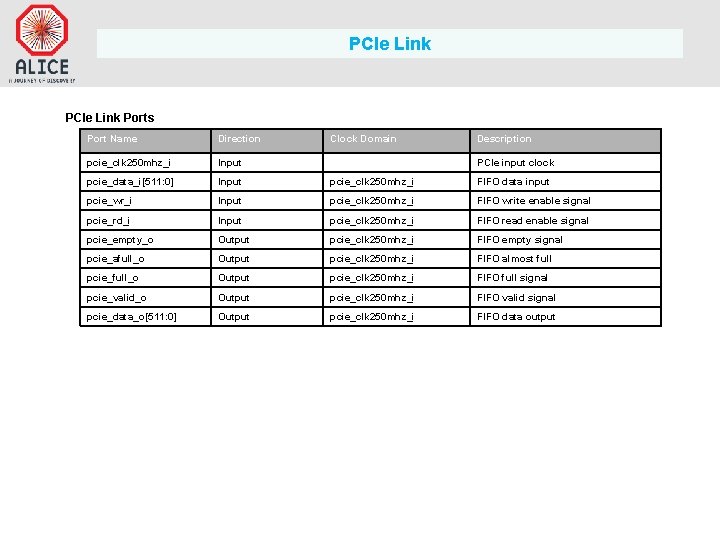

CRU Firmware User Logic Interfaces CTP FLP Server CRU LTU Common CRU FW/SW Components provided by the CRU team TTS Extensible by the Detector teams RAM 1 Detector Data Frames Developed by the Detector and DCS teams FEE 2 GBT User (detector specific) 3 Logic PCIe Detector Control Frames Developed by the Detector and O 2 teams FEE 4 CPU FLP DAQ Software GBTx, SCA, CRU Ctrl. FLP DCS Software NIC to EPN Servers NIC to DCS Servers • Main User Interfaces: 1 • TTS Downlink and Uplink 2 • GBT Downlinks and Uplinks 3 • PCIe Link 4 • Slow Control Links: Avalon-MM Slave Interface, GBT-SCA firmware level interface

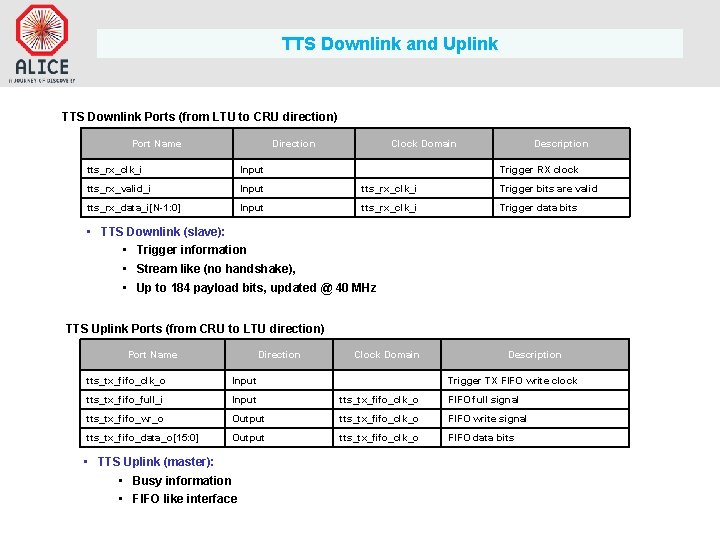

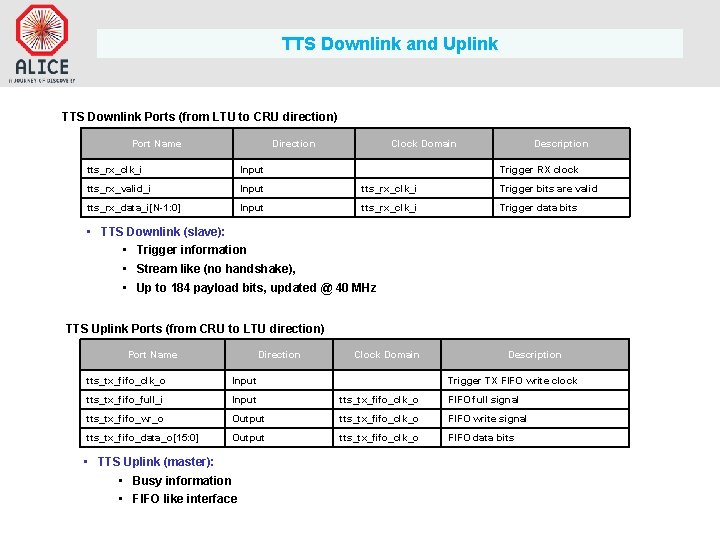

TTS Downlink and Uplink TTS Downlink Ports (from LTU to CRU direction) Port Name Direction Clock Domain Description tts_rx_clk_i Input Trigger RX clock tts_rx_valid_i Input tts_rx_clk_i Trigger bits are valid tts_rx_data_i[N-1: 0] Input tts_rx_clk_i Trigger data bits • TTS Downlink (slave): • Trigger information • Stream like (no handshake), • Up to 184 payload bits, updated @ 40 MHz TTS Uplink Ports (from CRU to LTU direction) Port Name Direction Clock Domain Description tts_tx_fifo_clk_o Input tts_tx_fifo_full_i Input tts_tx_fifo_clk_o FIFO full signal tts_tx_fifo_wr_o Output tts_tx_fifo_clk_o FIFO write signal tts_tx_fifo_data_o[15: 0] Output tts_tx_fifo_clk_o FIFO data bits • TTS Uplink (master): • Busy information • FIFO like interface Trigger TX FIFO write clock

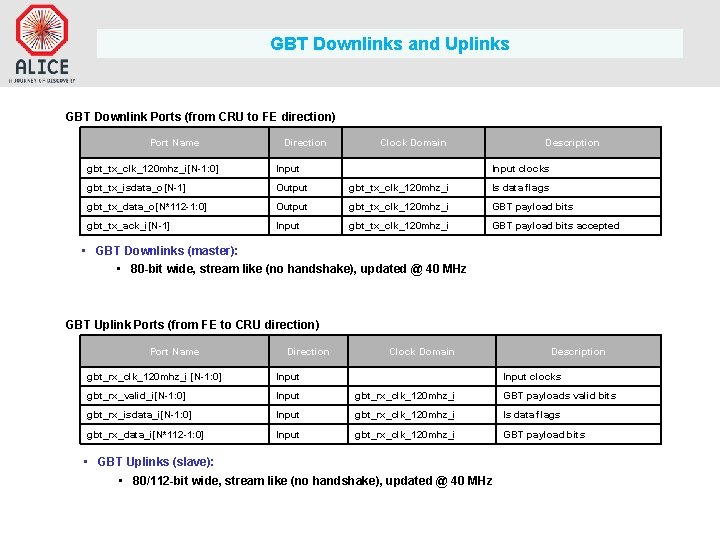

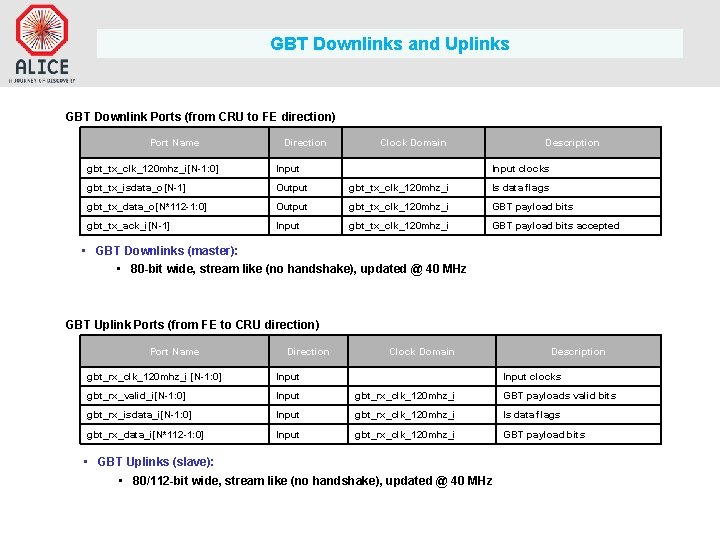

GBT Downlinks and Uplinks GBT Downlink Ports (from CRU to FE direction) Port Name Direction Clock Domain Description gbt_tx_clk_120 mhz_i[N-1: 0] Input clocks gbt_tx_isdata_o[N-1] Output gbt_tx_clk_120 mhz_i Is data flags gbt_tx_data_o[N*112 -1: 0] Output gbt_tx_clk_120 mhz_i GBT payload bits gbt_tx_ack_i[N-1] Input gbt_tx_clk_120 mhz_i GBT payload bits accepted • GBT Downlinks (master): • 80 -bit wide, stream like (no handshake), updated @ 40 MHz GBT Uplink Ports (from FE to CRU direction) Port Name Direction Clock Domain Description gbt_rx_clk_120 mhz_i [N-1: 0] Input clocks gbt_rx_valid_i[N-1: 0] Input gbt_rx_clk_120 mhz_i GBT payloads valid bits gbt_rx_isdata_i[N-1: 0] Input gbt_rx_clk_120 mhz_i Is data flags gbt_rx_data_i[N*112 -1: 0] Input gbt_rx_clk_120 mhz_i GBT payload bits • GBT Uplinks (slave): • 80/112 -bit wide, stream like (no handshake), updated @ 40 MHz

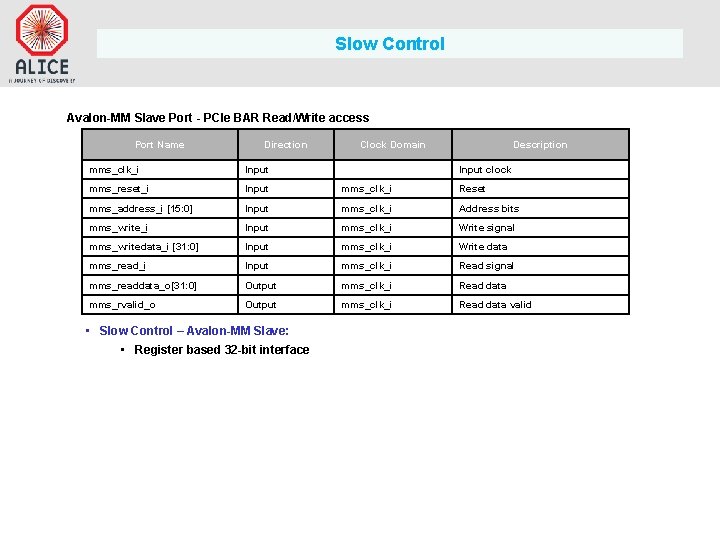

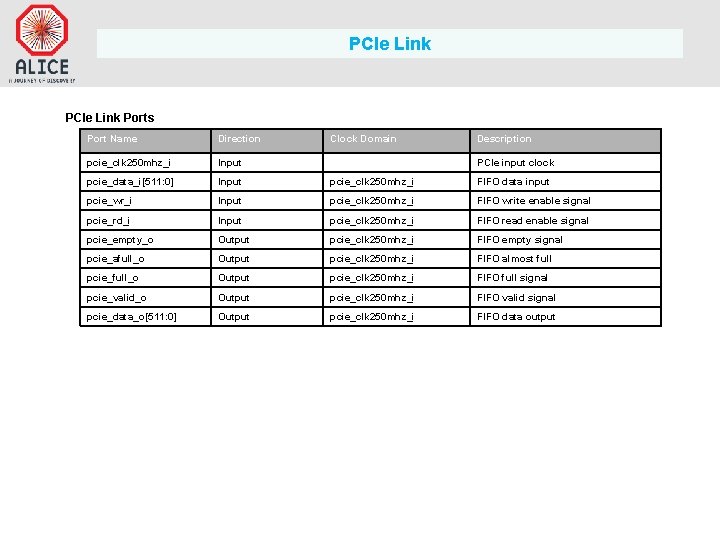

PCIe Link Ports Port Name Direction Clock Domain Description pcie_clk 250 mhz_i Input pcie_data_i[511: 0] Input pcie_clk 250 mhz_i FIFO data input pcie_wr_i Input pcie_clk 250 mhz_i FIFO write enable signal pcie_rd_i Input pcie_clk 250 mhz_i FIFO read enable signal pcie_empty_o Output pcie_clk 250 mhz_i FIFO empty signal pcie_afull_o Output pcie_clk 250 mhz_i FIFO almost full pcie_full_o Output pcie_clk 250 mhz_i FIFO full signal pcie_valid_o Output pcie_clk 250 mhz_i FIFO valid signal pcie_data_o[511: 0] Output pcie_clk 250 mhz_i FIFO data output PCIe input clock

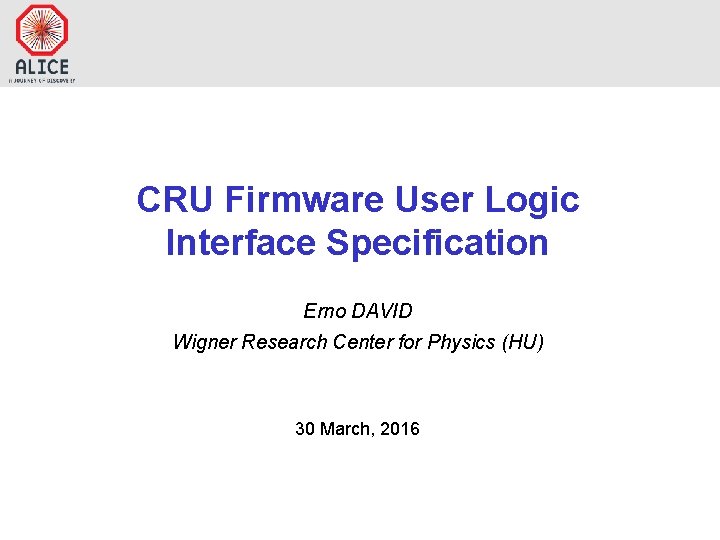

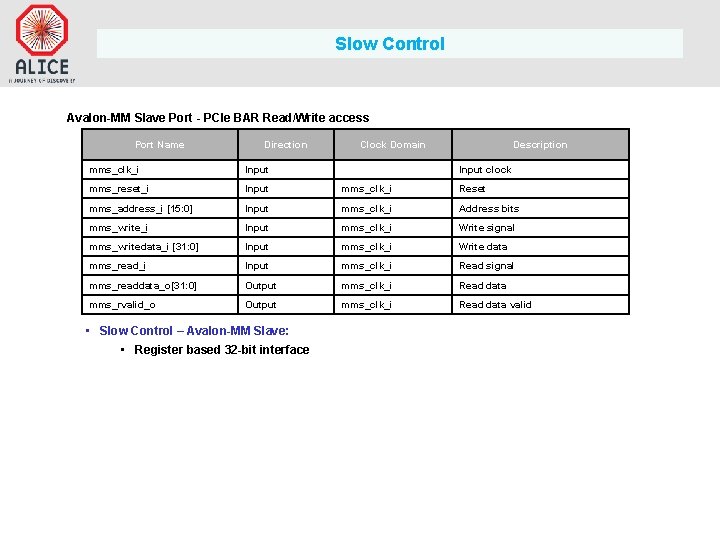

Slow Control Avalon-MM Slave Port - PCIe BAR Read/Write access Port Name Direction Clock Domain Description mms_clk_i Input mms_reset_i Input mms_clk_i Reset mms_address_i [15: 0] Input mms_clk_i Address bits mms_write_i Input mms_clk_i Write signal mms_writedata_i [31: 0] Input mms_clk_i Write data mms_read_i Input mms_clk_i Read signal mms_readdata_o[31: 0] Output mms_clk_i Read data mms_rvalid_o Output mms_clk_i Read data valid • Slow Control – Avalon-MM Slave: • Register based 32 -bit interface Input clock