Crosslayer Floorplan Optimization for Silicon Photonic No Cs

![Floorplan Optimization Flow [# of cores, core parameters, aspect ratio (AR)] 10 Floorplan Optimization Flow [# of cores, core parameters, aspect ratio (AR)] 10](https://slidetodoc.com/presentation_image_h/df52d875c80a8d89e30fd8c8bb0ab5f7/image-10.jpg)

- Slides: 31

Cross-layer Floorplan Optimization for Silicon Photonic No. Cs in Many-core Systems Ayse K. Coskun 3, Anjun Gu 1, Warren Jin 4, Ajay Joshi 3, Andrew B. Kahng 1, 2, Jonathan Klamkin 4, Yenai Ma 3, John Recchio 1, Vaishnav Srinivas 1 and Tiansheng Zhang 3 UCSD 1 ECE and 2 CSE Dept. ; 3 Boston University ECE Dept. ; 4 UCSB ECE Dept. This research has been partially funded by the NSF grants CNS-1149703 and CCF-1149549. Work at UCSD has been supported by NSF, Samsung and the IMPACT+ Center.

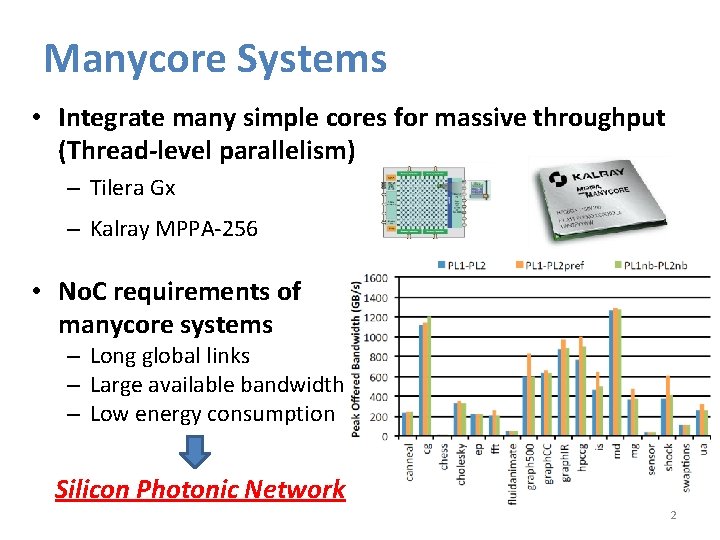

Manycore Systems • Integrate many simple cores for massive throughput (Thread-level parallelism) – Tilera Gx – Kalray MPPA-256 • No. C requirements of manycore systems – Long global links – Large available bandwidth – Low energy consumption Silicon Photonic Network 2

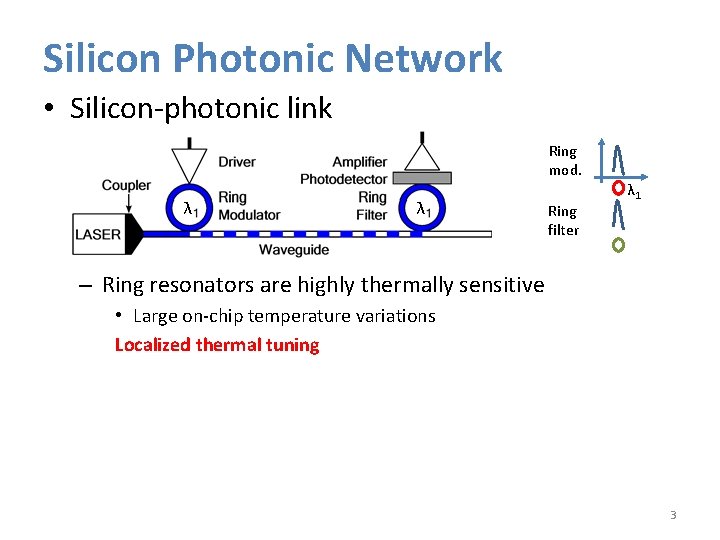

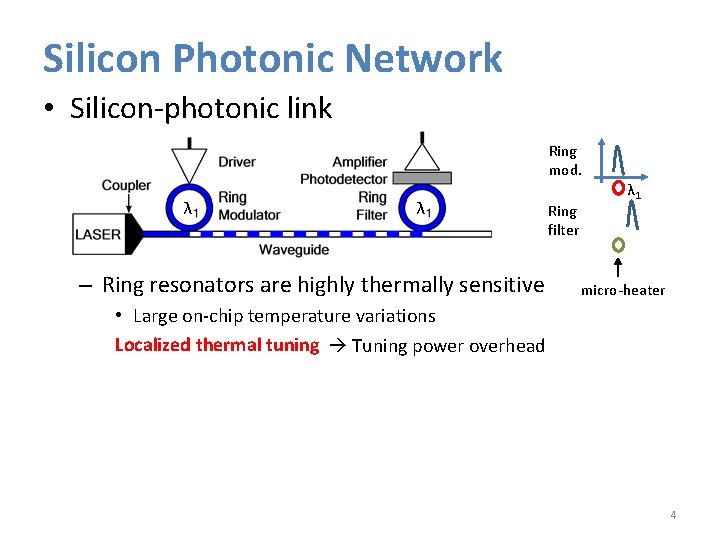

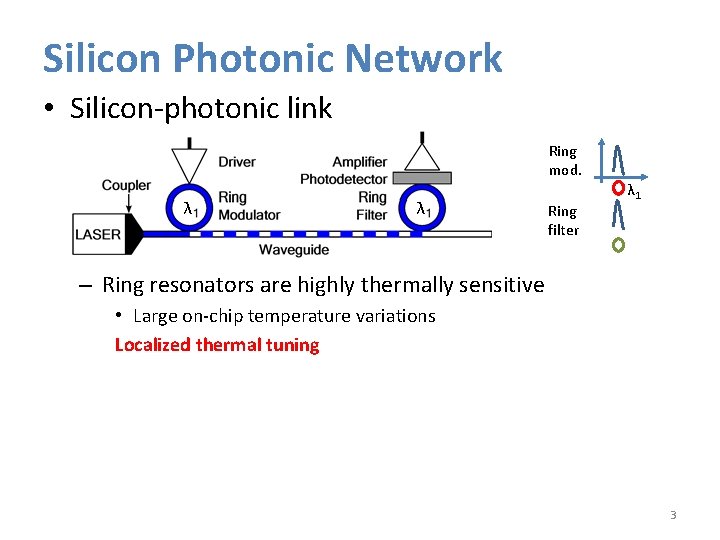

Silicon Photonic Network • Silicon-photonic link Ring mod. λ λ Ring filter λ 1 – Ring resonators are highly thermally sensitive • Large on-chip temperature variations Localized thermal tuning 3

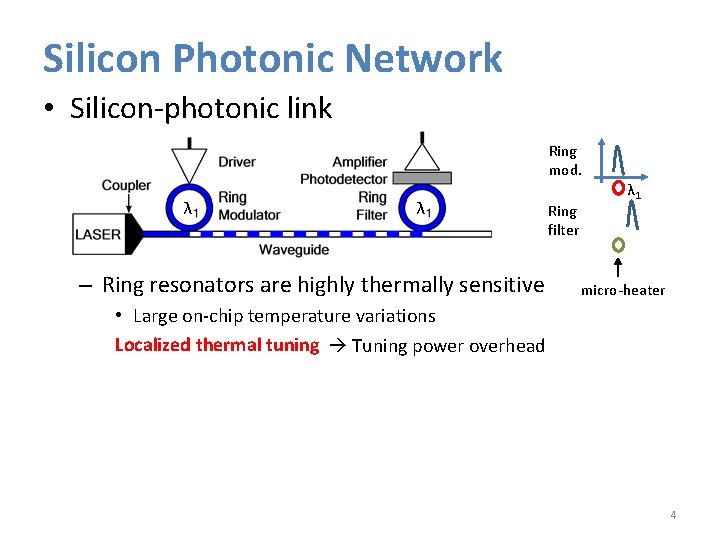

Silicon Photonic Network • Silicon-photonic link Ring mod. λ λ – Ring resonators are highly thermally sensitive Ring filter λ 1 micro-heater • Large on-chip temperature variations Localized thermal tuning Tuning power overhead 4

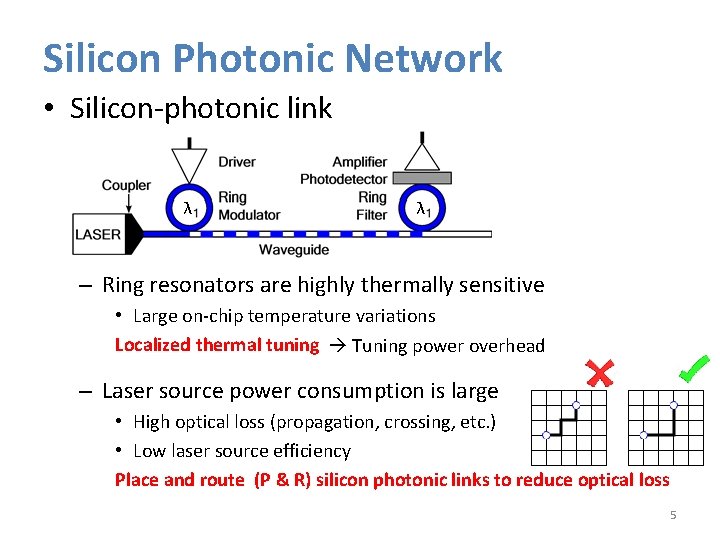

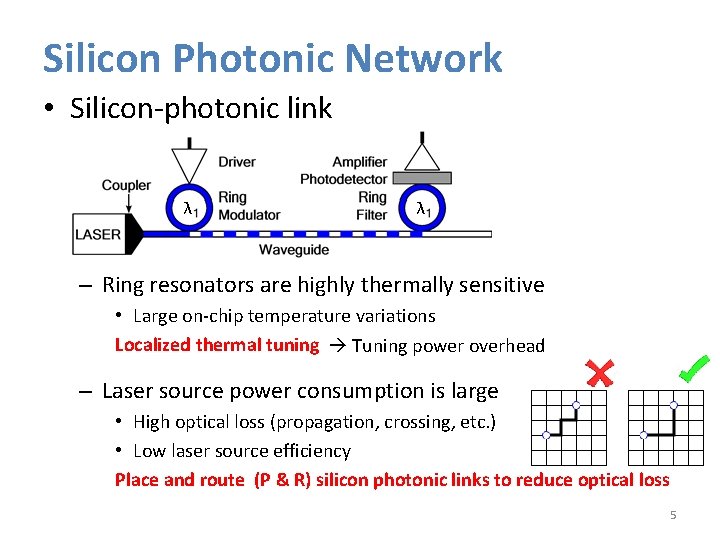

Silicon Photonic Network • Silicon-photonic link λ λ – Ring resonators are highly thermally sensitive • Large on-chip temperature variations Localized thermal tuning Tuning power overhead – Laser source power consumption is large • High optical loss (propagation, crossing, etc. ) • Low laser source efficiency Place and route (P & R) silicon photonic links to reduce optical loss 5

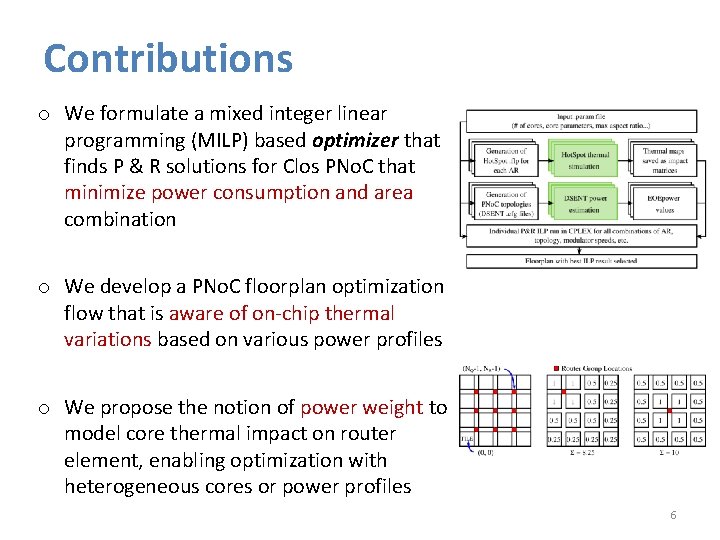

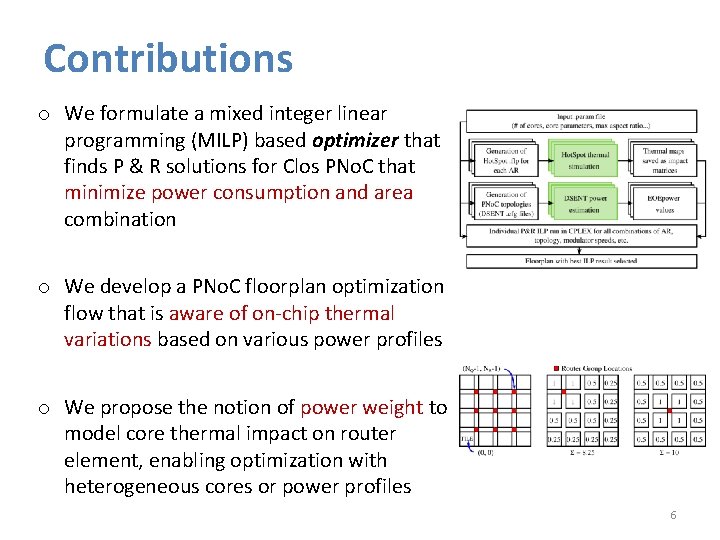

Contributions o We formulate a mixed integer linear programming (MILP) based optimizer that finds P & R solutions for Clos PNo. C that minimize power consumption and area combination o We develop a PNo. C floorplan optimization flow that is aware of on-chip thermal variations based on various power profiles o We propose the notion of power weight to model core thermal impact on router element, enabling optimization with heterogeneous cores or power profiles 6

Outline o Previous Work o Cross-layer Floorplan Optimization for PNo. Cs o Experimental Results o Conclusions 7

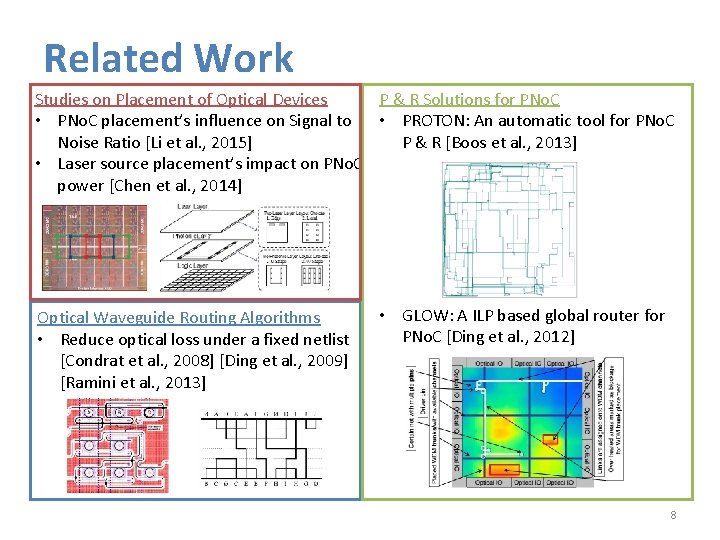

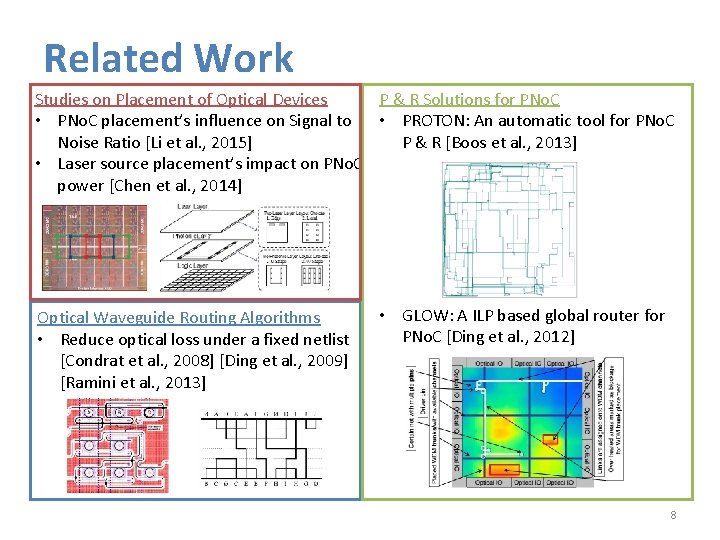

Related Work Studies on Placement of Optical Devices P & R Solutions for PNo. C • PNo. C placement’s influence on Signal to • PROTON: An automatic tool for PNo. C Noise Ratio [Li et al. , 2015] P & R [Boos et al. , 2013] • Laser source placement’s impact on PNo. C power [Chen et al. , 2014] Optical Waveguide Routing Algorithms • Reduce optical loss under a fixed netlist [Condrat et al. , 2008] [Ding et al. , 2009] [Ramini et al. , 2013] • GLOW: A ILP based global router for PNo. C [Ding et al. , 2012] 8

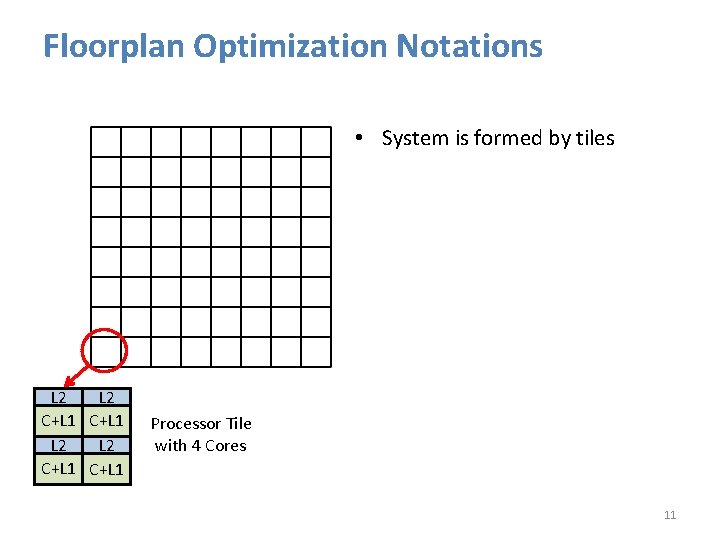

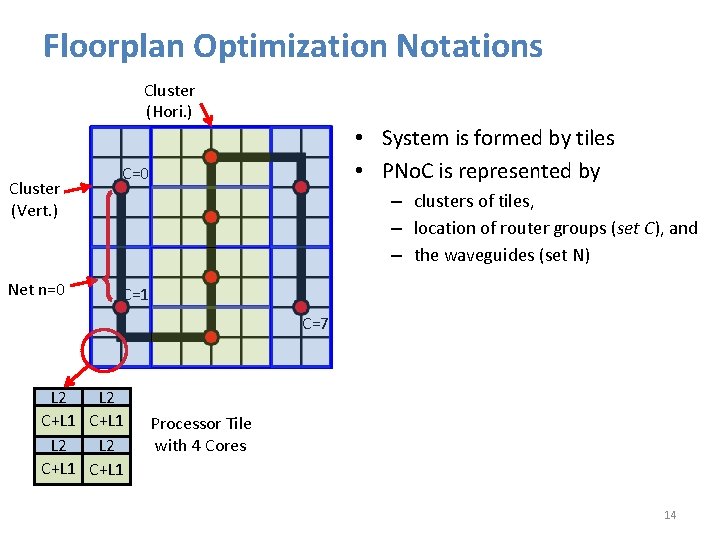

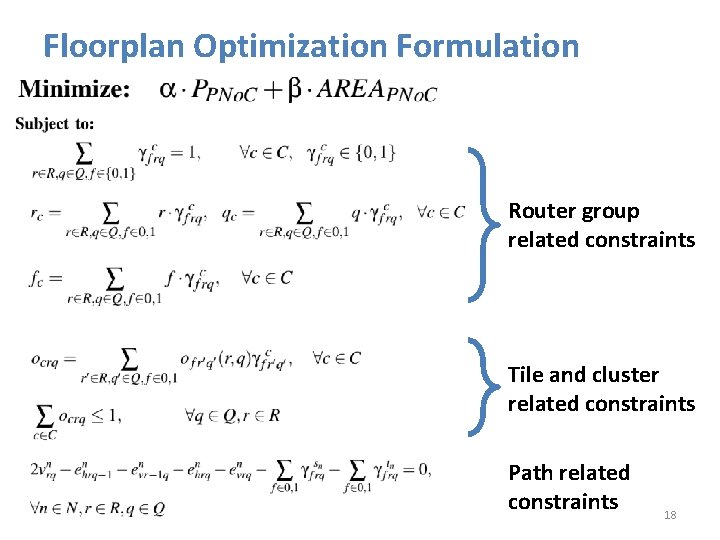

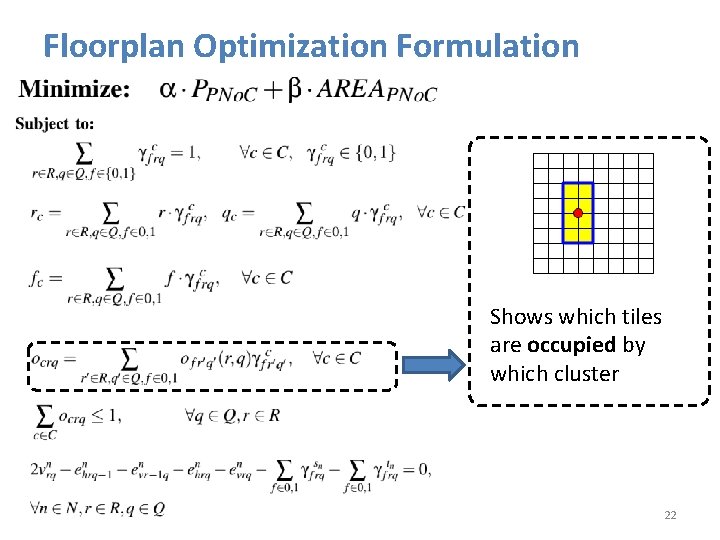

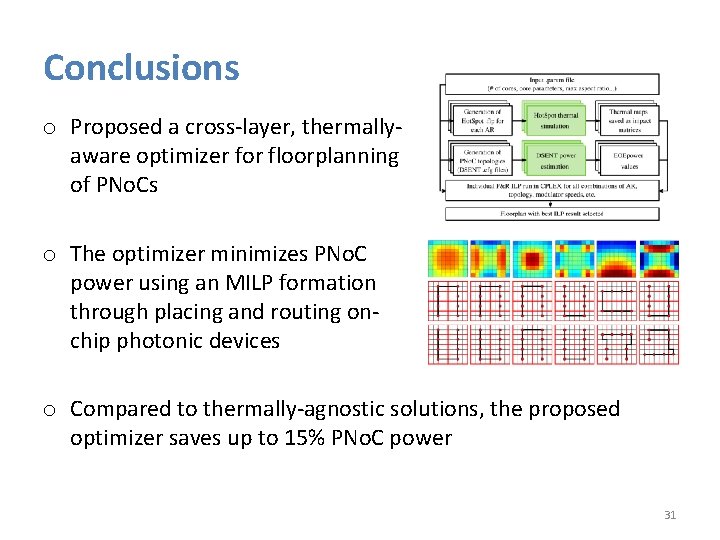

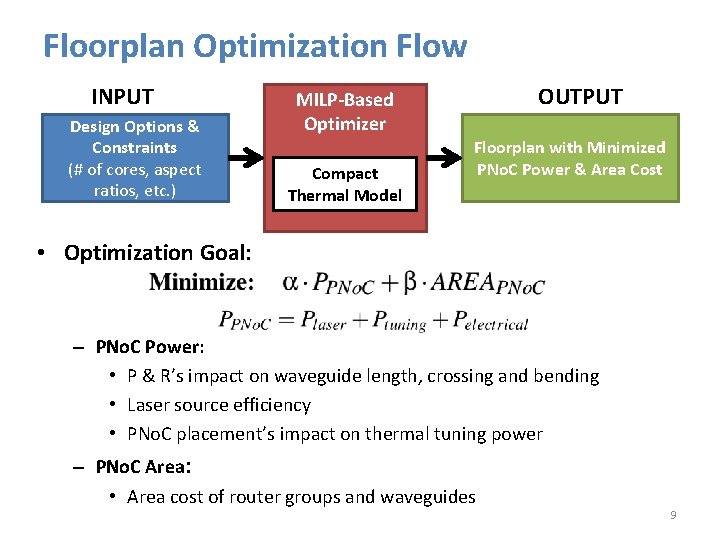

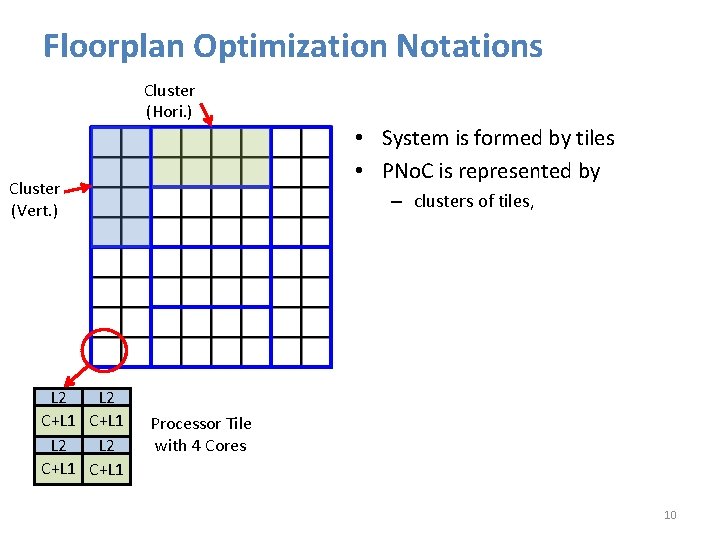

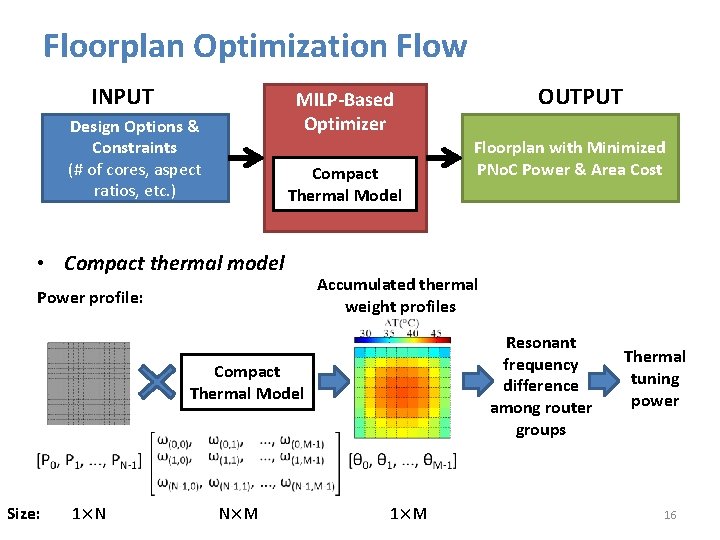

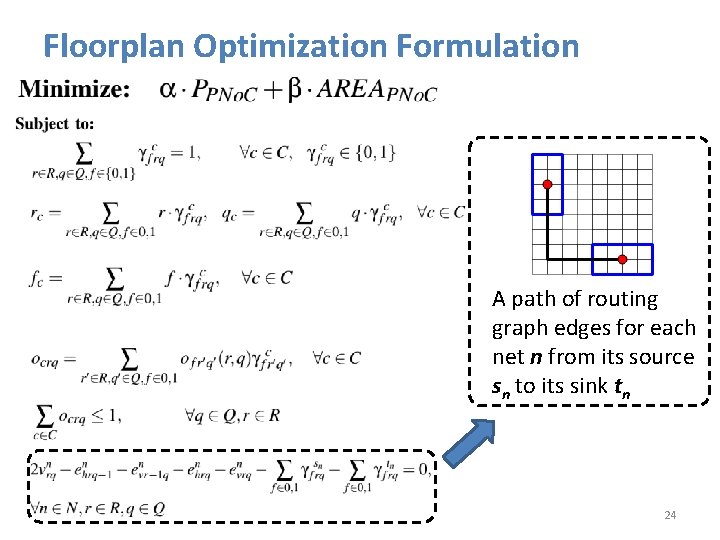

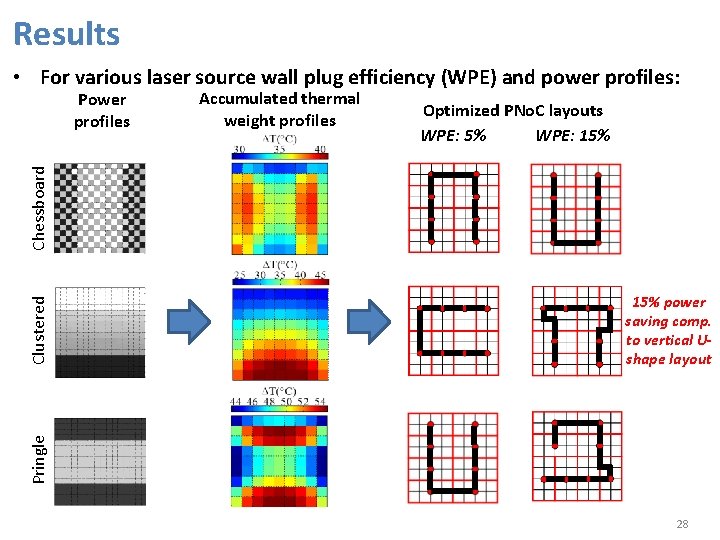

Floorplan Optimization Flow INPUT Design Options & Constraints (# of cores, aspect ratios, etc. ) OUTPUT MILP-Based Optimizer Compact Thermal Model Floorplan with Minimized PNo. C Power & Area Cost • Optimization Goal: – PNo. C Power: • P & R’s impact on waveguide length, crossing and bending • Laser source efficiency • PNo. C placement’s impact on thermal tuning power – PNo. C Area: • Area cost of router groups and waveguides 9

![Floorplan Optimization Flow of cores core parameters aspect ratio AR 10 Floorplan Optimization Flow [# of cores, core parameters, aspect ratio (AR)] 10](https://slidetodoc.com/presentation_image_h/df52d875c80a8d89e30fd8c8bb0ab5f7/image-10.jpg)

Floorplan Optimization Flow [# of cores, core parameters, aspect ratio (AR)] 10

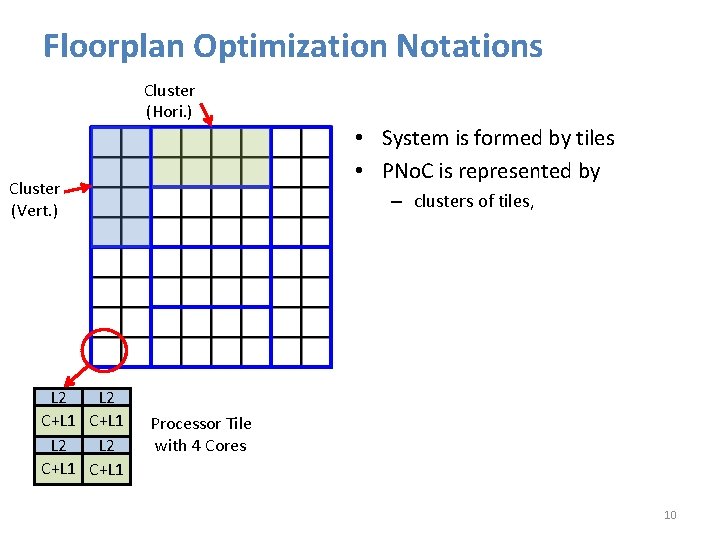

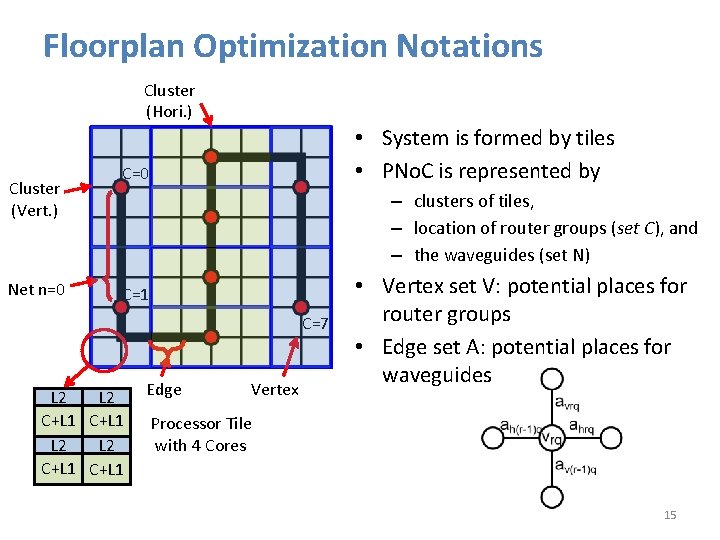

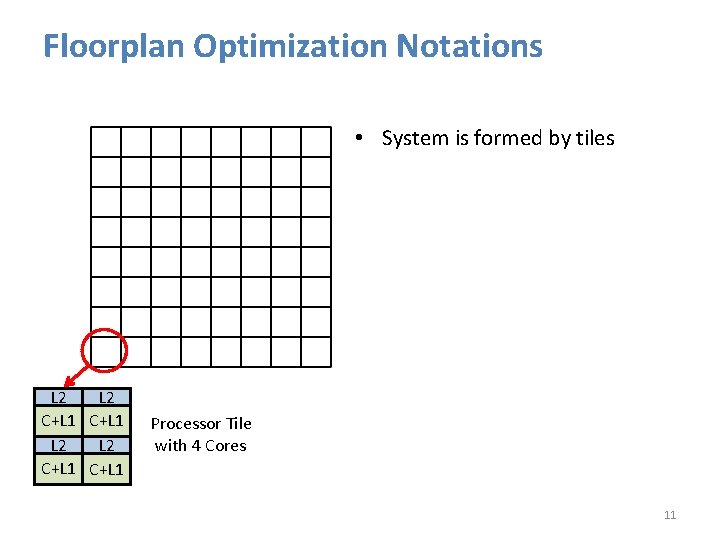

Floorplan Optimization Notations • System is formed by tiles L 2 L 2 C+L 1 Processor Tile with 4 Cores 11

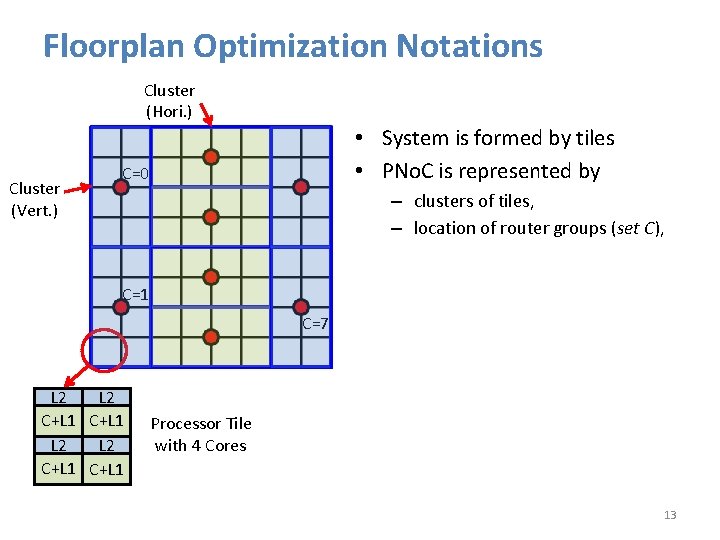

Floorplan Optimization Notations Cluster (Hori. ) • System is formed by tiles • PNo. C is represented by Cluster (Vert. ) L 2 L 2 C+L 1 – clusters of tiles, Processor Tile with 4 Cores 10

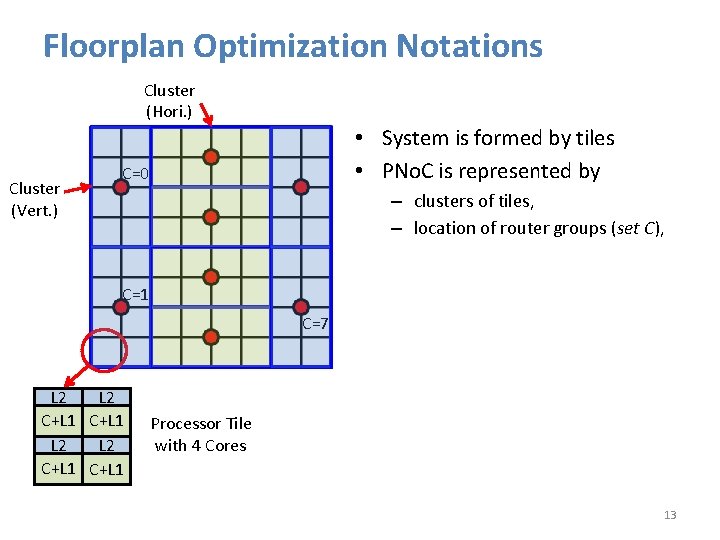

Floorplan Optimization Notations Cluster (Hori. ) Cluster (Vert. ) • System is formed by tiles • PNo. C is represented by C=0 – clusters of tiles, – location of router groups (set C), C=1 C=7 L 2 L 2 C+L 1 Processor Tile with 4 Cores 13

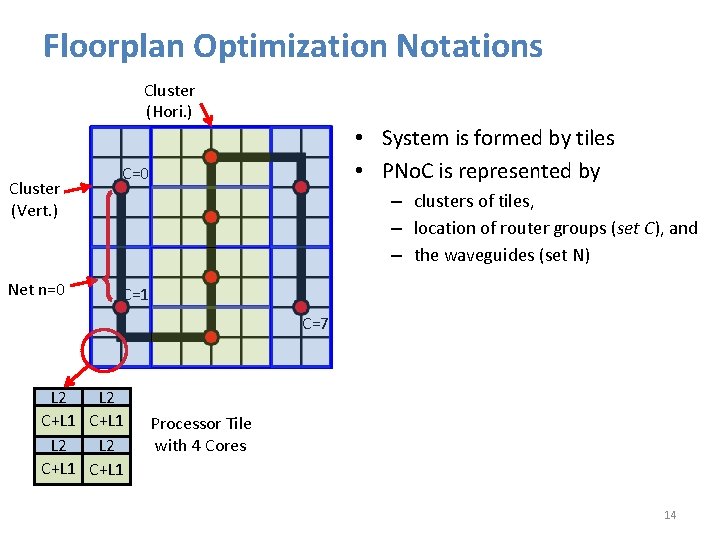

Floorplan Optimization Notations Cluster (Hori. ) Cluster (Vert. ) Net n=0 • System is formed by tiles • PNo. C is represented by C=0 – clusters of tiles, – location of router groups (set C), and – the waveguides (set N) C=1 C=7 L 2 L 2 C+L 1 Processor Tile with 4 Cores 14

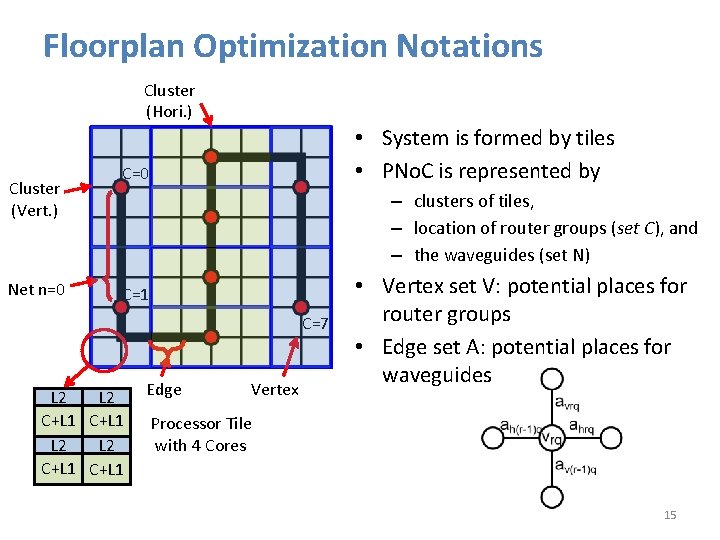

Floorplan Optimization Notations Cluster (Hori. ) Cluster (Vert. ) Net n=0 • System is formed by tiles • PNo. C is represented by C=0 – clusters of tiles, – location of router groups (set C), and – the waveguides (set N) C=1 C=7 L 2 L 2 C+L 1 Edge Vertex • Vertex set V: potential places for router groups • Edge set A: potential places for waveguides Processor Tile with 4 Cores 15

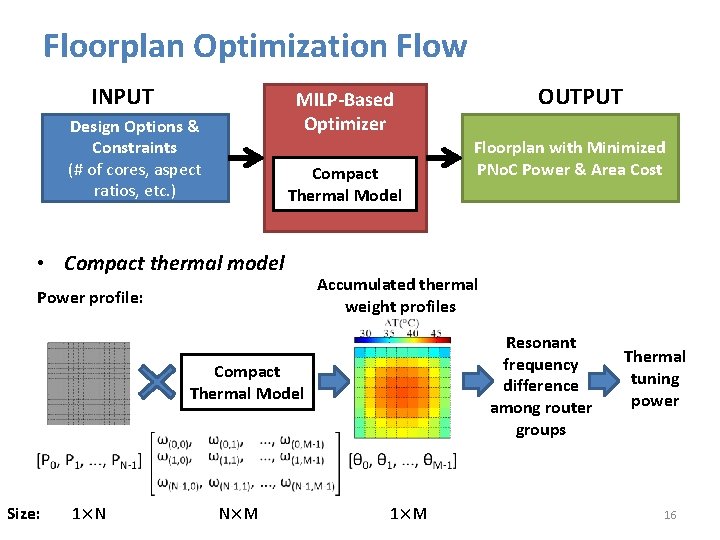

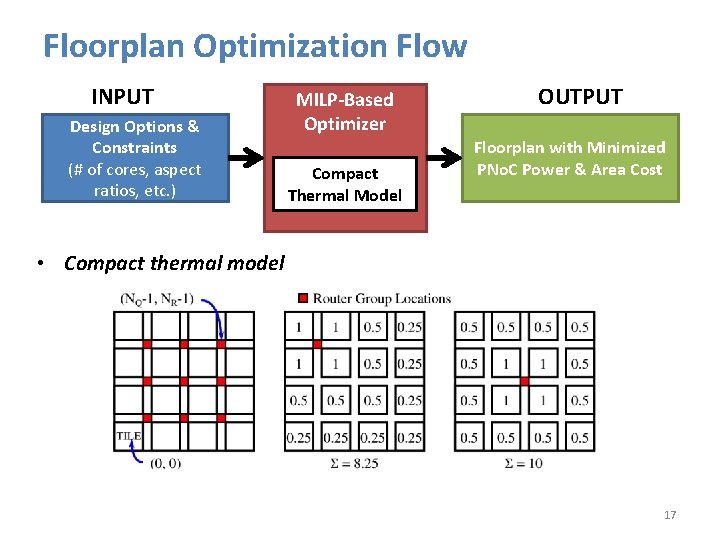

Floorplan Optimization Flow INPUT Design Options & Constraints (# of cores, aspect ratios, etc. ) Compact Thermal Model • Compact thermal model Power profile: 1×N N×M Floorplan with Minimized PNo. C Power & Area Cost Accumulated thermal weight profiles Resonant frequency difference among router groups Compact Thermal Model Size: OUTPUT MILP-Based Optimizer 1×M Thermal tuning power 16

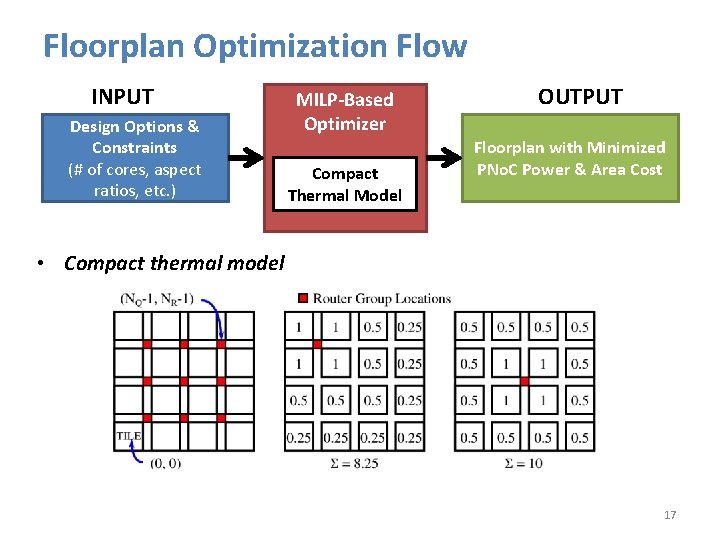

Floorplan Optimization Flow INPUT Design Options & Constraints (# of cores, aspect ratios, etc. ) MILP-Based Optimizer Compact Thermal Model OUTPUT Floorplan with Minimized PNo. C Power & Area Cost • Compact thermal model 17

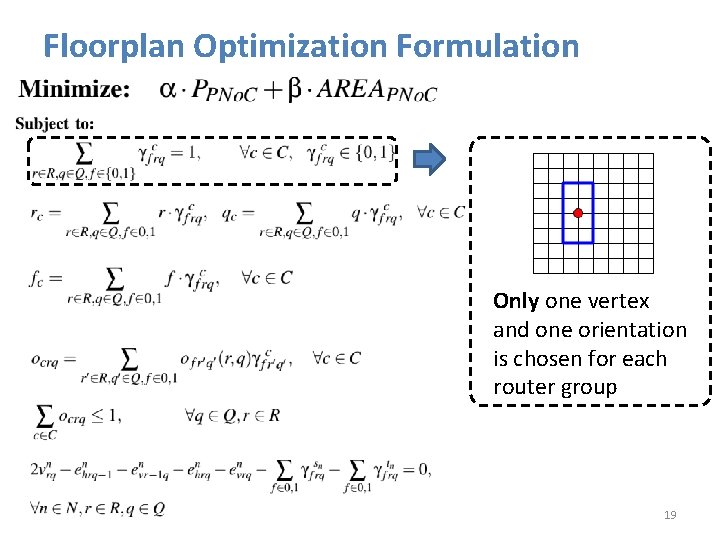

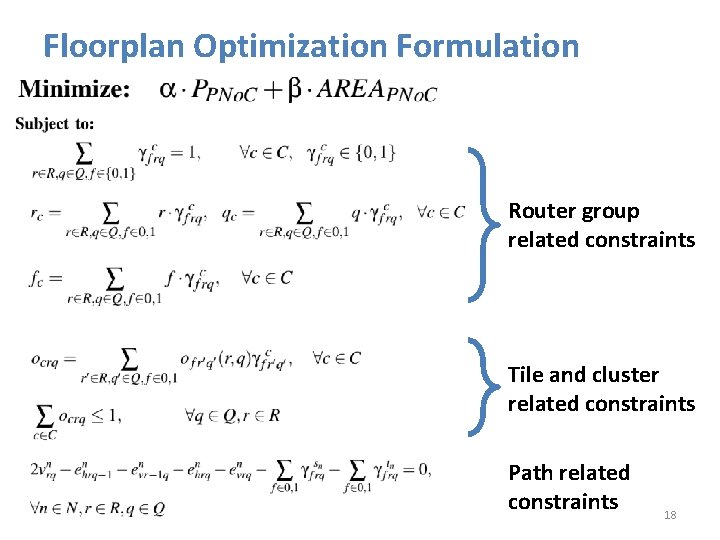

Floorplan Optimization Formulation Router group related constraints Tile and cluster related constraints Path related constraints 18

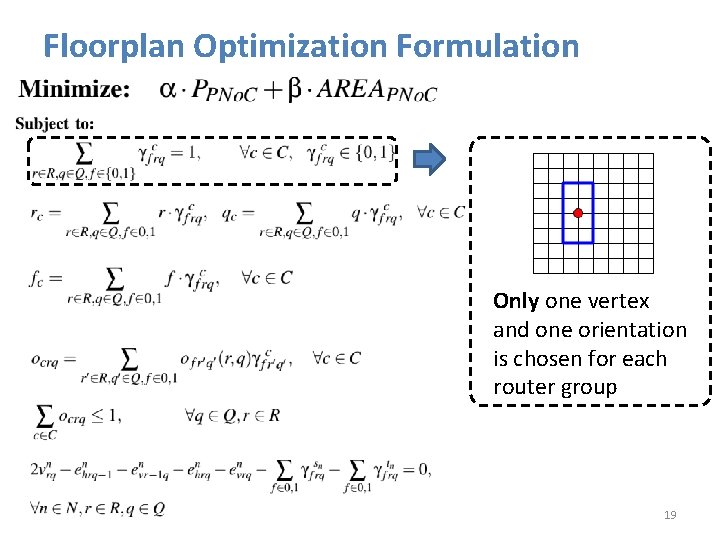

Floorplan Optimization Formulation Only one vertex and one orientation is chosen for each router group 19

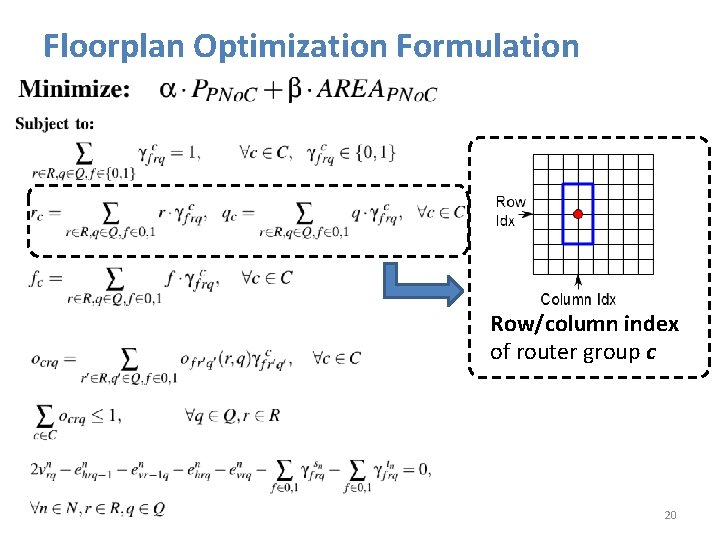

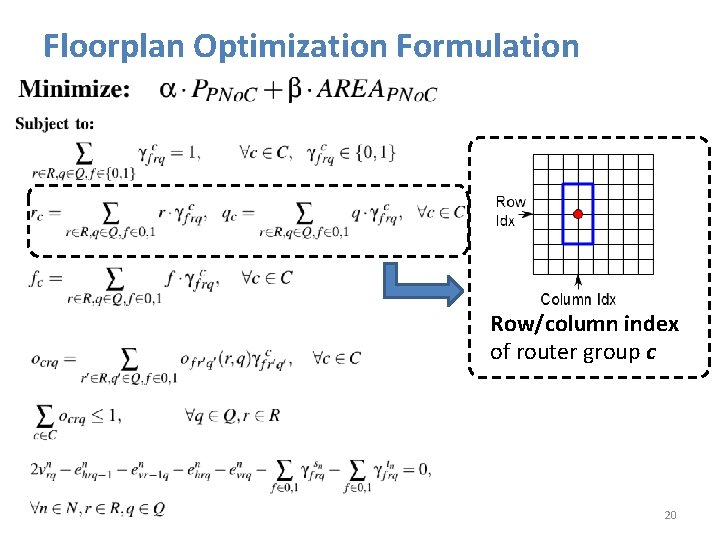

Floorplan Optimization Formulation Row/column index of router group c 20

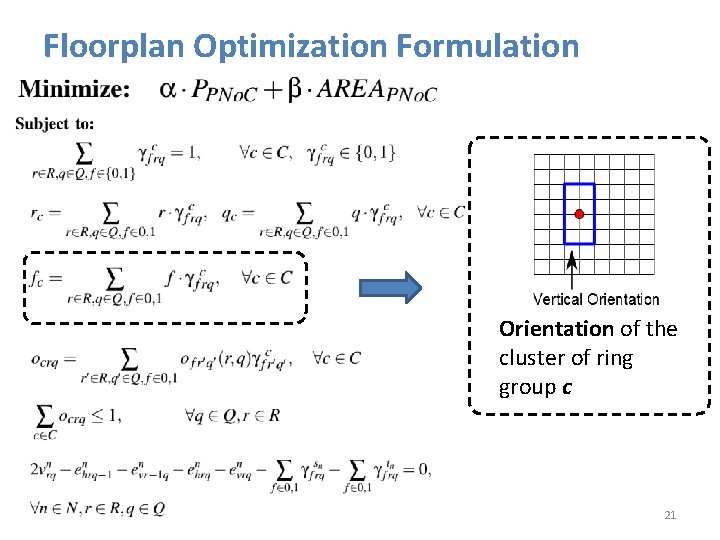

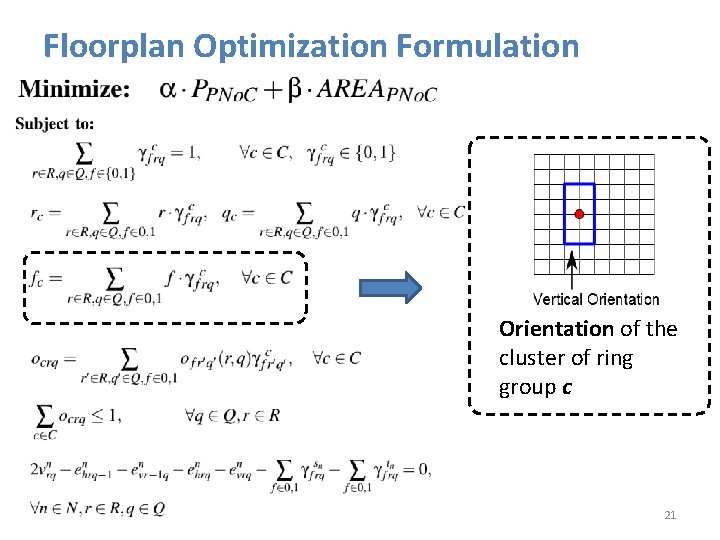

Floorplan Optimization Formulation Orientation of the cluster of ring group c 21

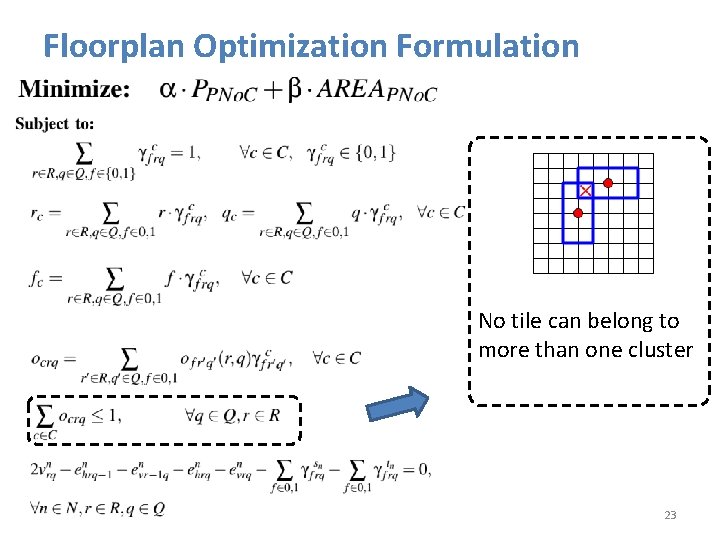

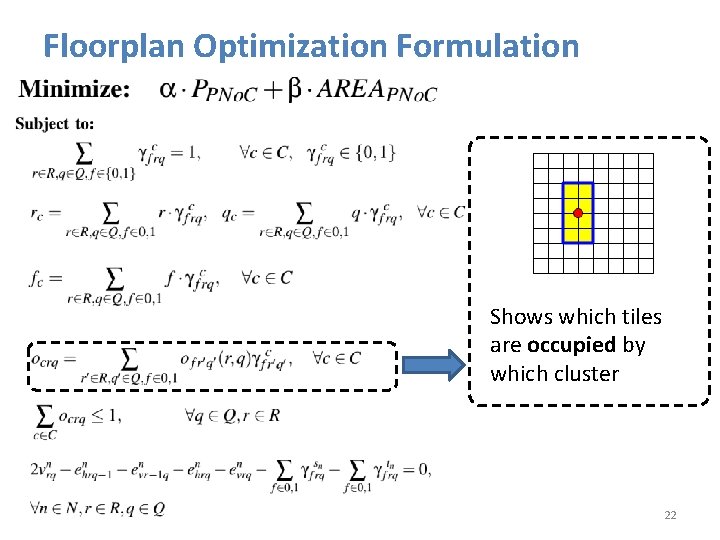

Floorplan Optimization Formulation Shows which tiles are occupied by which cluster 22

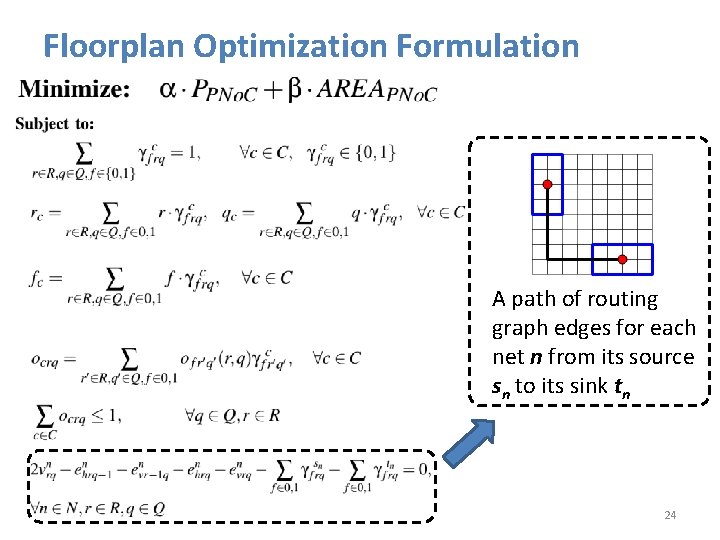

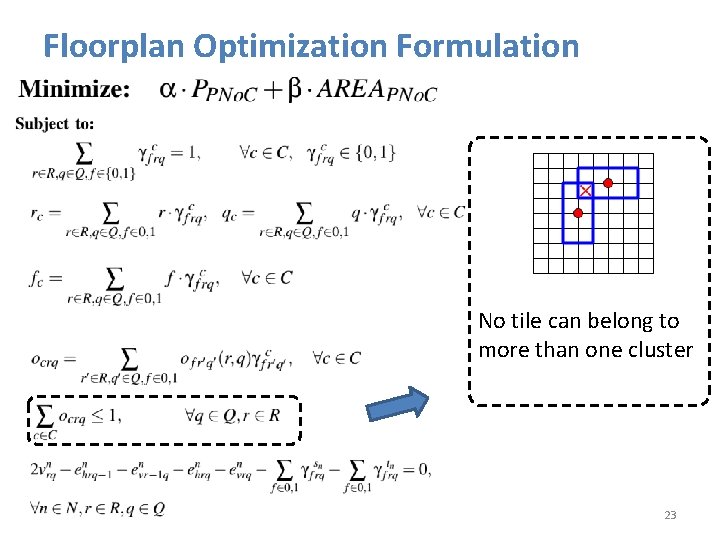

Floorplan Optimization Formulation No tile can belong to more than one cluster 23

Floorplan Optimization Formulation A path of routing graph edges for each net n from its source sn to its sink tn 24

Outline o Previous Work o Cross-layer Floorplan Optimization for PNo. Cs o Experimental Results o Conclusions 25

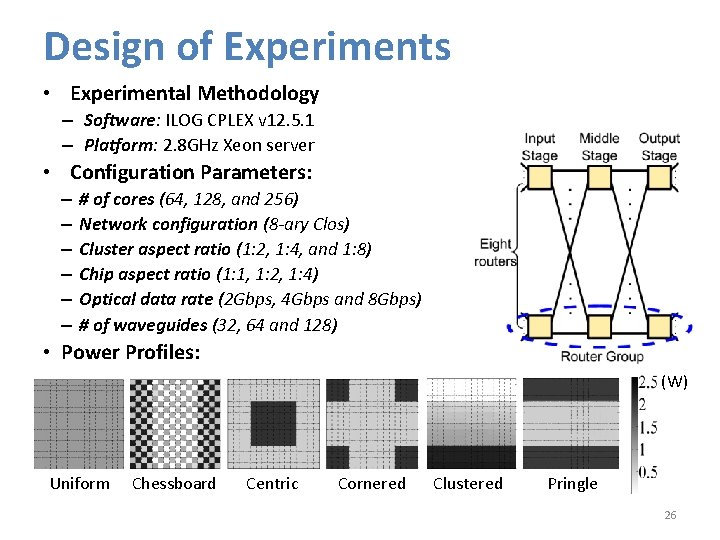

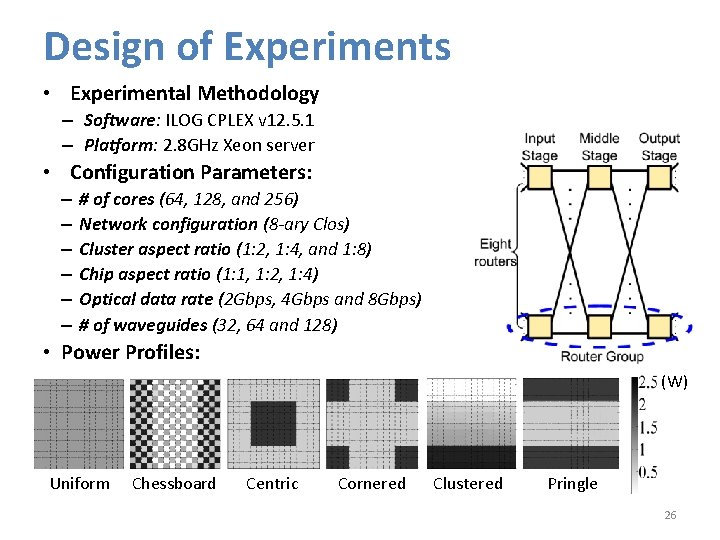

Design of Experiments • Experimental Methodology – Software: ILOG CPLEX v 12. 5. 1 – Platform: 2. 8 GHz Xeon server • Configuration Parameters: – – – # of cores (64, 128, and 256) Network configuration (8 -ary Clos) Cluster aspect ratio (1: 2, 1: 4, and 1: 8) Chip aspect ratio (1: 1, 1: 2, 1: 4) Optical data rate (2 Gbps, 4 Gbps and 8 Gbps) # of waveguides (32, 64 and 128) • Power Profiles: (W) Uniform Chessboard Centric Cornered Clustered Pringle 26

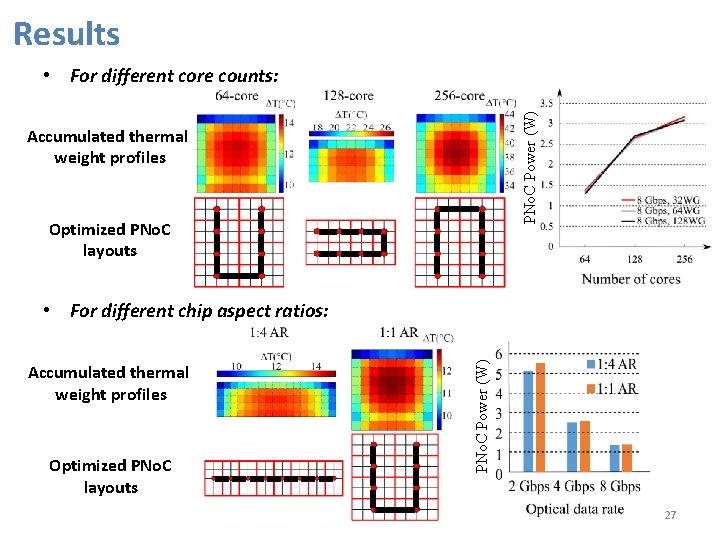

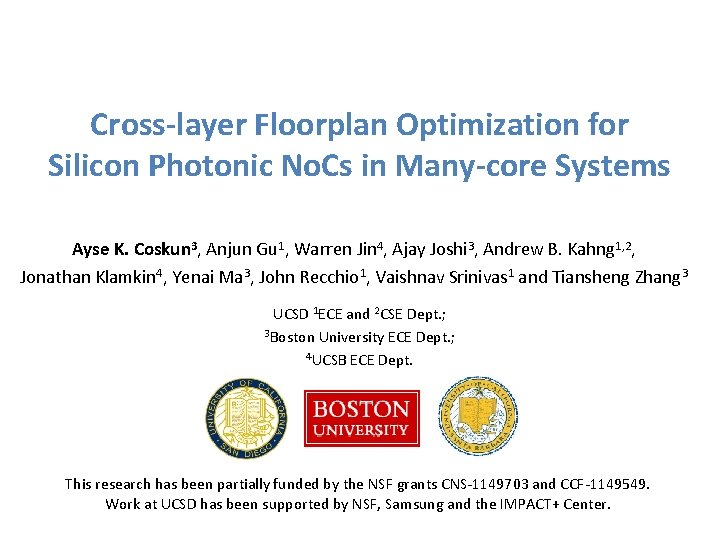

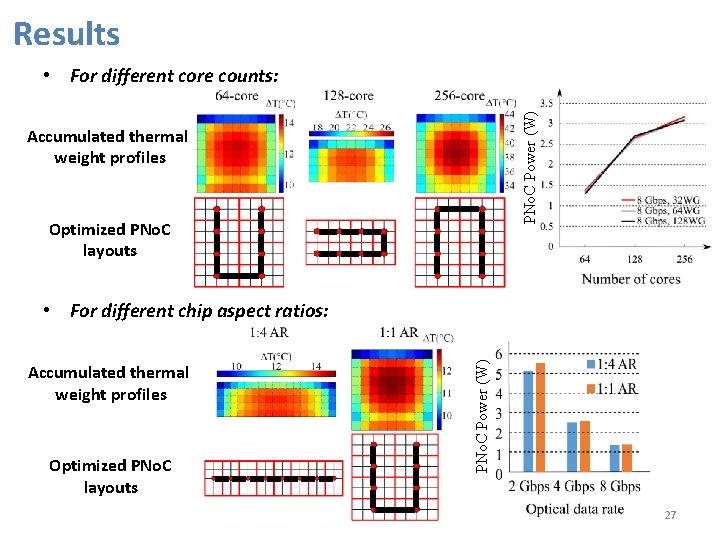

Results PNo. C Power (W) • For different core counts: Accumulated thermal weight profiles Optimized PNo. C layouts PNo. C Power (W) • For different chip aspect ratios: 27

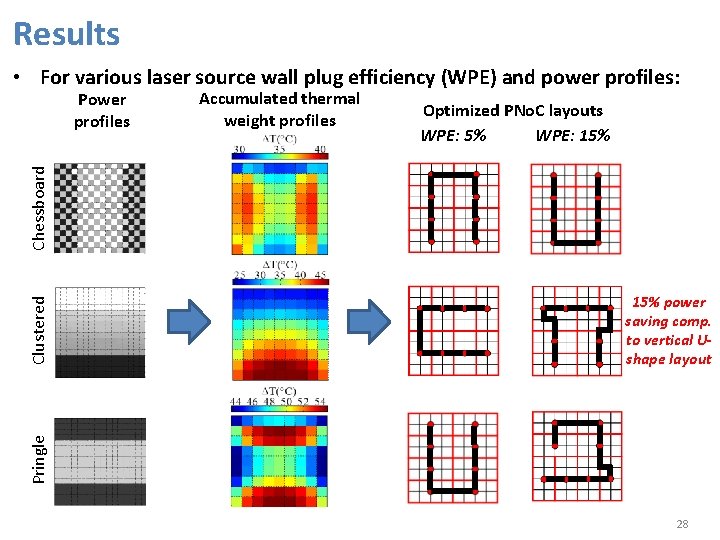

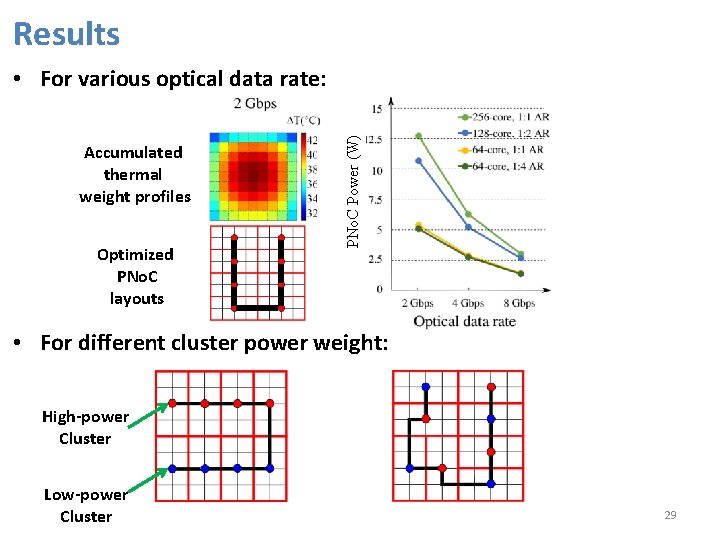

Results • For various laser source wall plug efficiency (WPE) and power profiles: Accumulated thermal weight profiles Optimized PNo. C layouts WPE: 15% WPE: 5% 15% power saving comp. to vertical Ushape layout Pringle Clustered Chessboard Power profiles 28

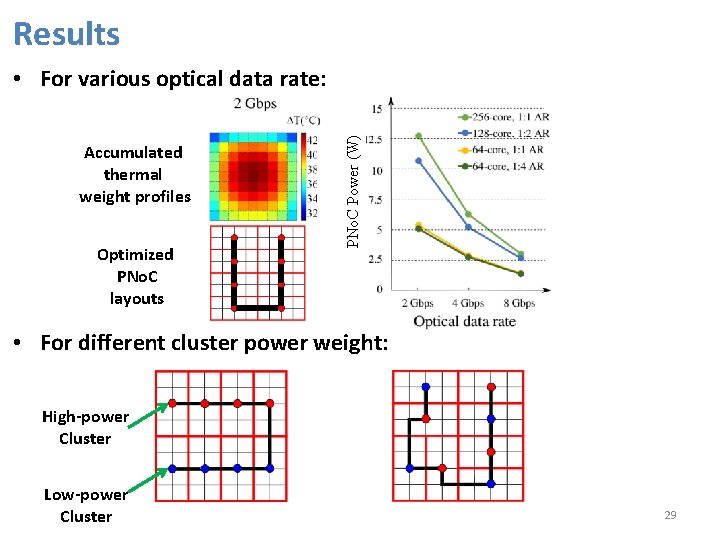

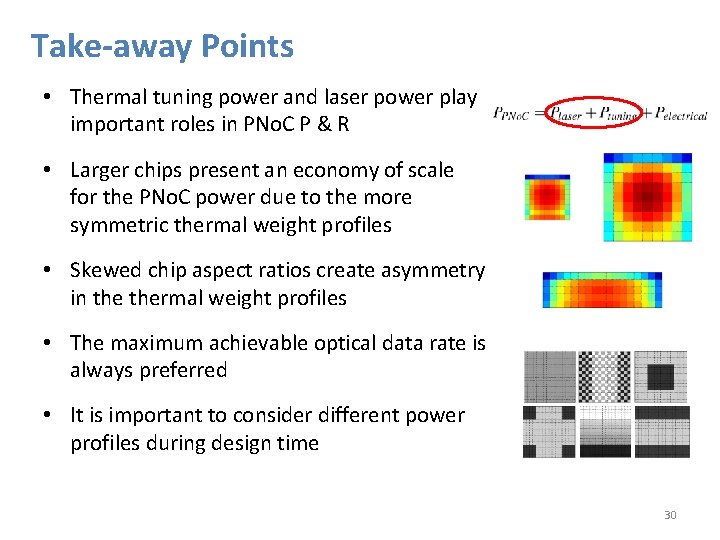

Results Accumulated thermal weight profiles Optimized PNo. C layouts PNo. C Power (W) • For various optical data rate: • For different cluster power weight: High-power Cluster Low-power Cluster 29

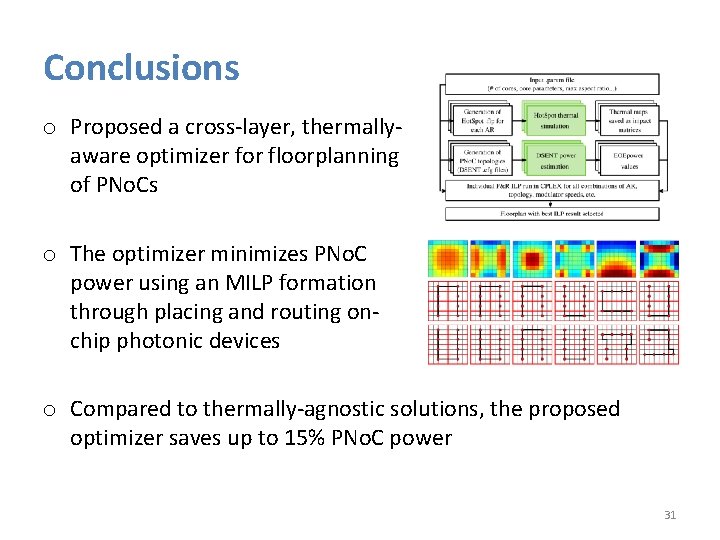

Take-away Points • Thermal tuning power and laser power play important roles in PNo. C P & R • Larger chips present an economy of scale for the PNo. C power due to the more symmetric thermal weight profiles • Skewed chip aspect ratios create asymmetry in thermal weight profiles • The maximum achievable optical data rate is always preferred • It is important to consider different power profiles during design time 30

Conclusions o Proposed a cross-layer, thermallyaware optimizer for floorplanning of PNo. Cs o The optimizer minimizes PNo. C power using an MILP formation through placing and routing onchip photonic devices o Compared to thermally-agnostic solutions, the proposed optimizer saves up to 15% PNo. C power 31