Crossbar switches By Alejandro Ayala Hardware design l

Crossbar switches By Alejandro Ayala

Hardware design l Show hardware design of several modern crossbar switches used for multiprocessing system on chip or multicore design.

![AMD Opteron Architecture [1] l Integrated N. Bridge l Data & Command packets are AMD Opteron Architecture [1] l Integrated N. Bridge l Data & Command packets are](http://slidetodoc.com/presentation_image/30bd76798f1c2164890928e55c5046a0/image-3.jpg)

AMD Opteron Architecture [1] l Integrated N. Bridge l Data & Command packets are separated

![Intel Xeon 7500 [2] Intel Xeon 7500 [2]](http://slidetodoc.com/presentation_image/30bd76798f1c2164890928e55c5046a0/image-4.jpg)

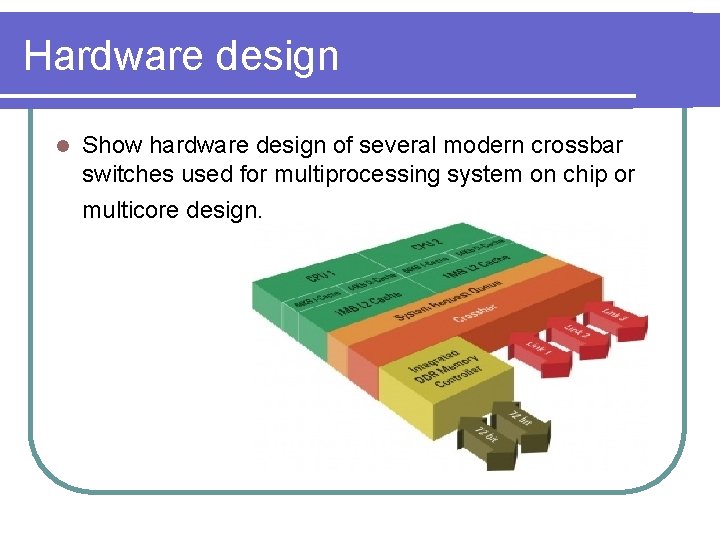

Intel Xeon 7500 [2]

Intel Xeon 7500 (cont) 8 port (each 80 bit) l Intel Quick. Path Interconnect communication l

![Ultra. SPARC T 2 [4] pipeline crossbar l High-bandwidth l 8 x 9 x. Ultra. SPARC T 2 [4] pipeline crossbar l High-bandwidth l 8 x 9 x.](http://slidetodoc.com/presentation_image/30bd76798f1c2164890928e55c5046a0/image-6.jpg)

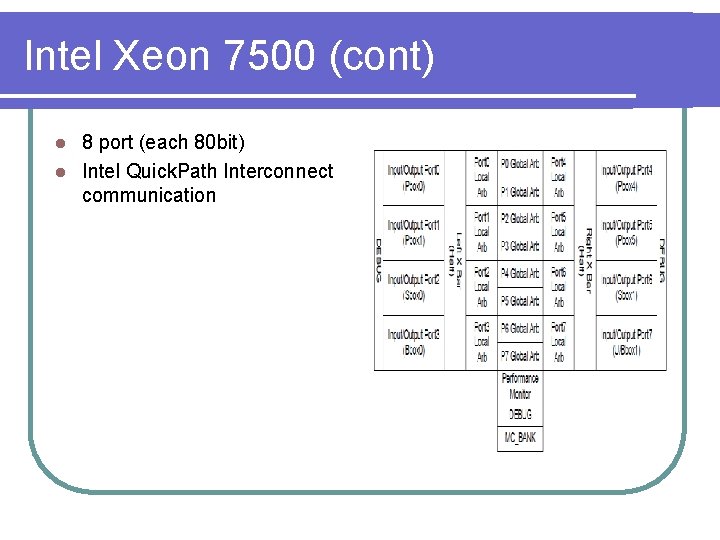

Ultra. SPARC T 2 [4] pipeline crossbar l High-bandwidth l 8 x 9 x. Bar l l l Cores-Mem Cores-I/O

Ultra. Sparc T 2 (cont) l Divided into two parts l PCX l CPX l PCX/CPX divided into two parts l Arbiter l l Assigns by old age Data slice

Characteristics of the crossbar Compare characteristics of several switches used in modern MPSo. C design l Are the switches buffered or bufferless? Is buffering done at the input, output, or at each crosspoint? What is the size of the buffers? Why that much? l How is the crosspoint implemented? Are the crossbars pipelined? What is the size of the crossbar switch? What is the bandwidth? l

![AMD Opteron [1] l Buffers at Input l Size are allocated to optimize throughput AMD Opteron [1] l Buffers at Input l Size are allocated to optimize throughput](http://slidetodoc.com/presentation_image/30bd76798f1c2164890928e55c5046a0/image-9.jpg)

AMD Opteron [1] l Buffers at Input l Size are allocated to optimize throughput

System Request Queue (SRQ) l What is the System request queue in AMD 64 Opteron, Athlon X 2?

![System Request Queue [1] Prioritizes the access from both cores to use the crossbar. System Request Queue [1] Prioritizes the access from both cores to use the crossbar.](http://slidetodoc.com/presentation_image/30bd76798f1c2164890928e55c5046a0/image-11.jpg)

System Request Queue [1] Prioritizes the access from both cores to use the crossbar. l Prevents contention to memory/resources l

Knockout switch l What is knockout switch?

![Knockout switch [3] Problem: l Fully connected switch (ie every input connects to every Knockout switch [3] Problem: l Fully connected switch (ie every input connects to every](http://slidetodoc.com/presentation_image/30bd76798f1c2164890928e55c5046a0/image-13.jpg)

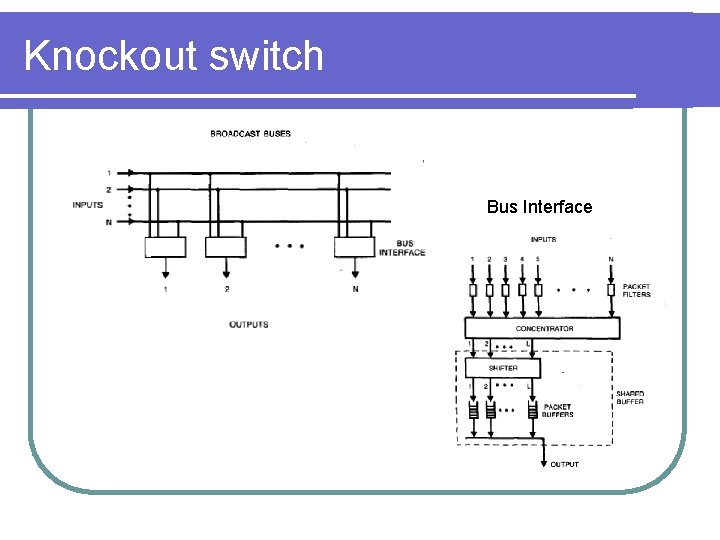

Knockout switch [3] Problem: l Fully connected switch (ie every input connects to every output) l Congestion at output – different input might want to talk to same output. l Solution: l Concentrator at output l Buffer l

Knockout switch Bus Interface

![References [1] Pat Conway, Bill Hughes, "The AMD Opteron Northbridge Architecture, " IEEE Micro, References [1] Pat Conway, Bill Hughes, "The AMD Opteron Northbridge Architecture, " IEEE Micro,](http://slidetodoc.com/presentation_image/30bd76798f1c2164890928e55c5046a0/image-15.jpg)

References [1] Pat Conway, Bill Hughes, "The AMD Opteron Northbridge Architecture, " IEEE Micro, vol. 27, no. 2, pp. 10 -21, Mar. /Apr. 2007, doi: 10. 1109/MM. 2007. 43 [2] Intel Xeon Processor 7500 series Volume 2, Datasheet, March 2010 [3] Y. Yeh, M. Hluchyj, and A. Acampora, “The Knockout Switch: A Simple, Modular Architecture for High-Performance Packet Switching, ” IEEE J. Selected Areas in Comm. , vol. 5, no. 8, pp. 1274 1287, Oct. 1987. [4] U. G. Nawathe, et al. . “An 8 -Core 64 Thread 64 b Power-Efficient SPARC So. C, ” in IEEE International Solid-State Circuits Conference (ISSCC), Dig. Tech Papers, Feb. 2007, pp. 108 -110.

- Slides: 15