Critical Power Slope Understanding the Runtime Effects of

- Slides: 21

Critical Power Slope Understanding the Runtime Effects of Frequency Scaling Akihiko Miyoshi, Charles Lefurgy, Eric Van Hensbergen Ram Rajamony Rajkumar

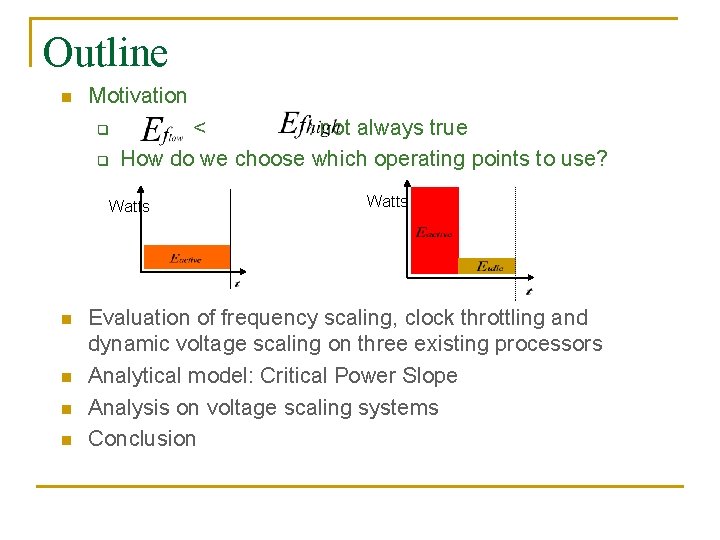

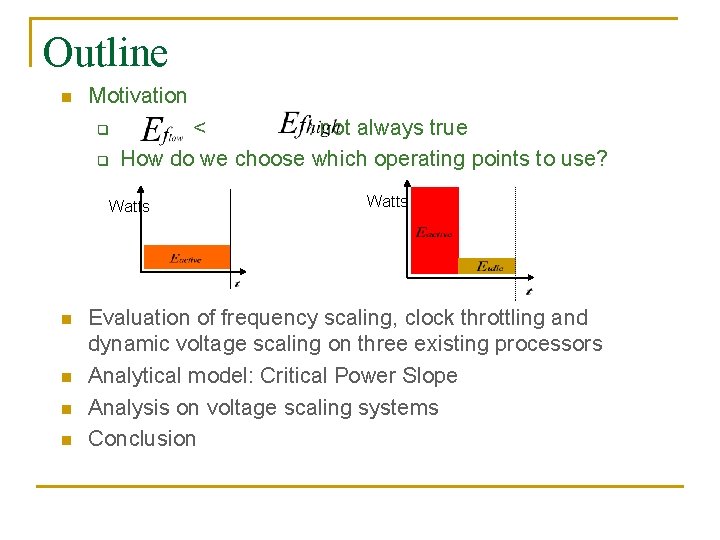

Motivation n Power management algorithms implicitly assume that lower performance points are more energy efficient that higher points n This paper shows that this assumption is not always valid n Also helps decide which operating points of a processor should be considered by an power management algorithm

Outline n Motivation q q < : not always true How do we choose which operating points to use? Watts n n Watts Evaluation of frequency scaling, clock throttling and dynamic voltage scaling on three existing processors Analytical model: Critical Power Slope Analysis on voltage scaling systems Conclusion

Techniques of Power Management n n n Frequency scaling q Processor clock is reduced q Processor consumes less energy at the expense of reduced performance Clock throttling q Clock runs at original frequency q Clock signal is gated/disabled for some cycles at regular intervals Dynamic voltage scaling q Reduces power consumed by lowering the operating voltage q Advantageous because E ∝ V 2

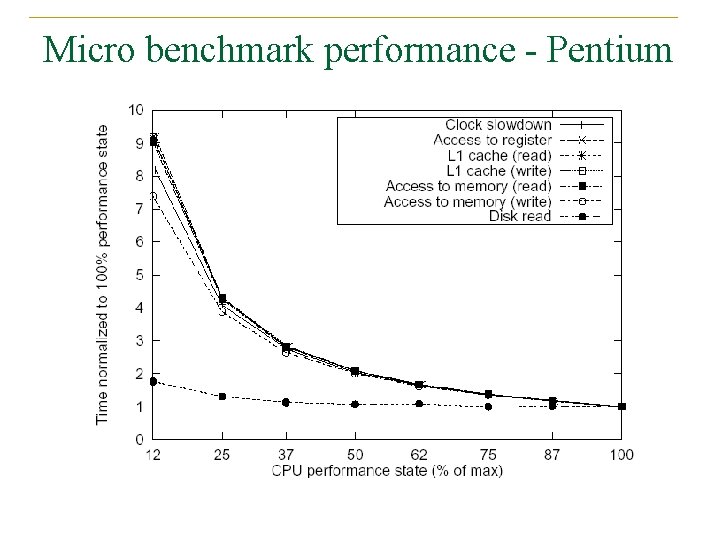

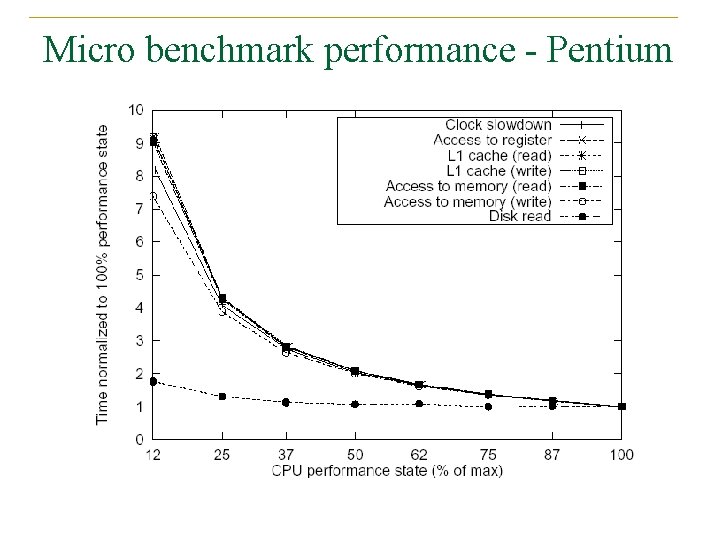

Linux on Pentium n Dell Inspiron 8000 laptop with 850 MHz PIII processor with 512 Mb of RAM running Linux 2. 4. 6 n Processor runs at 8 different performance states q 100% 87. 5% 75% 62. 5% 50% 37. 5% 25% 12. 5% n Effect is evaluated by throttling the clock n The following micro benchmarks were considered q q q Access to register L 1 cache (read) L 1 cache (write) Access to memory (read) Access to memory (write) Disk Read

Micro benchmark performance - Pentium

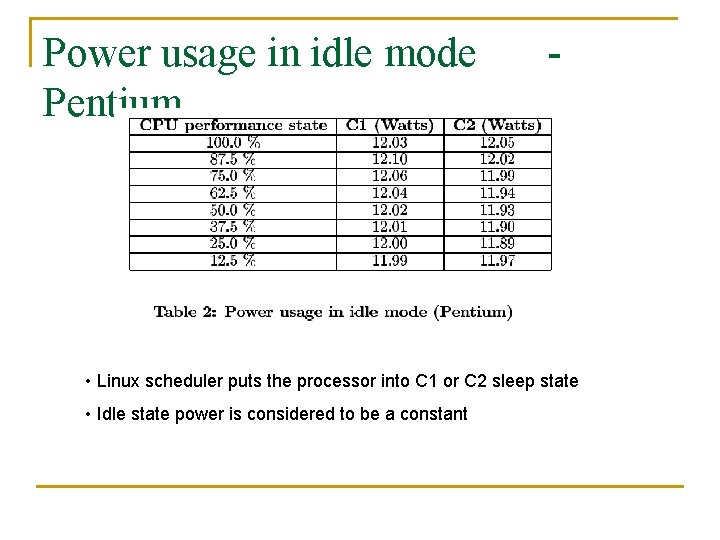

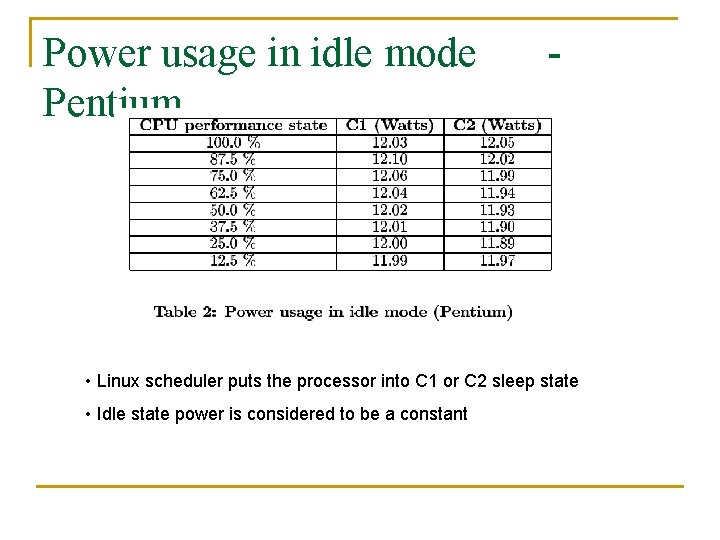

Power usage in idle mode Pentium - • Linux scheduler puts the processor into C 1 or C 2 sleep state • Idle state power is considered to be a constant

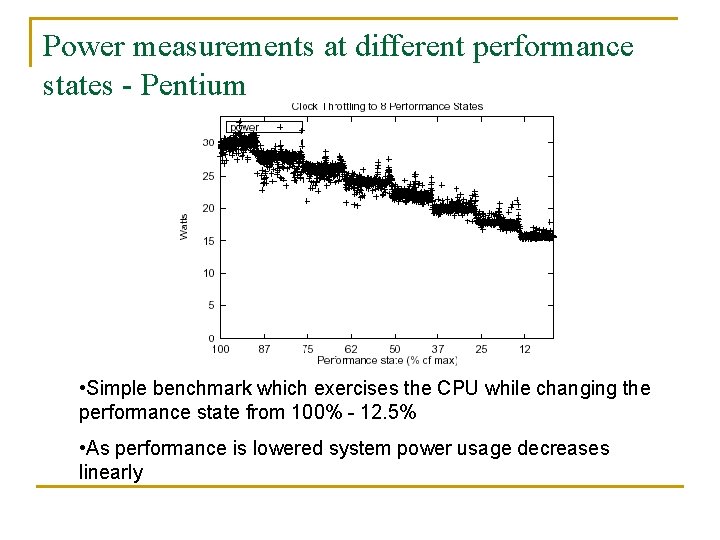

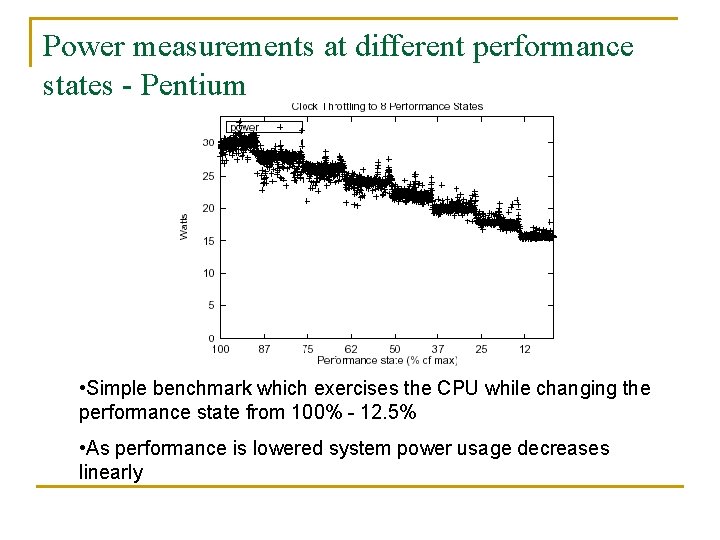

Power measurements at different performance states - Pentium • Simple benchmark which exercises the CPU while changing the performance state from 100% - 12. 5% • As performance is lowered system power usage decreases linearly

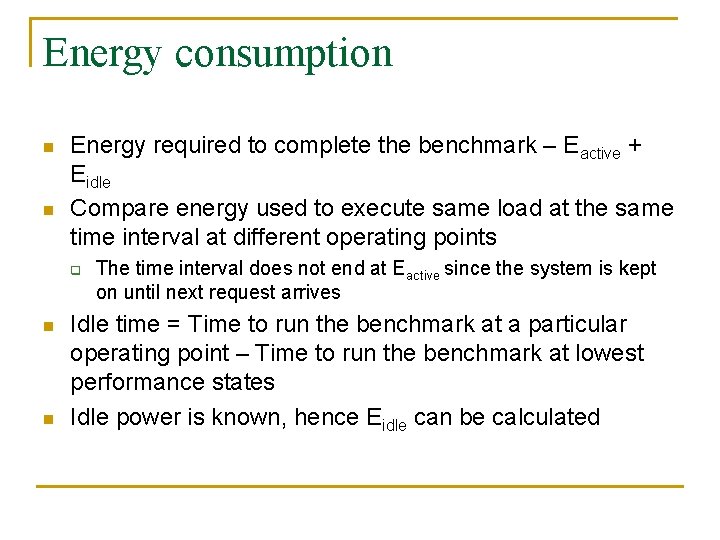

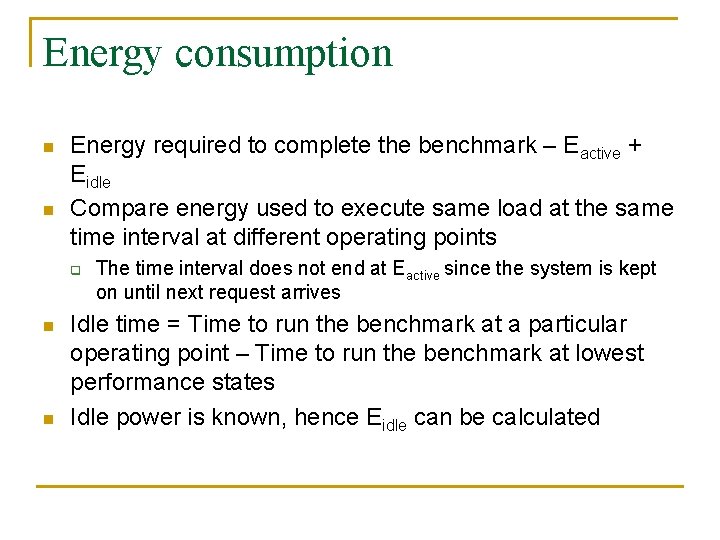

Energy consumption n n Energy required to complete the benchmark – Eactive + Eidle Compare energy used to execute same load at the same time interval at different operating points q n n The time interval does not end at Eactive since the system is kept on until next request arrives Idle time = Time to run the benchmark at a particular operating point – Time to run the benchmark at lowest performance states Idle power is known, hence Eidle can be calculated

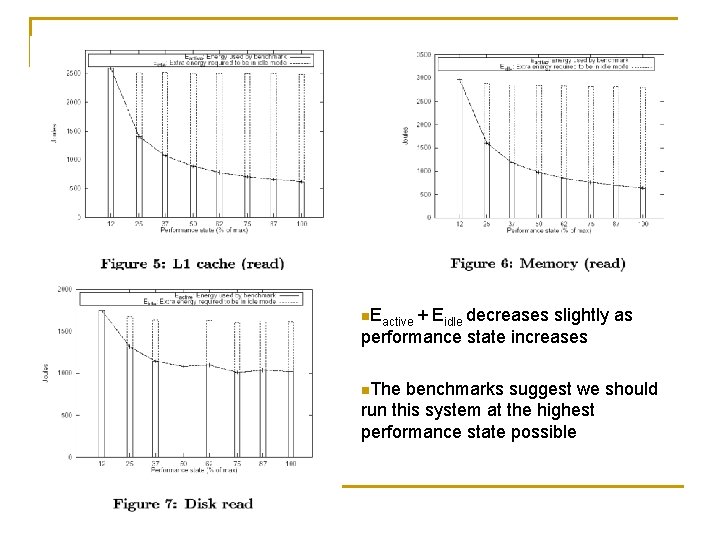

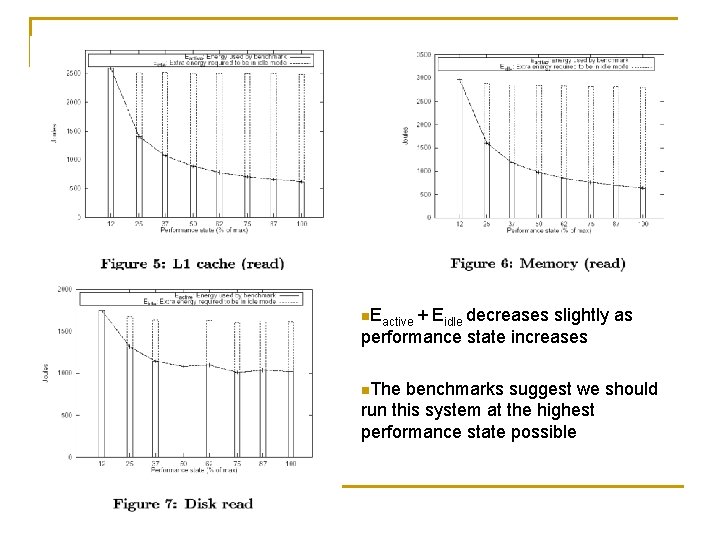

n. Eactive + Eidle decreases slightly as performance state increases n. The benchmarks suggest we should run this system at the highest performance state possible

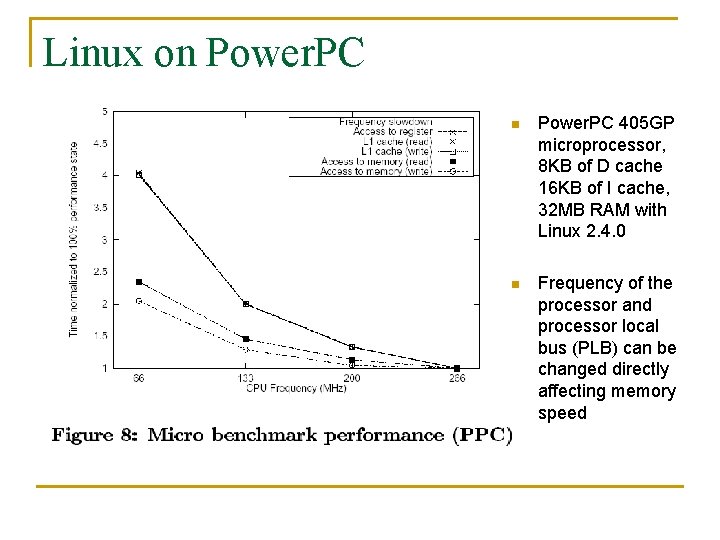

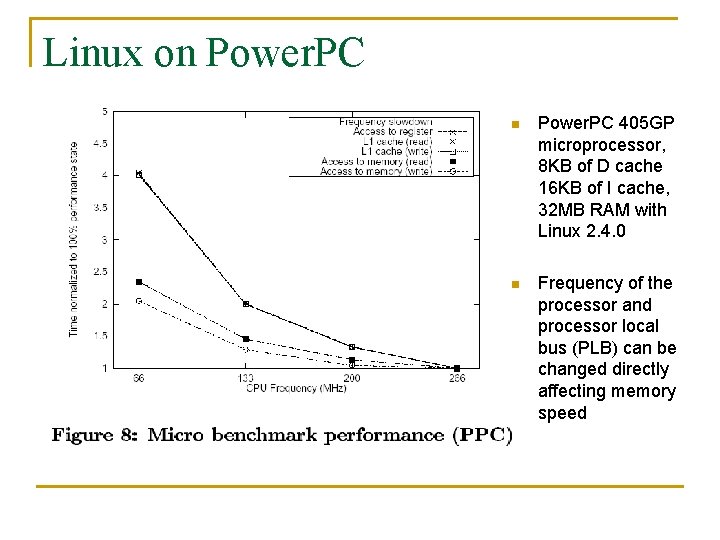

Linux on Power. PC 405 GP microprocessor, 8 KB of D cache 16 KB of I cache, 32 MB RAM with Linux 2. 4. 0 n Frequency of the processor and processor local bus (PLB) can be changed directly affecting memory speed

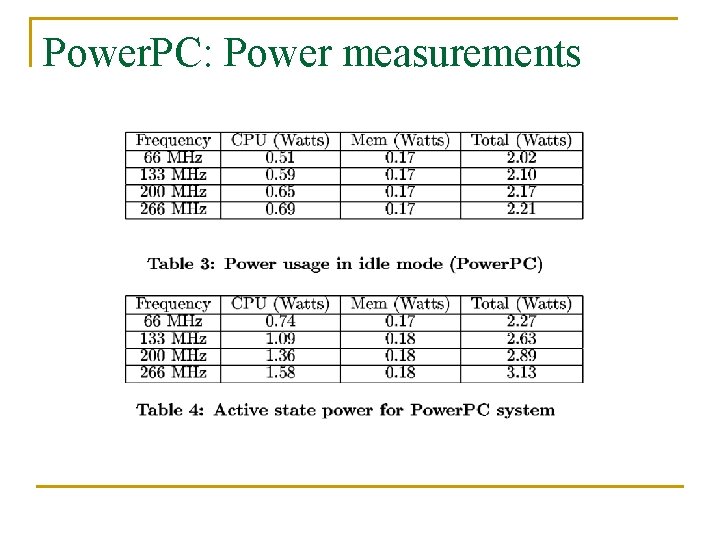

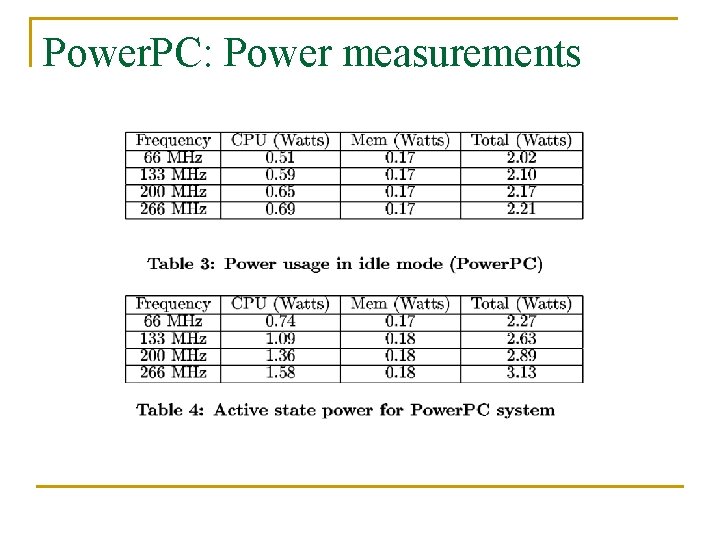

Power. PC: Power measurements

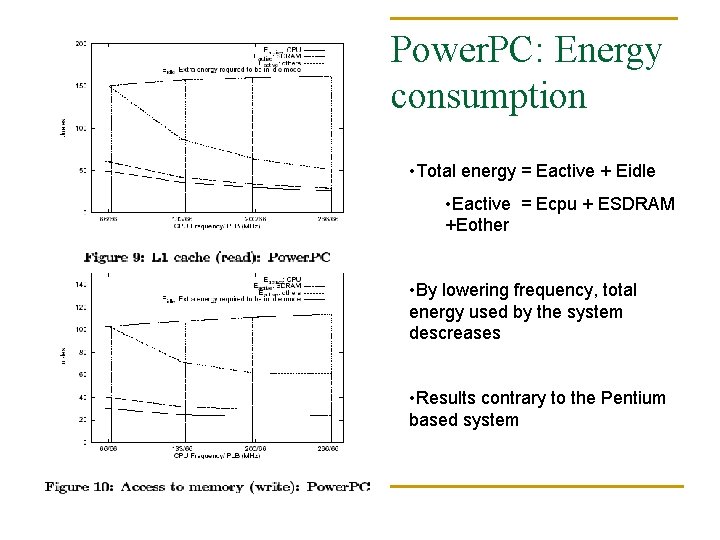

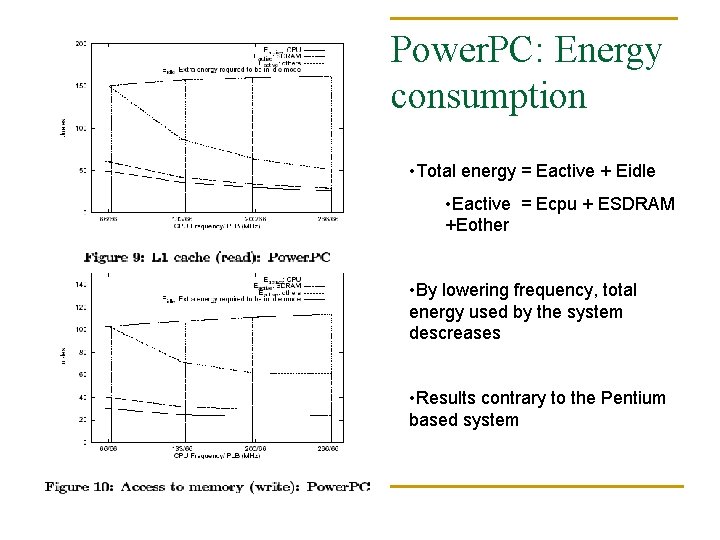

Power. PC: Energy consumption • Total energy = Eactive + Eidle • Eactive = Ecpu + ESDRAM +Eother • By lowering frequency, total energy used by the system descreases • Results contrary to the Pentium based system

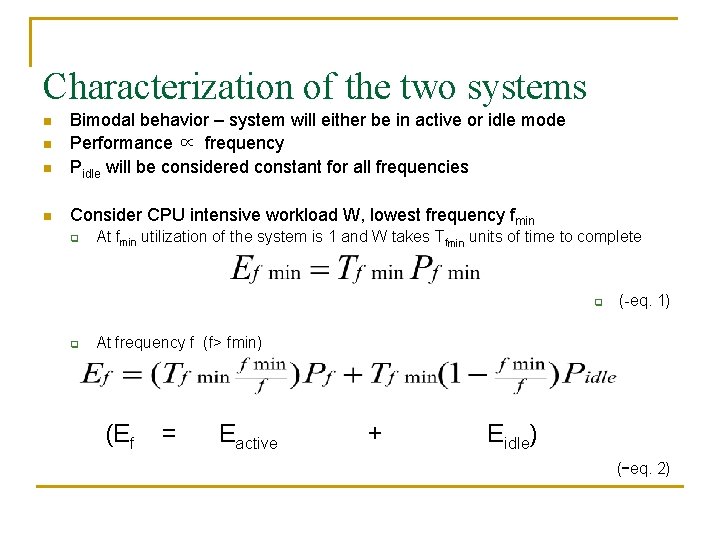

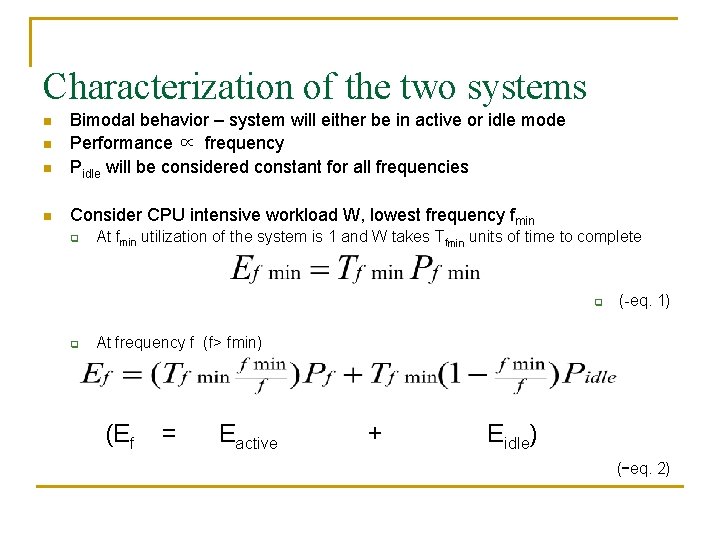

Characterization of the two systems n Bimodal behavior – system will either be in active or idle mode Performance ∝ frequency Pidle will be considered constant for all frequencies n Consider CPU intensive workload W, lowest frequency fmin n n q At fmin utilization of the system is 1 and W takes Tfmin units of time to complete q q (-eq. 1) At frequency f (f> fmin) (Ef = Eactive + Eidle) (-eq. 2)

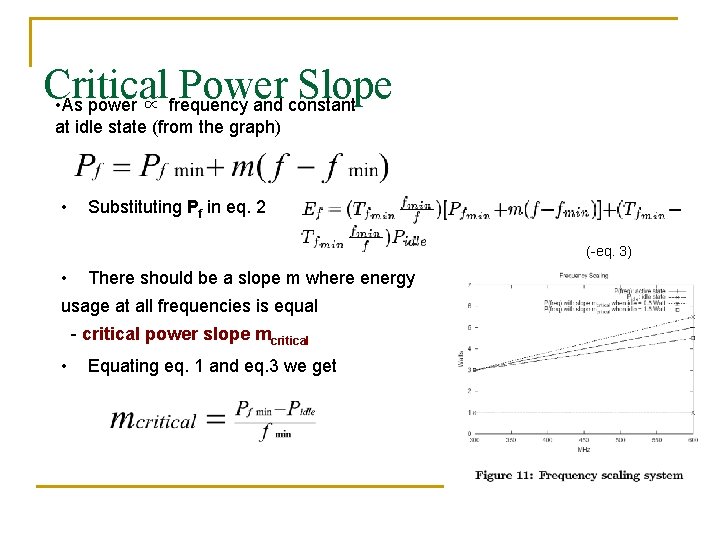

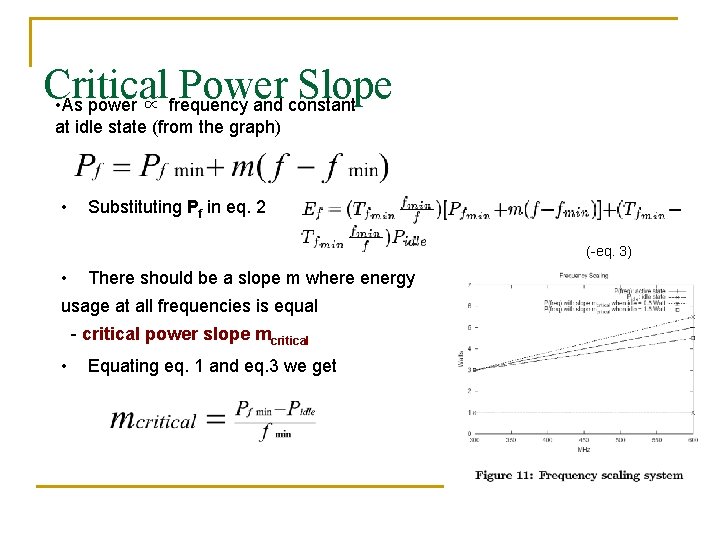

Critical Power Slope • As power ∝ frequency and constant at idle state (from the graph) • Substituting Pf in eq. 2 (-eq. 3) • There should be a slope m where energy usage at all frequencies is equal - critical power slope mcritical • Equating eq. 1 and eq. 3 we get

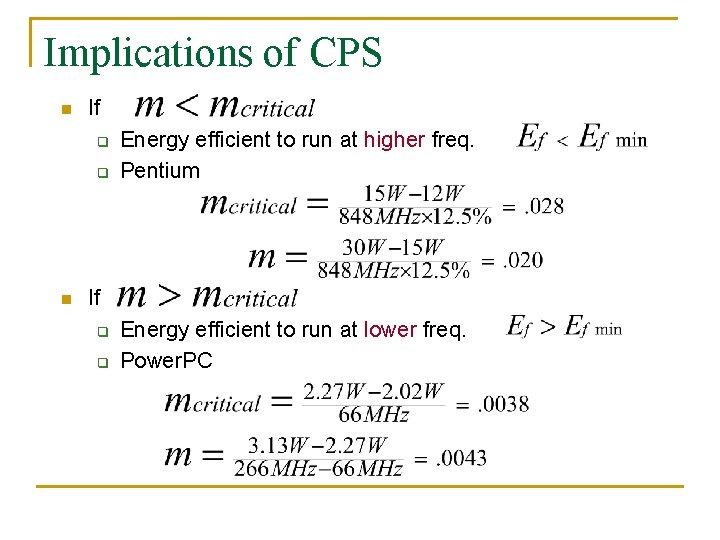

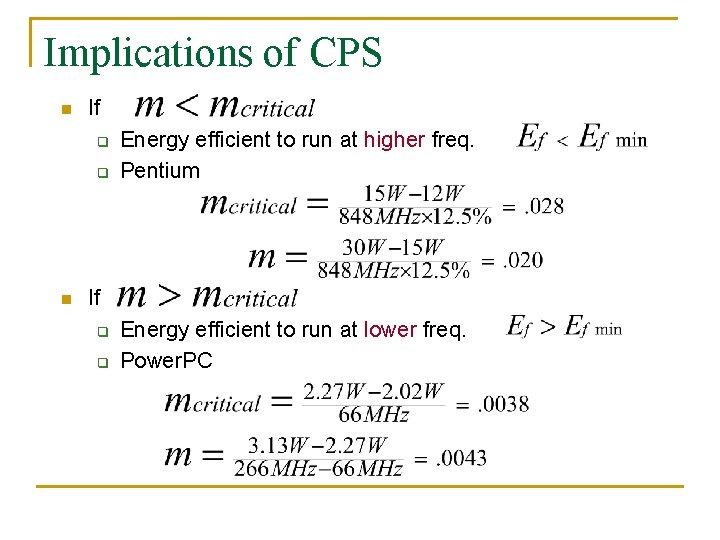

Implications of CPS n If q q n Energy efficient to run at higher freq. Pentium If q q Energy efficient to run at lower freq. Power. PC

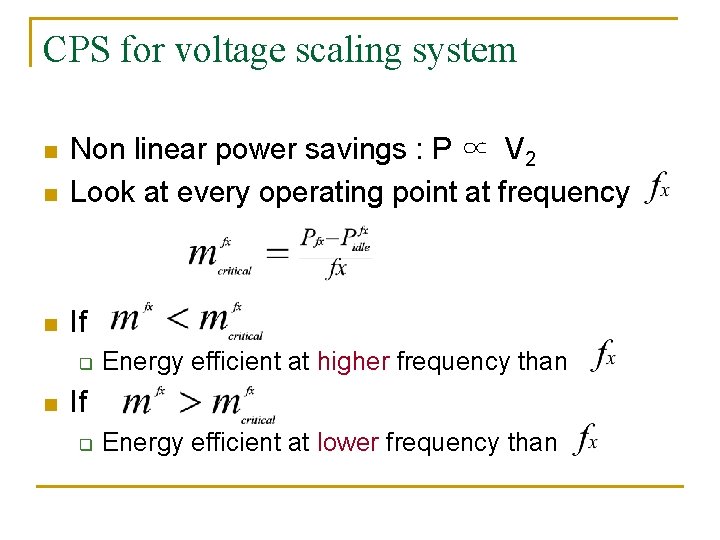

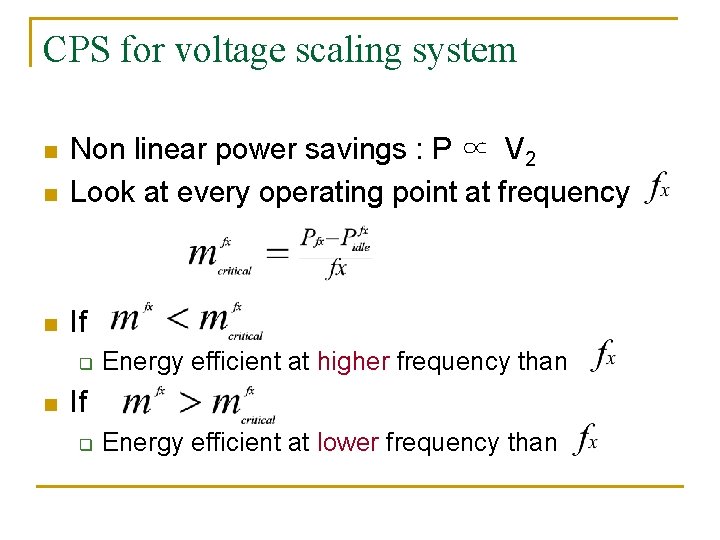

CPS for voltage scaling system n Non linear power savings : P ∝ V 2 Look at every operating point at frequency n If n q n Energy efficient at higher frequency than If q Energy efficient at lower frequency than

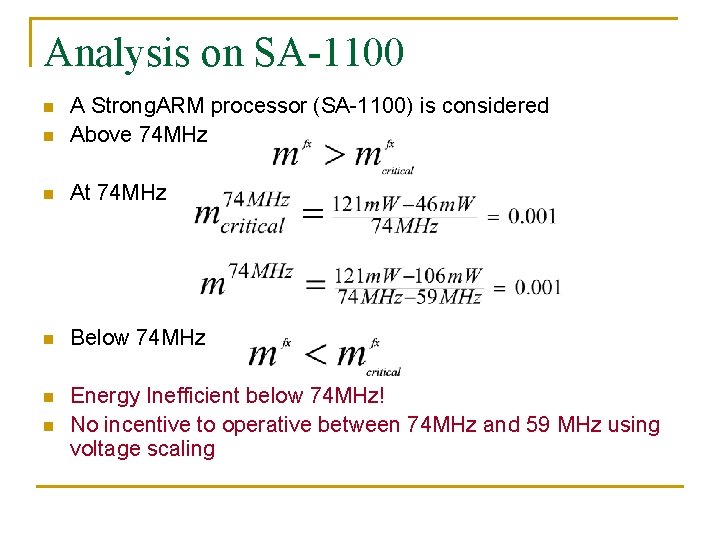

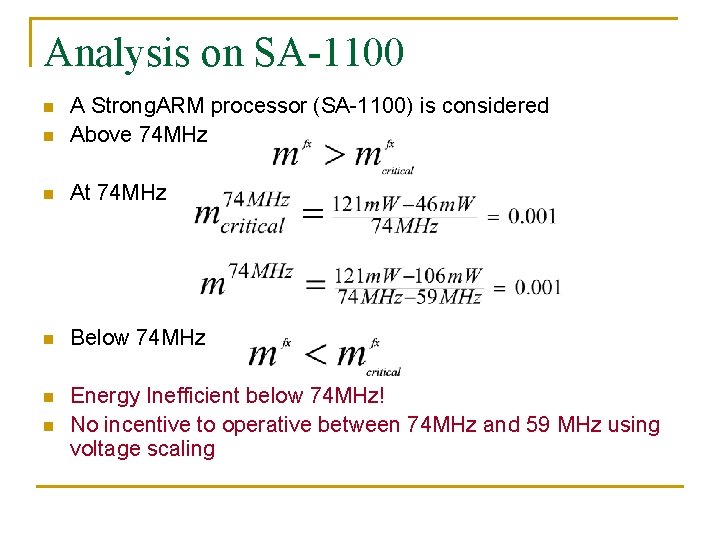

Analysis on SA-1100 n A Strong. ARM processor (SA-1100) is considered Above 74 MHz n At 74 MHz n Below 74 MHz n Energy Inefficient below 74 MHz! No incentive to operative between 74 MHz and 59 MHz using voltage scaling n n

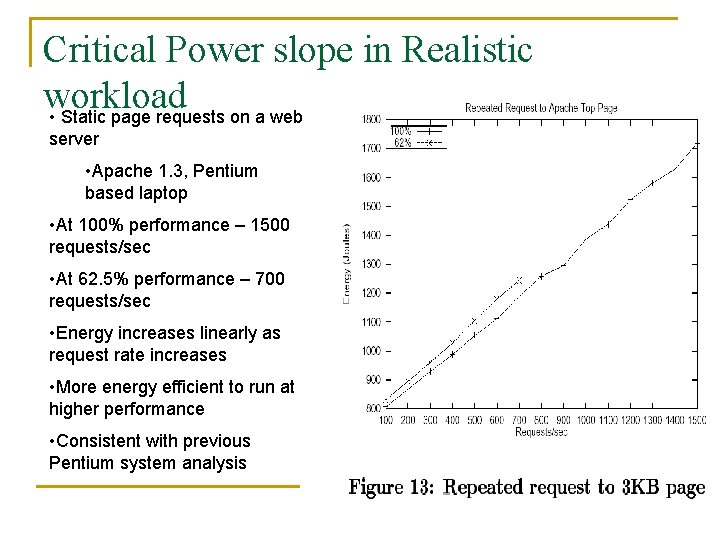

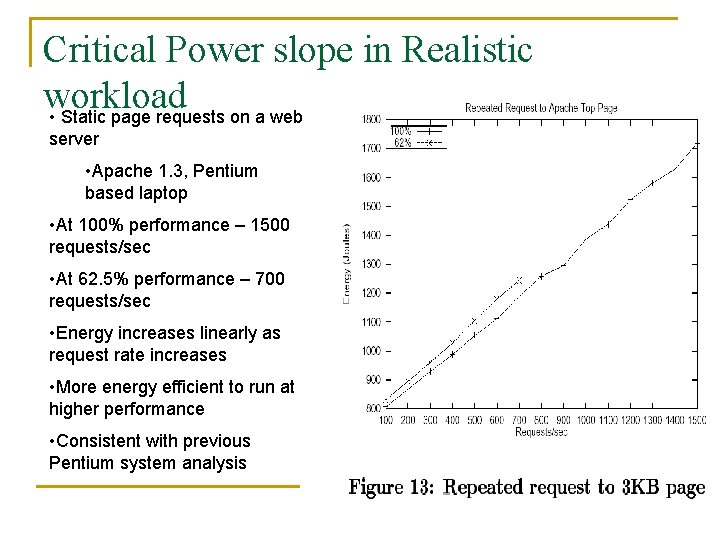

Critical Power slope in Realistic workload • Static page requests on a web server • Apache 1. 3, Pentium based laptop • At 100% performance – 1500 requests/sec • At 62. 5% performance – 700 requests/sec • Energy increases linearly as request rate increases • More energy efficient to run at higher performance • Consistent with previous Pentium system analysis

Conclusion n This paper shows the assumption that lower performance points are more energy efficient that higher performance points is not valid n This paper helps decide which operating point to choose in a power management scheme

Questions?