Creating Test Environments HDL Model stimulus check API

- Slides: 15

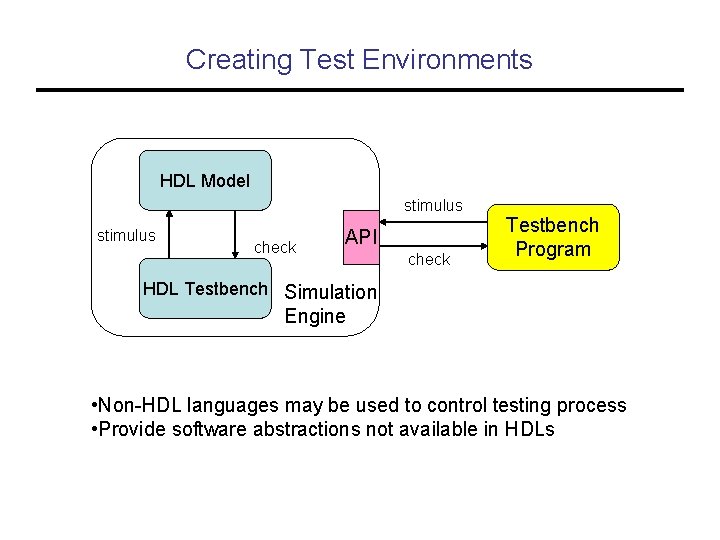

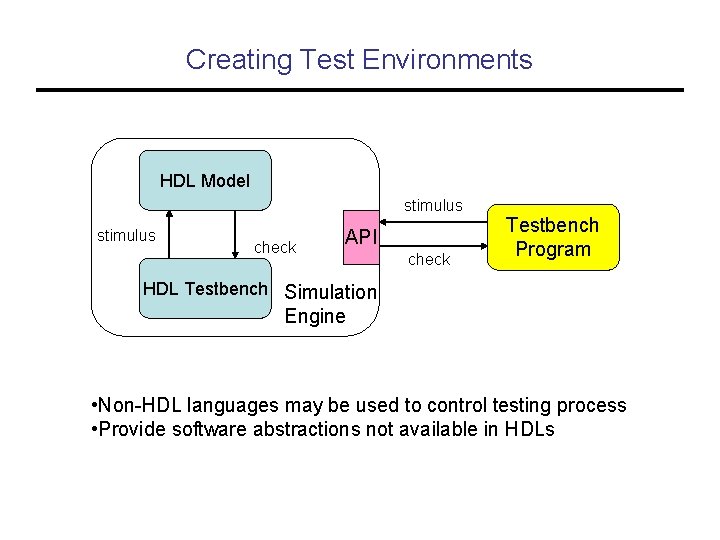

Creating Test Environments HDL Model stimulus check API check Testbench Program HDL Testbench Simulation Engine • Non-HDL languages may be used to control testing process • Provide software abstractions not available in HDLs

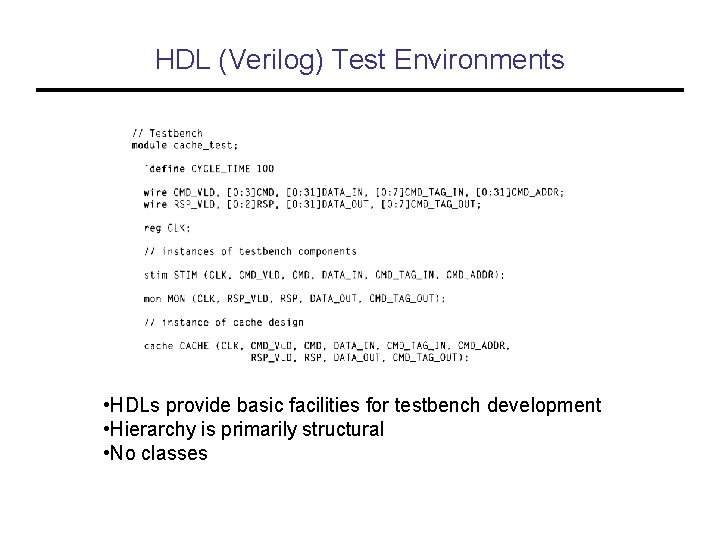

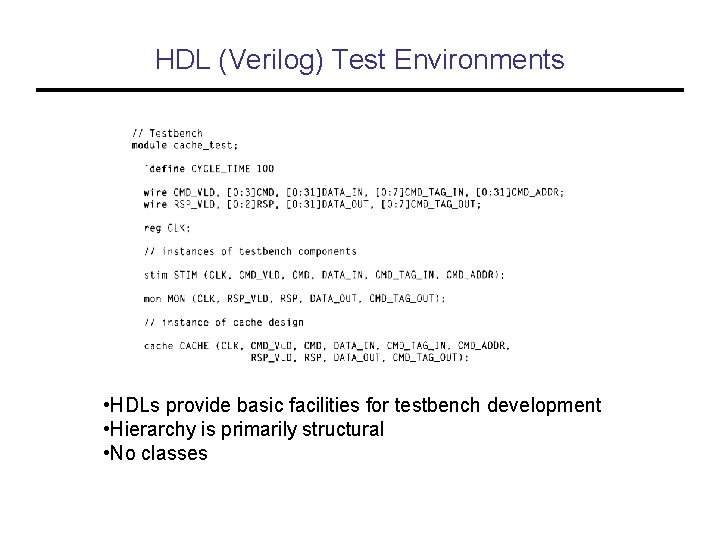

HDL (Verilog) Test Environments • HDLs provide basic facilities for testbench development • Hierarchy is primarily structural • No classes

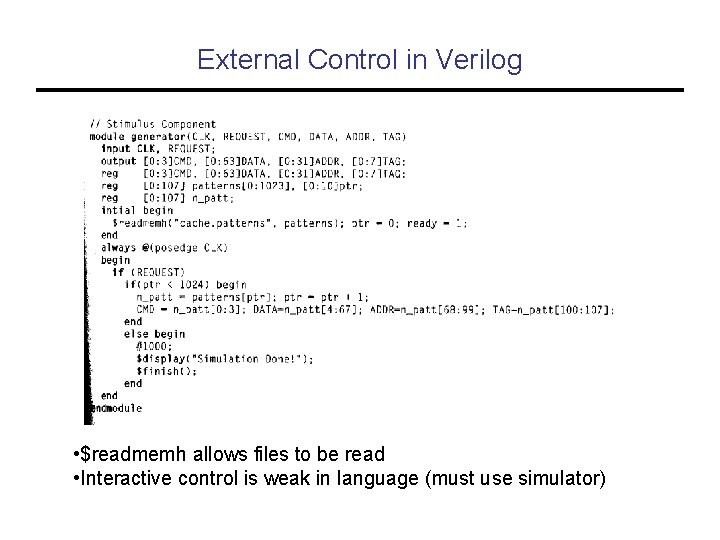

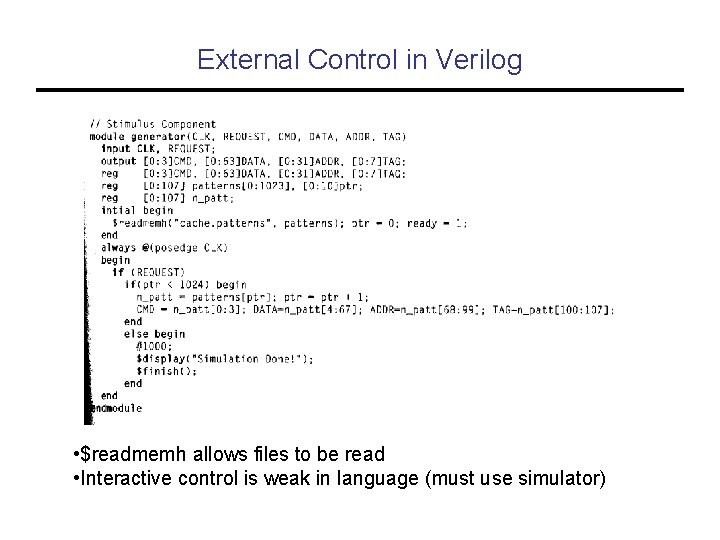

External Control in Verilog • $readmemh allows files to be read • Interactive control is weak in language (must use simulator)

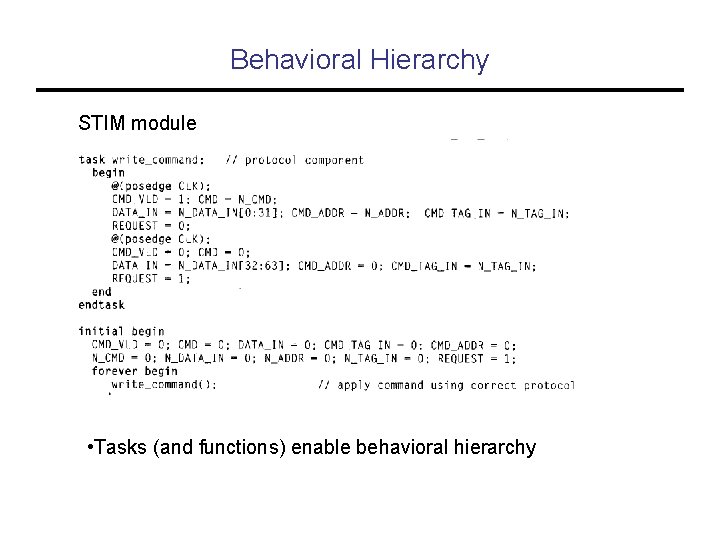

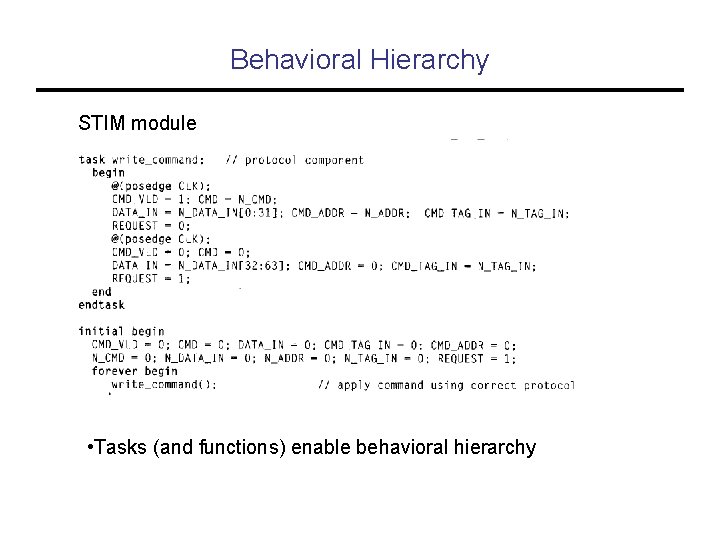

Behavioral Hierarchy STIM module • Tasks (and functions) enable behavioral hierarchy

Other Verilog Testbench Features Debug Trace File Generation • $display/$fdisplay print data to stdio/files • $monitor/$fmonitor print data whenever signals change Randomization - watch out for seed values • $random produces uniform distribution • $dist_normal(), $dist_exponential, $dist_poisson

C/C++ Testbench Benefits • Every engineer can write C/C++ code • Can use classes, pointers, and other software features Disadvantages • Control flow between HDL and C/C++ domain in confusing • Partitioning is an issue • Difficult to make HW tests in SW language (time, structure, etc)

Integrated C/C++ Testbench • HDL Simulator calls C/C++ functions - Program Language Interface (PLI) for Verilog - Foreign Language Interface (FLI) or VHPI for VHDL Ex. The write_command task could be written in C • C/C++ performs sub-functions (i. e. make test data, compare test response) but top control flow is in HDL • C/C++ can be invoked implicitly on events, at time steps • May be hard to follow control flow when invocation is implicit

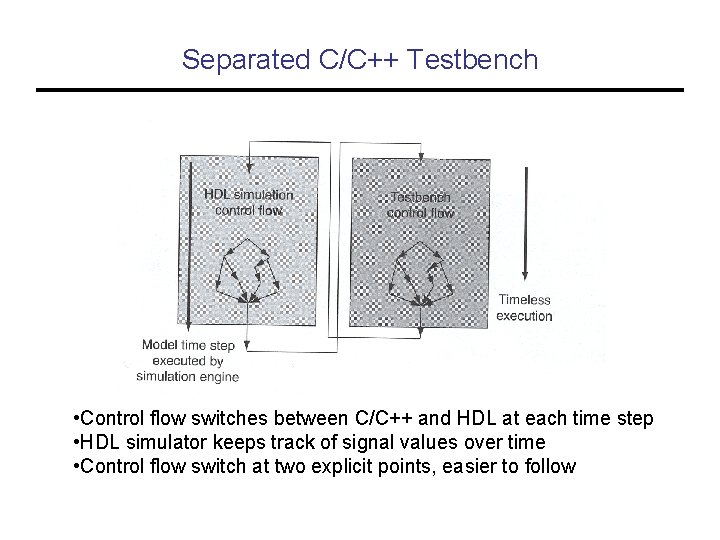

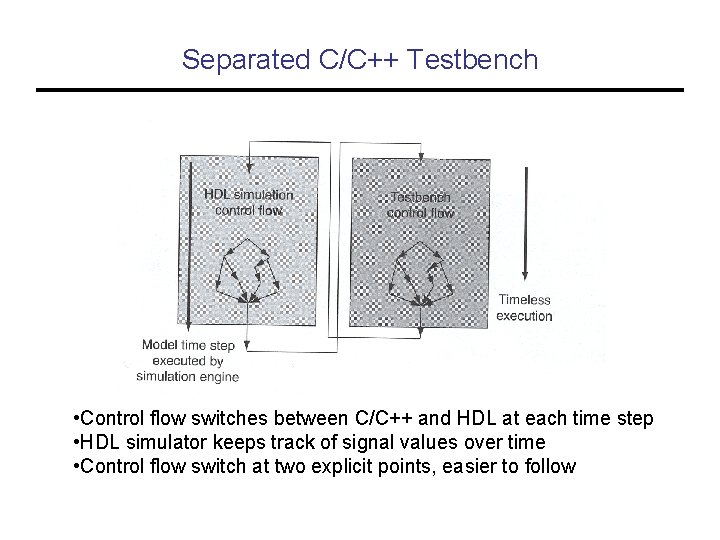

Separated C/C++ Testbench • Control flow switches between C/C++ and HDL at each time step • HDL simulator keeps track of signal values over time • Control flow switch at two explicit points, easier to follow

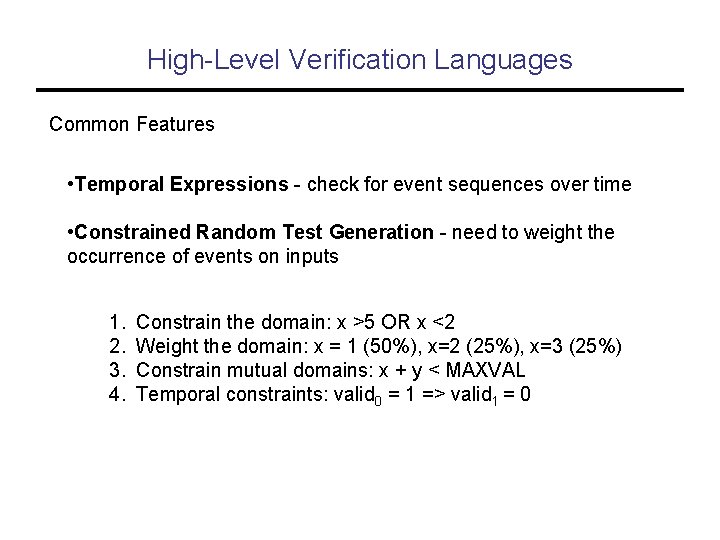

High-Level Verification Languages Common Features • Temporal Expressions - check for event sequences over time • Constrained Random Test Generation - need to weight the occurrence of events on inputs 1. 2. 3. 4. Constrain the domain: x >5 OR x <2 Weight the domain: x = 1 (50%), x=2 (25%), x=3 (25%) Constrain mutual domains: x + y < MAXVAL Temporal constraints: valid 0 = 1 => valid 1 = 0

High-Level Verification Language Features • Coverage Collection - Quantify the amount of the design covered during testing • Automatic Garbage Collection (Memory Management) - No malloc, memory leaks, etc. • Interpretation and Compilation - Interpretation is often useful during interactive debugging

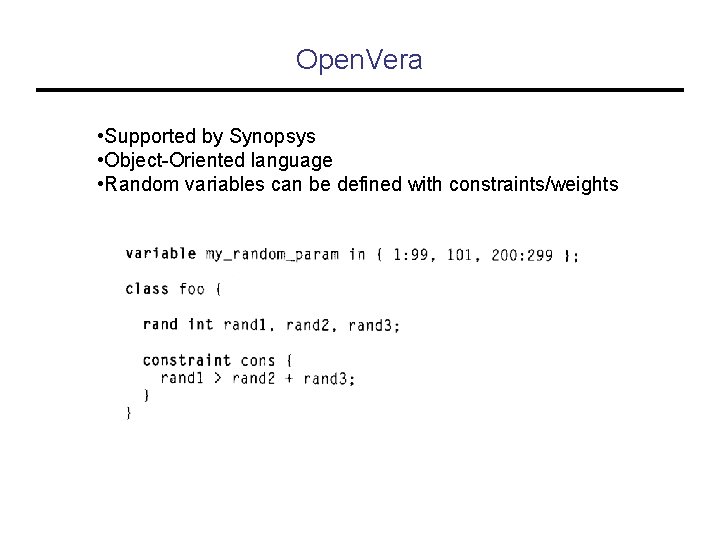

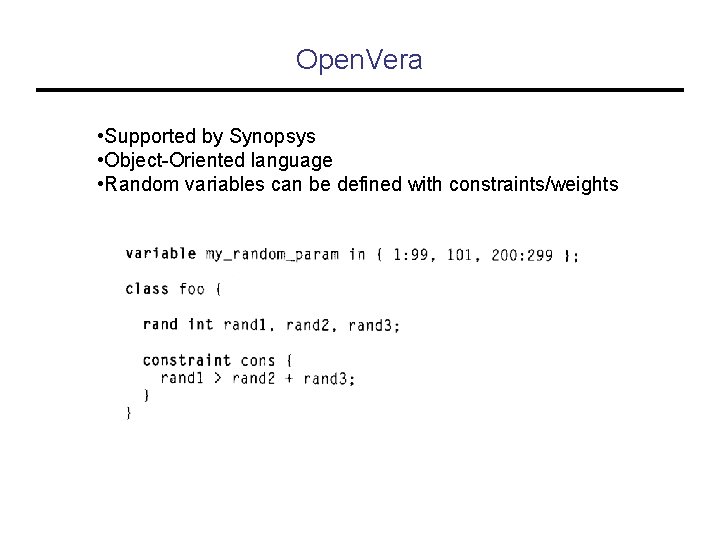

Open. Vera • Supported by Synopsys • Object-Oriented language • Random variables can be defined with constraints/weights

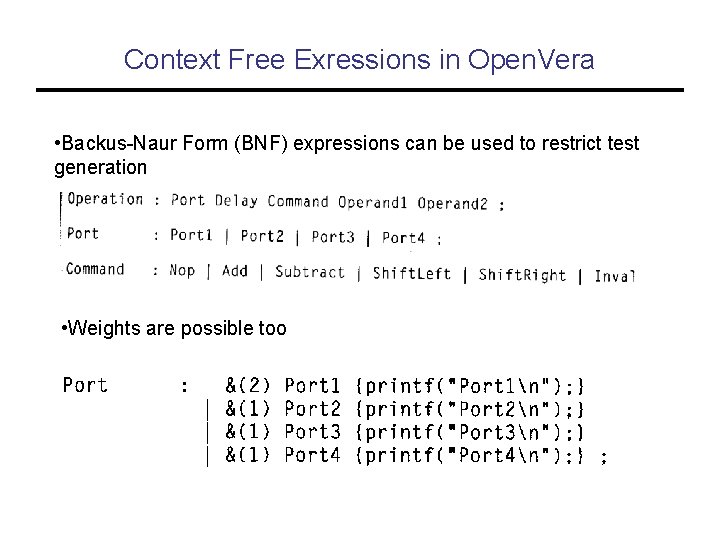

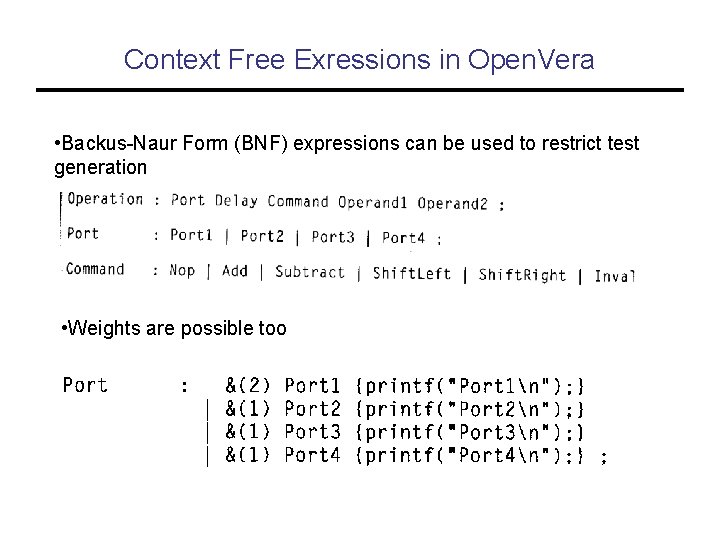

Context Free Exressions in Open. Vera • Backus-Naur Form (BNF) expressions can be used to restrict test generation • Weights are possible too

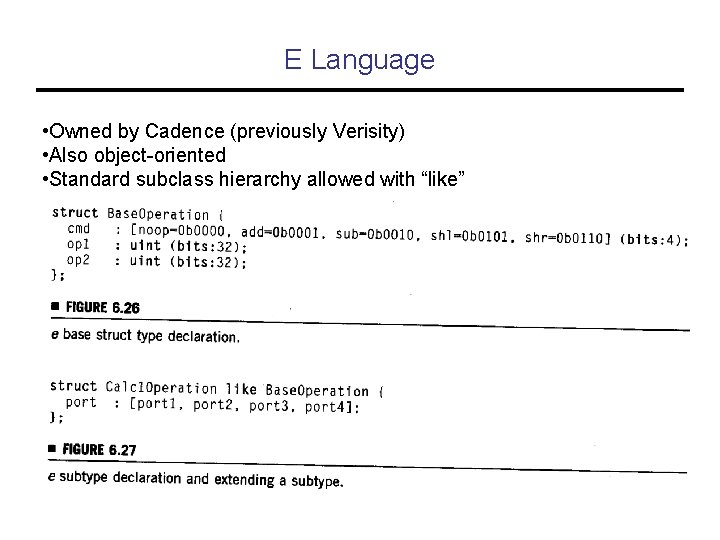

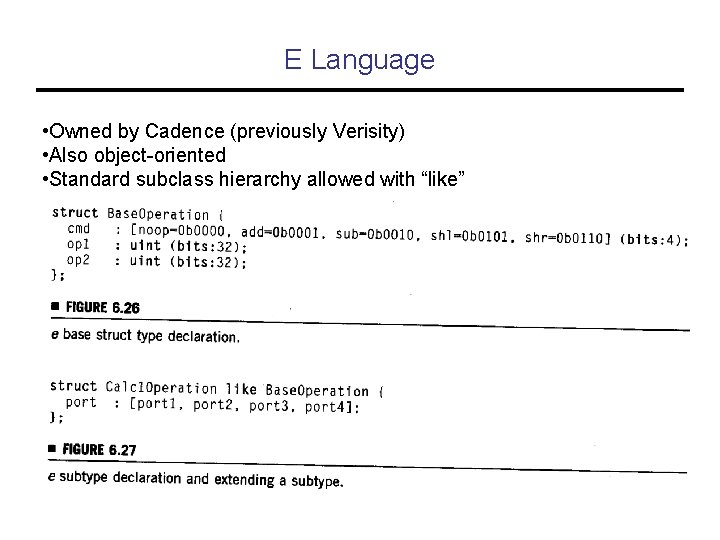

E Language • Owned by Cadence (previously Verisity) • Also object-oriented • Standard subclass hierarchy allowed with “like”

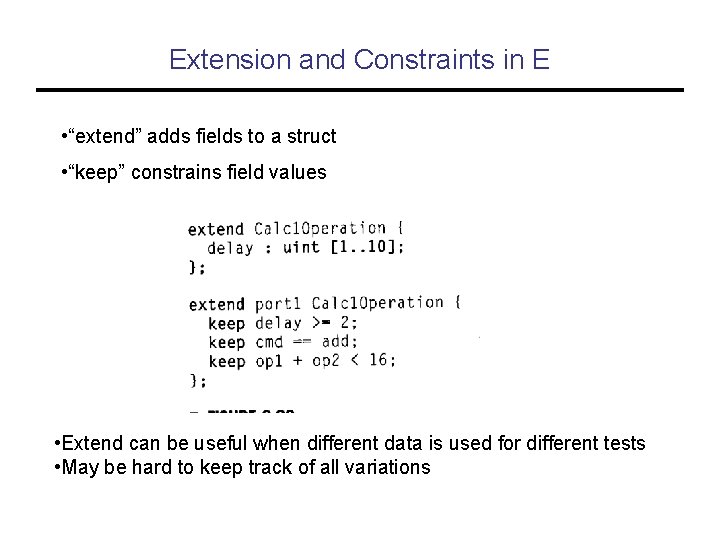

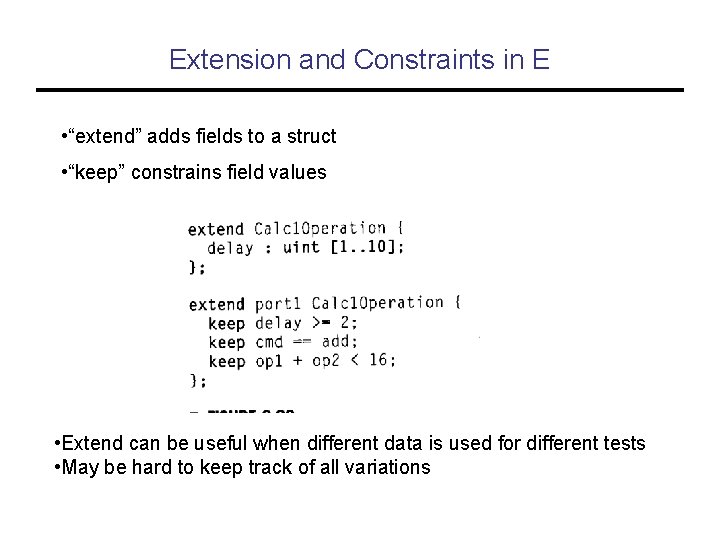

Extension and Constraints in E • “extend” adds fields to a struct • “keep” constrains field values • Extend can be useful when different data is used for different tests • May be hard to keep track of all variations

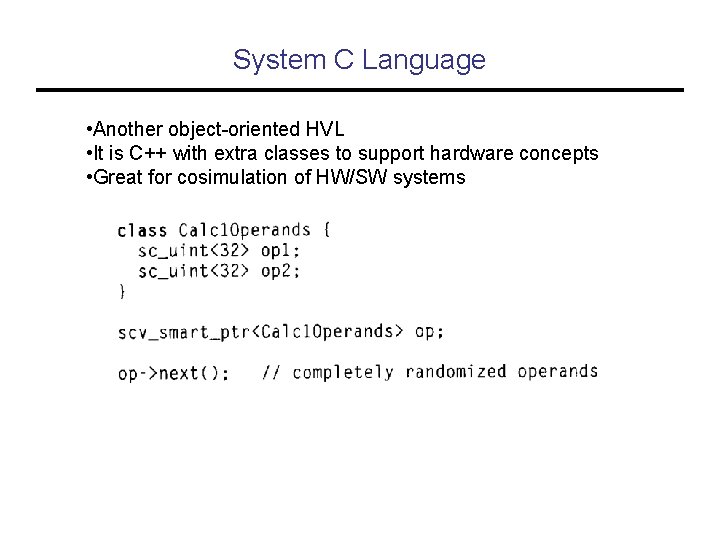

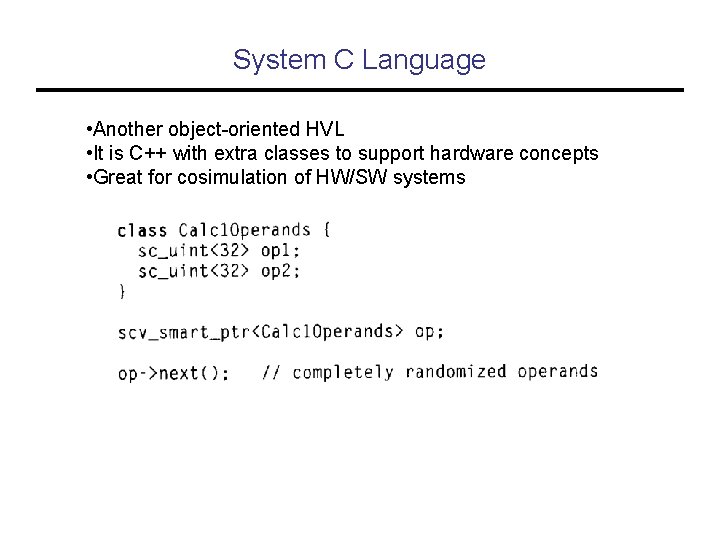

System C Language • Another object-oriented HVL • It is C++ with extra classes to support hardware concepts • Great for cosimulation of HW/SW systems