CPUs Real View 2005 M 2 M 3

![博创科技 嵌入互动 4. 3 CPSR/SPSR (续) M[4: 0] 模式 Accessible Registers 10000 User PC, 博创科技 嵌入互动 4. 3 CPSR/SPSR (续) M[4: 0] 模式 Accessible Registers 10000 User PC,](https://slidetodoc.com/presentation_image/56d3e73d6336f8fe8dcb1106252b9294/image-71.jpg)

- Slides: 94

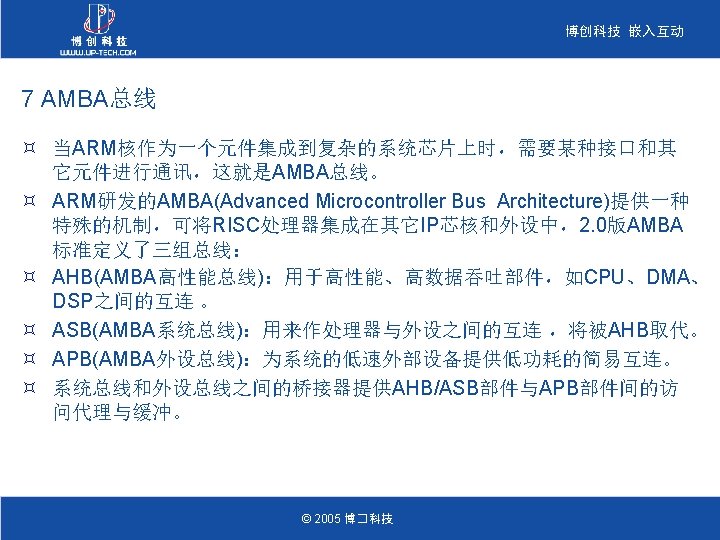

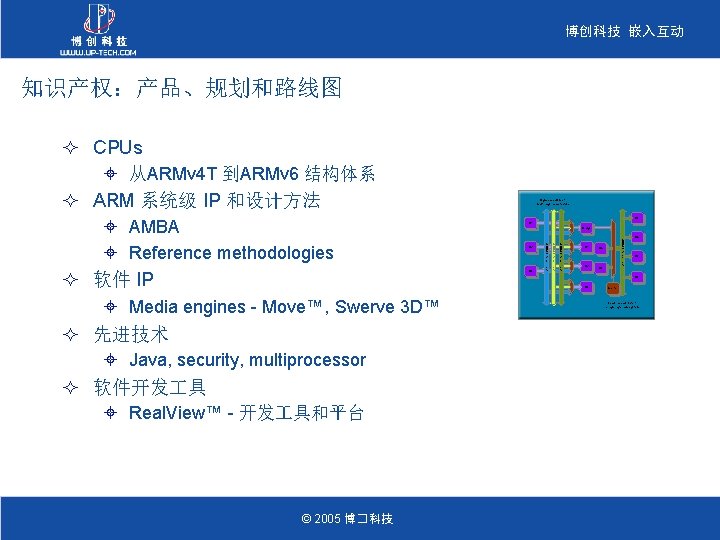

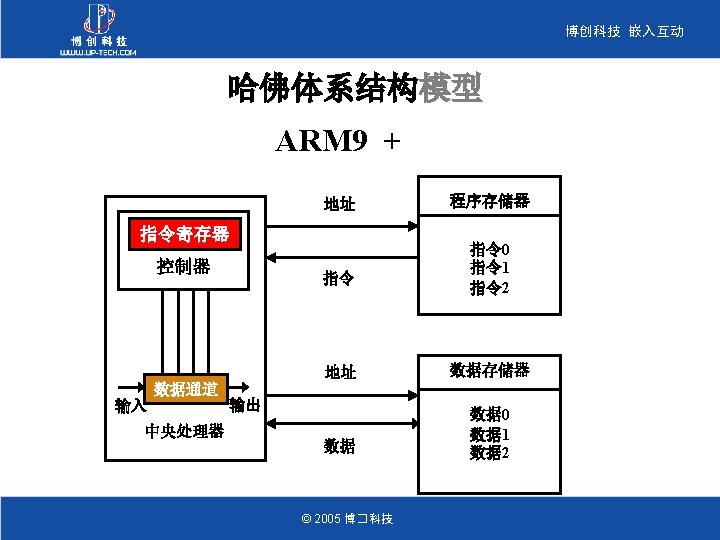

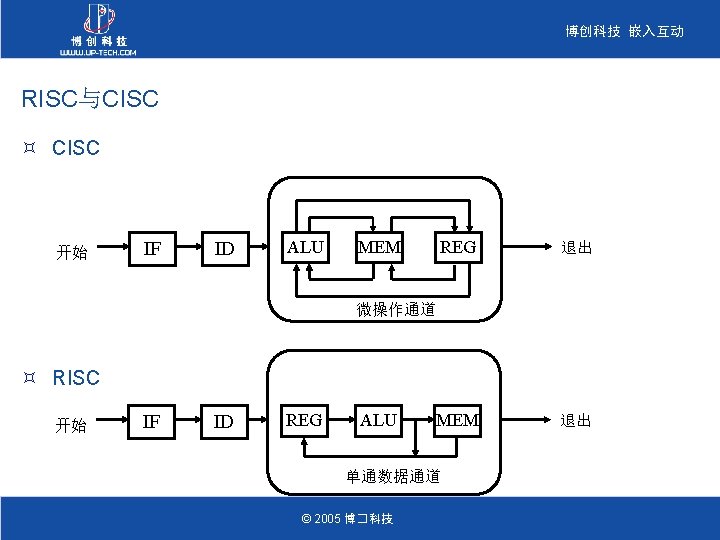

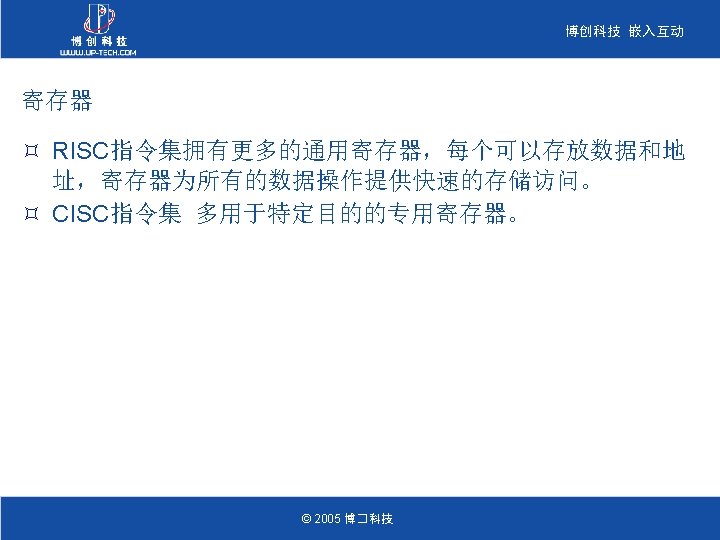

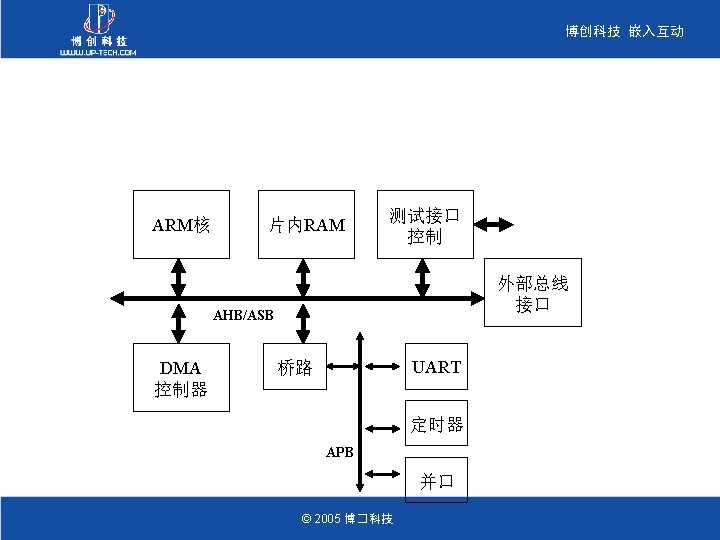

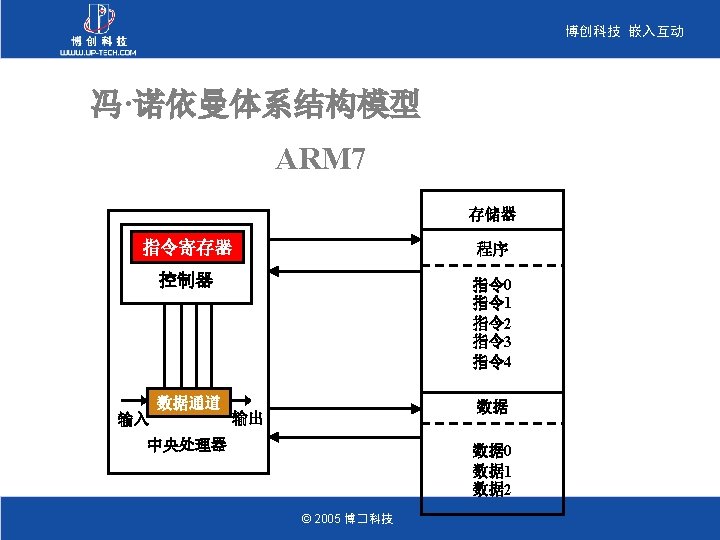

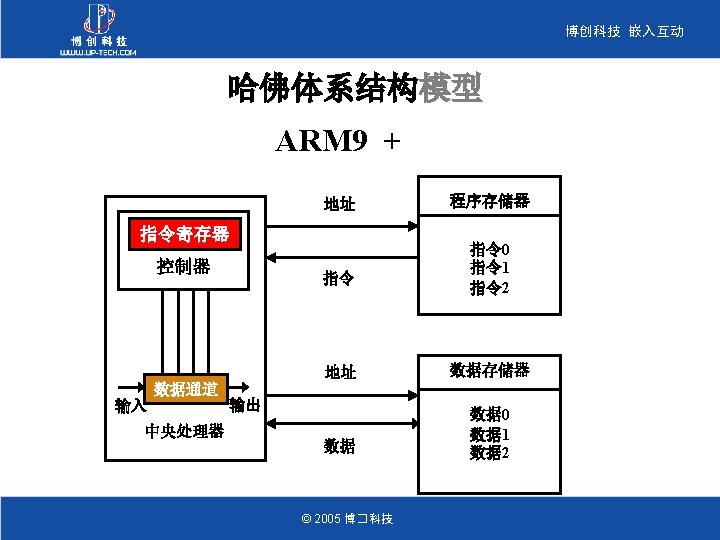

博创科技 嵌入互动 知识产权:产品、规划和路线图 ² CPUs ± Real. View™ - 开发 具和平台 © 2005 博� 科技 M 2 M 3 S 1 S 2 AMBA Interconnect ² 软件开发 具 Bridge AMBA Interconnect ± Java, security, multiprocessor S 3 M 1 AMBA Interconnect ² 先进技术 High-speed 64 -bit multi-layer architecture AMBA Interconnect ± 从ARMv 4 T 到ARMv 6 结构体系 ² ARM 系统级 IP 和设计方法 ± AMBA ± Reference methodologies ² 软件 IP ± Media engines - Move™, Swerve 3 D™ M 4 M 5 S 4 S 5 S 6 S 3 Arbiter Lower speed, 32 -bit, single-layer subsystem

博创科技 嵌入互动 ARM Partnership Model © 2005 博� 科技

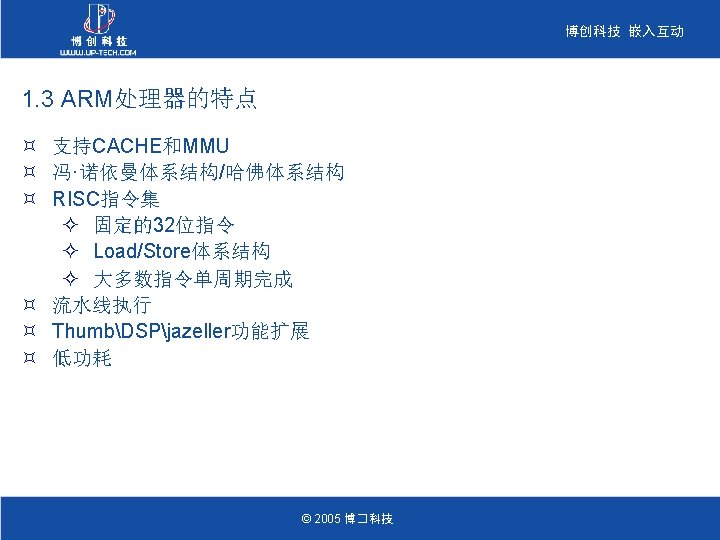

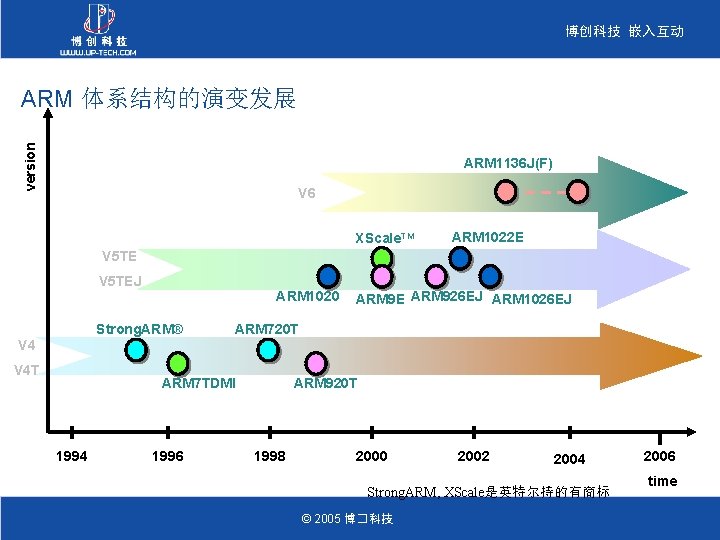

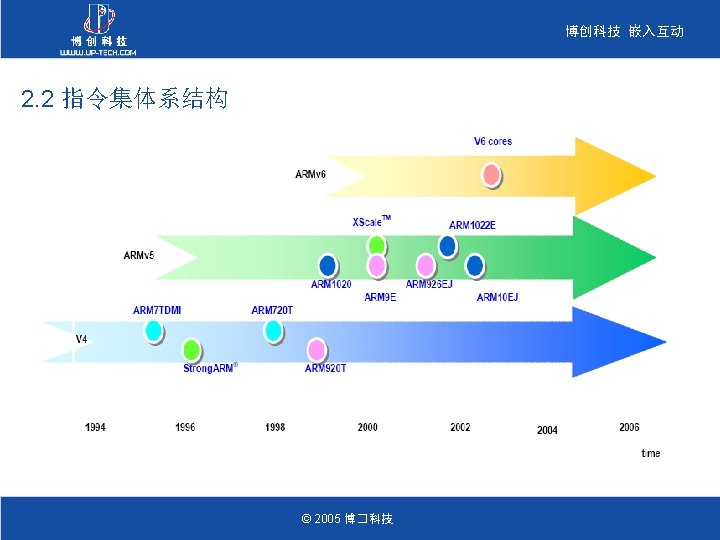

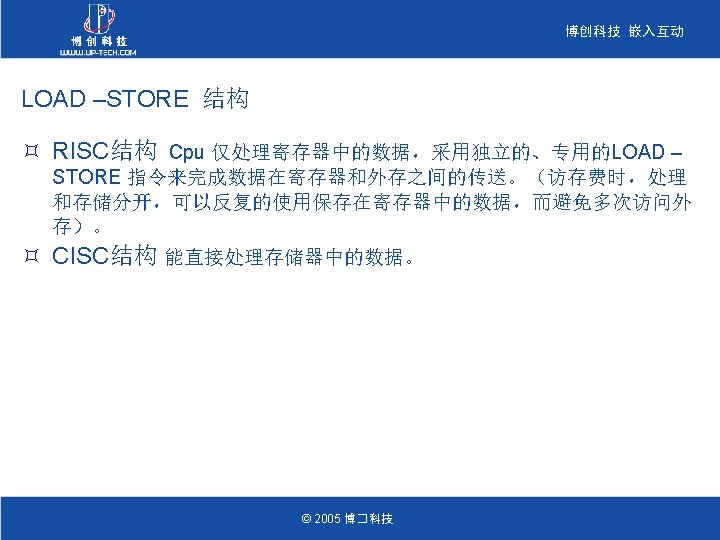

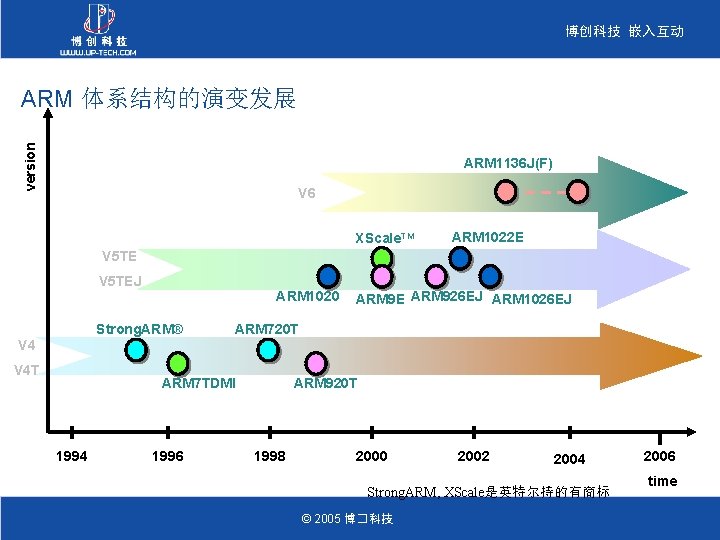

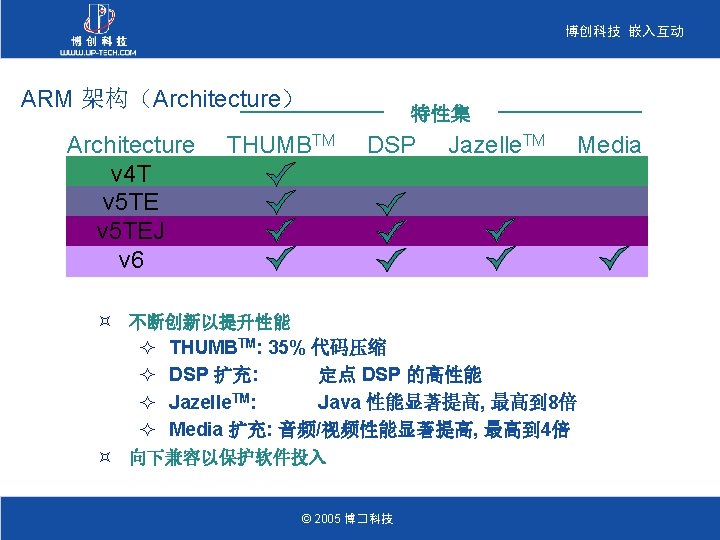

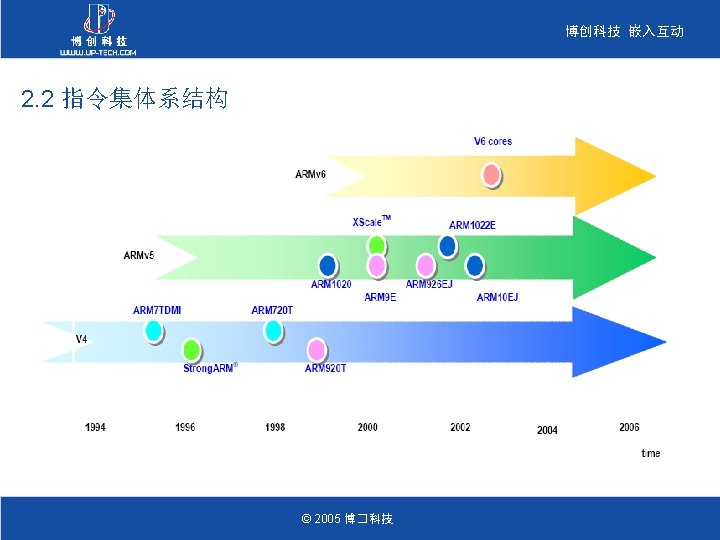

博创科技 嵌入互动 version ARM 体系结构的演变发展 ARM 1136 J(F) V 6 XScale. TM ARM 1022 E V 5 TEJ ARM 1020 Strong. ARM® V 4 T ARM 720 T ARM 7 TDMI 1994 1996 ARM 9 E ARM 926 EJ ARM 1026 EJ ARM 920 T 1998 2000 2002 2004 Strong. ARM, XScale是英特尔持的有商标 © 2005 博� 科技 2006 time

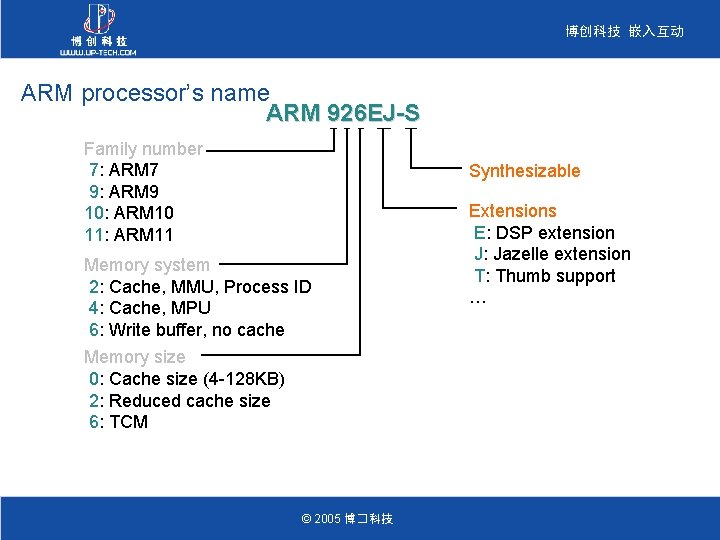

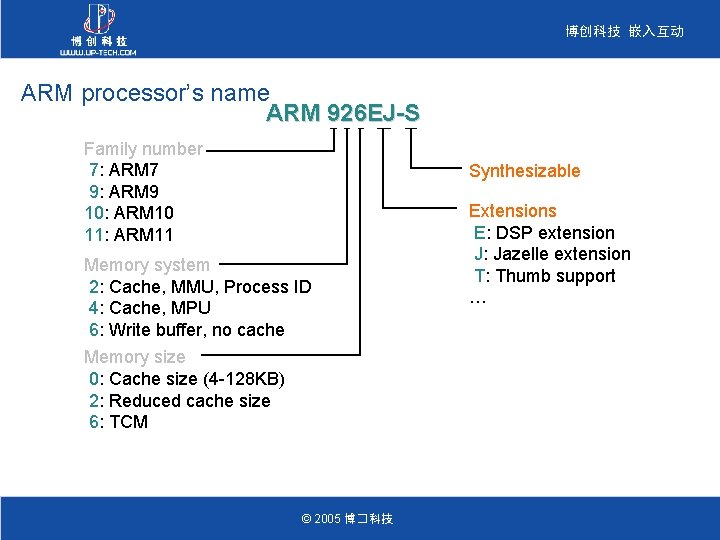

博创科技 嵌入互动 ARM processor’s name ARM 926 EJ-S Family number 7: ARM 7 9: ARM 9 10: ARM 10 11: ARM 11 Synthesizable Memory system 2: Cache, MMU, Process ID 4: Cache, MPU 6: Write buffer, no cache Memory size 0: Cache size (4 -128 KB) 2: Reduced cache size 6: TCM © 2005 博� 科技 Extensions E: DSP extension J: Jazelle extension T: Thumb support …

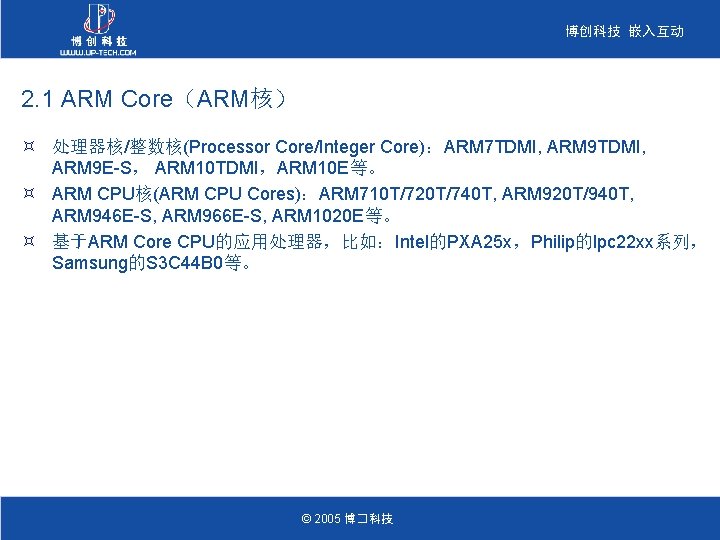

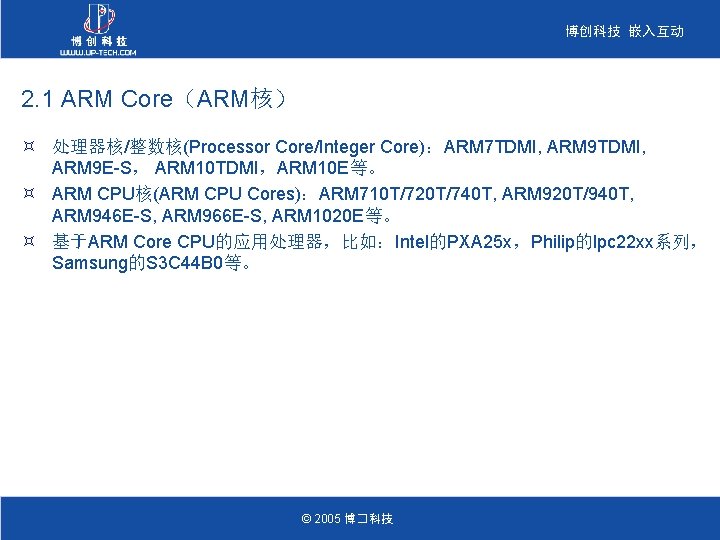

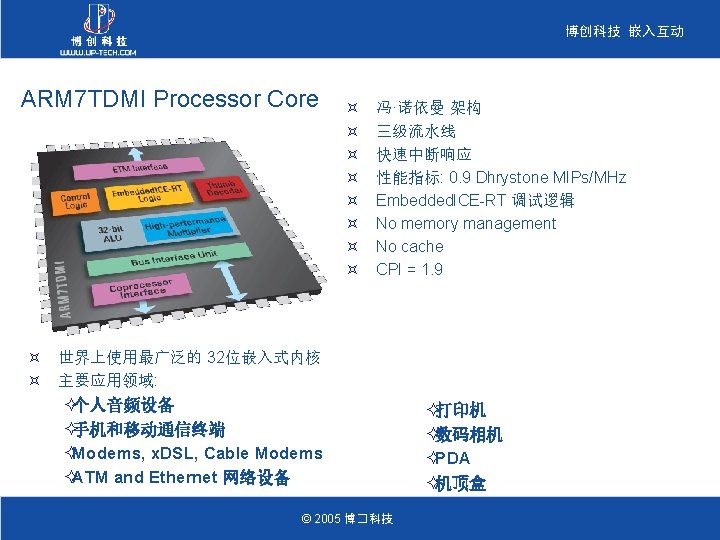

博创科技 嵌入互动 2. 1 ARM Core(ARM核) ³ 处理器核/整数核(Processor Core/Integer Core):ARM 7 TDMI, ARM 9 TDMI, ARM 9 E-S, ARM 10 TDMI,ARM 10 E等。 ³ ARM CPU核(ARM CPU Cores):ARM 710 T/720 T/740 T, ARM 920 T/940 T, ARM 946 E-S, ARM 966 E-S, ARM 1020 E等。 ³ 基于ARM Core CPU的应用处理器,比如:Intel的PXA 25 x,Philip的lpc 22 xx系列, Samsung的S 3 C 44 B 0等。 © 2005 博� 科技

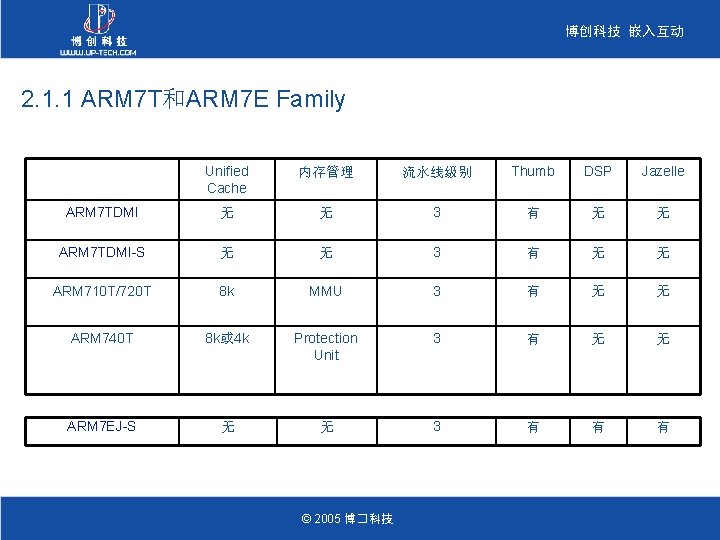

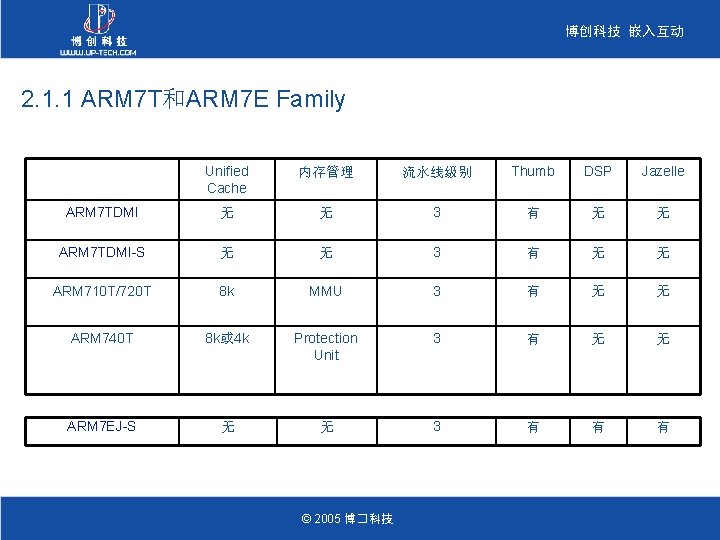

博创科技 嵌入互动 2. 1. 1 ARM 7 T和ARM 7 E Family Unified Cache 内存管理 流水线级别 Thumb DSP Jazelle ARM 7 TDMI 无 无 3 有 无 无 ARM 7 TDMI-S 无 无 3 有 无 无 ARM 710 T/720 T 8 k MMU 3 有 无 无 ARM 740 T 8 k或 4 k Protection Unit 3 有 无 无 ARM 7 EJ-S 无 无 3 有 有 有 © 2005 博� 科技

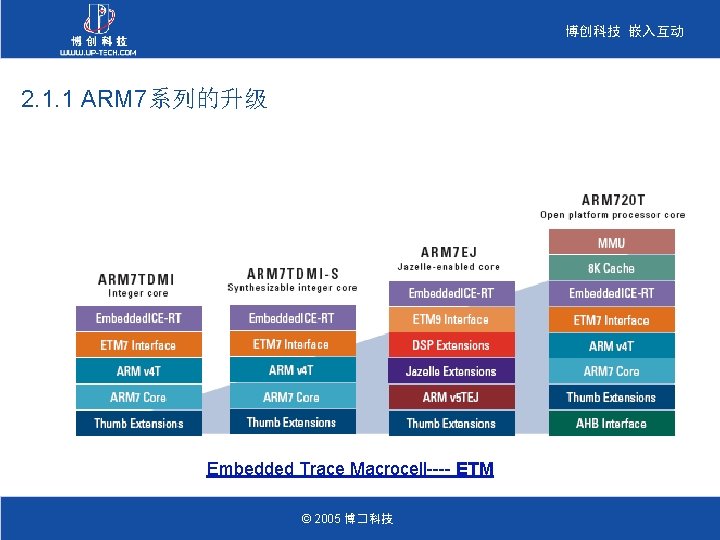

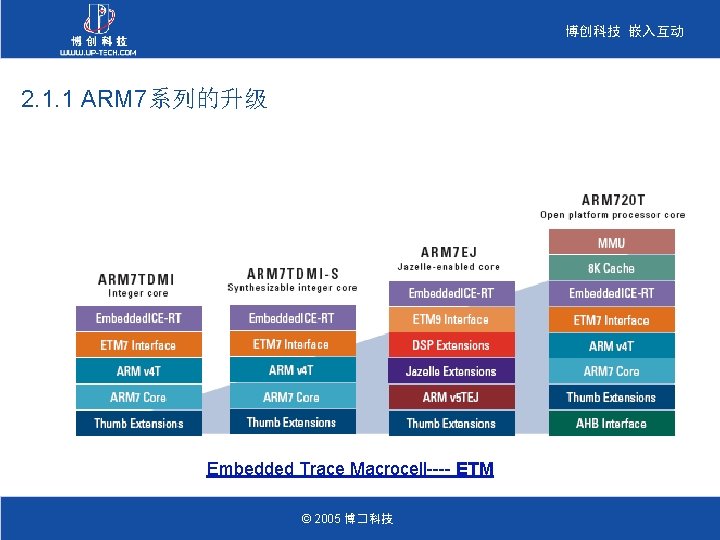

博创科技 嵌入互动 2. 1. 1 ARM 7系列的升级 Embedded Trace Macrocell---- ETM © 2005 博� 科技

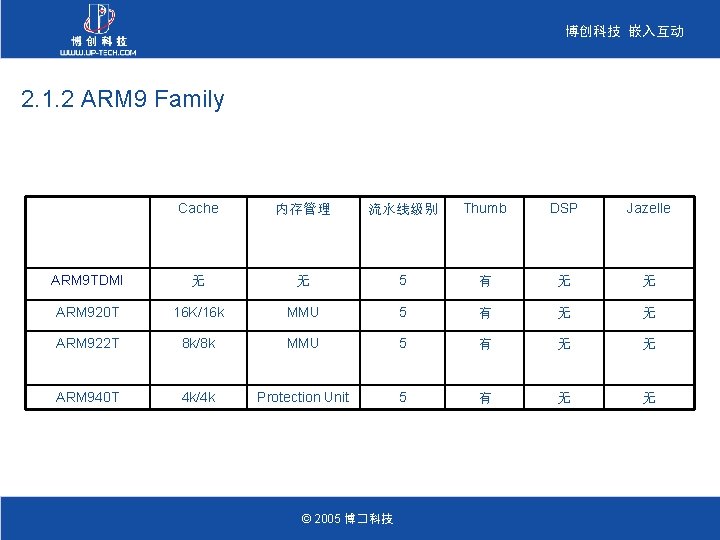

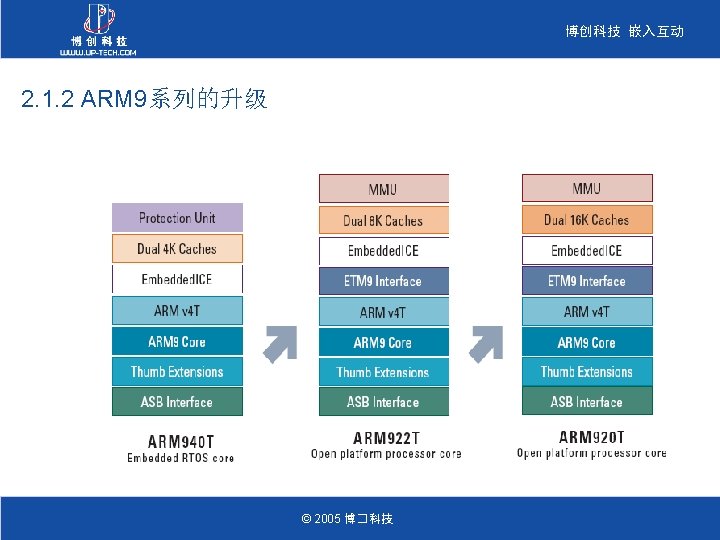

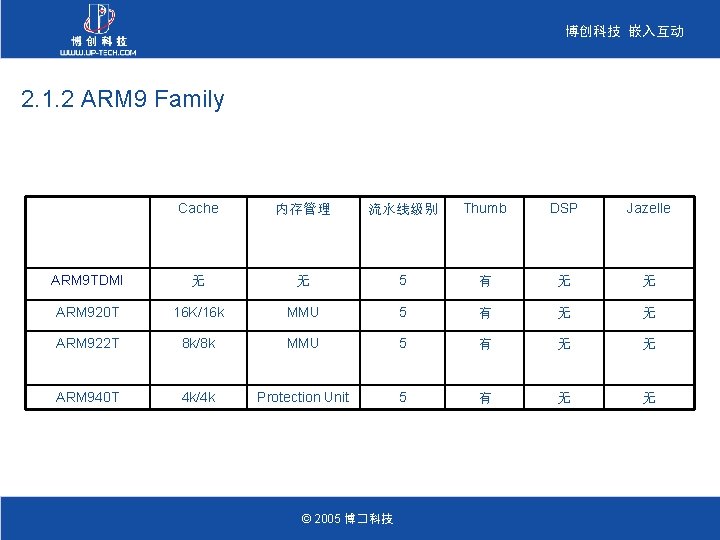

博创科技 嵌入互动 2. 1. 2 ARM 9 Family Cache 内存管理 流水线级别 Thumb DSP Jazelle ARM 9 TDMI 无 无 5 有 无 无 ARM 920 T 16 K/16 k MMU 5 有 无 无 ARM 922 T 8 k/8 k MMU 5 有 无 无 ARM 940 T 4 k/4 k Protection Unit 5 有 无 无 © 2005 博� 科技

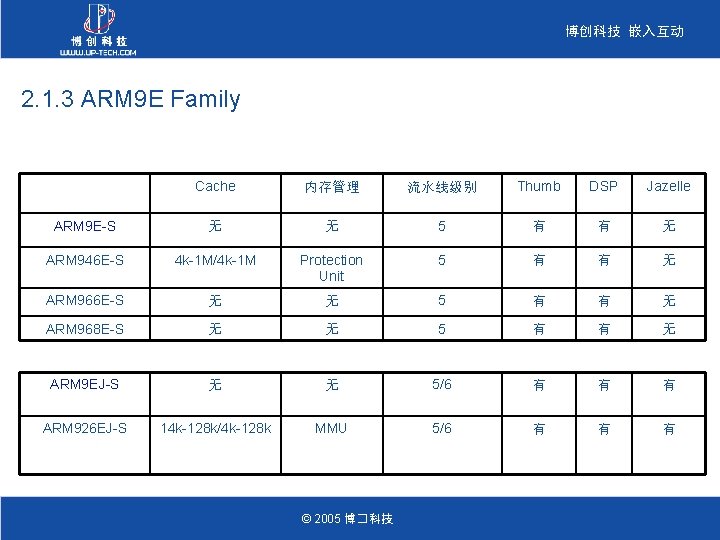

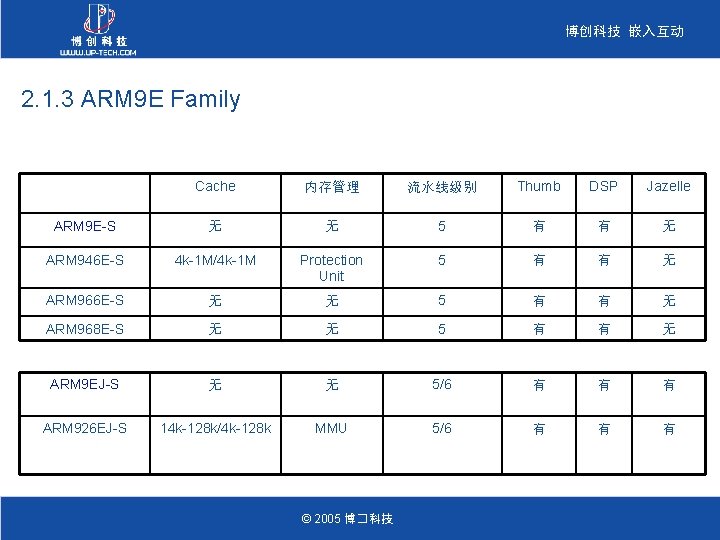

博创科技 嵌入互动 2. 1. 3 ARM 9 E Family Cache 内存管理 流水线级别 Thumb DSP Jazelle ARM 9 E-S 无 无 5 有 有 无 ARM 946 E-S 4 k-1 M/4 k-1 M Protection Unit 5 有 有 无 ARM 966 E-S 无 无 5 有 有 无 ARM 968 E-S 无 无 5 有 有 无 ARM 9 EJ-S 无 无 5/6 有 有 有 ARM 926 EJ-S 14 k-128 k/4 k-128 k MMU 5/6 有 有 有 © 2005 博� 科技

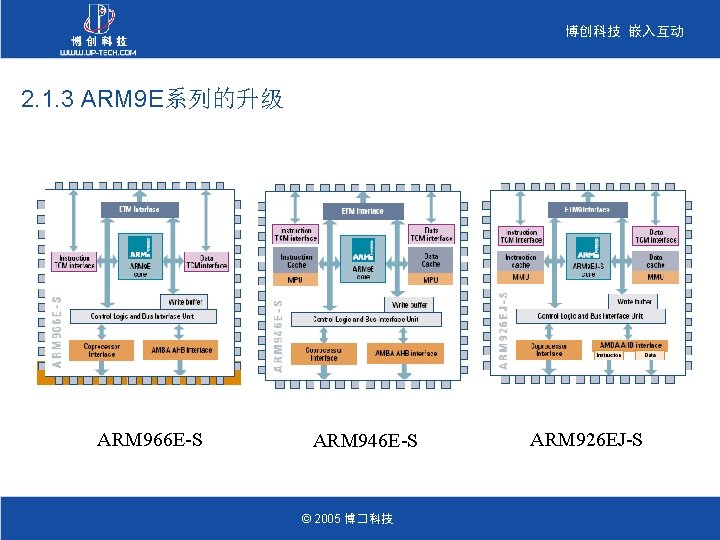

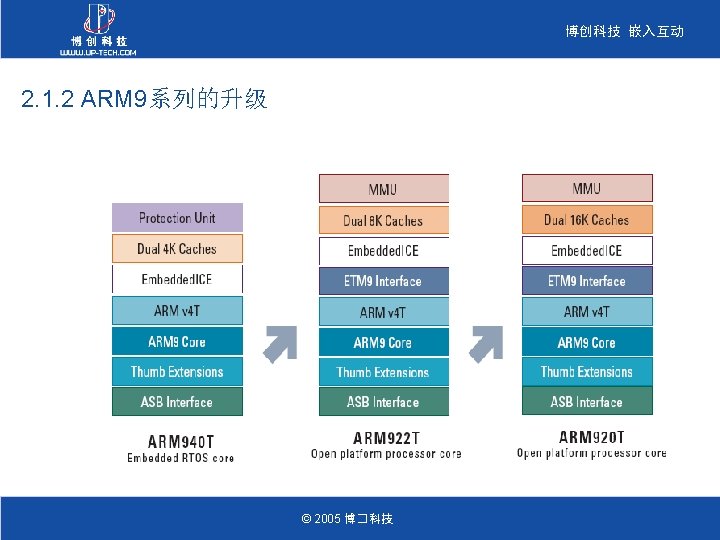

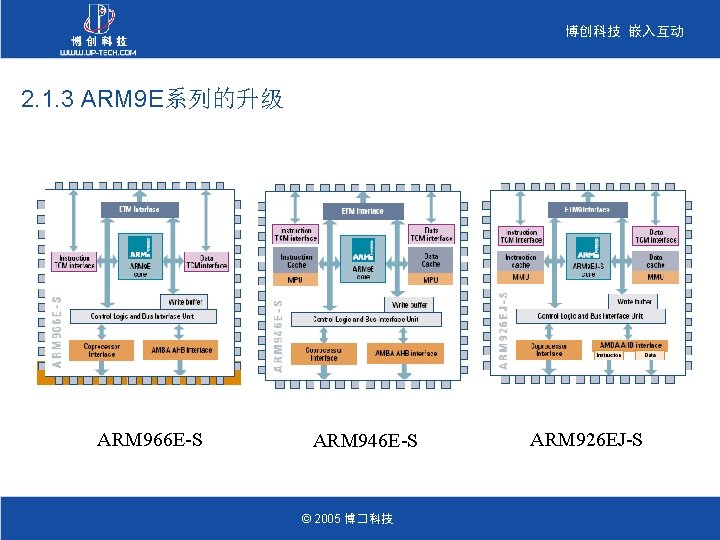

博创科技 嵌入互动 2. 1. 3 ARM 9 E系列的升级 ARM 966 E-S ARM 946 E-S © 2005 博� 科技 ARM 926 EJ-S

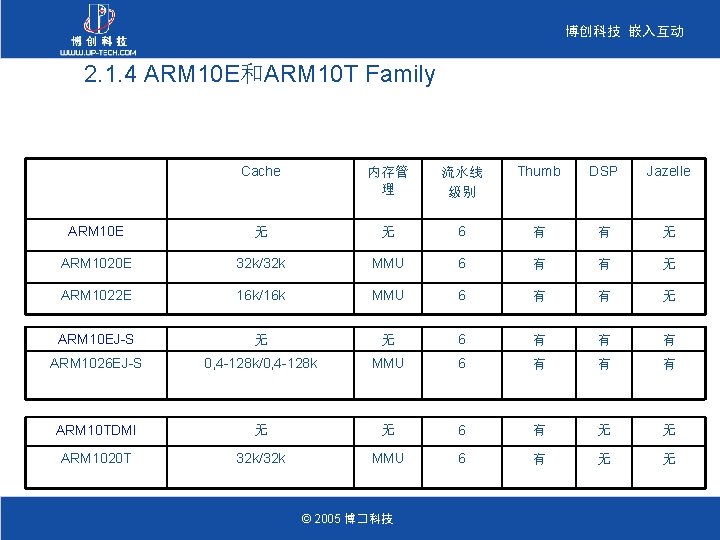

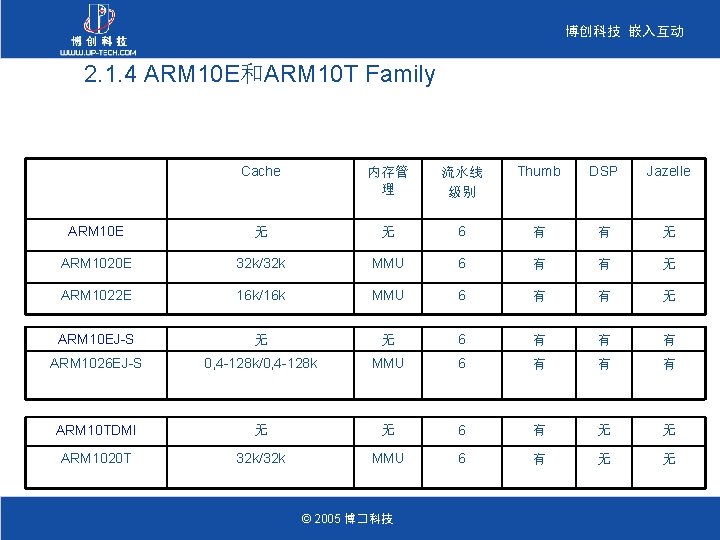

博创科技 嵌入互动 2. 1. 4 ARM 10 E和ARM 10 T Family Cache 内存管 理 流水线 级别 Thumb DSP Jazelle ARM 10 E 无 无 6 有 有 无 ARM 1020 E 32 k/32 k MMU 6 有 有 无 ARM 1022 E 16 k/16 k MMU 6 有 有 无 ARM 10 EJ-S 无 无 6 有 有 有 ARM 1026 EJ-S 0, 4 -128 k/0, 4 -128 k MMU 6 有 有 有 ARM 10 TDMI 无 无 6 有 无 无 ARM 1020 T 32 k/32 k MMU 6 有 无 无 © 2005 博� 科技

博创科技 嵌入互动 2. 1. 5 ARM 11 Family Cache 内存管 理 流水线级 别 Thumb DSP Jazelle 浮点运算 ARM 1136 J-S 4 -64 k MMU 8 有 有 有 无 ARM 1136 JF-S 4 -64 k MMU 8 有 有 ARM 1156 T 2 -S 可配置 9 Thumb-2 有 无 无 ARM 1156 T 2 F-S 可配置 9 Thumb-2 有 无 有 © 2005 博� 科技

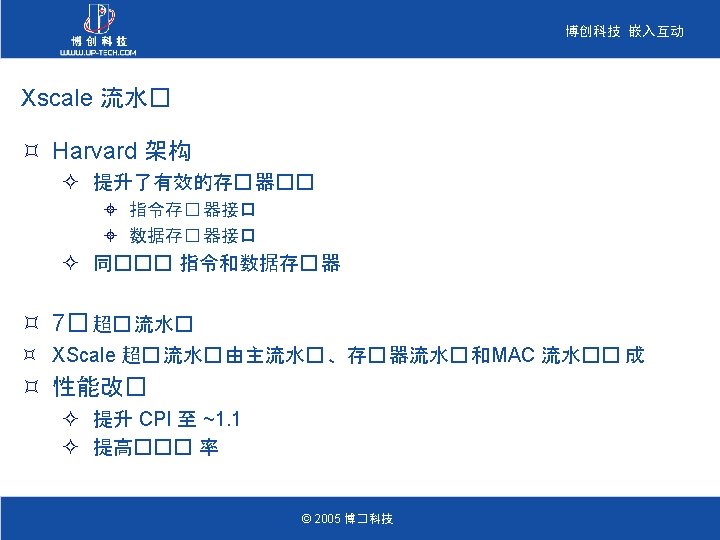

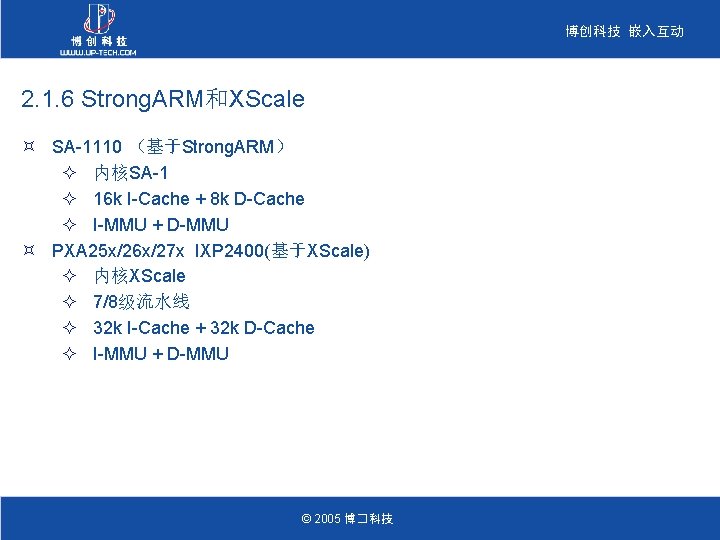

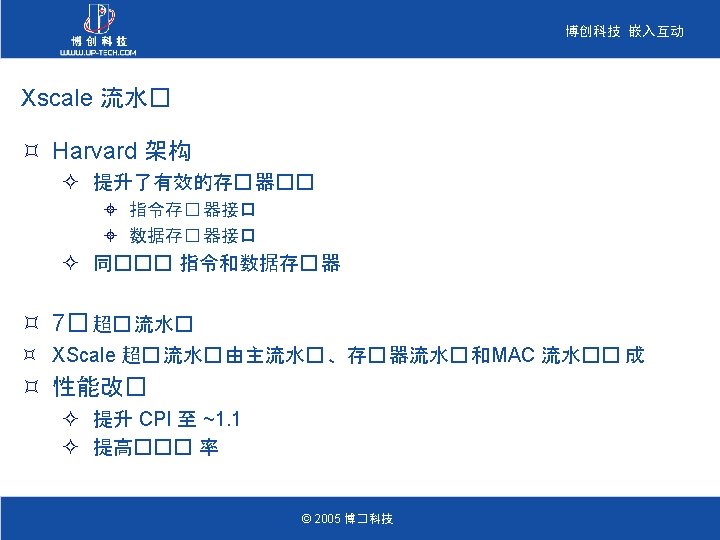

博创科技 嵌入互动 2. 1. 6 Strong. ARM和XScale ³ SA-1110 (基于Strong. ARM) ² 内核SA-1 ² 16 k I-Cache + 8 k D-Cache ² I-MMU + D-MMU ³ PXA 25 x/26 x/27 x IXP 2400(基于XScale) ² 内核XScale ² 7/8级流水线 ² 32 k I-Cache + 32 k D-Cache ² I-MMU + D-MMU © 2005 博� 科技

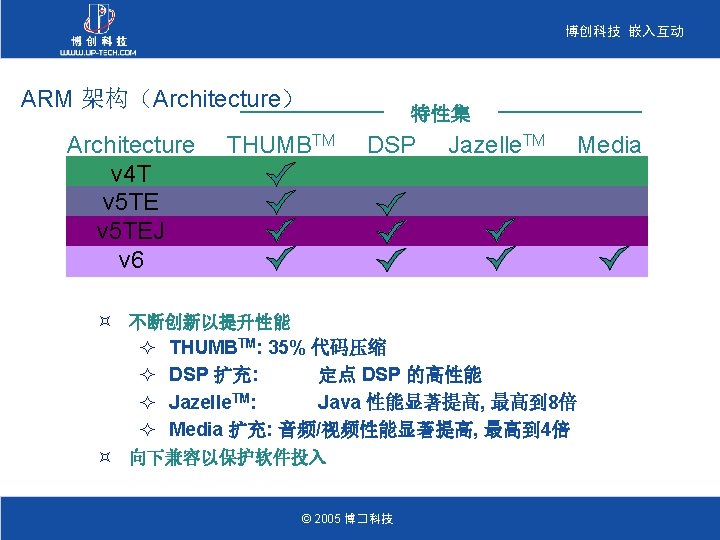

博创科技 嵌入互动 2. 2 指令集体系结构(ISA) Thumb DSP Jazelle Media Trust. Zone Thumb-2 v 4 Strong. ARM v 4 T * ARM 7 T, ARM 9 v 5 T * ARM 10 T,XScale v 5 TE * * v 5 TEJ * * * v 6 Z * * v 6 T 2 * * ARM 9 E, ARM 10 E ARM 7 EJ, ARM 9 EJ, ARM 10 EJ ARM 1136 J(F)-S * * ARM 1156 T 2(F)-S 注:v 5 T支持的Thumb是对v 4 T中的Thumb的扩展 © 2005 博� 科技

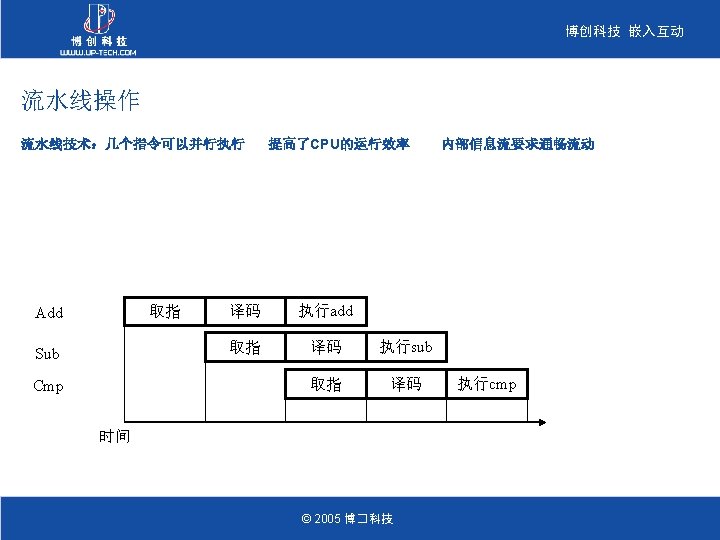

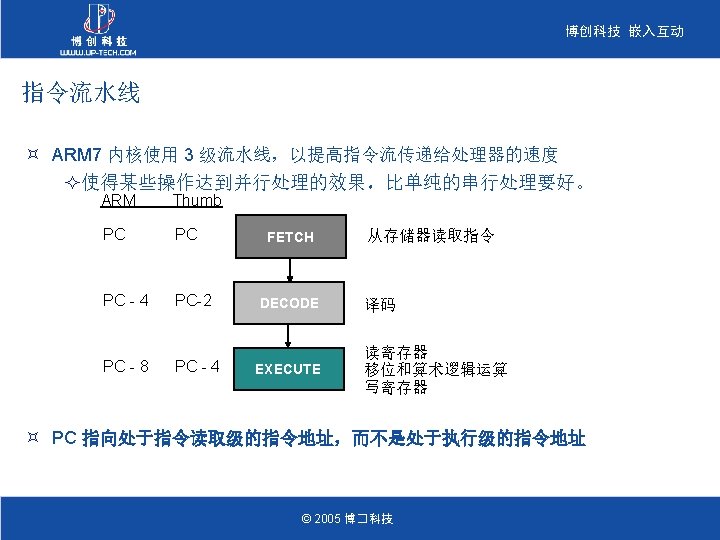

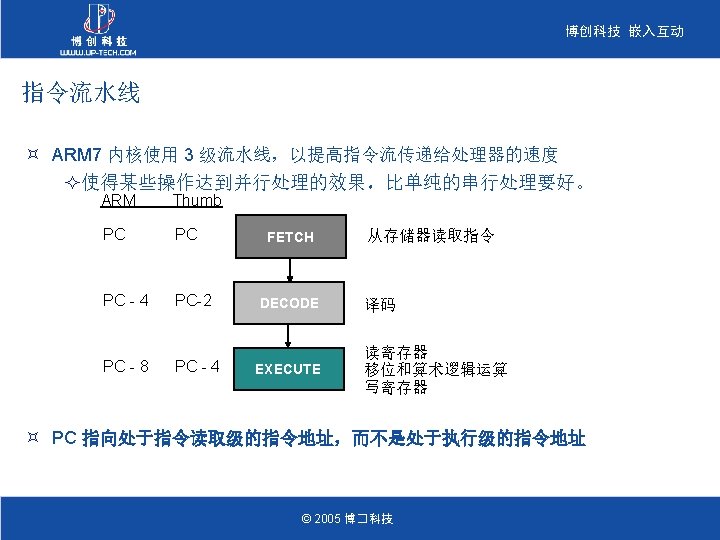

博创科技 嵌入互动 优秀的流水线结构 Cycle 1 2 3 4 5 6 Operation ADD SUB MOV AND Fetch Decode Execute Fetch ORR Decode Execute Fetch EOR Decode Execute Fetch CMP Decode Fetch RSB ³ 本例中 6 个时钟周期内一共完成了 6 条指令 ³ 全部对寄存器进行操作 (单周期执行) ³ 指令周期数 (CPI) = 1 © 2005 博� 科技

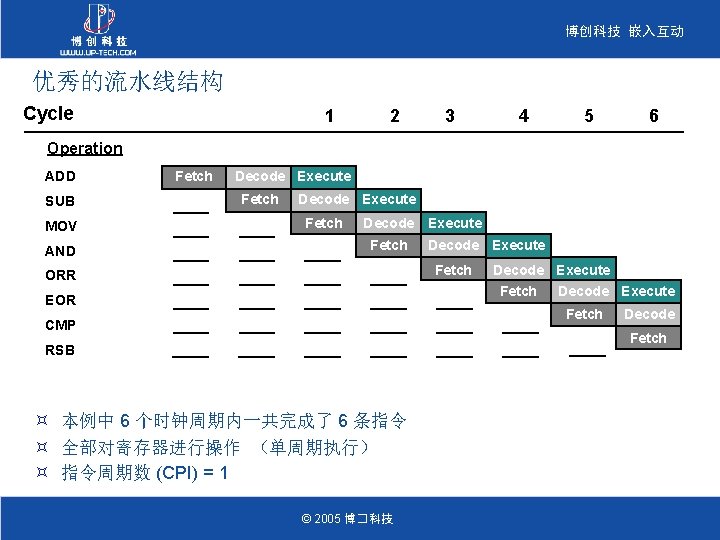

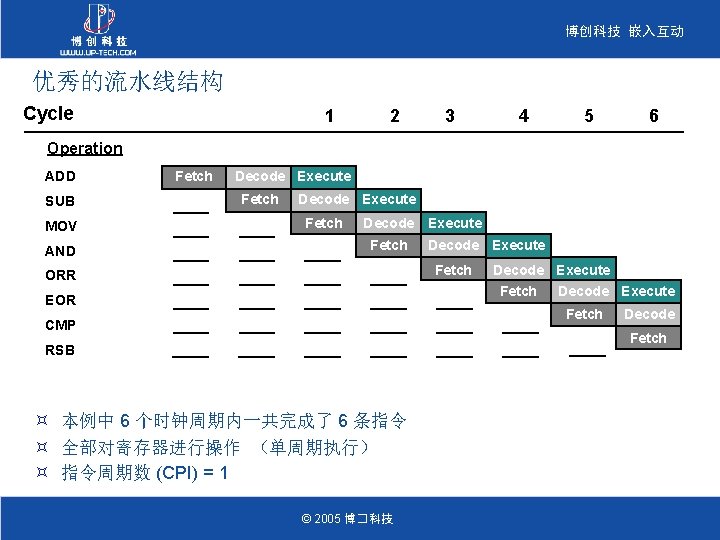

博创科技 嵌入互动 流水线执行举例:LDR Cycle 1 2 3 4 5 6 Operation ADD SUB LDR MOV Fetch Decode Execute Fetch AND Data Writeback Decode Execute Fetch Decode Fetch ORR ³ 本例中 6 个时钟周期内一共完成了 4 条指令 ³ 指令周期数(CPI) = 1. 5 © 2005 博� 科技

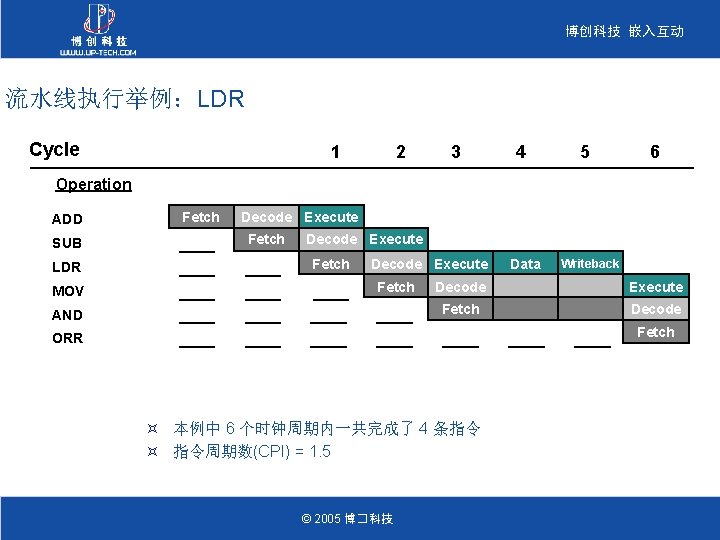

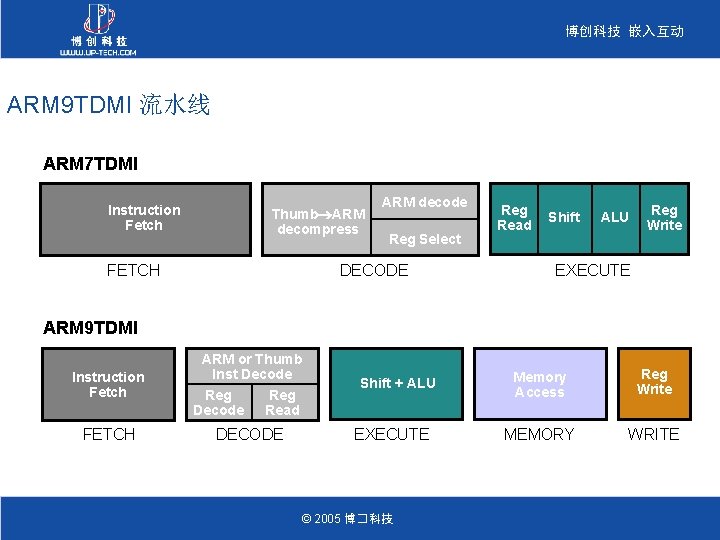

博创科技 嵌入互动 ARM 9 TDMI 流水线 ARM 7 TDMI Instruction Fetch Thumb®ARM decompress FETCH ARM decode Reg Select DECODE Reg Read Shift ALU Reg Write EXECUTE ARM 9 TDMI Instruction Fetch ARM or Thumb Inst Decode Reg Decode Read FETCH DECODE Shift + ALU EXECUTE © 2005 博� 科技 Memory Access Reg Write MEMORY WRITE

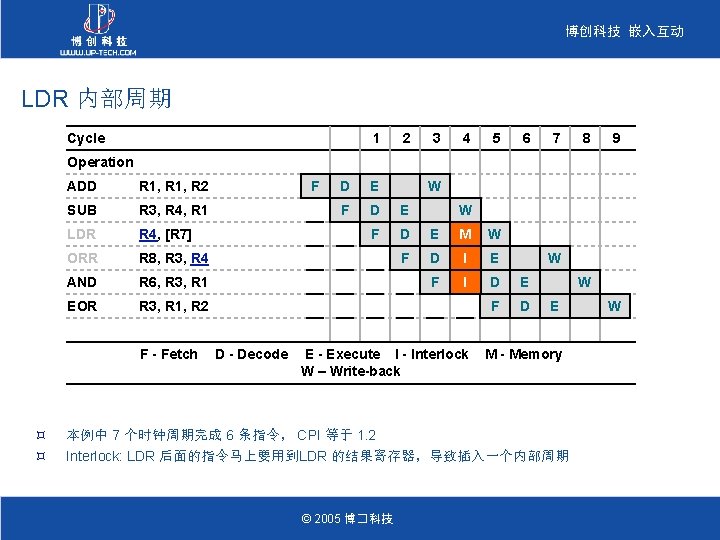

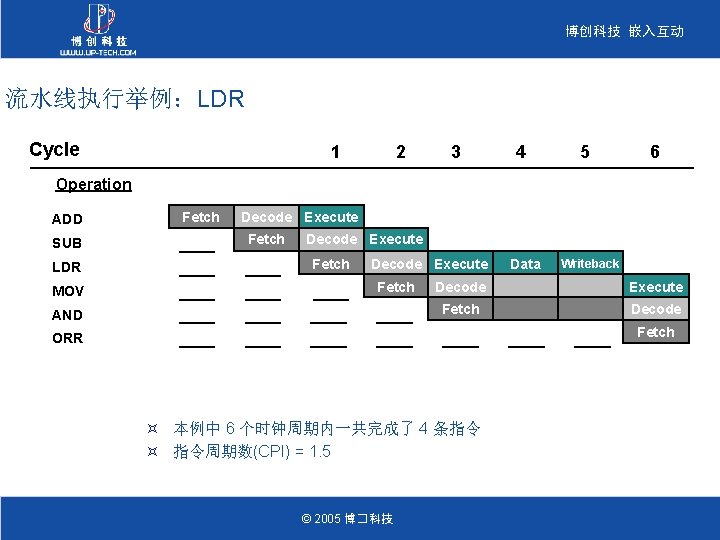

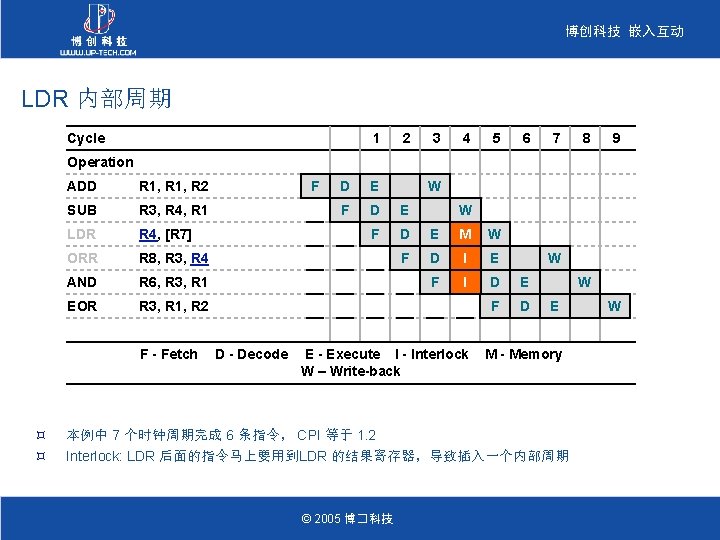

博创科技 嵌入互动 LDR 内部周期 Cycle 1 2 3 4 5 6 7 8 9 Operation ADD R 1, R 2 SUB R 3, R 4, R 1 LDR R 4, [R 7] ORR R 8, R 3, R 4 AND R 6, R 3, R 1 EOR R 3, R 1, R 2 F - Fetch ³ ³ F D - Decode D E W F D E M W F D I E F I D E F D W E - Execute I - Interlock W – Write-back W W E M - Memory 本例中 7 个时钟周期完成 6 条指令, CPI 等于 1. 2 Interlock: LDR 后面的指令马上要用到LDR 的结果寄存器,导致插入一个内部周期 © 2005 博� 科技 W

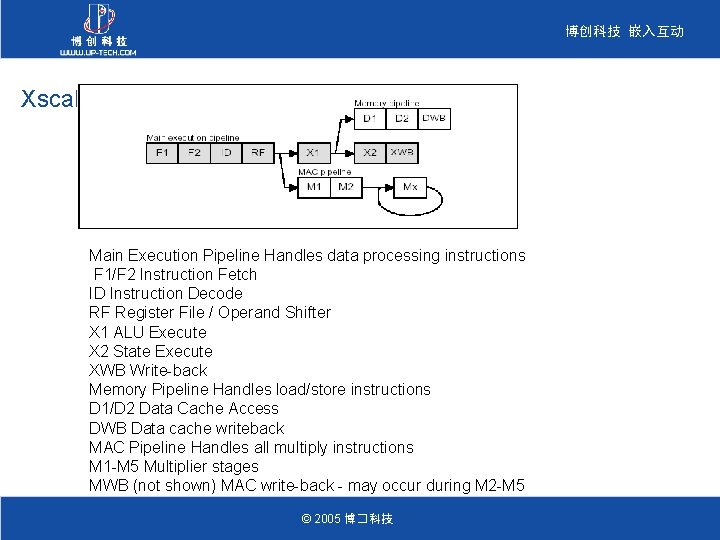

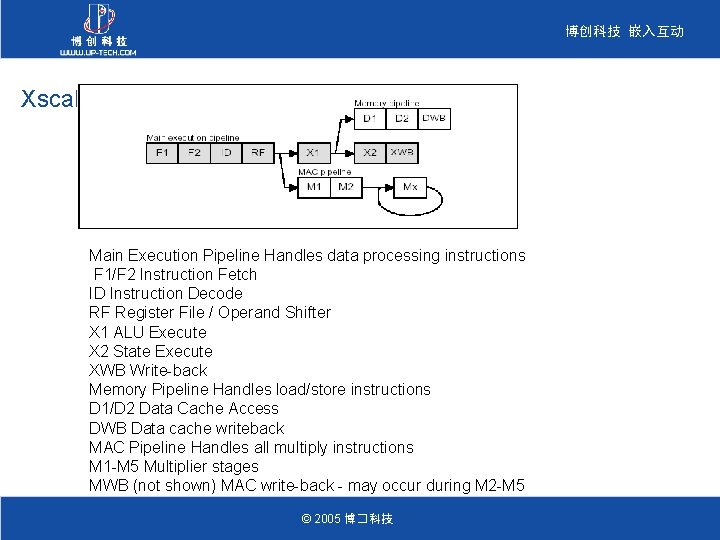

博创科技 嵌入互动 Xscale 流水� Main Execution Pipeline Handles data processing instructions F 1/F 2 Instruction Fetch ID Instruction Decode RF Register File / Operand Shifter X 1 ALU Execute X 2 State Execute XWB Write-back Memory Pipeline Handles load/store instructions D 1/D 2 Data Cache Access DWB Data cache writeback MAC Pipeline Handles all multiply instructions M 1 -M 5 Multiplier stages MWB (not shown) MAC write-back - may occur during M 2 -M 5 © 2005 博� 科技

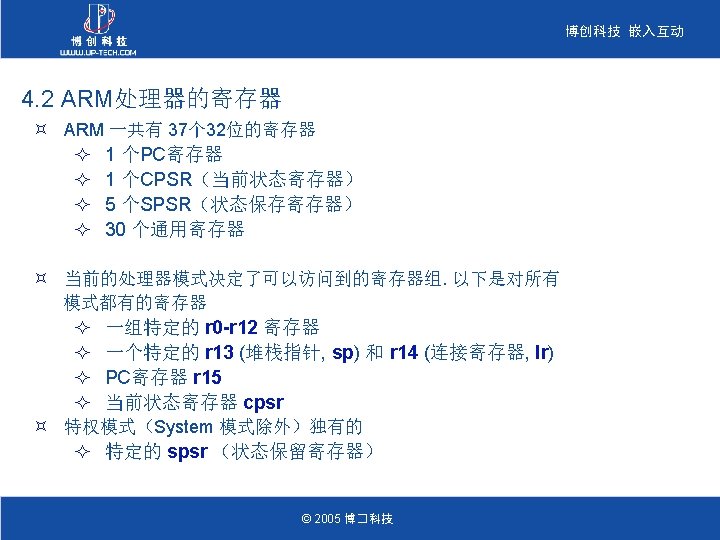

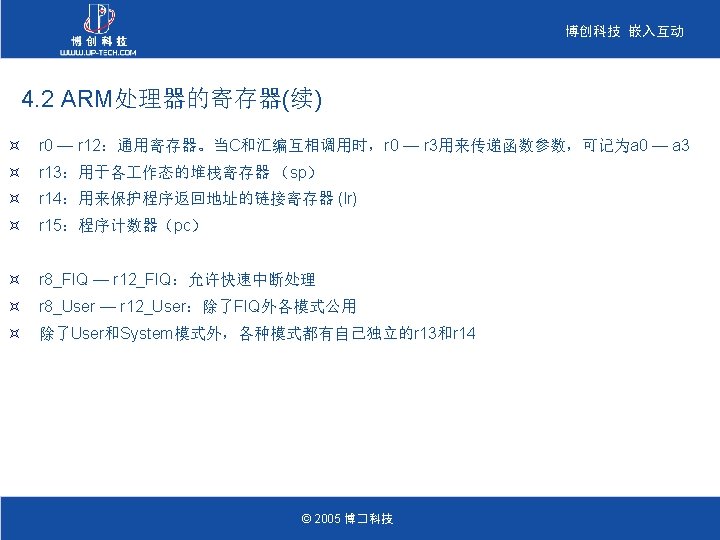

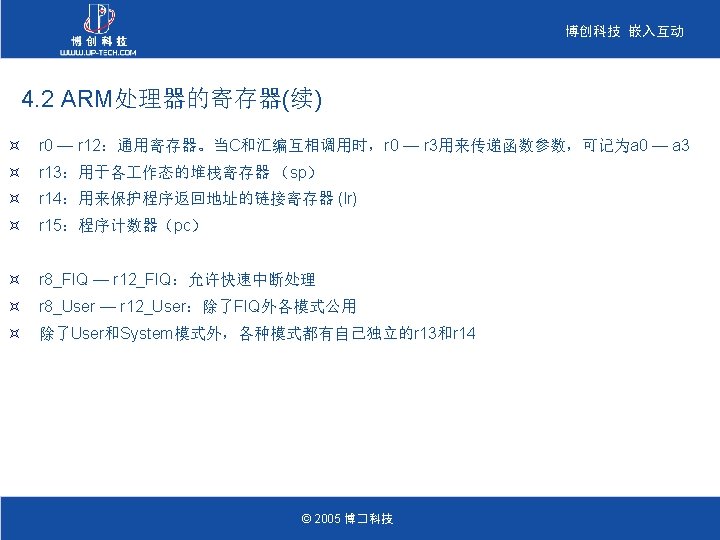

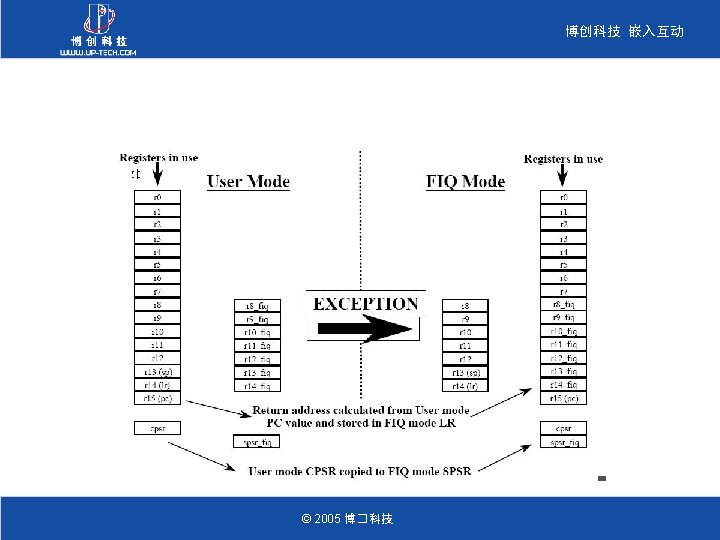

博创科技 嵌入互动 4. 2 ARM处理器的寄存器(续) User/System Supervisor Abort Undefined Interrupt Fast Interrupt R 0 R 1 R 2 R 3 R 4 R 5 R 6 R 7 R 8 R 9 R 10 R 0 R 1 R 2 R 3 R 4 R 5 R 6 R 7 R 8 R 9 R 10 R 1 R 2 R 3 R 4 R 5 R 6 R 7 R 8_FIQ R 9_FIQ R 10_FIQ R 11 R 11_FIQ R 12 R 12_FIQ R 13_SVC R 13_ABORT R 13_UNDEF R 13_IRQ R 13_FIQ R 14_SVC R 14_ABORT R 14_UNDEF R 14_IRQ R 14_FIQ PC CPSR SPSR_SVC PC CPSR SPSR_ABORT PC CPSR SPSR_UNDEF PC CPSR SPSR_IRQ PC CPSR SPSR_FIQ © 2005 博� 科技

博创科技 嵌入互动 寄存器组织 Current Visible Registers Undef SVCMode User Abort User Mode FIQ IRQ User Mode r 0 r 0 r 1 r 1 r 2 r 2 r 3 r 3 r 4 r 4 r 5 r 5 r 6 r 6 r 7 r 7 r 8 r 8 r 9 r 9 r 10 r 11 r 12 r 13 (sp) r 14 (lr) r 15 (pc) cpsr spsr Banked out Registers User FIQ FIQ r 8 r 9 r 10 r 11 r 12 r 13 (sp) r 14 (lr) r 14 r 8 r 8 r 9 r 9 r 10 r 11 r 12 r 13 (sp) r 14 (lr) spsr © 2005 博� 科技 IRQ IRQ r 13 r 14 (sp) (lr) spsr SVC SVC r 13 r 14 (sp) (lr) spsr Undef r 13 r 14 (sp) (lr) spsr Abort r 13 r 14 (sp) (lr) spsr

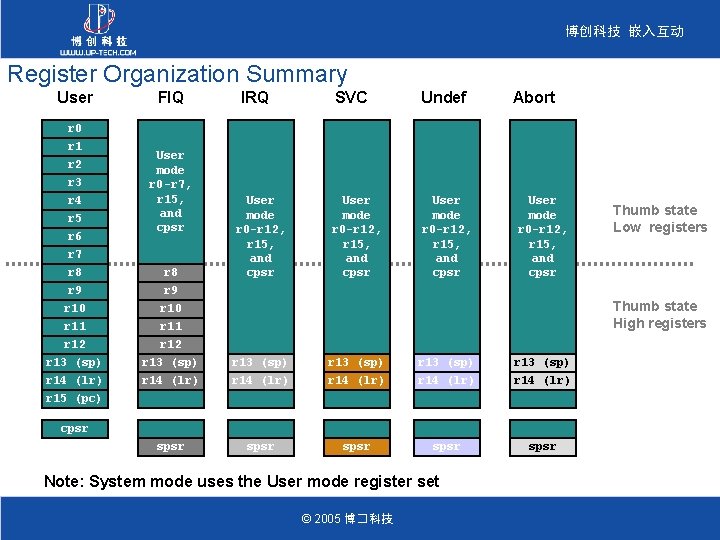

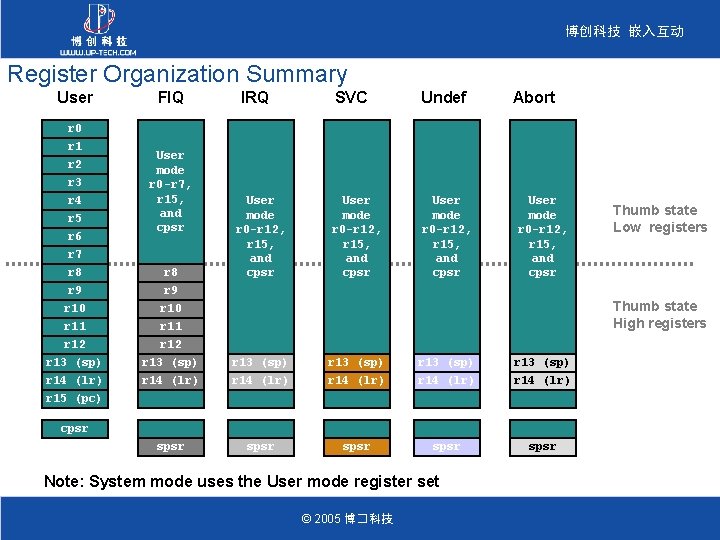

博创科技 嵌入互动 Register Organization Summary User FIQ IRQ SVC Undef User mode r 0 -r 12, r 15, and cpsr Abort r 0 r 1 r 2 r 3 r 4 r 5 r 6 r 7 r 8 r 9 r 10 r 11 r 12 r 13 (sp) r 14 (lr) r 15 (pc) User mode r 0 -r 7, r 15, and cpsr User mode r 0 -r 12, r 15, and cpsr r 8 r 9 r 10 r 11 r 12 r 13 (sp) r 14 (lr) r 13 (sp) r 14 (lr) spsr spsr Thumb state Low registers Thumb state High registers cpsr Note: System mode uses the User mode register set © 2005 博� 科技

![博创科技 嵌入互动 4 3 CPSRSPSR 续 M4 0 模式 Accessible Registers 10000 User PC 博创科技 嵌入互动 4. 3 CPSR/SPSR (续) M[4: 0] 模式 Accessible Registers 10000 User PC,](https://slidetodoc.com/presentation_image/56d3e73d6336f8fe8dcb1106252b9294/image-71.jpg)

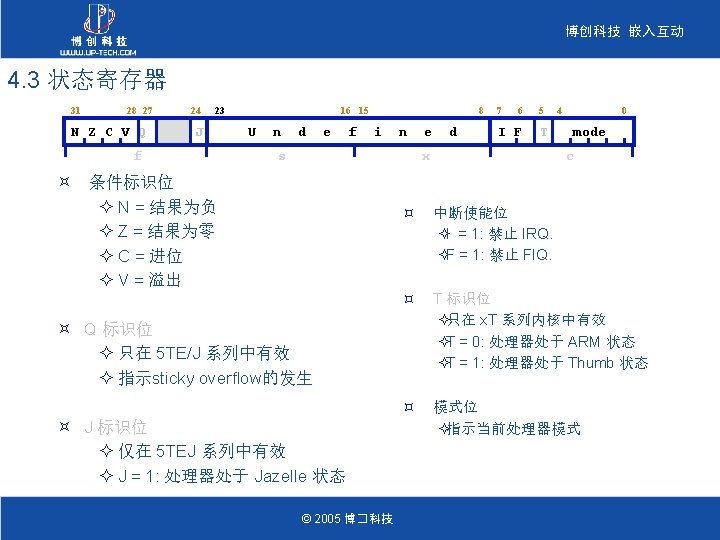

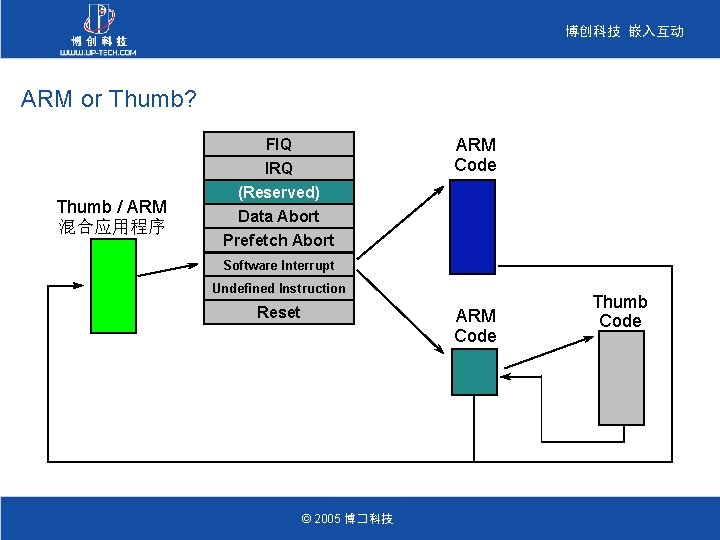

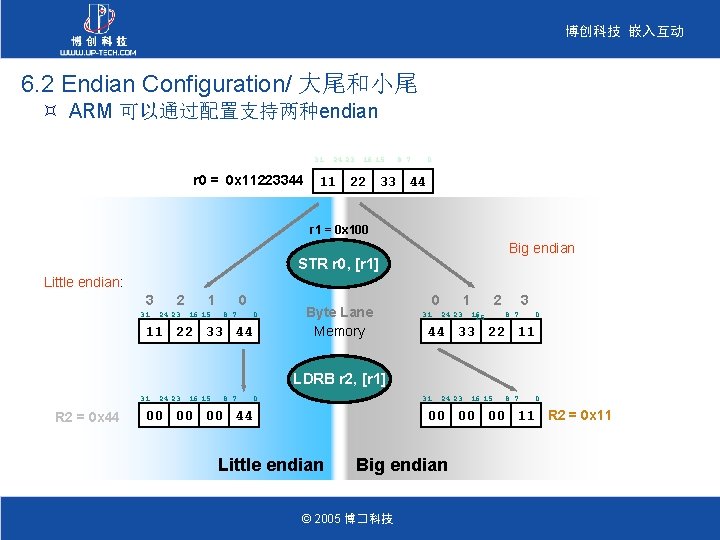

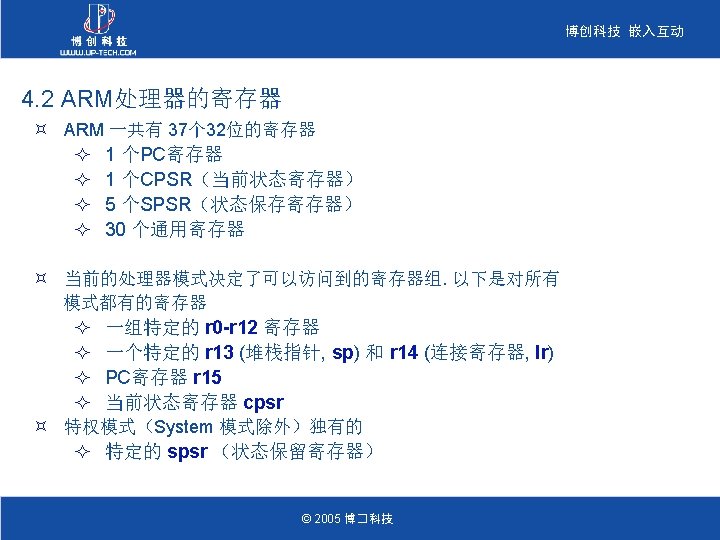

博创科技 嵌入互动 4. 3 CPSR/SPSR (续) M[4: 0] 模式 Accessible Registers 10000 User PC, R 14 to R 0, CPSR 10001 FIQ PC, R 14_FIQ to R 8_FIQ, R 7 to R 0, CPSR, SPSR_FIQ 10010 IRQ PC, R 14_IRQ, R 13_IRQ, R 12 to R 0, CPSR, SPSR_IRQ 10011 SVC PC, R 14_SVC, R 13_SVC, R 12 to R 0, CPSR, SPSR_SVC 10111 Abort PC, R 14_ABORT, R 13_ABORT, R 12 to R 0, CPSR, SPSR_ABORT 11011 Undef PC, R 14_UNDEF, R 13_UNDEF, R 12 to R 0, CPSR, SPSR_UNDEF 11111 System PC, R 14 to R 0, CPSR (Architecture 4 only) © 2005 博� 科技

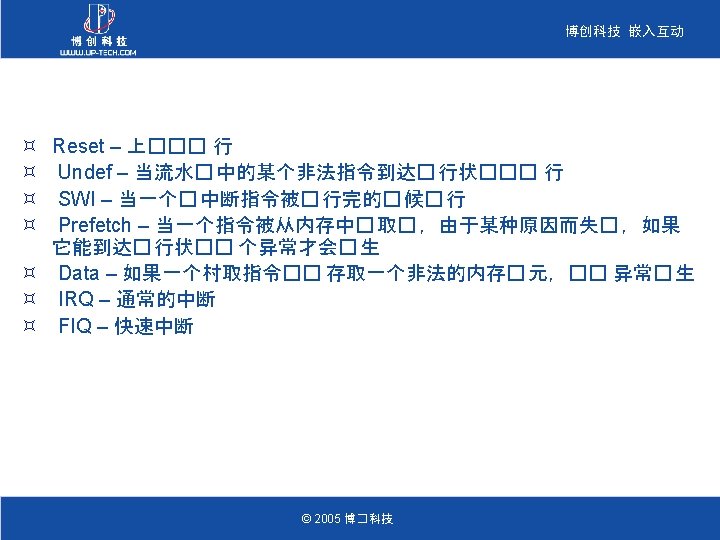

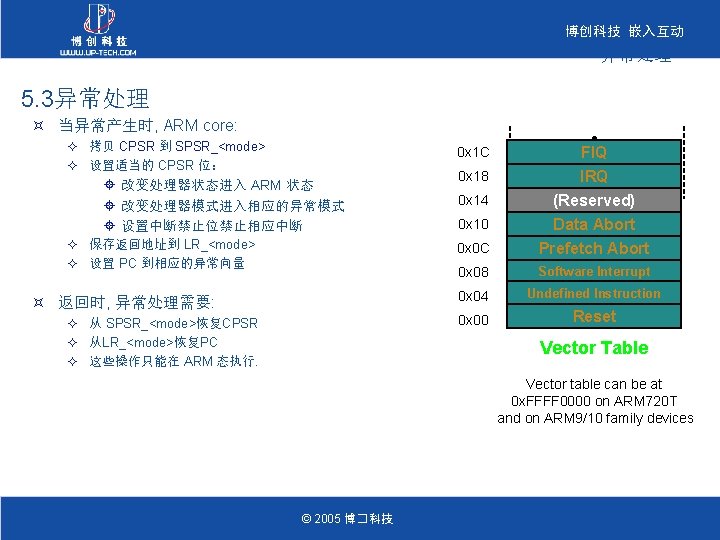

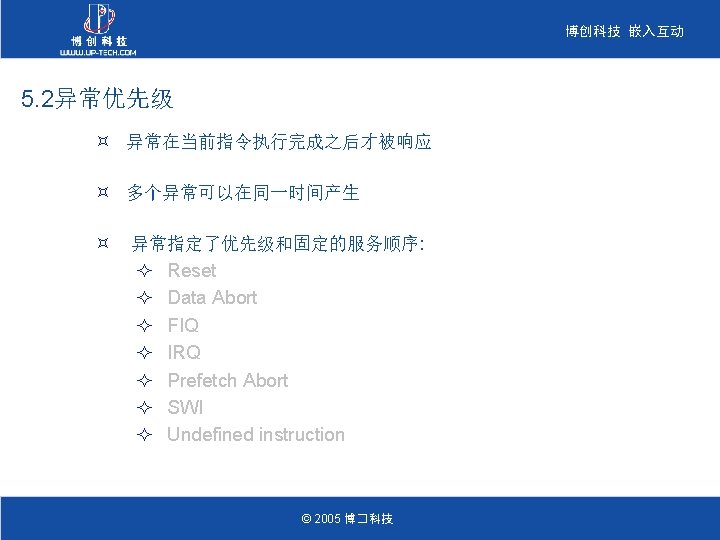

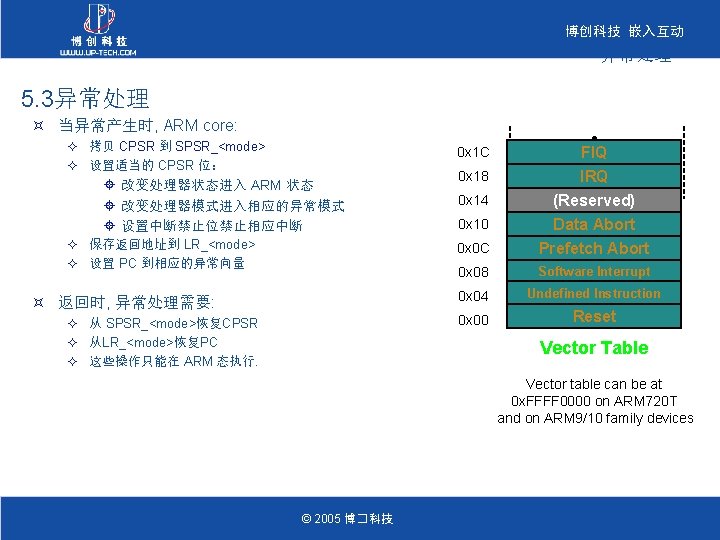

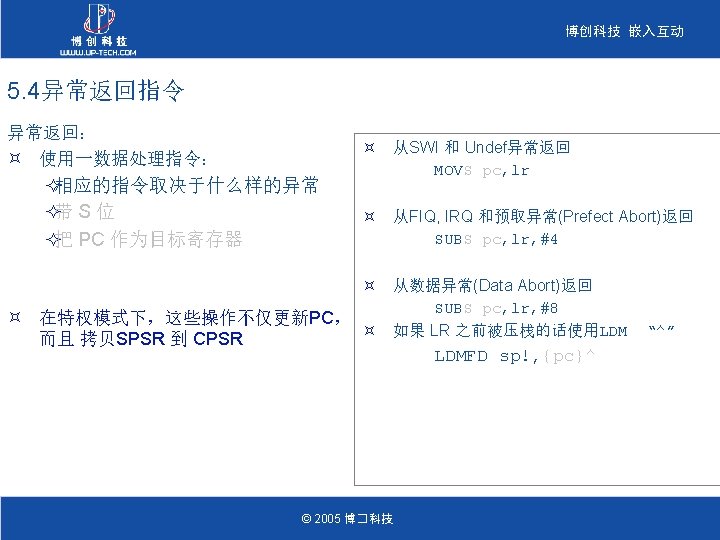

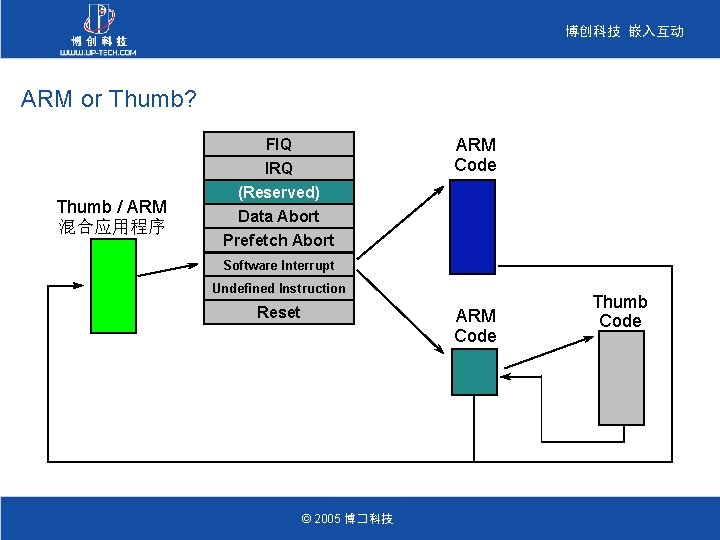

博创科技 嵌入互动 异常处理 5. 3异常处理 ³ 当异常产生时, ARM core: ² 拷贝 CPSR 到 SPSR_<mode> ² 设置适当的 CPSR 位: ± 改变处理器状态进入 ARM 状态 ± 改变处理器模式进入相应的异常模式 ± 设置中断禁止位禁止相应中断 ² 保存返回地址到 LR_<mode> ² 设置 PC 到相应的异常向量 ³ 返回时, 异常处理需要: ² 从 SPSR_<mode>恢复CPSR ² 从LR_<mode>恢复PC ² 这些操作只能在 ARM 态执行. 0 x 0 C FIQ IRQ (Reserved) Data Abort Prefetch Abort 0 x 08 Software Interrupt 0 x 04 Undefined Instruction 0 x 00 Reset 0 x 1 C 0 x 18 0 x 14 0 x 10 Vector Table Vector table can be at 0 x. FFFF 0000 on ARM 720 T and on ARM 9/10 family devices © 2005 博� 科技

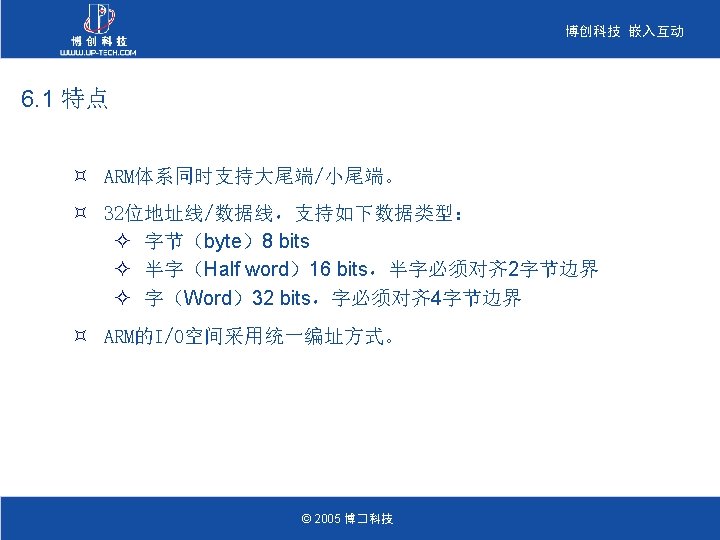

博创科技 嵌入互动 ARM or Thumb? Thumb / ARM 混合应用程序 FIQ IRQ (Reserved) Data Abort Prefetch Abort ARM Code Software Interrupt Undefined Instruction Reset ARM Code © 2005 博� 科技 Thumb Code

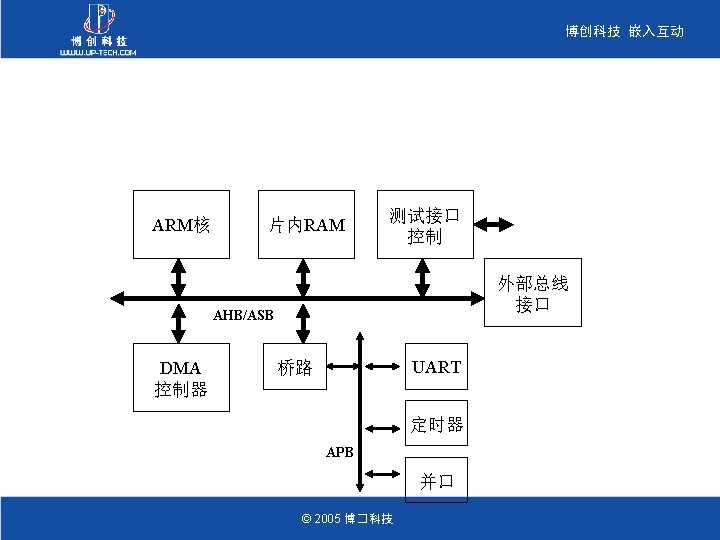

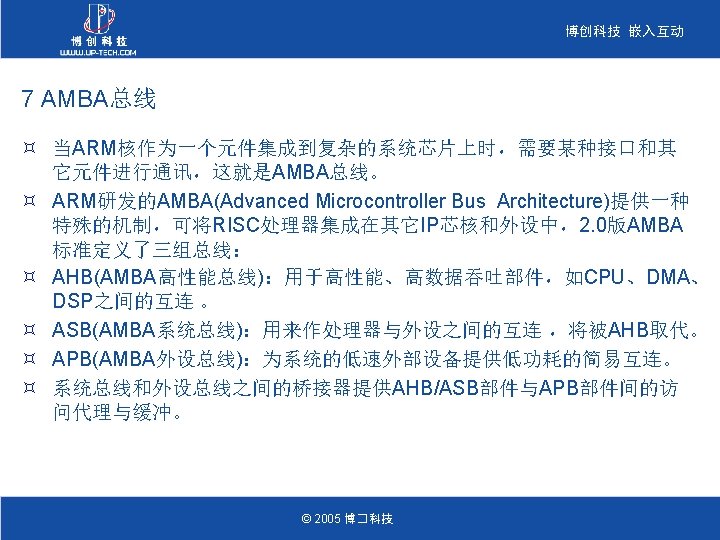

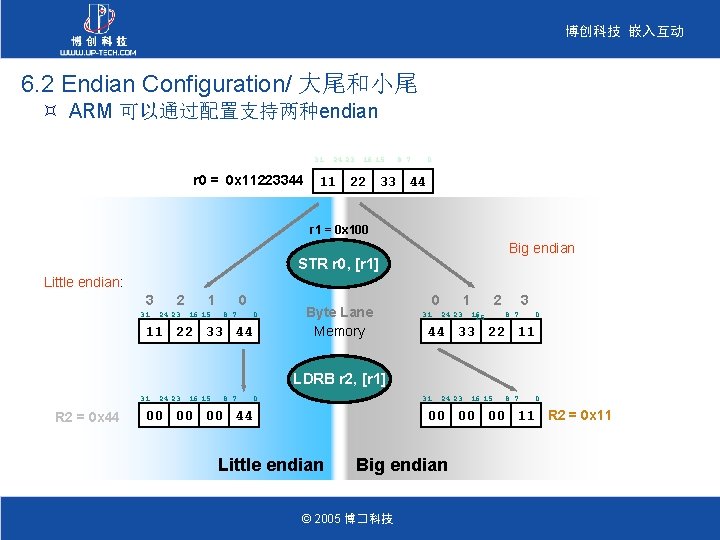

博创科技 嵌入互动 6. 2 Endian Configuration/ 大尾和小尾 ³ ARM 可以通过配置支持两种endian 31 r 0 = 0 x 11223344 24 23 16 15 8 7 0 11 22 33 44 r 1 = 0 x 100 Big endian STR r 0, [r 1] Little endian: 3 31 2 1 24 23 16 15 0 8 7 0 11 22 33 44 Byte Lane Memory 0 31 1 24 23 16 15 2 3 8 7 0 44 33 22 11 LDRB r 2, [r 1] 31 R 2 = 0 x 44 24 23 16 15 8 7 0 31 24 23 16 15 8 7 0 00 00 00 11 R 2 = 0 x 11 00 00 00 44 Little endian Big endian © 2005 博� 科技