CPUs Microcode Protection And Processor Modes Chapter 7

- Slides: 39

CPUs: Microcode, Protection And Processor Modes Chapter 7

Evolution of Computers Early systems �Single Central Processing Unit (CPU) �controlled entire computer �Responsible for all I/O as well as computation Modern computer �Decentralized architecture(multiple processors) �I/O device such as disk contains processor �CPU coordinates and controls other processors

CPU Complexity �Designed for wide variety of control and processing tasks �Many special-purpose subunits for speed �Example: Pentium contains 54 million transistors

Why is CPU so Complex? 1. Multiple Roles: running application programs, operating system, handling external I/O devices, starting or stopping the computer and managing memory. Hence CPU often include Multiple Instruction sets to do all the roles. 2. Protection and Privilege: In modern computers some subsystems have higher privilege than others Ex: an application program can be prevented from directly interacting with I/O devices , operating system code can be protected from deliberate change. 3. Hardware priorities: CPU uses priority schemes Ex: I/O devices have higher priority than application programs.

Why is CPU so Complex? (cont’) 4. Generality: CPU works with many applications hence the instruction set contains many and different types of instructions (i. e. CISC design) 5. Data Size: CPU is designed to handle large data values. Thus for the purpose of speed the logic gates are replicated. Ex. To handle 64 bit value the CPU must have 64 copies of each gate. 6. Speed: Most significant source of CPU complexity is due to the desire for speed. To achieve highest performance the functional units in the CPU are replicated and they operate simultaneously (parallel hardware)

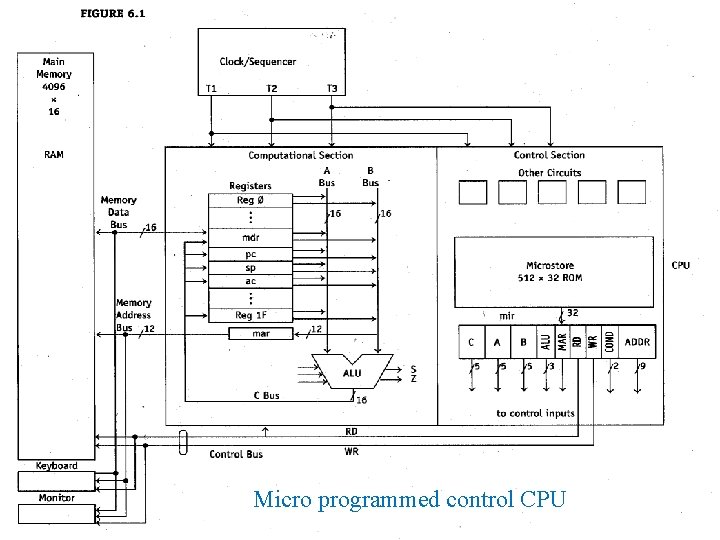

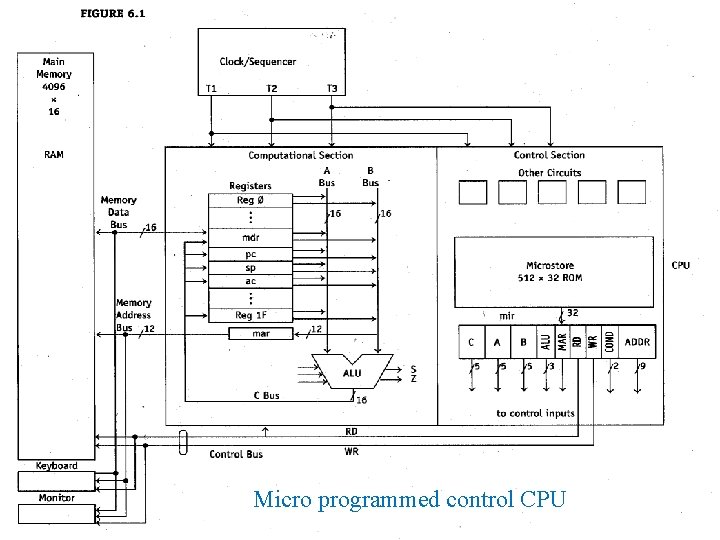

Implementing the Instruction Set �The instructions can be implemented in the CPU either by hard wired control or by micro programmed control. �Hard wired Control: Direct implementation is accomplished using the logic gates. - difficult to debug and change - very fast but expensive �Micro Programmed control: Implemented using a microcontroller and micro code. - flexible - slow , stored in EEPROM called control store

Microcontroller �Microcontroller: An integrated chip which has the ability to execute a stored set of instructions. -Microcontroller is like a computer inside a single chip. - It has all necessary parts (CPU, ROM, RAM, timers) integrated inside one IC. - Its not the same as the standard processor. - It can contain instructions for LOAD, STORE, ADD etc, like the general processor.

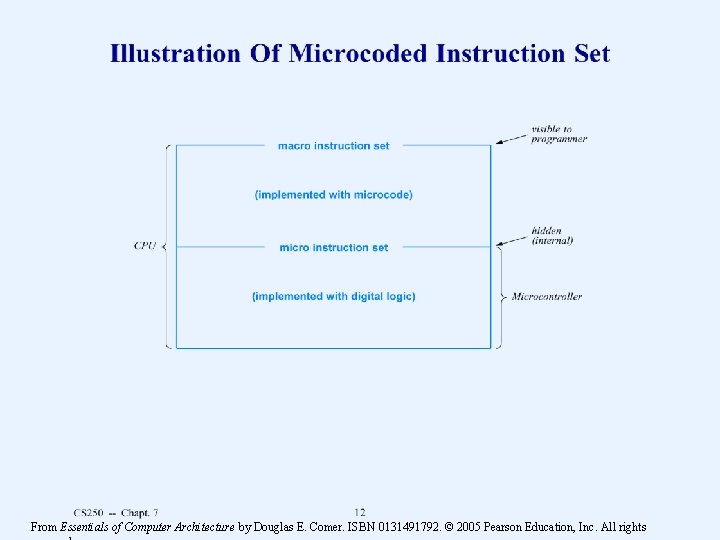

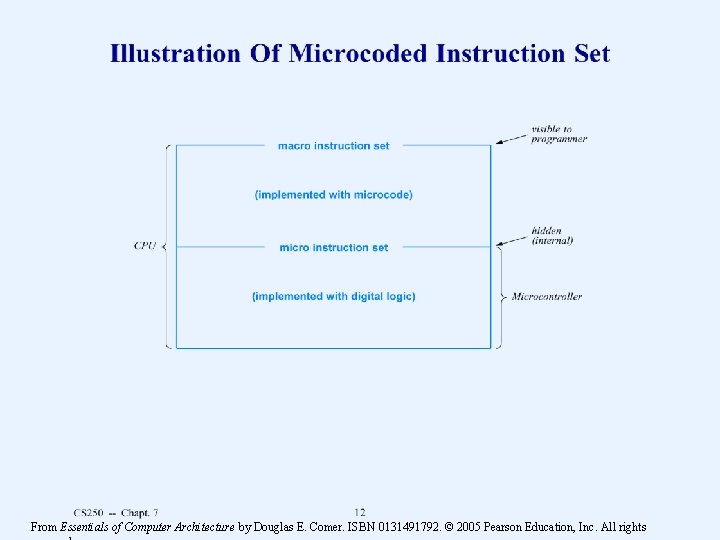

Micro Coded Instructions Microcode: -Micro programs form the code which in turn consist of series of microinstructions. - It runs on the microcontroller. - It is not visible to a programmer �Micro-instructions: low-level instructions used to implement complex machine instructions (macroinstructions) �-Macro instructions: ISA instructions implemented as microcode subroutines �Can be entirely different than micro instructions

From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. © 2005 Pearson Education, Inc. All rights

Micro programmed control CPU

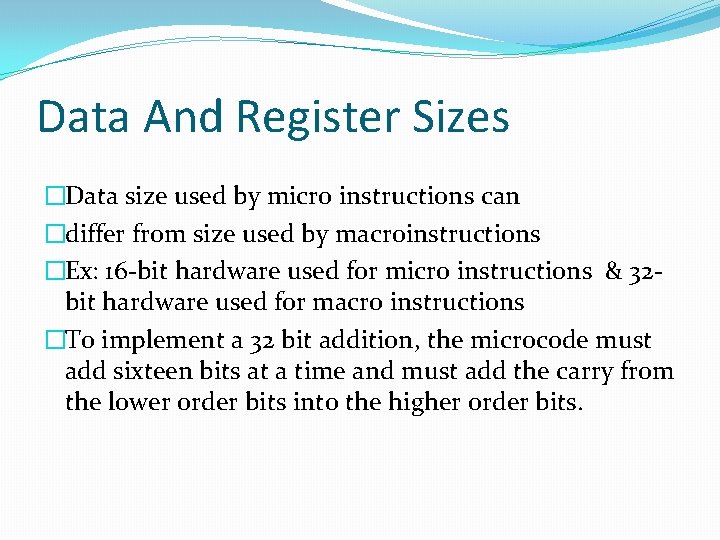

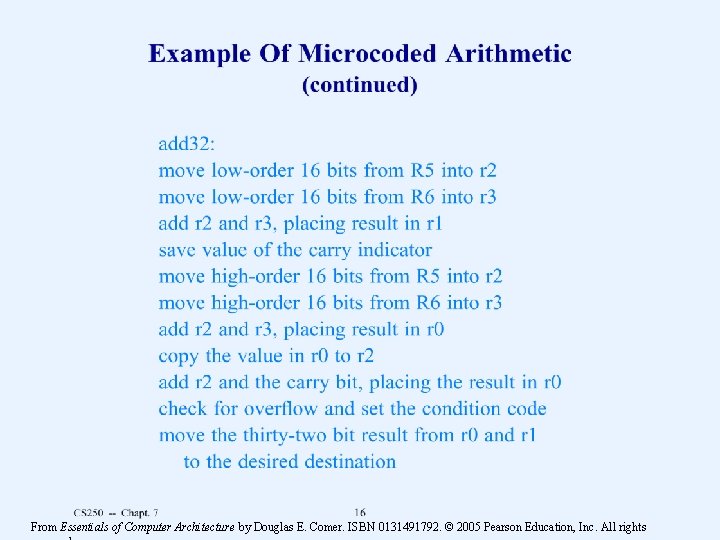

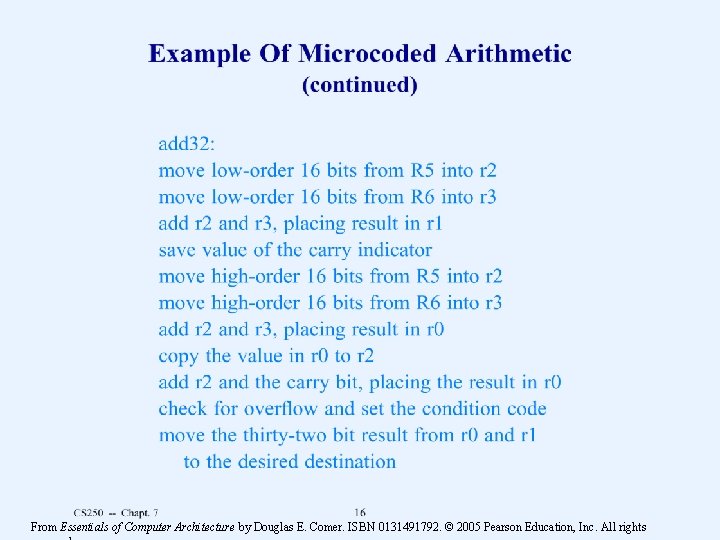

Data And Register Sizes �Data size used by micro instructions can �differ from size used by macroinstructions �Ex: 16 -bit hardware used for micro instructions & 32 bit hardware used for macro instructions �To implement a 32 bit addition, the microcode must add sixteen bits at a time and must add the carry from the lower order bits into the higher order bits.

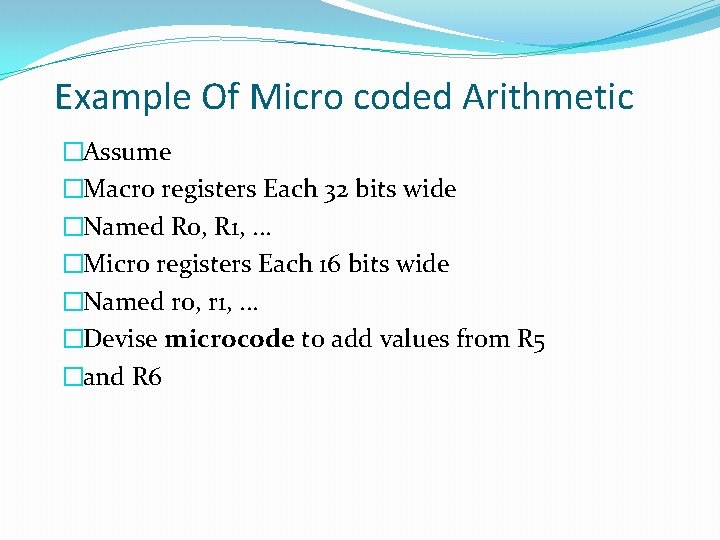

Example Of Micro coded Arithmetic �Assume �Macro registers Each 32 bits wide �Named R 0, R 1, . . . �Micro registers Each 16 bits wide �Named r 0, r 1, . . . �Devise microcode to add values from R 5 �and R 6

From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. © 2005 Pearson Education, Inc. All rights

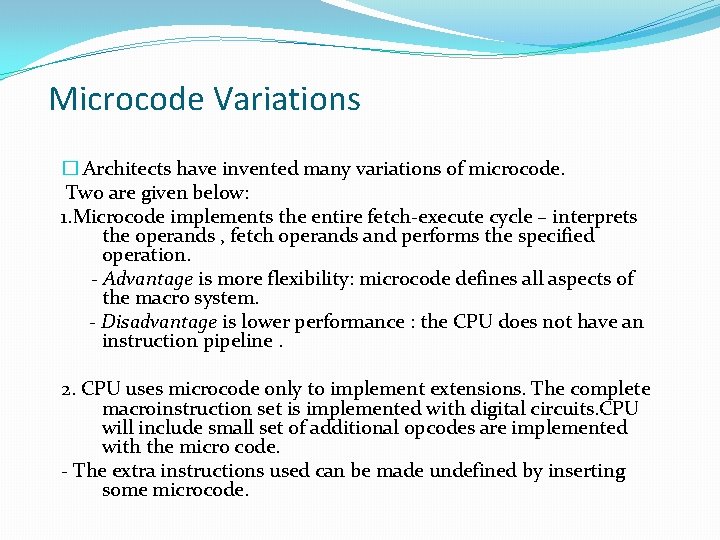

Microcode Variations � Architects have invented many variations of microcode. Two are given below: 1. Microcode implements the entire fetch-execute cycle – interprets the operands , fetch operands and performs the specified operation. - Advantage is more flexibility: microcode defines all aspects of the macro system. - Disadvantage is lower performance : the CPU does not have an instruction pipeline. 2. CPU uses microcode only to implement extensions. The complete macroinstruction set is implemented with digital circuits. CPU will include small set of additional opcodes are implemented with the micro code. - The extra instructions used can be made undefined by inserting some microcode.

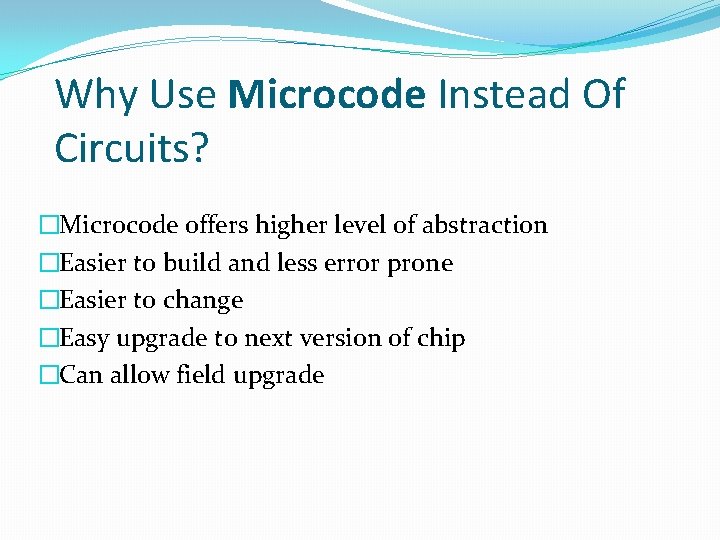

Why Use Microcode Instead Of Circuits? �Microcode offers higher level of abstraction �Easier to build and less error prone �Easier to change �Easy upgrade to next version of chip �Can allow field upgrade

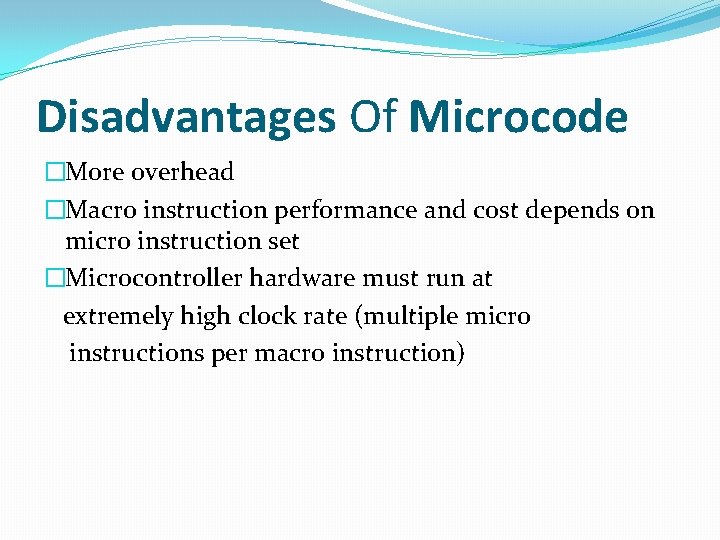

Disadvantages Of Microcode �More overhead �Macro instruction performance and cost depends on micro instruction set �Microcontroller hardware must run at extremely high clock rate (multiple micro instructions per macro instruction)

Visibility To Programmers Fixed microcode �Approach used by most CPUs �Microcode only visible to CPU designer Alterable microcode �May be restricted to extensions (creating new macro instructions) �User software written to use new instructions �Known as reconfigurable CPU

Reconfigurable CPU �Some CPUs provide a mechanism that allows microcode to be rewritten. � The motivation for allowing such change arises from the desire for flexibility and optimization. �The CPU's owner can create a macro instruction set that is optimized for a specific task.

In Practice �Writing microcode is tedious and time- consuming �Results are difficult to test �Microcode seldom gives performance equal to discrete hardware �Result: reconfigurable CPUs have not enjoyed much success

Two Fundamental Types of Microcode �What programming paradigm is used for microcode? �Two fundamental types -Vertical -Horizontal

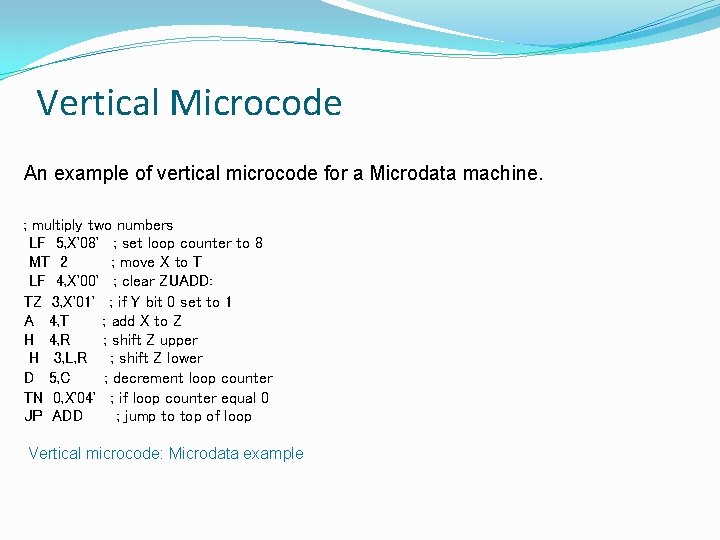

Vertical Microcode �A vertical microinstruction is highly encoded and looks like a simple macroinstruction; it might contain a single opcode field and one or two operand specifiers. �Vertical microcode similar to conventional assembly language �Typically performs one operation at a time �Has access to all facilities macro instruction set uses -ALU -General-purpose registers -Memory -I/O buses

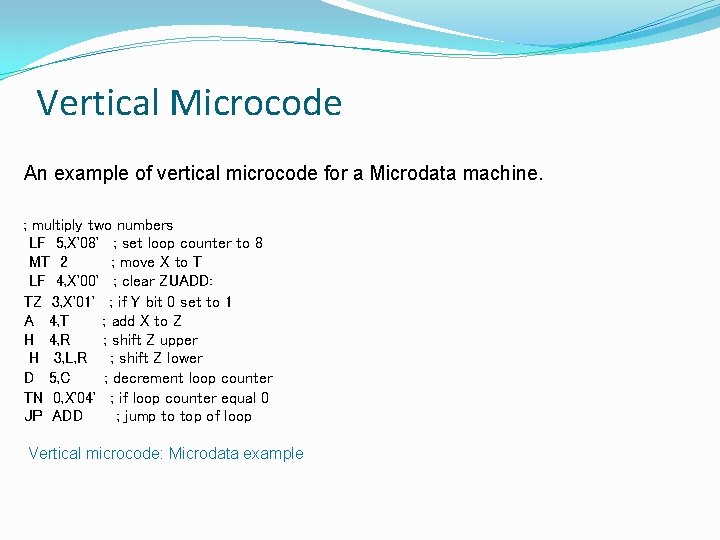

Vertical Microcode An example of vertical microcode for a Microdata machine. ; multiply two numbers LF 5, X'08' ; set loop counter to 8 MT 2 ; move X to T LF 4, X'00' ; clear ZUADD: TZ 3, X'01' ; if Y bit 0 set to 1 A 4, T ; add X to Z H 4, R ; shift Z upper H 3, L, R ; shift Z lower D 5, C ; decrement loop counter TN 0, X'04' ; if loop counter equal 0 JP ADD ; jump to top of loop Vertical microcode: Microdata example

Example of Vertical Microcode �Micro controller used in CISC processor consists of a fast RISC processor. �Programmer writes microcode for each macro instruction �Hardware decodes macro instruction and invokes correct microcode routine

Advantages And Disadvantages Of Vertical Microcode �Easy to read �Programmers are comfortable using it �Unattractive to hardware designers because higher clock rates needed �Generally has low performance (multiple micro instructions needed for one macro �instruction)

Horizontal Microcode �Alternative to vertical microcode �Exploits parallelism in underlying hardware �Controls functional units and data movement �Difficult to program

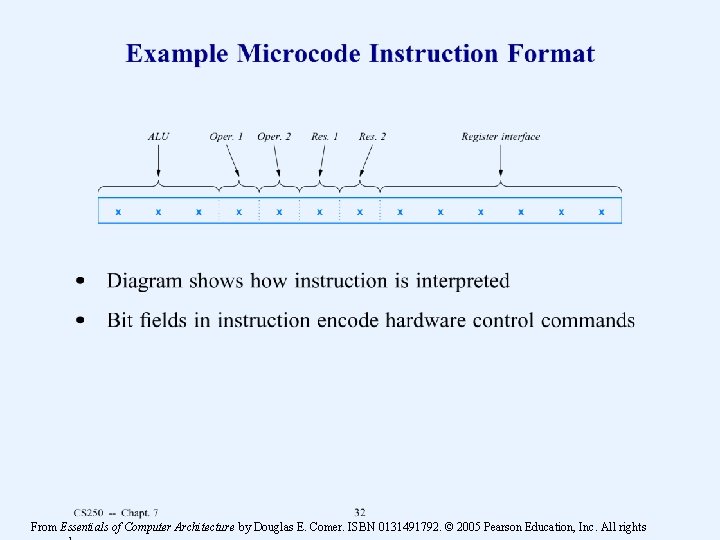

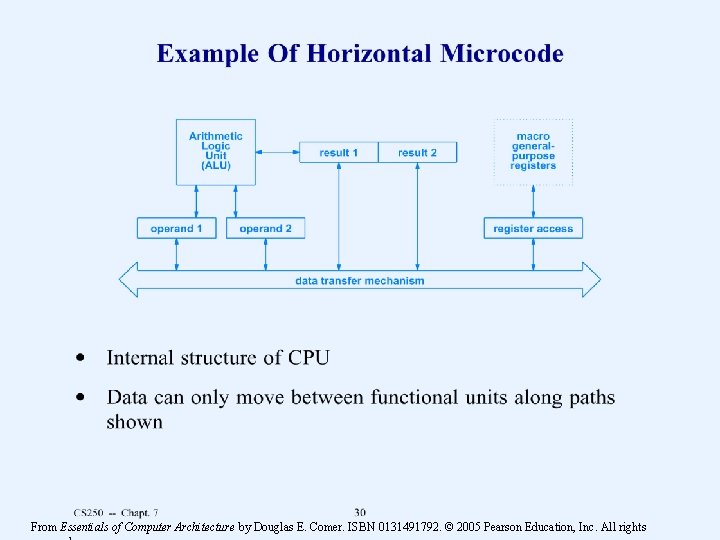

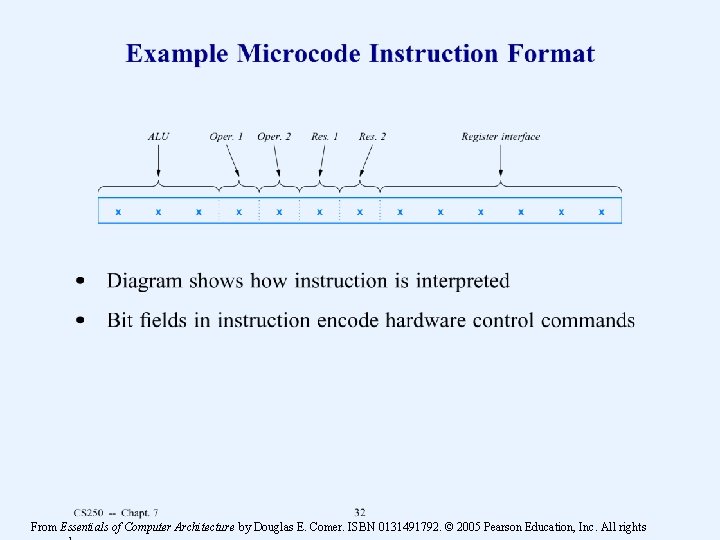

The Important Point About Horizontal Microcode �Horizontal microcode allows the hardware to run faster, but is more difficult to program. �Each instruction controls a set of hardware units �Instruction specifies the Transfer of data Which hardware units operate

From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. © 2005 Pearson Education, Inc. All rights

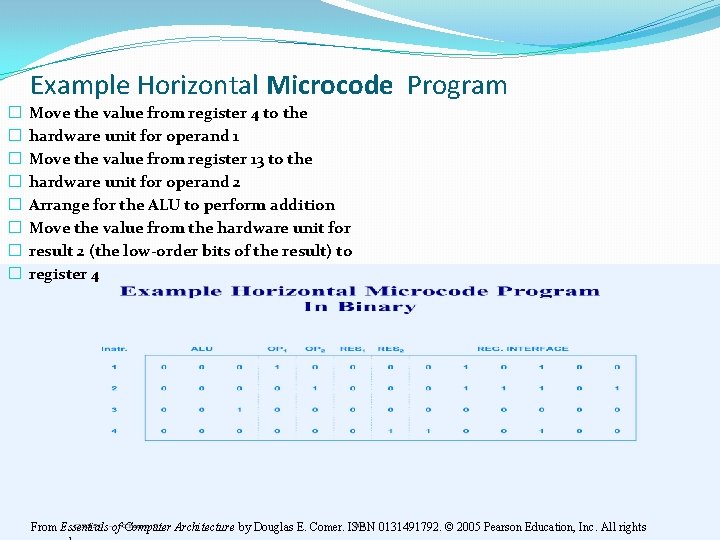

From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. © 2005 Pearson Education, Inc. All rights

From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. © 2005 Pearson Education, Inc. All rights

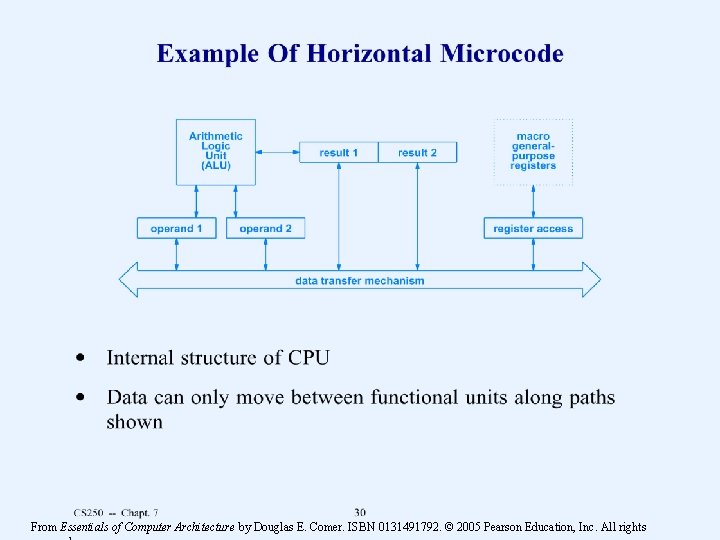

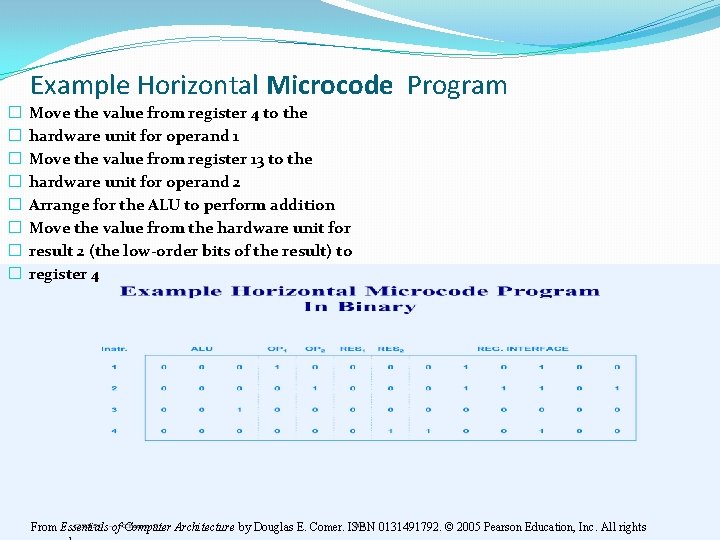

Example Horizontal Microcode Program � � � � Move the value from register 4 to the hardware unit for operand 1 Move the value from register 13 to the hardware unit for operand 2 Arrange for the ALU to perform addition Move the value from the hardware unit for result 2 (the low-order bits of the result) to register 4 From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. © 2005 Pearson Education, Inc. All rights

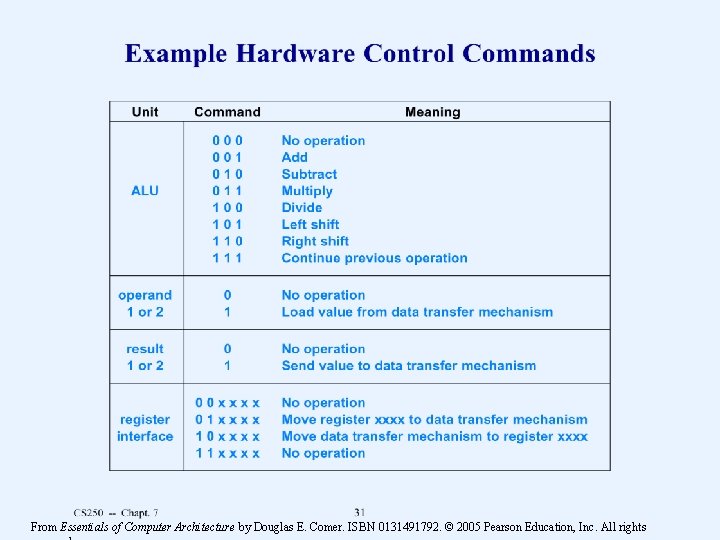

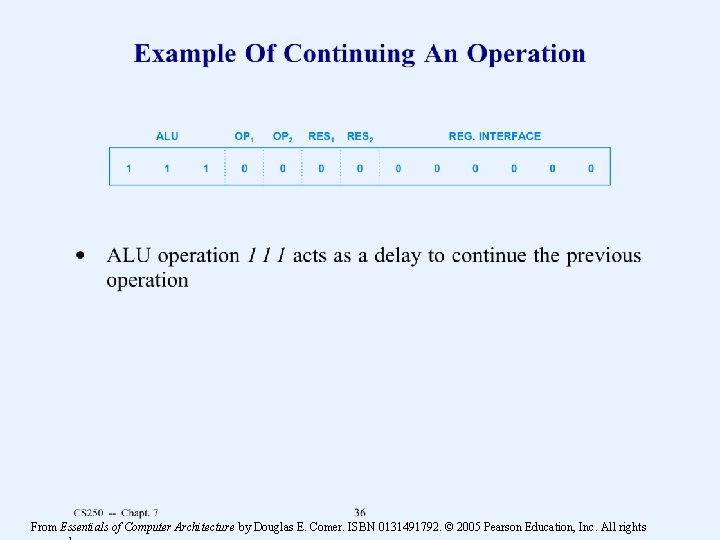

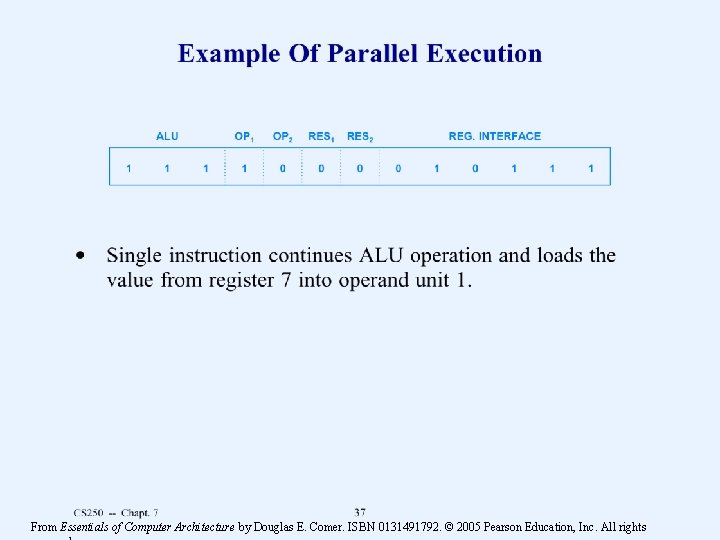

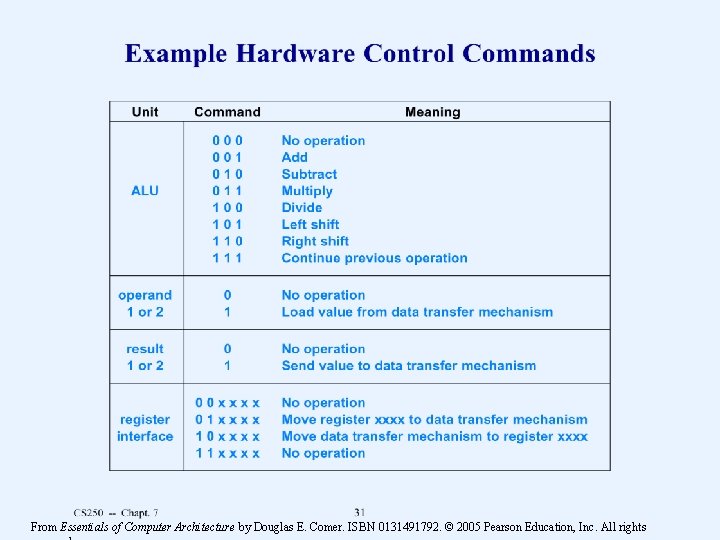

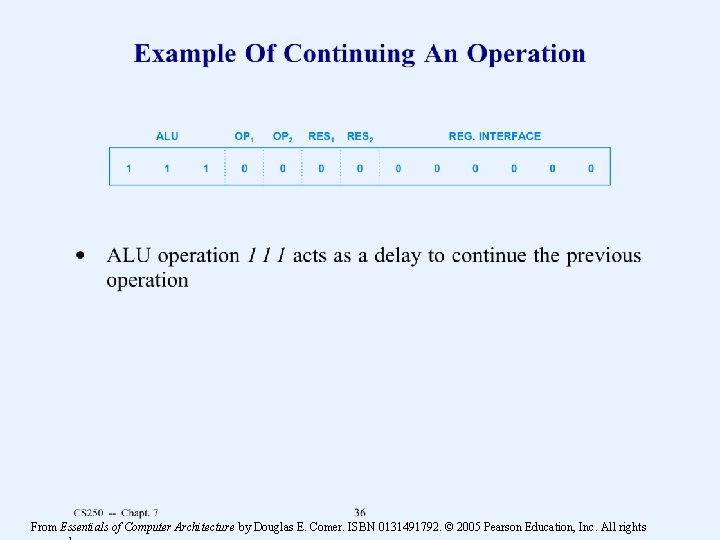

Horizontal Microcode And Timing �Each microcode instruction takes one cycle �Functional unit may require more than one cycle to complete an operation �Programmer must accommodate hardware timing or errors can result �To wait for functional unit, insert microcode instructions that continue the operation, from the table given above 111 is the code to denote that the ALU is continuing the previous operation.

From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. © 2005 Pearson Education, Inc. All rights

From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. © 2005 Pearson Education, Inc. All rights

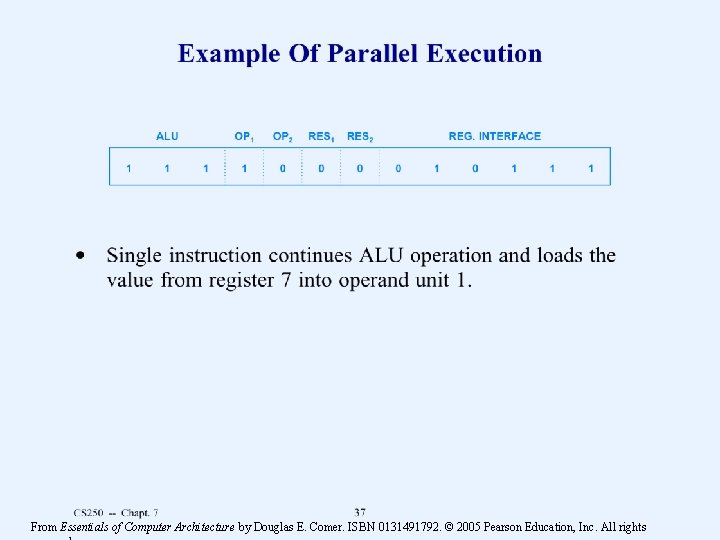

Horizontal Microcode And Parallel Execution �Because an instruction contains separate fields that each correspond to one hardware unit, horizontal �microcode makes it easy to specify simultaneous, parallel operation of multiple hardware units

Intelligent Microcontroller �Schedules instructions by assigning work to functional units �Handles operations in parallel. �Ex: Add R 1, R 3, R 7 Sub R 4, R 6 Add R 9, R 1, R 2 Shift R 12, 5 �If the CPU contains enough functional units, the controller can schedule all four macro instructions to be executed at the same time.

Parallelism And Execution Order �The controller must ensure that computing values in parallel does not change the meaning of the program. �The operands overlap: R 7 is the destination in Instruction 1 and operand in instruction 3. Ex: div R 1, R 3, R 7 sub R 4, R 6 add R 7, R 1, R 2 shift R 12, 5 �An intelligent controller must accommodate overlap. �It must balance between two goals: maximize the amount of parallel evaluation, while preserving the original(sequential) semantics

How can a controller schedule parallel activities and handle the overlap �The answer lies in a mechanism called the SCOREBOARD. �This mechanism maintains information about dependencies among instructions and the original macro instruction sequence execution. �Thus helps the controller to know when to fetch the operands, when to execute etc. �It uses the concept of Out-of-order processing. �Then reorders the results to reflect the order of specified by the code.

The Important Concept of Branch Prediction A CPU that offers parallel instruction execution can handle conditional branches by precomputing values on one or both branches and choosing which values to use at a later time when the computation of the branch condition completes

Summary �CPU offers modes of execution that determine protection and privilege �Complex CPU usually implemented with microcode �Vertical microcode uses conventional instruction set �Horizontal microcode uses unconventional instructions