CPU Structure z CPU must y Fetch instructions

- Slides: 25

CPU Structure z CPU must: y. Fetch instructions: The processor reads an instruction from memory. y. Interpret instructions: The instruction is decoded to determine what action is required. y. Fetch data: Reading data from memory or I/O. y. Process data: Performing required arithmetic or logical operations on data. y. Write data: writing data to memory or I/O. 1

Registers z CPU must have some working space (temporary storage) Called registers. z Number and function vary between processor designs z One of the major design decisions z Top level of memory hierarchy z Categories: x. General Purpose x. Data x. Address x. Condition Codes 2

General Purpose Registers (1) z May be true general purpose z May be restricted z May be used for data or addressing z Data y. Accumulator z Addressing y. Segment 3

General Purpose Registers (2) z Make them general purpose y. Increase flexibility and programmer options y. Increase instruction size & complexity z Make them specialized y. Smaller (faster) instructions y. Less flexibility z Between 8 – 32 registers. z Fewer = more memory references z More does not reduce memory references 4

How big? z Large enough to hold full address z Large enough to hold full word z Often possible to combine two data registers y. C programming ydouble int a; ylong int a; 5

Condition Code Registers z Sets of individual bits ye. g. result of last operation was zero z Can be read (implicitly) by programs ye. g. Jump if zero z Can not (usually) be set by programs 6

Control & Status Registers z Program Counter: contains address of an instruction to be fetched. z Instruction Decoding Register: contains the instruction most recently fetched. z Memory Address Register: contains the address of a location in memory. z Memory Buffer Register: contains a word of data to be written to memory or the word most recently read. 7

What is an “Architecture”? z When we refer to “Architecture, ” we often use it as an abbreviation for an instruction set architecture (ISA). z The ISA is the interface between hardware and software. z The architecture is a specification for what the processor will do, and how the software must communicate to the processor. z Note that the “architecture” states only what will be done, but not how. 8

RISC z The design goals and principles behind reduced instruction set computers (RISC) are: y Smaller is faster y Simplicity favors regularity y Make the common case fast z Regularity will basically apply to instruction sizes and instruction formats. z RISC architectures have a fewer number of simple instructions than complex instruction set computer (CISC) architectures. z Access to memory using Load and Store command only. 9

MIPS z MIPS is a common RISC ISA. MIPS processors are in extensive use by NEC, Nintendo, Cisco, SGI, Sony, etc. z MIPS has 32 integer registers. z It uses only a limited number of addressing modes. z MIPS has a fairly regular instruction encoding. All instructions are 32 bits long (4 bytes), and there are only three instruction formats 10

MIPS Arithmetic Instructions z MIPS arithmetic instructions have three operands: add a, b, c This instruction takes the sum of registers b and c and puts the answer into register a. It is equivalent to the C code: a = b + c; z What if we want to code the following? a = b + c + d; z We need to do it in two steps: add a, b, c add a, a, d z Note that multiple operands may refer to the same register 11

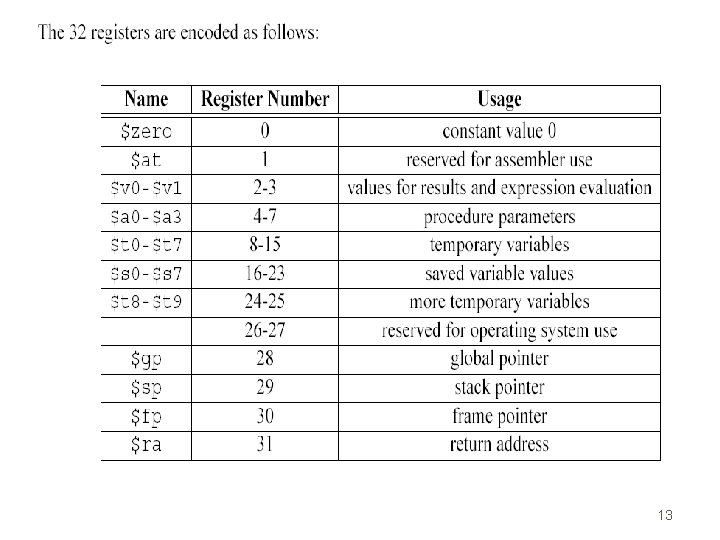

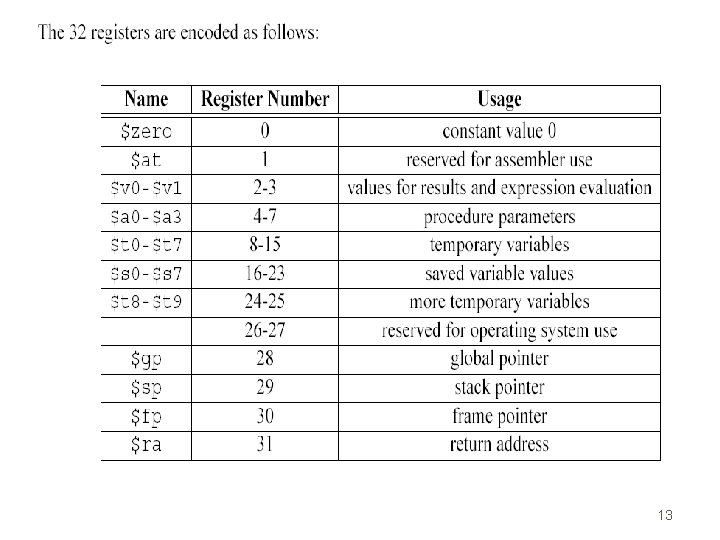

MIPS Registers and Memory z In MIPS, the operands must be registers. z 32 registers are provided each register stores a 32 -bit value. The compilers associate variables with registers z registers are referred to by names such as $s 0 and $t 1 z we use the “s” registers for values that correspond to variables in our programs, and we use the “t” registers for temporary values (more on this later) 12

13

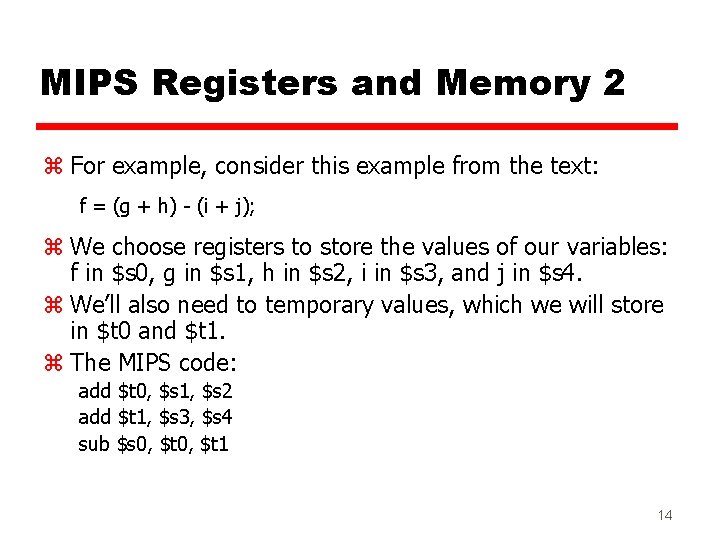

MIPS Registers and Memory 2 z For example, consider this example from the text: f = (g + h) - (i + j); z We choose registers to store the values of our variables: f in $s 0, g in $s 1, h in $s 2, i in $s 3, and j in $s 4. z We’ll also need to temporary values, which we will store in $t 0 and $t 1. z The MIPS code: add $t 0, $s 1, $s 2 add $t 1, $s 3, $s 4 sub $s 0, $t 1 14

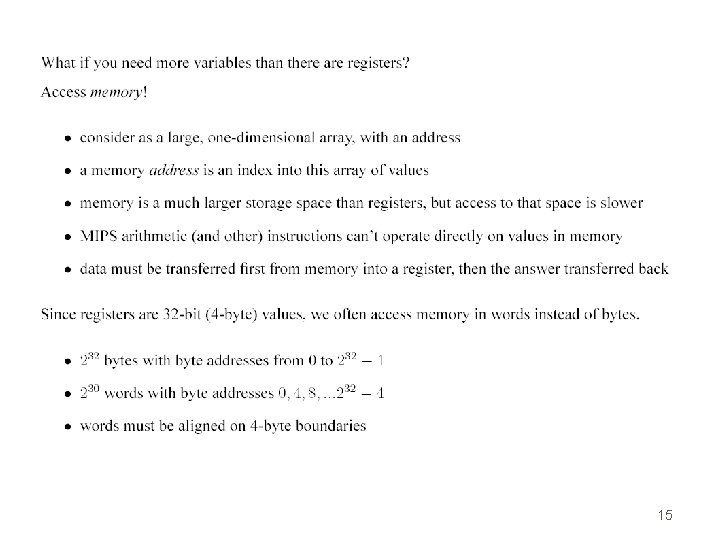

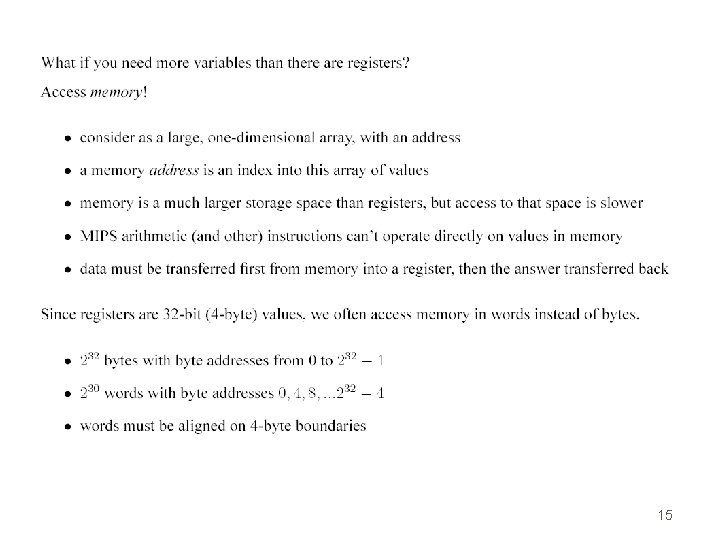

15

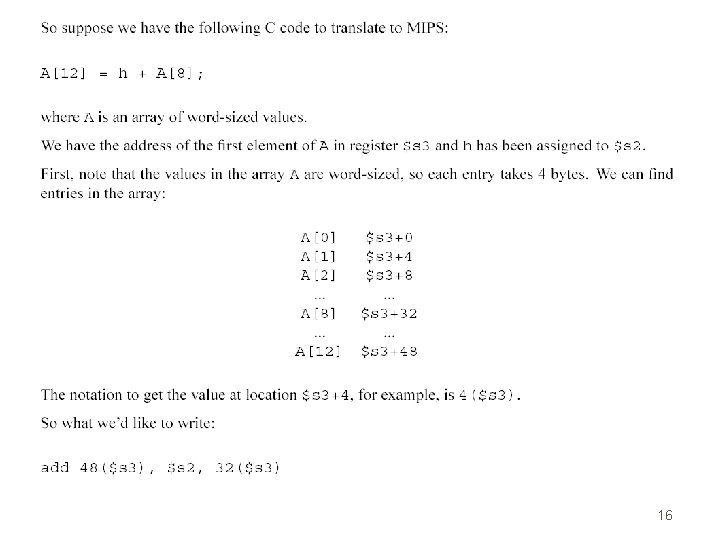

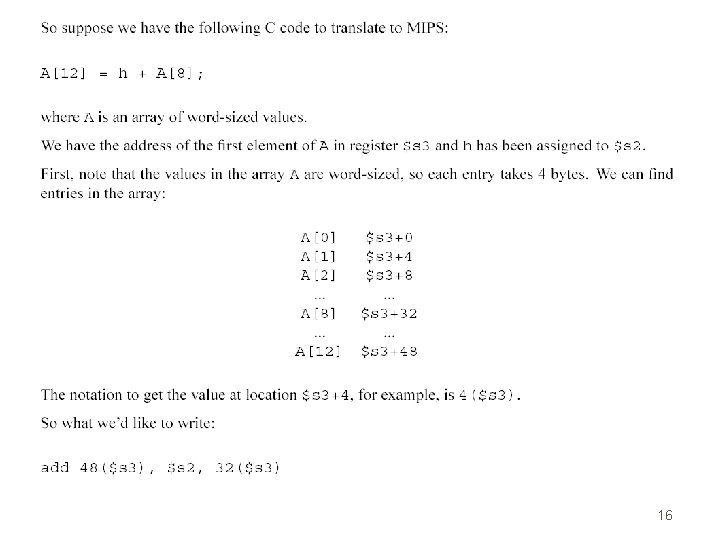

16

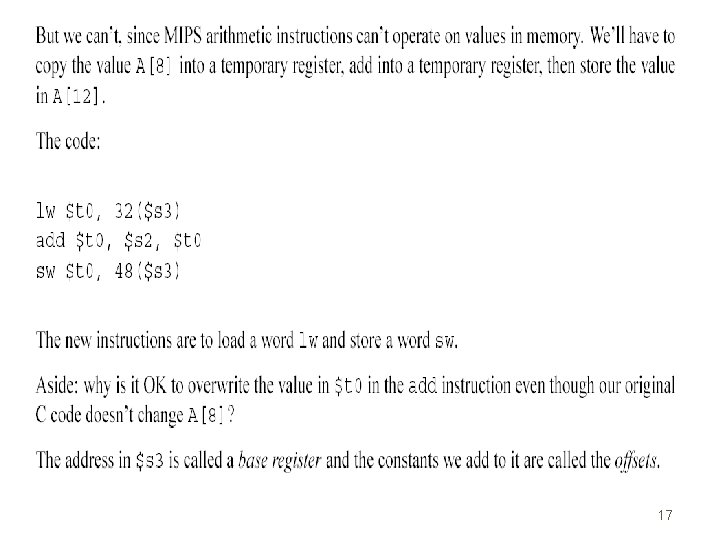

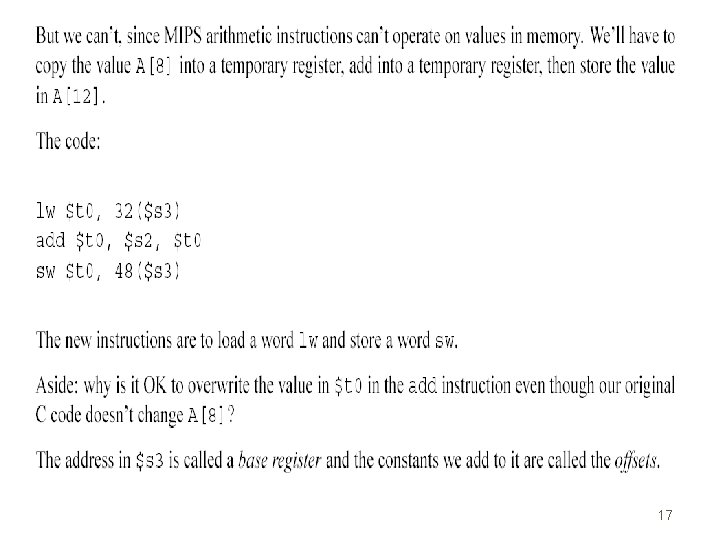

17

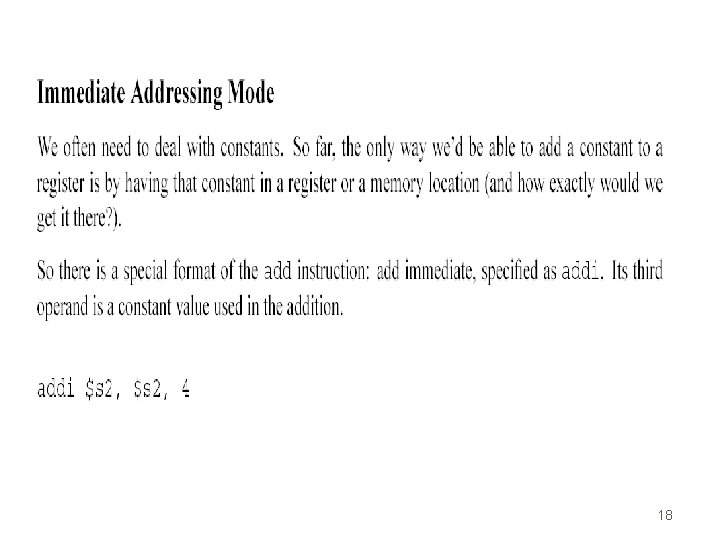

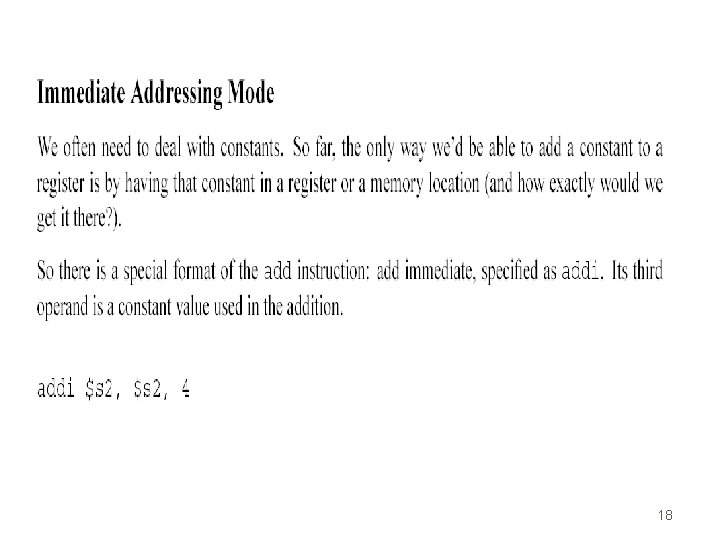

18

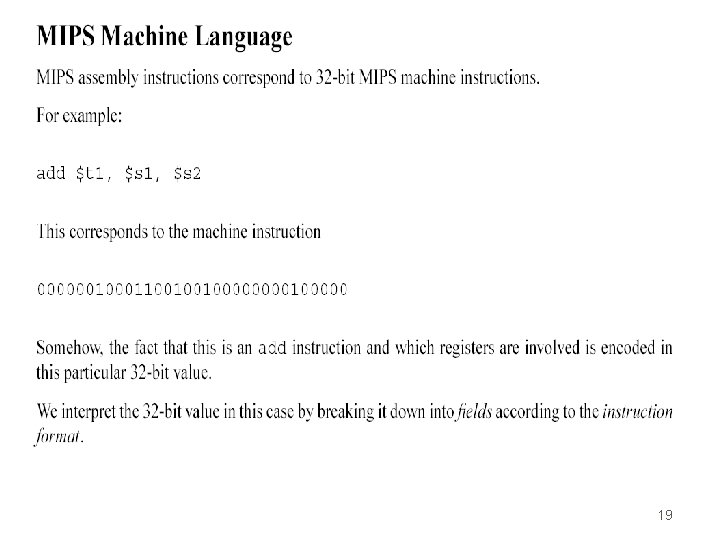

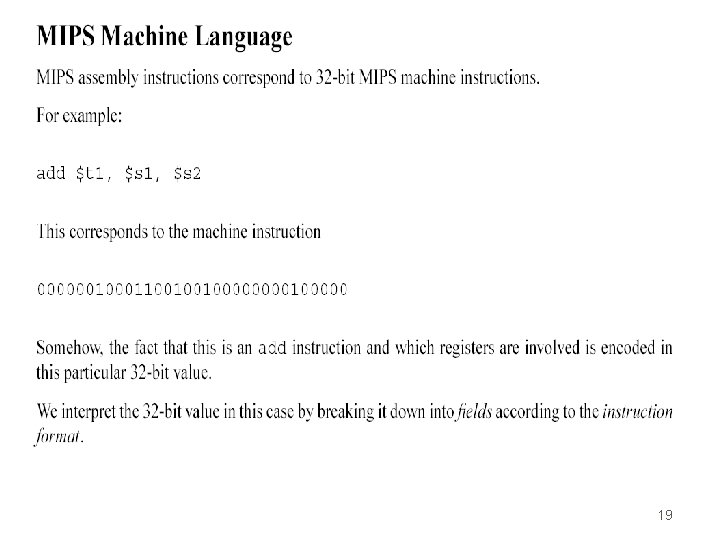

19

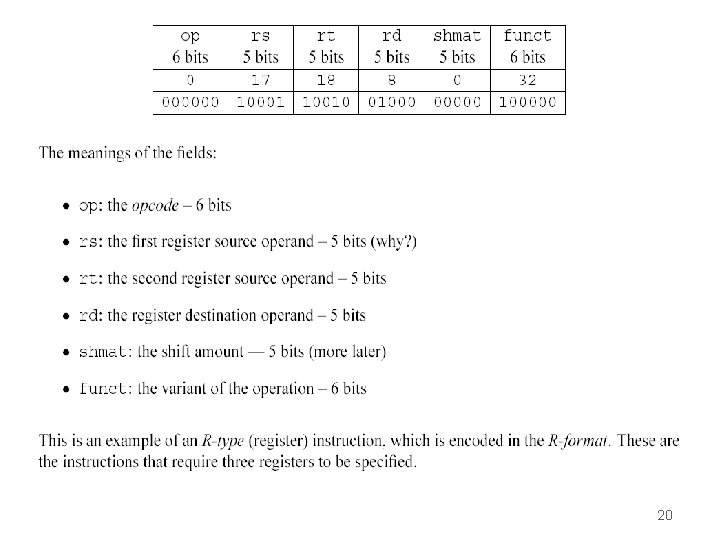

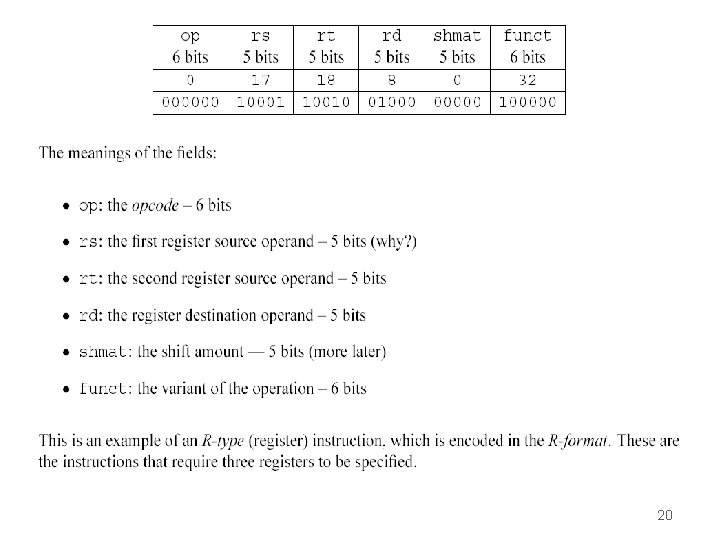

20

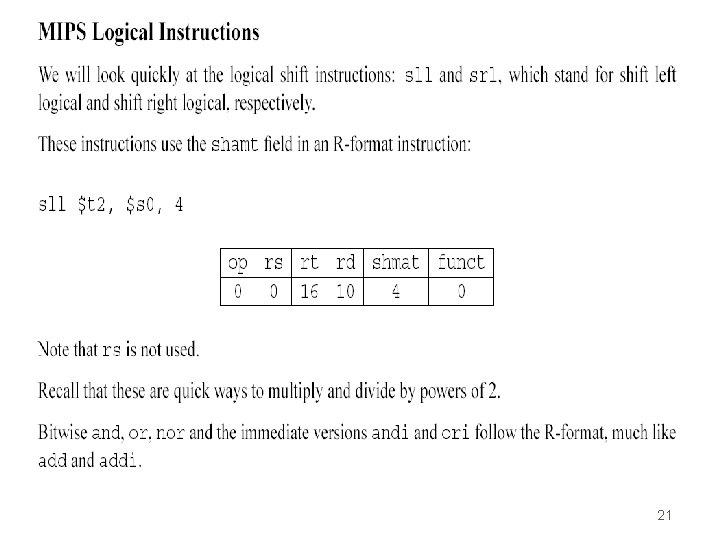

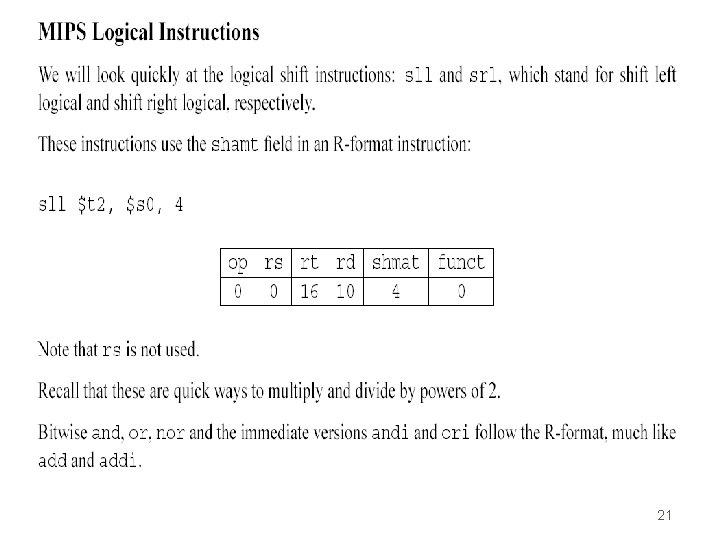

21

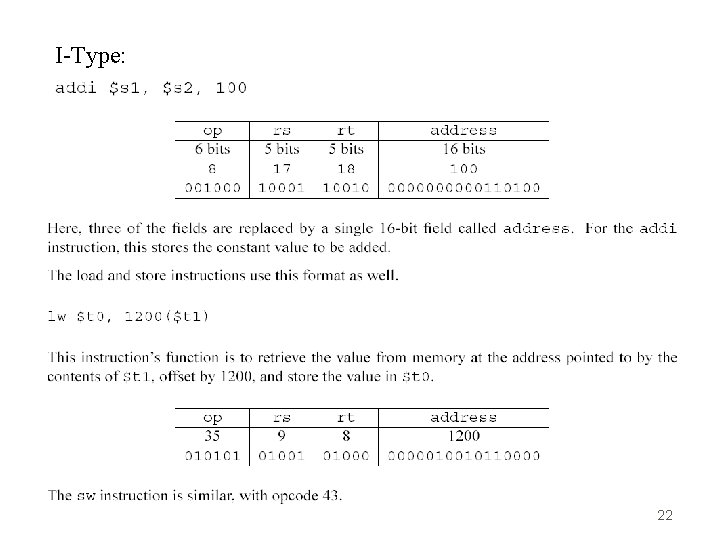

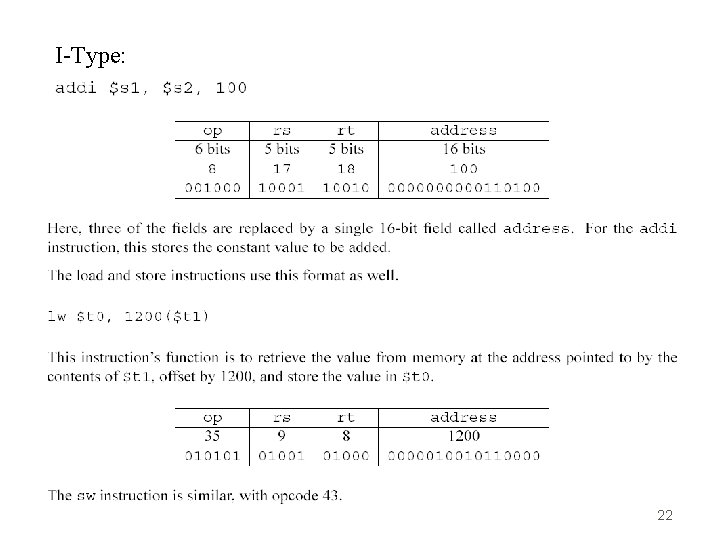

I-Type: 22

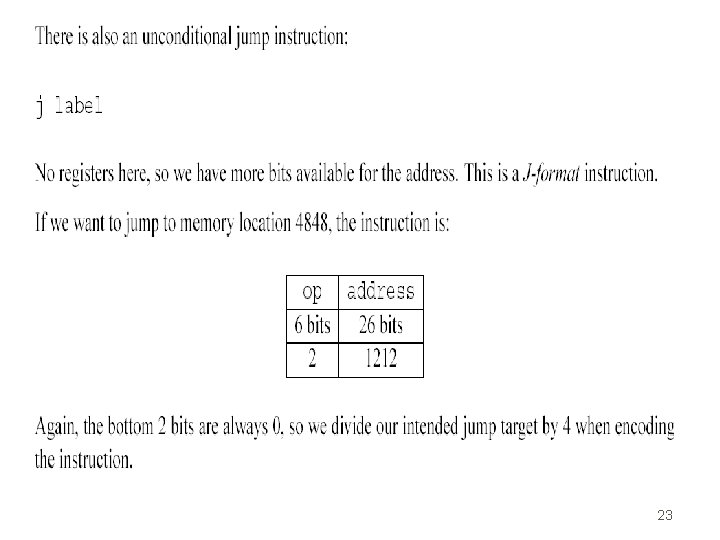

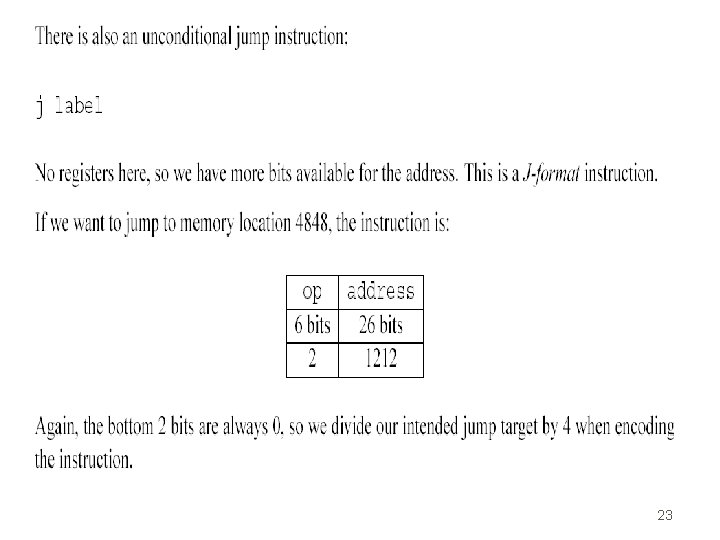

23

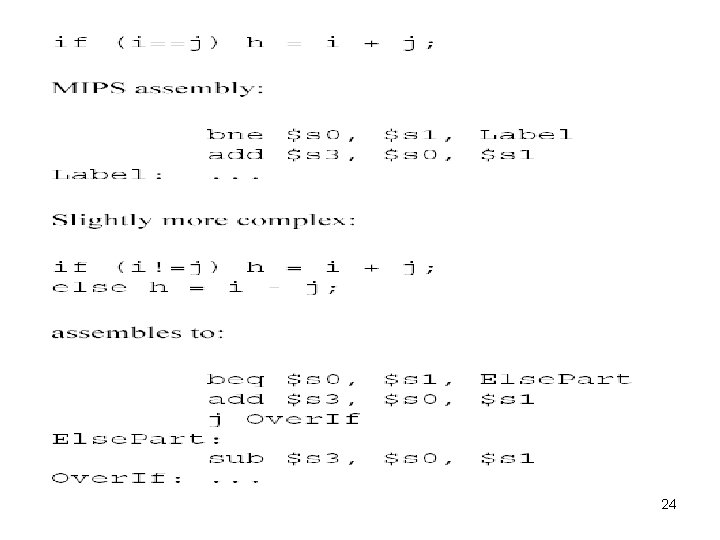

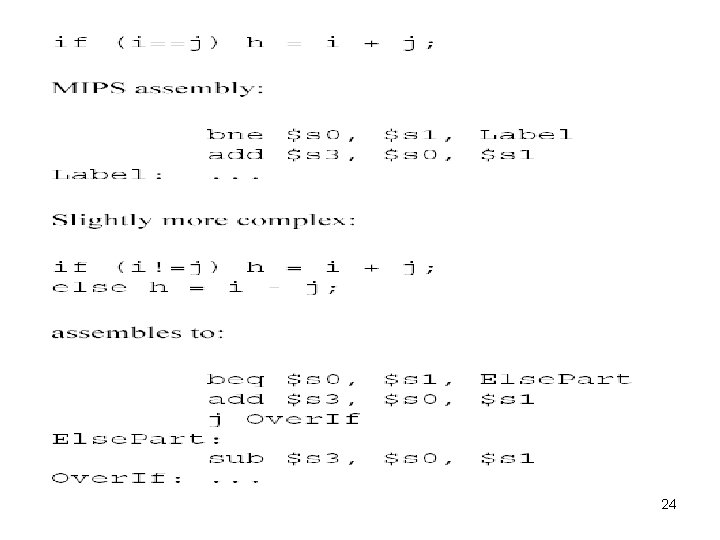

24

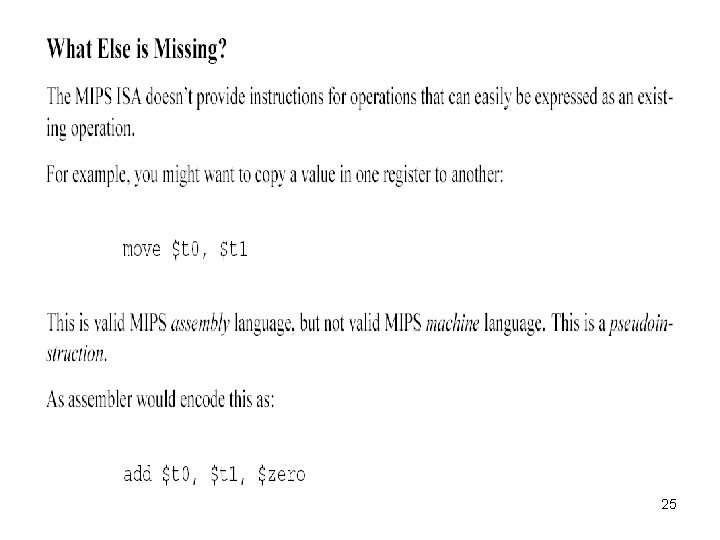

25