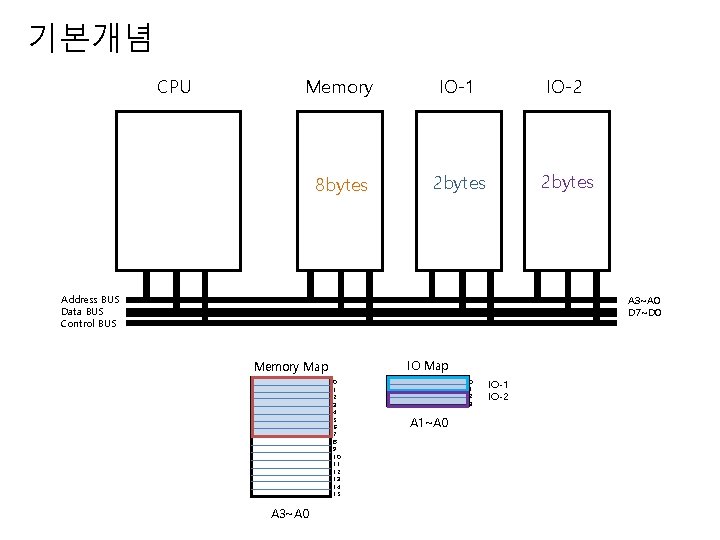

CPU Memory IO1 IO2 8 bytes 2 bytes

기본개념 CPU Memory IO-1 IO-2 8 bytes 2 bytes Address BUS Data BUS Control BUS A 3~A 0 D 7~D 0 IO Map Memory Map 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 A 3~A 0 0 1 2 3 A 1~A 0 IO-1 IO-2

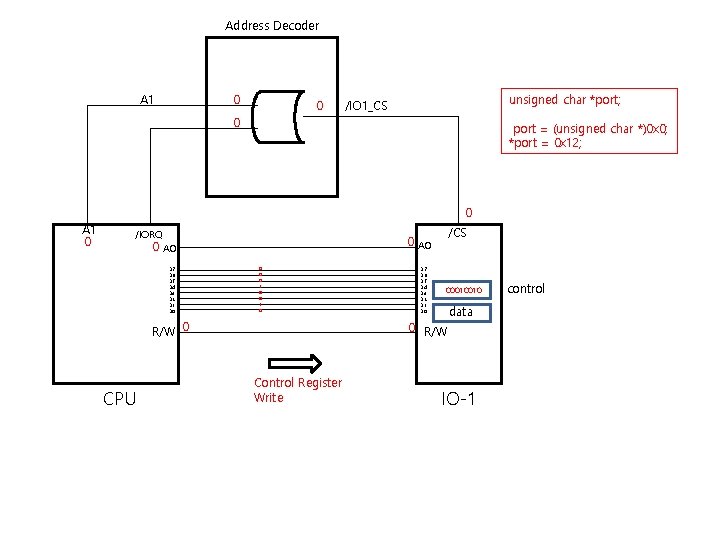

Address Decoder A 1 0 0 unsigned char *port; /IO 1_CS 0 port = (unsigned char *)0 x 0; *port = 0 x 12; 0 A 1 0 /IORQ D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 0 1 0 R/W 0 CPU /CS 0 A 0 D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 00010010 0 R/W Control Register Write data IO-1 control

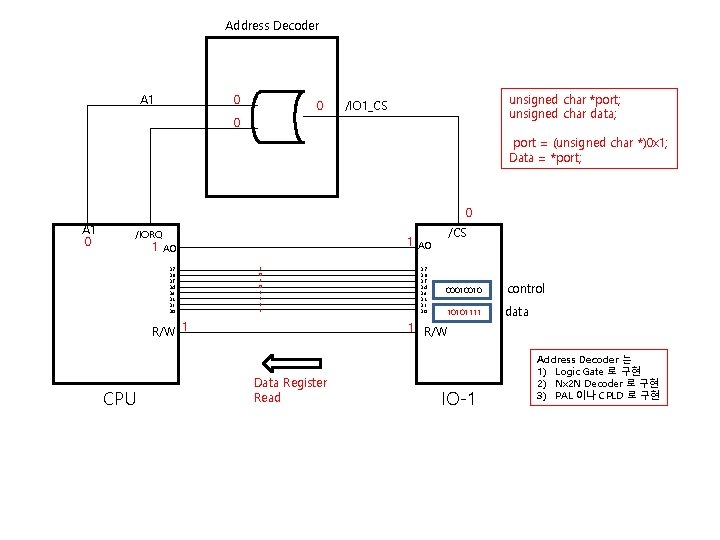

Address Decoder A 1 0 0 unsigned char *port; unsigned char data; /IO 1_CS 0 port = (unsigned char *)0 x 1; Data = *port; 0 A 1 0 /IORQ D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 1 0 1 1 R/W 1 CPU /CS 1 A 0 D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 00010010 control 10101111 data 1 R/W Data Register Read IO-1 Address Decoder 는 1) Logic Gate 로 구현 2) Nx 2 N Decoder 로 구현 3) PAL 이나 CPLD 로 구현

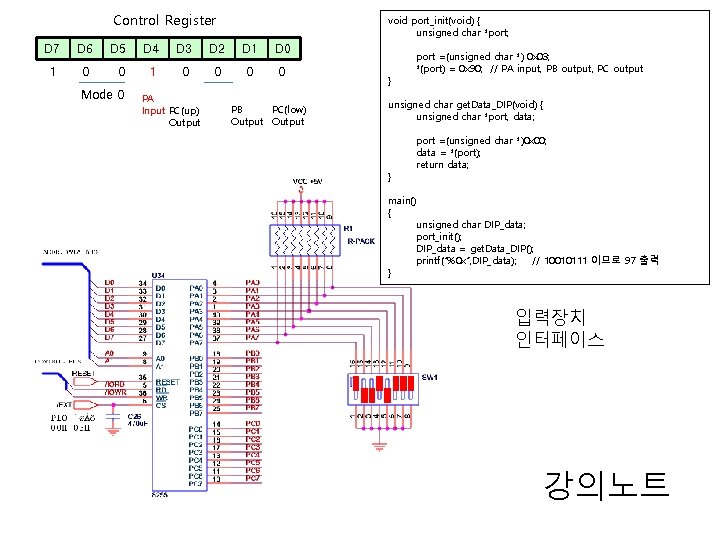

Control Register void port_init(void) { unsigned char *port; D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 1 0 0 0 0 Mode 0 PA Input PC(up) Output PB PC(low) Output } port =(unsigned char *) 0 x 03; *(port) = 0 x 90; // PA input, PB output, PC output unsigned char get. Data_DIP(void) { unsigned char *port, data; } port =(unsigned char *)0 x 00; data = *(port); return data; main() { unsigned char DIP_data; port_init(); DIP_data = get. Data_DIP(); printf(“%0 x”, DIP_data); // 10010111 이므로 97 출력 } 입력장치 인터페이스 강의노트

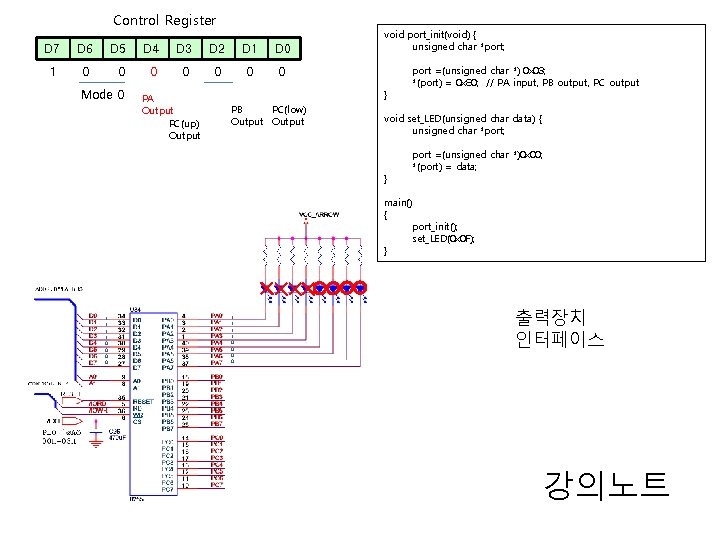

Control Register D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 1 0 0 0 0 Mode 0 PA Output PC(up) Output void port_init(void) { unsigned char *port; } PB PC(low) Output port =(unsigned char *) 0 x 03; *(port) = 0 x 80; // PA input, PB output, PC output void set_LED(unsigned char data) { unsigned char *port; } port =(unsigned char *)0 x 00; *(port) = data; main() { port_init(); set_LED(0 x 0 F); } 1 1 1 1 0 0 0 0 출력장치 인터페이스 강의노트

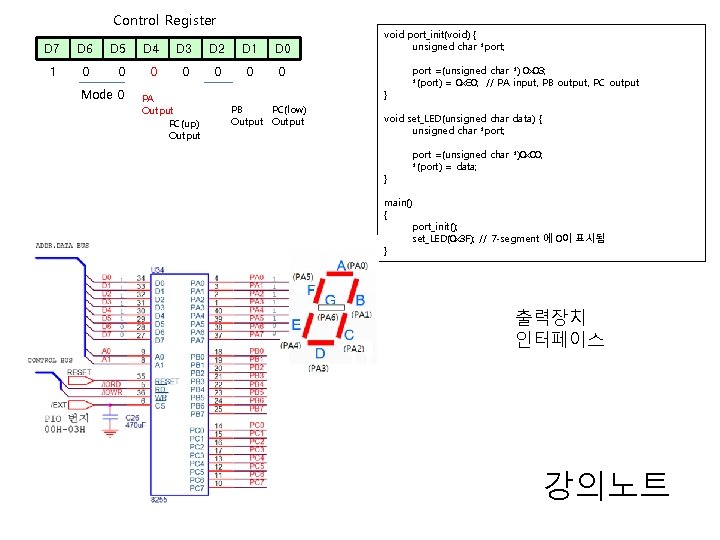

Control Register D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 1 0 0 0 0 Mode 0 PA Output PC(up) Output void port_init(void) { unsigned char *port; } PB PC(low) Output port =(unsigned char *) 0 x 03; *(port) = 0 x 80; // PA input, PB output, PC output void set_LED(unsigned char data) { unsigned char *port; } port =(unsigned char *)0 x 00; *(port) = data; main() { port_init(); set_LED(0 x 3 F); // 7 -segment 에 0이 표시됨 } 출력장치 인터페이스 강의노트

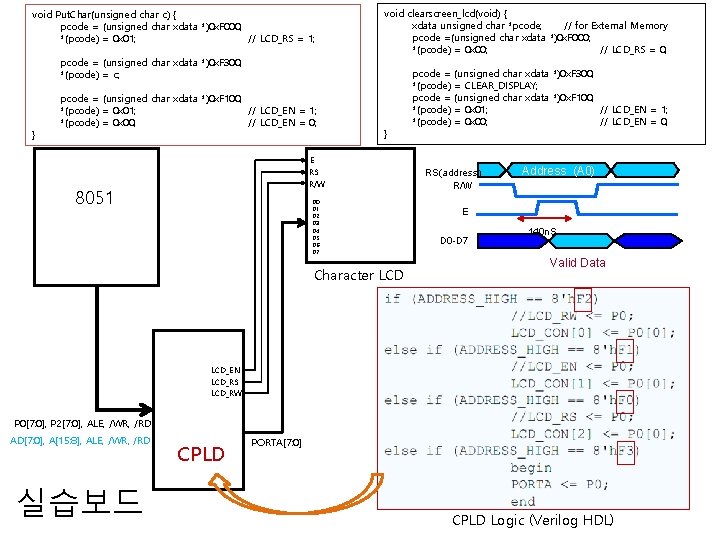

void Put. Char(unsigned char c) { pcode = (unsigned char xdata *)0 x. F 000; *(pcode) = 0 x 01; // LCD_RS = 1; pcode = (unsigned char xdata *)0 x. F 300; *(pcode) = c; } pcode = (unsigned char xdata *)0 x. F 100; *(pcode) = 0 x 01; // LCD_EN = 1; *(pcode) = 0 x 00; // LCD_EN = 0; void clearscreen_lcd(void) { xdata unsigned char *pcode; // for External Memory pcode =(unsigned char xdata *)0 x. F 000; *(pcode) = 0 x 00; // LCD_RS = 0; } E RS R/W 8051 D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 Character LCD pcode = *(pcode) (unsigned char xdata *)0 x. F 300; = CLEAR_DISPLAY; (unsigned char xdata *)0 x. F 100; = 0 x 01; // LCD_EN = 1; = 0 x 00; // LCD_EN = 0; RS(address) R/W Address (A 0) E D 0 -D 7 140 n. S Valid Data LCD_EN LCD_RS LCD_RW P 0[7: 0], P 2[7: 0], ALE, /WR, /RD AD[7: 0], A[15: 8], ALE, /WR, /RD 실습보드 CPLD PORTA[7: 0] CPLD Logic (Verilog HDL)

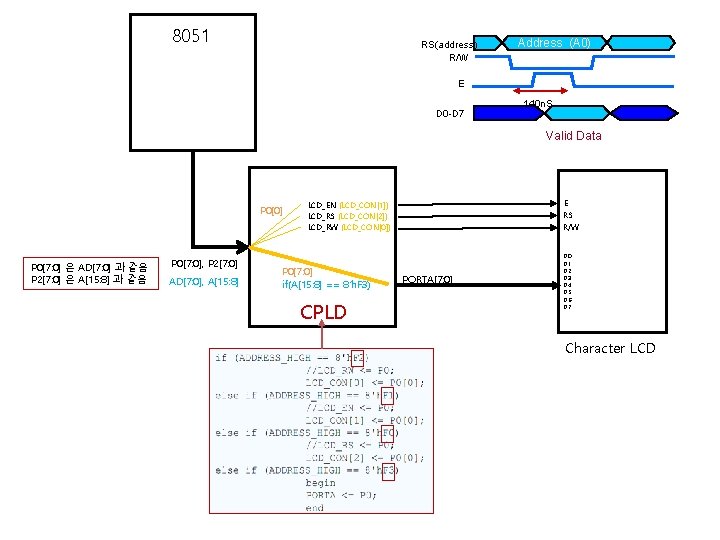

8051 RS(address) R/W Address (A 0) E D 0 -D 7 140 n. S Valid Data P 0[0] P 0[7: 0] 은 AD[7: 0] 과 같음 P 2[7: 0] 은 A[15: 8] 과 같음 P 0[7: 0], P 2[7: 0] AD[7: 0], A[15: 8] E RS R/W LCD_EN (LCD_CON[1]) LCD_RS (LCD_CON[2]) LCD_RW (LCD_CON[0]) P 0[7: 0] if(A[15: 8] == 8’h. F 3) CPLD PORTA[7: 0] D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 Character LCD

- Slides: 8