CPU DesignProject Multicycle Datapath with Finite State Machine

![Core Instruction set: Name Mnemic Format Operation Opcode Add add R R[rd] = R[rs] Core Instruction set: Name Mnemic Format Operation Opcode Add add R R[rd] = R[rs]](https://slidetodoc.com/presentation_image/24c0c21a4010906bd41f51d7e1939d08/image-2.jpg)

- Slides: 10

CPU Design-Project { Multicycle Datapath with Finite State Machine as Control Unit N. S. V Ravi Tej Uppu

![Core Instruction set Name Mnemic Format Operation Opcode Add add R Rrd Rrs Core Instruction set: Name Mnemic Format Operation Opcode Add add R R[rd] = R[rs]](https://slidetodoc.com/presentation_image/24c0c21a4010906bd41f51d7e1939d08/image-2.jpg)

Core Instruction set: Name Mnemic Format Operation Opcode Add add R R[rd] = R[rs] + R[rt] 0000 And and R R[rd] = R[rs] & R[rt] 0001 Or or R R[rd] = R[rs] | R[rt] 0010 Subtract sub R R[rd] = R[rs] - R[rt] 0011 Not not R R[rd] = nt[ R[rs] | $0] 0100 Xor xor R R[rd] = R[rs] xor R[rt] 0101 Load word lw I R[rt]=M(R[rs]+sign. Ext. Imm) 0110 Store word sw I M(R[rs]+sign. Ext. Imm)=R[rt] 0111 Add Imm addi I R[rt] = R[rs] + sign. Ext. Imm 1000 And Imm andi I R[rt] = R[rs] & sign. Ext. Imm 1001 Or Imm ori I R[rt] = R[rs] | sign. Ext. Imm 1010 Branch on equal beq I if R[rs]==R[rt], PC=PC+4+brn add 1011 Halt hlt J PC = PC - 1 1100 Jump j J PC = jump address 1101 Set on less than slt R R[rd] = (R[rs]<R[rt]) ? 1 : 0 1110 Jump and link jal I R[15]=PC+4; PC = jump address 1111

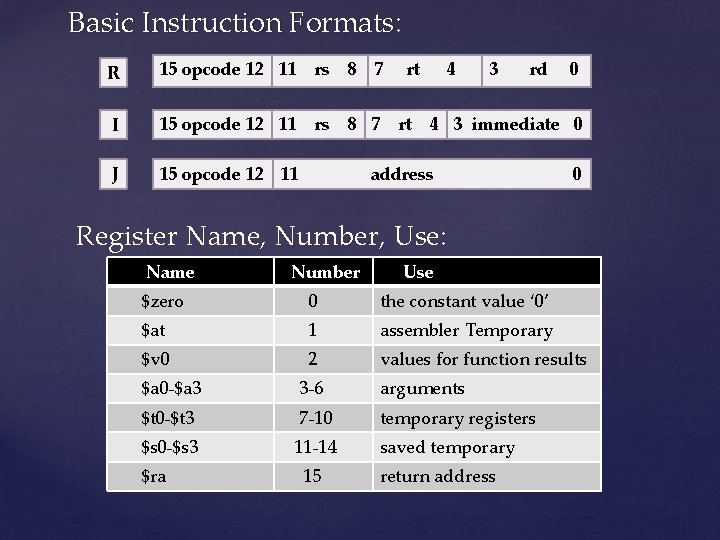

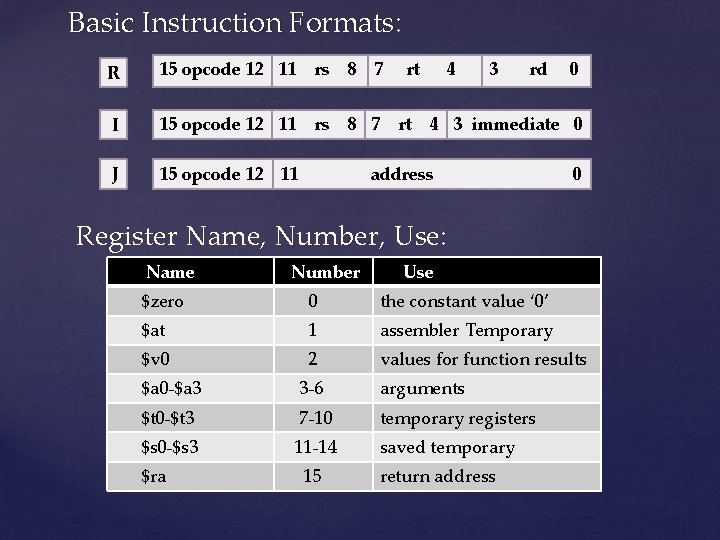

Basic Instruction Formats: R 15 opcode 12 11 rs 8 7 I 15 opcode 12 11 rs 8 7 J 15 opcode 12 11 rt 4 3 rd 0 rt 4 3 immediate 0 address 0 Register Name, Number, Use: Name Number Use $zero 0 the constant value ‘ 0’ $at 1 assembler Temporary $v 0 2 values for function results $a 0 -$a 3 3 -6 arguments $t 0 -$t 3 7 -10 temporary registers $s 0 -$s 3 11 -14 saved temporary $ra 15 return address

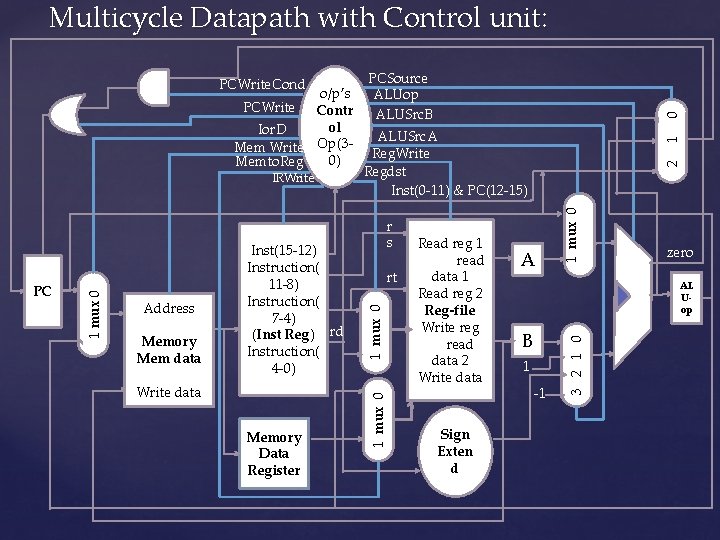

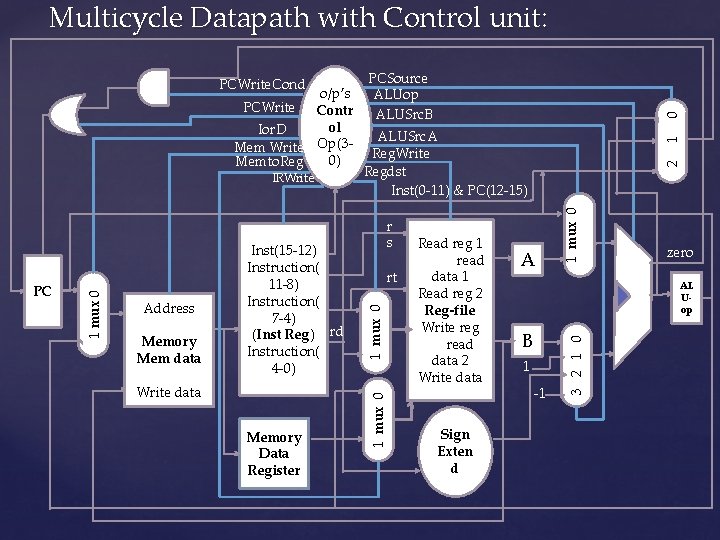

Multicycle Datapath with Control unit: Address Memory Mem data Write data Memory Data Register rt 0 Read reg 1 read data 1 Read reg 2 Reg-file Write reg read data 2 Write data Sign Exten d 1 2 A 1 mux 0 Inst(15 -12) Instruction( 11 -8) Instruction( 7 -4) (Inst Reg) rd Instruction( 4 -0) r s zero AL Uop B 1 -1 3 2 1 0 PC 1 mux 0 IRWrite ALUSrc. A Reg. Write Regdst Inst(0 -11) & PC(12 -15) 1 mux 0 o/p’s PCWrite Contr ol Ior. D Mem Write Op(30) Memto. Reg PCSource ALUop ALUSrc. B 1 mux 0 PCWrite. Cond

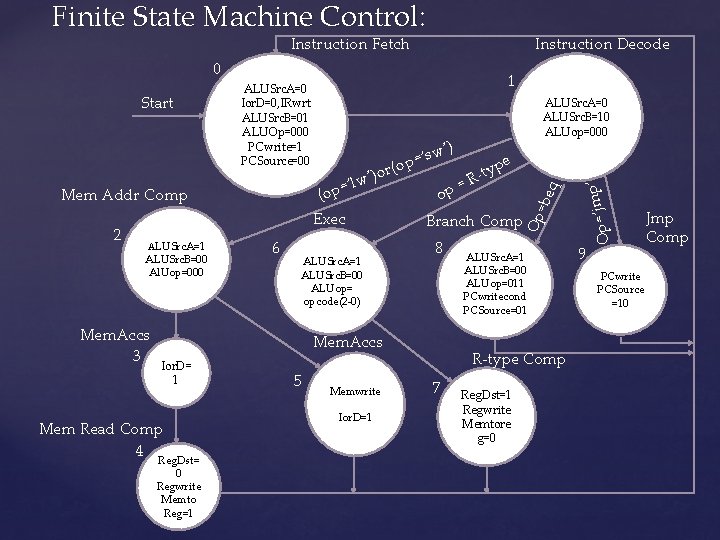

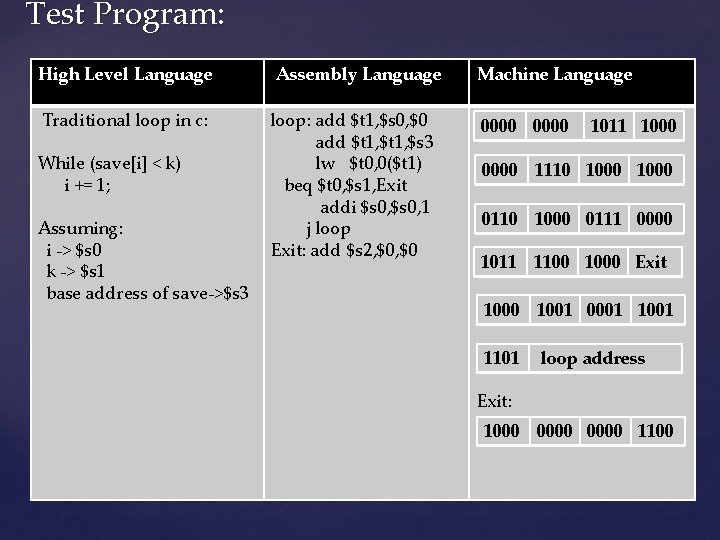

Finite State Machine Control: Instruction Decode Instruction Fetch 0 ALUSrc. A=1 ALUSrc. B=00 Al. Uop=000 Mem. Accs 3 6 ALUSrc. A=1 ALUSrc. B=00 ALUop= opcode(2 -0) Branch Comp 8 Mem. Accs Ior. D= 1 Mem Read Comp 4 Reg. Dst= 0 Regwrite Memto Reg=1 5 Memwrite Ior. D=1 ALUSrc. A=1 ALUSrc. B=00 ALUop=011 PCwritecond PCSource=01 R-type Comp 7 Reg. Dst=1 Regwrite Memtore g=0 p’ q op pe -ty R = =be ‘ o lw’) =‘sw p o r( m Op=‘j 2 ’) = (op Exec Mem Addr Comp ALUSrc. A=0 ALUSrc. B=10 ALUop=000 Op Start 1 ALUSrc. A=0 Ior. D=0, IRwrt ALUSrc. B=01 ALUOp=000 PCwrite=1 PCSource=00 9 PCwrite PCSource =10 Jmp Comp

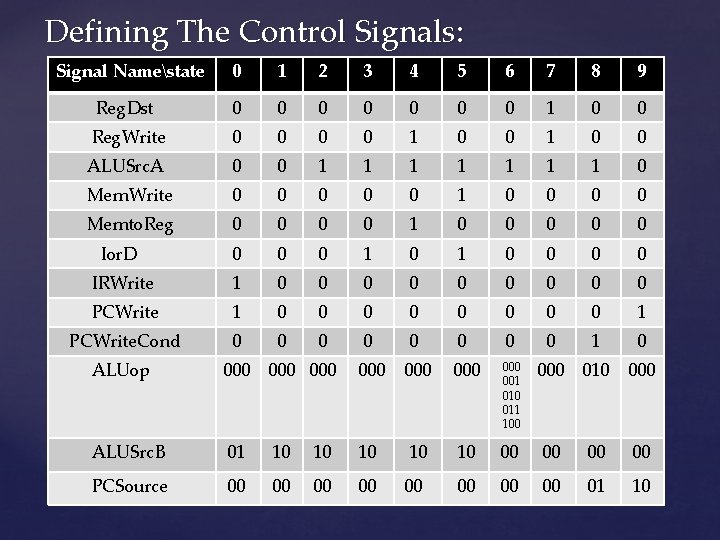

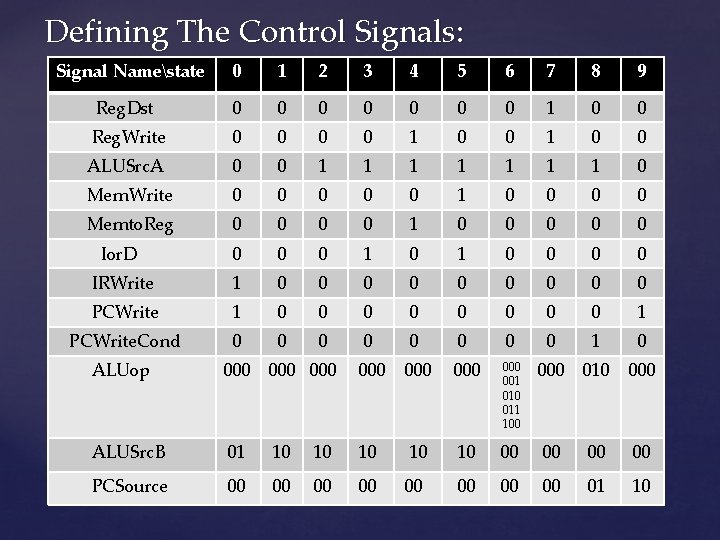

Defining The Control Signals: Signal Namestate 0 1 2 3 4 5 6 7 8 9 Reg. Dst 0 0 0 0 1 0 0 Reg. Write 0 0 1 0 0 ALUSrc. A 0 0 1 1 1 1 0 Mem. Write 0 0 0 1 0 0 Memto. Reg 0 0 1 0 0 0 Ior. D 0 0 0 1 0 0 IRWrite 1 0 0 0 0 0 PCWrite 1 0 0 0 0 1 PCWrite. Cond 0 0 0 0 1 0 ALUop 000 000 001 010 011 100 010 000 ALUSrc. B 01 10 10 10 00 00 PCSource 00 00 01 10

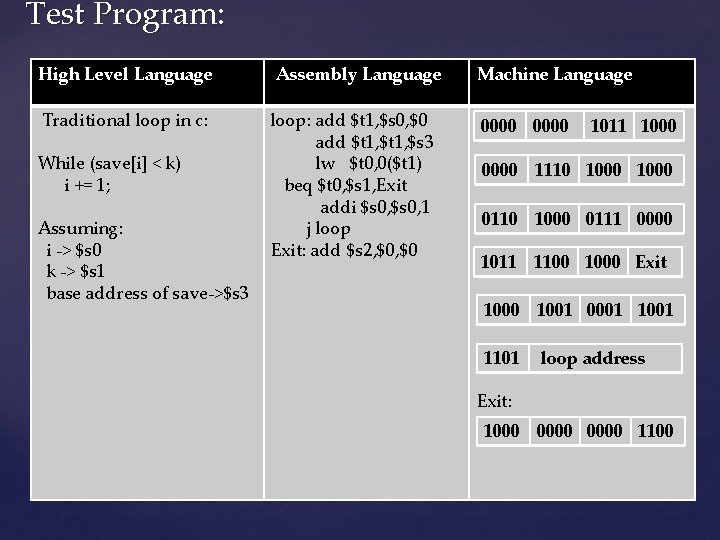

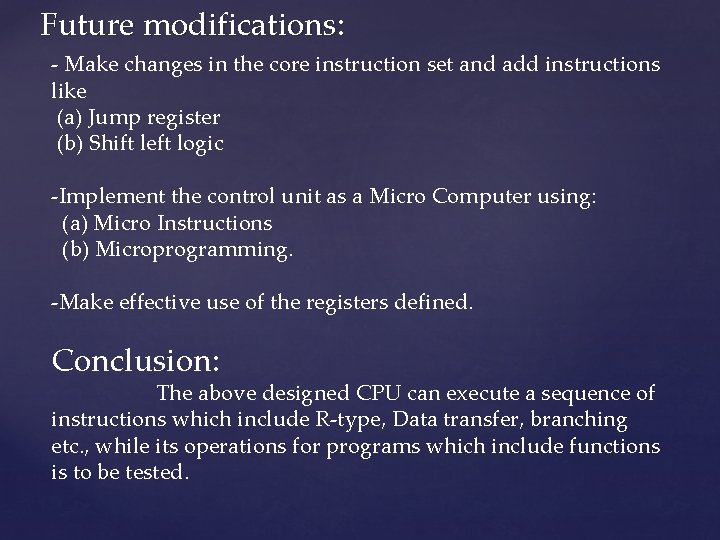

Test Program: High Level Language Assembly Language Machine Language Traditional loop in c: loop: add $t 1, $s 0, $0 add $t 1, $s 3 lw $t 0, 0($t 1) beq $t 0, $s 1, Exit addi $s 0, 1 j loop Exit: add $s 2, $0 0000 While (save[i] < k) i += 1; Assuming: i -> $s 0 k -> $s 1 base address of save->$s 3 1011 1000 0000 1110 1000 0110 1000 0111 0000 1011 1100 1000 Exit 1000 1001 0001 1101 loop address Exit: 1000 0000 1100

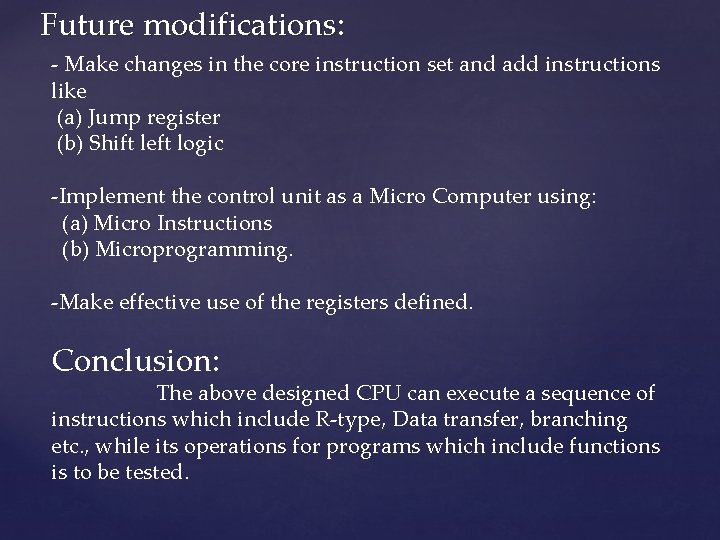

Future modifications: - Make changes in the core instruction set and add instructions like (a) Jump register (b) Shift left logic -Implement the control unit as a Micro Computer using: (a) Micro Instructions (b) Microprogramming. -Make effective use of the registers defined. Conclusion: The above designed CPU can execute a sequence of instructions which include R-type, Data transfer, branching etc. , while its operations for programs which include functions is to be tested.

Questions

Thank you!