CPU Design Levels of Representation 61 C Review

![Levels of Representation (61 C Review) temp = v[k]; High Level Language Program Compiler Levels of Representation (61 C Review) temp = v[k]; High Level Language Program Compiler](https://slidetodoc.com/presentation_image/a27ee861464f0f30d75af9a753763f57/image-2.jpg)

![Instruction Execute. . . Out In IR[adr] MAR, Accu MDR, Write 02 1 0 Instruction Execute. . . Out In IR[adr] MAR, Accu MDR, Write 02 1 0](https://slidetodoc.com/presentation_image/a27ee861464f0f30d75af9a753763f57/image-15.jpg)

![Instruction Execute. . . Out In IR[adr] MAR, Accu MDR, Write 04 1 1 Instruction Execute. . . Out In IR[adr] MAR, Accu MDR, Write 04 1 1](https://slidetodoc.com/presentation_image/a27ee861464f0f30d75af9a753763f57/image-23.jpg)

![Instruction Execute (1). . . IR[adress] MAR , Read 05 Out In 1 0 Instruction Execute (1). . . IR[adress] MAR , Read 05 Out In 1 0](https://slidetodoc.com/presentation_image/a27ee861464f0f30d75af9a753763f57/image-27.jpg)

![Instruction Execute. . . (acc ≥ 0 IR[adress] PC) 08 Out In 0 5 Instruction Execute. . . (acc ≥ 0 IR[adress] PC) 08 Out In 0 5](https://slidetodoc.com/presentation_image/a27ee861464f0f30d75af9a753763f57/image-32.jpg)

- Slides: 40

CPU Design

![Levels of Representation 61 C Review temp vk High Level Language Program Compiler Levels of Representation (61 C Review) temp = v[k]; High Level Language Program Compiler](https://slidetodoc.com/presentation_image/a27ee861464f0f30d75af9a753763f57/image-2.jpg)

Levels of Representation (61 C Review) temp = v[k]; High Level Language Program Compiler Assembly Language Program Assembler Machine Language Program v[k] = v[k+1]; v[k+1] = temp; lw lw sw sw 0000 1010 1100 0101 1001 1111 0110 1000 $15, $16, $15, 1100 0101 1010 0000 0110 1000 1111 1001 0($2) 4($2) 1010 0000 0101 1100 1111 1000 0110 0101 1100 0000 1010 1000 0110 1001 1111 Machine Interpretation Control Signal Specification ALUOP[0: 3] <= Inst. Reg[9: 11] & MASK ° ° 1/22/02 CS 252/Culler Lec 1. 2

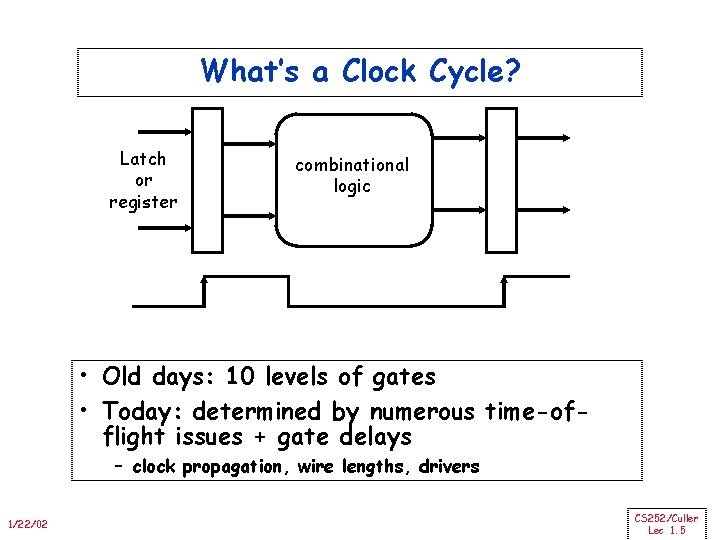

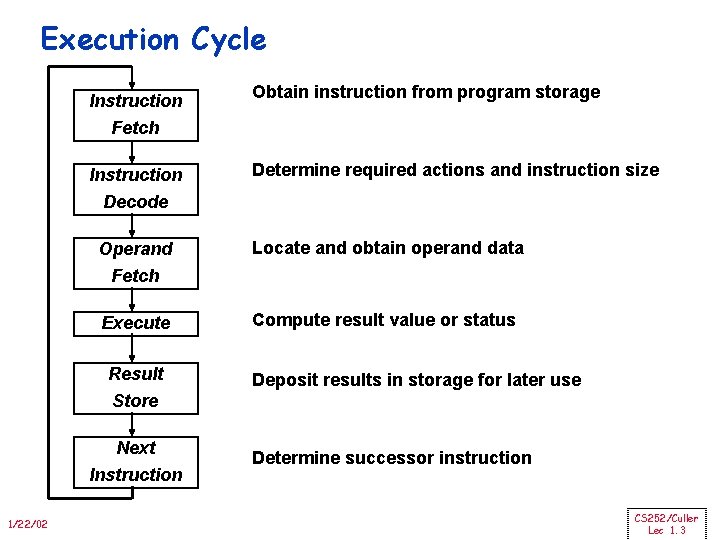

Execution Cycle Instruction Obtain instruction from program storage Fetch Instruction Determine required actions and instruction size Decode Operand Locate and obtain operand data Fetch Execute Result Compute result value or status Deposit results in storage for later use Store Next Instruction 1/22/02 Determine successor instruction CS 252/Culler Lec 1. 3

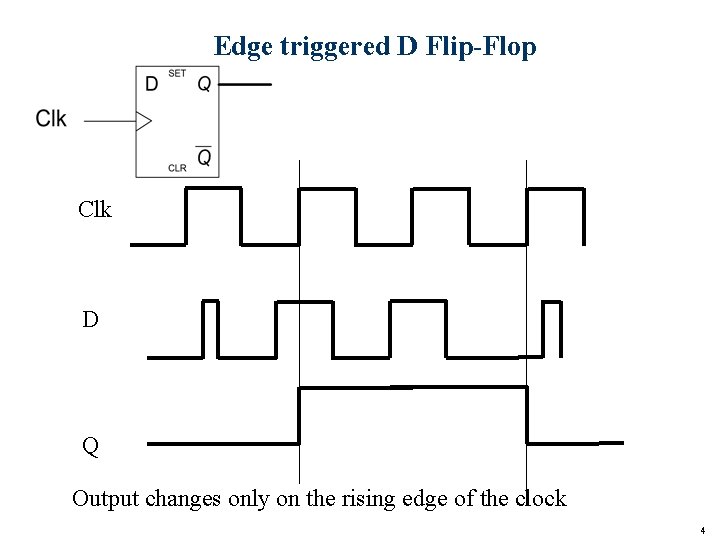

Edge triggered D Flip-Flop Clk D Q Output changes only on the rising edge of the clock 4

What’s a Clock Cycle? Latch or register combinational logic • Old days: 10 levels of gates • Today: determined by numerous time-offlight issues + gate delays – clock propagation, wire lengths, drivers 1/22/02 CS 252/Culler Lec 1. 5

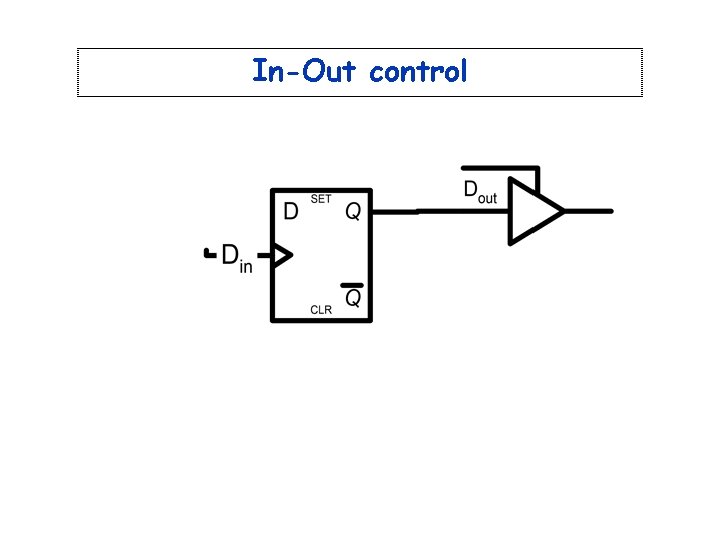

In-Out control

• Instruction 00

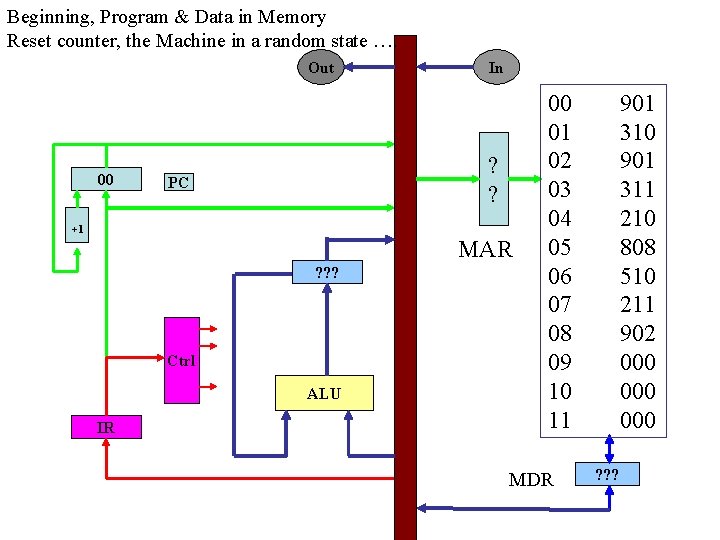

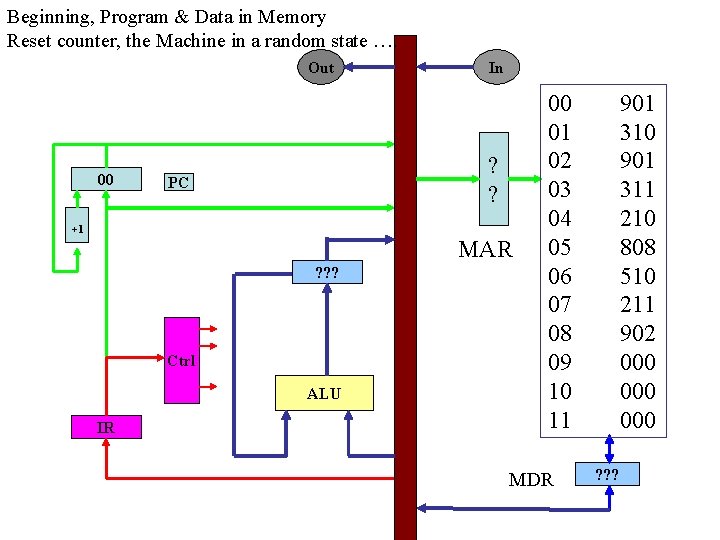

Beginning, Program & Data in Memory Reset counter, the Machine in a random state …. Out 00 In ? ? PC +1 MAR ? ? ? Ctrl ALU IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 000 ? ? ?

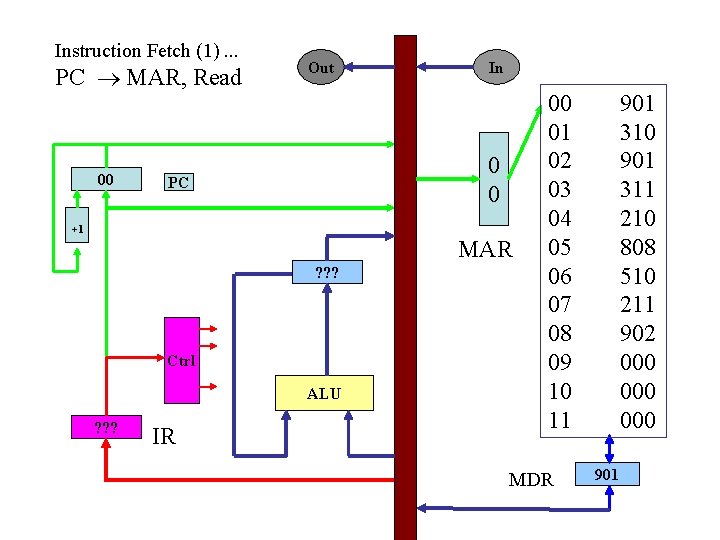

Instruction Fetch (1). . . PC MAR, Read 00 Out In 0 0 PC +1 MAR ? ? ? Ctrl ALU ? ? ? IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 000 901

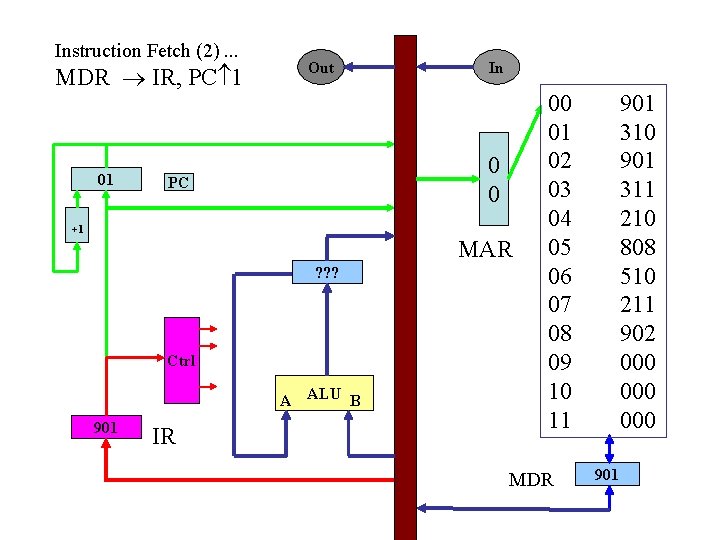

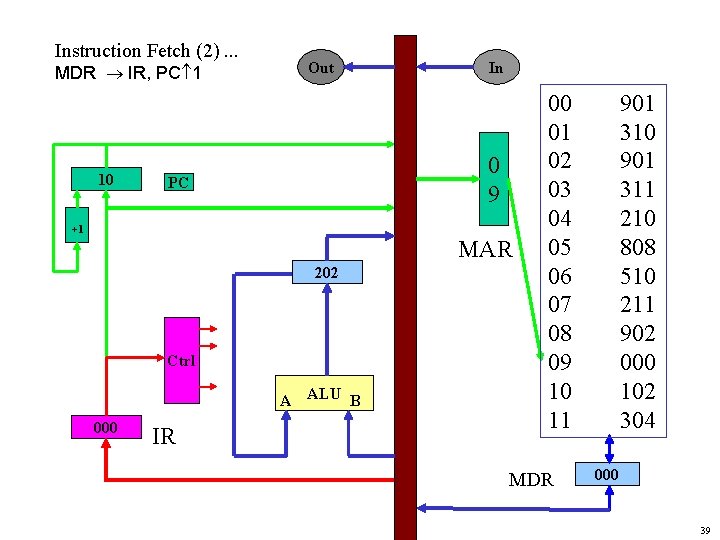

Instruction Fetch (2). . . MDR IR, PC 1 01 Out In 0 0 PC +1 MAR ? ? ? Ctrl A ALU B 901 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 000 901

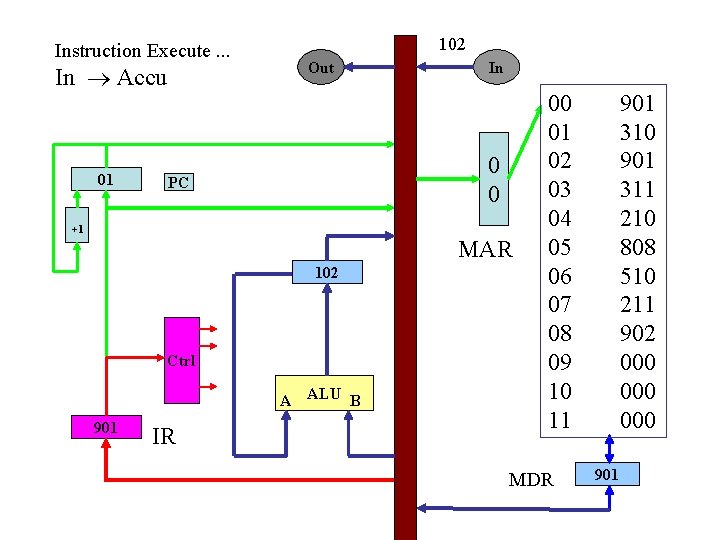

Instruction Execute. . . In Accu 01 102 Out In 0 0 PC +1 MAR 102 Ctrl A ALU B 901 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 000 901

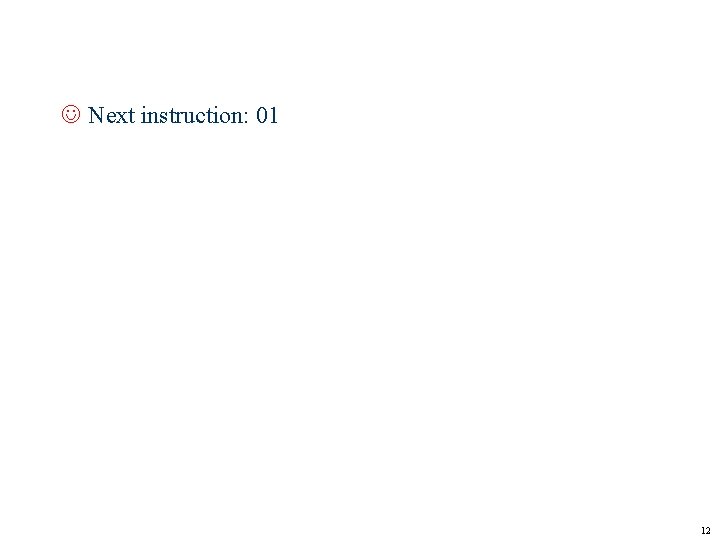

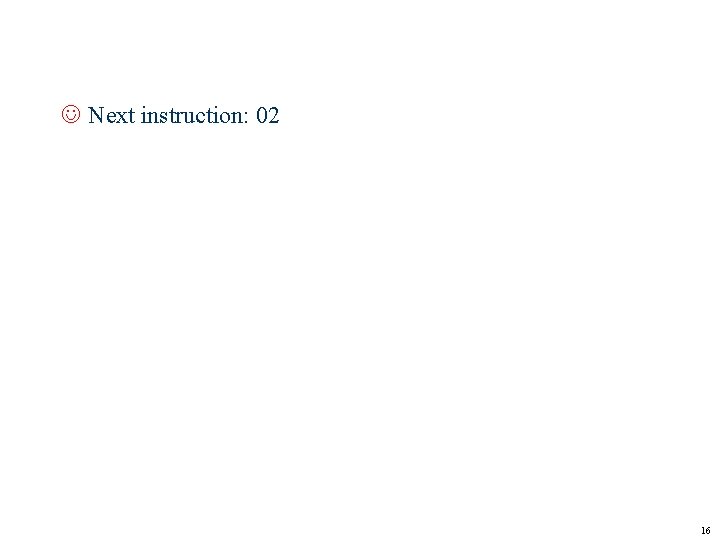

J Next instruction: 01 12

Instruction Fetch (1). . . PC MAR, Read 01 Out In 0 1 PC +1 MAR 102 Ctrl ALU 901 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 000 310 13

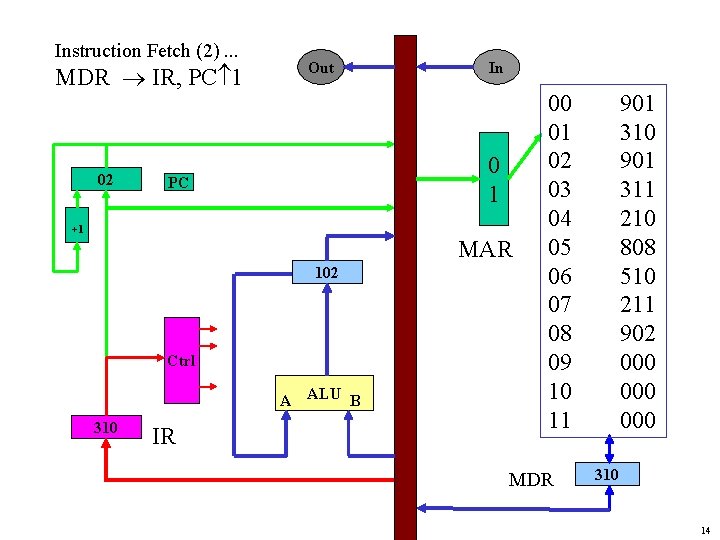

Instruction Fetch (2). . . MDR IR, PC 1 02 Out In 0 1 PC +1 MAR 102 Ctrl A ALU B 310 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 000 310 14

![Instruction Execute Out In IRadr MAR Accu MDR Write 02 1 0 Instruction Execute. . . Out In IR[adr] MAR, Accu MDR, Write 02 1 0](https://slidetodoc.com/presentation_image/a27ee861464f0f30d75af9a753763f57/image-15.jpg)

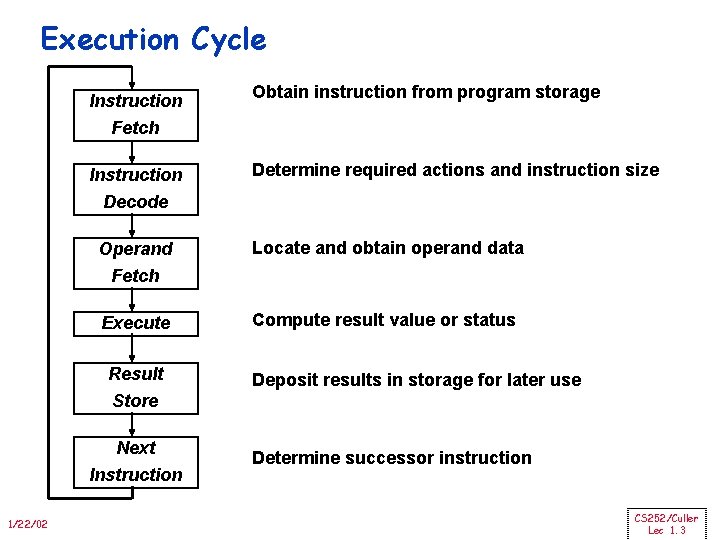

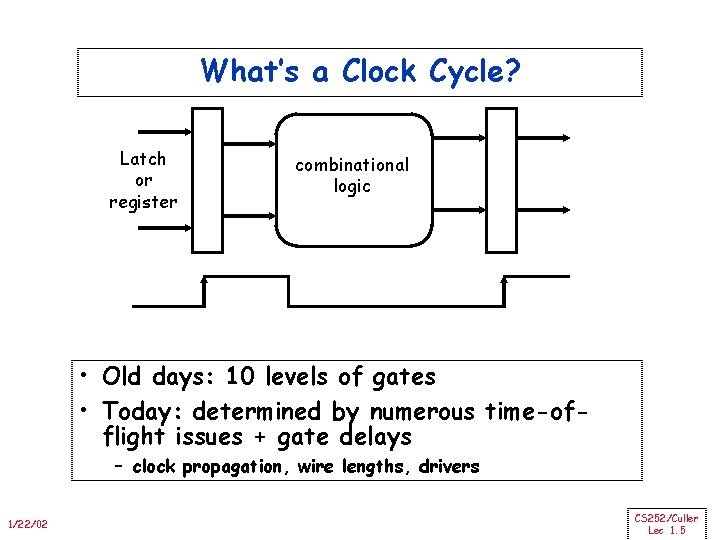

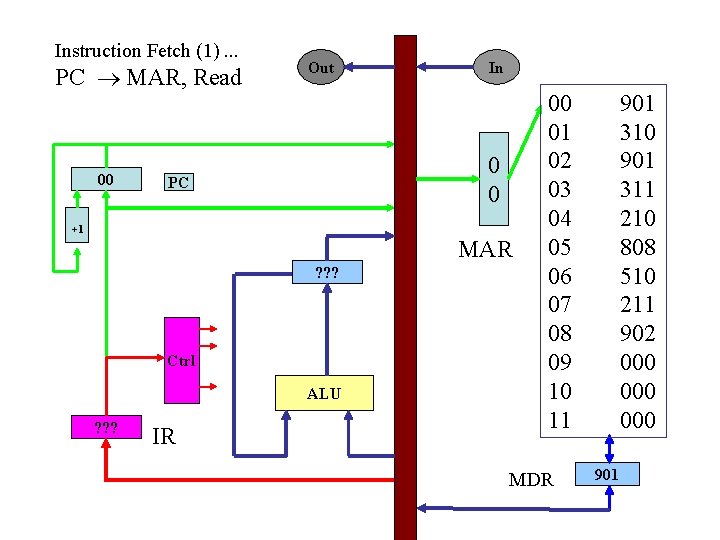

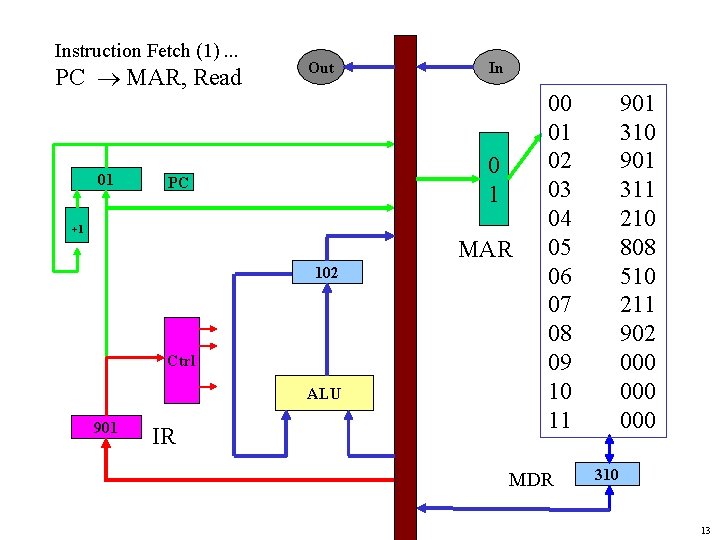

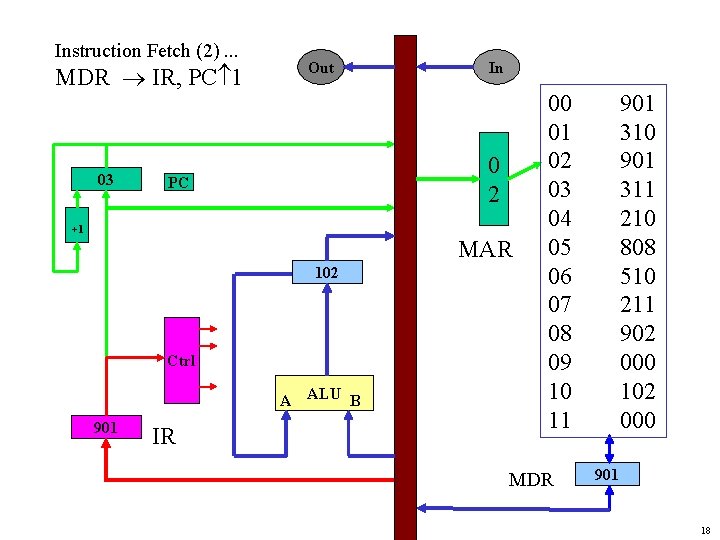

Instruction Execute. . . Out In IR[adr] MAR, Accu MDR, Write 02 1 0 PC +1 MAR 102 ACCU Ctrl A ALU B 310 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 15

J Next instruction: 02 16

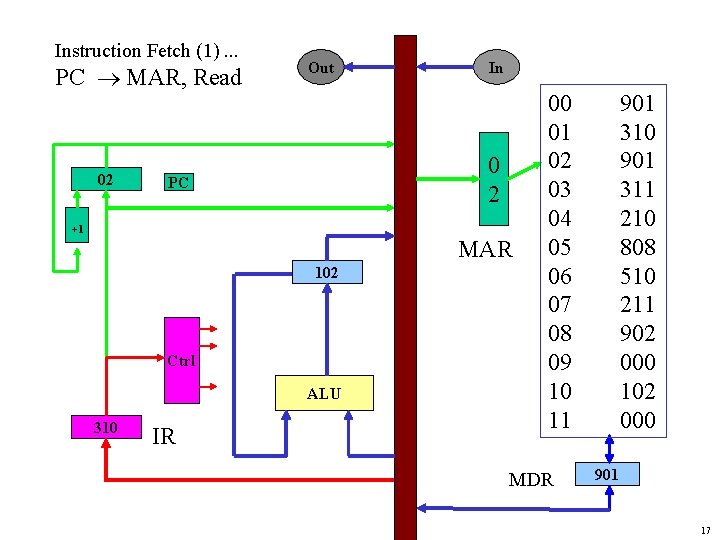

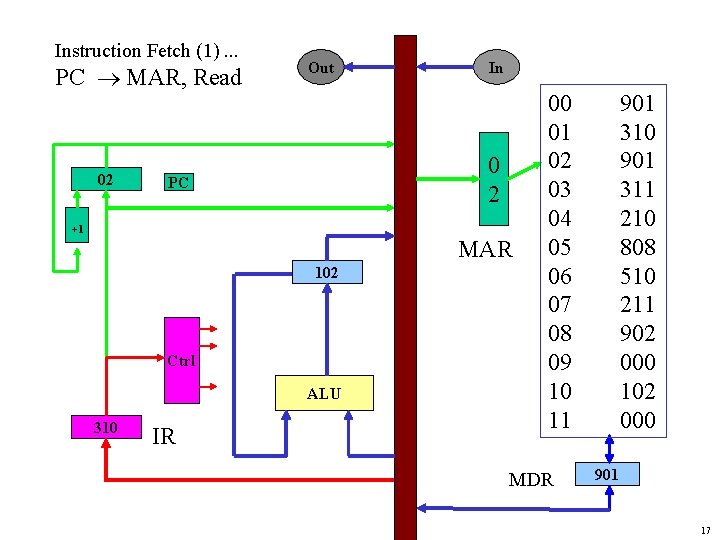

Instruction Fetch (1). . . PC MAR, Read 02 Out In 0 2 PC +1 MAR 102 Ctrl ALU 310 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 000 901 17

Instruction Fetch (2). . . MDR IR, PC 1 03 Out In 0 2 PC +1 MAR 102 Ctrl A ALU B 901 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 000 901 18

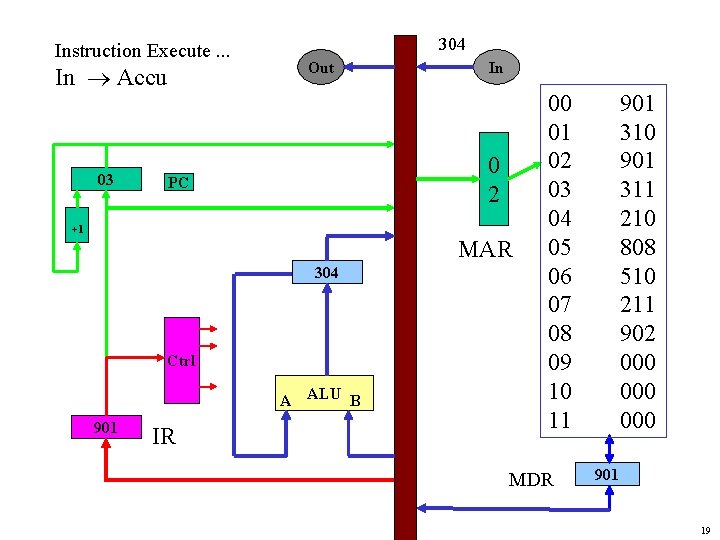

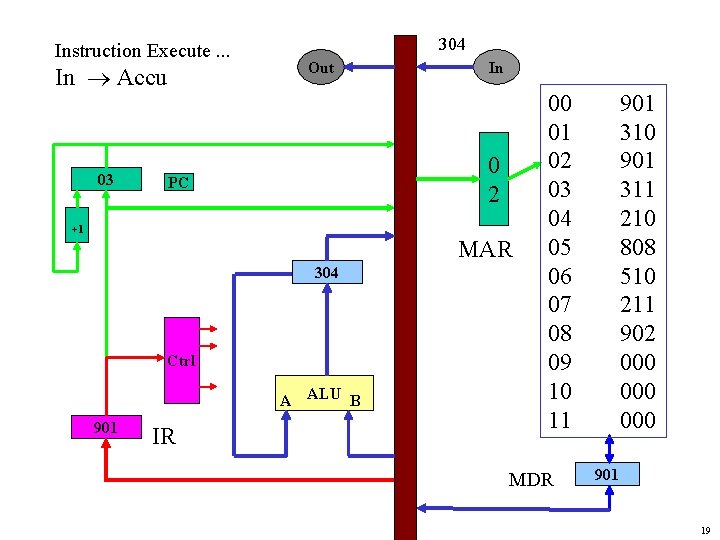

Instruction Execute. . . In Accu 03 304 Out In 0 2 PC +1 MAR 304 Ctrl A ALU B 901 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 000 901 19

J Next instruction: 03 20

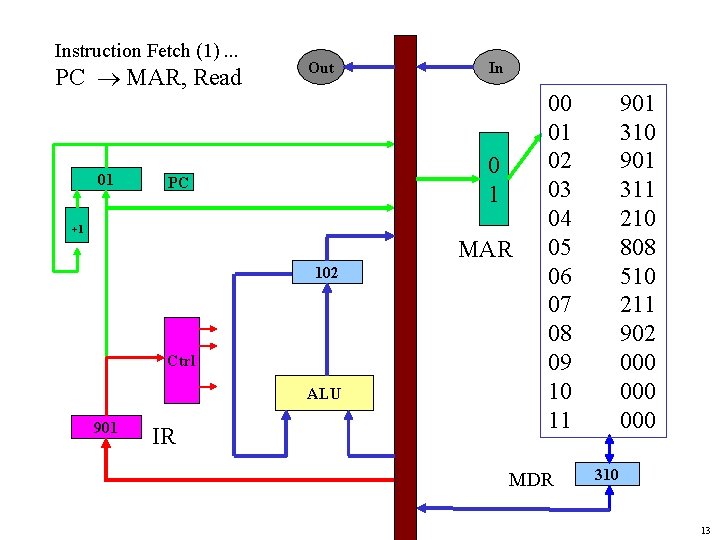

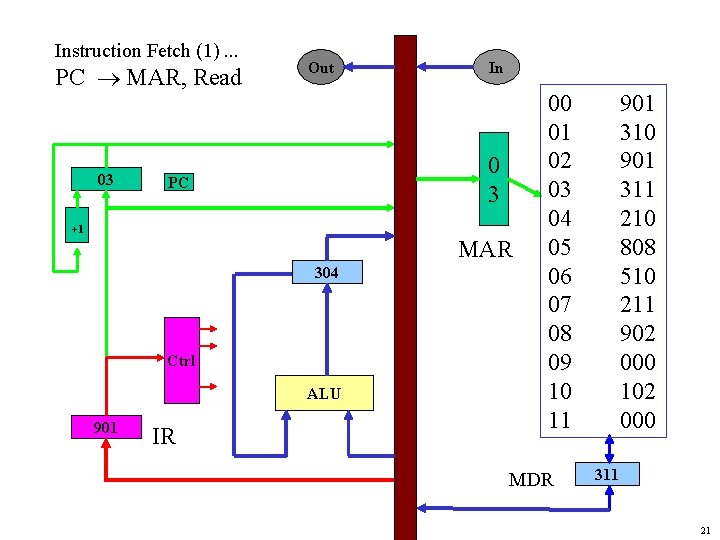

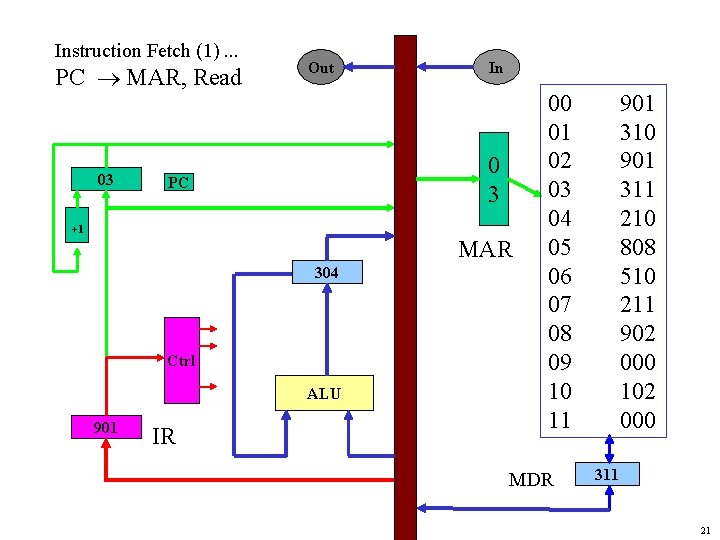

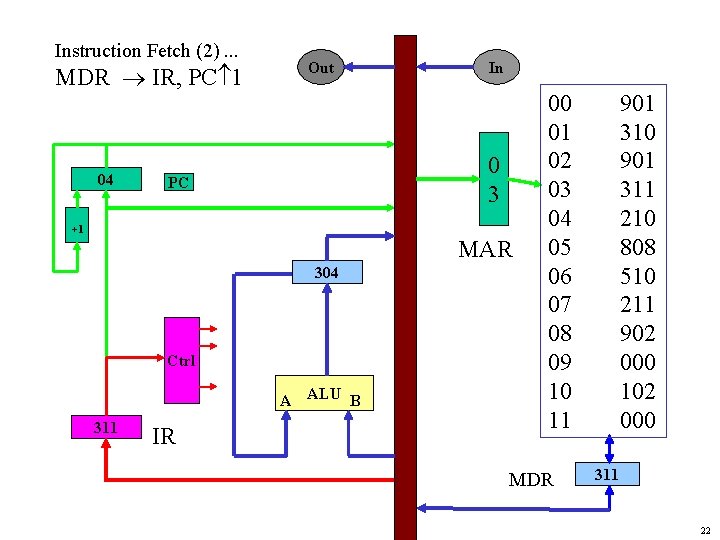

Instruction Fetch (1). . . PC MAR, Read 03 Out In 0 3 PC +1 MAR 304 Ctrl ALU 901 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 000 311 21

Instruction Fetch (2). . . MDR IR, PC 1 04 Out In 0 3 PC +1 MAR 304 Ctrl A ALU B 311 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 000 311 22

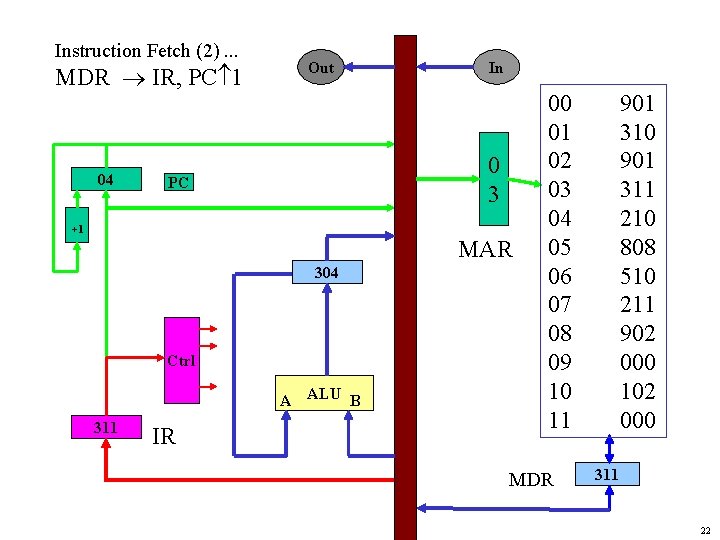

![Instruction Execute Out In IRadr MAR Accu MDR Write 04 1 1 Instruction Execute. . . Out In IR[adr] MAR, Accu MDR, Write 04 1 1](https://slidetodoc.com/presentation_image/a27ee861464f0f30d75af9a753763f57/image-23.jpg)

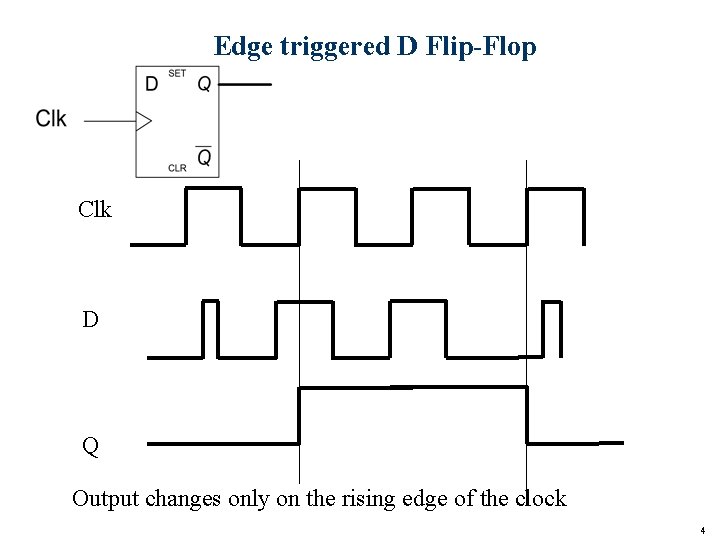

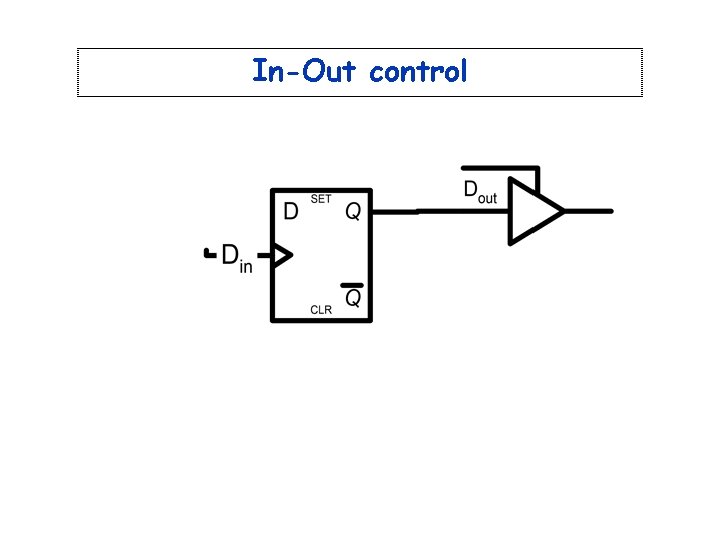

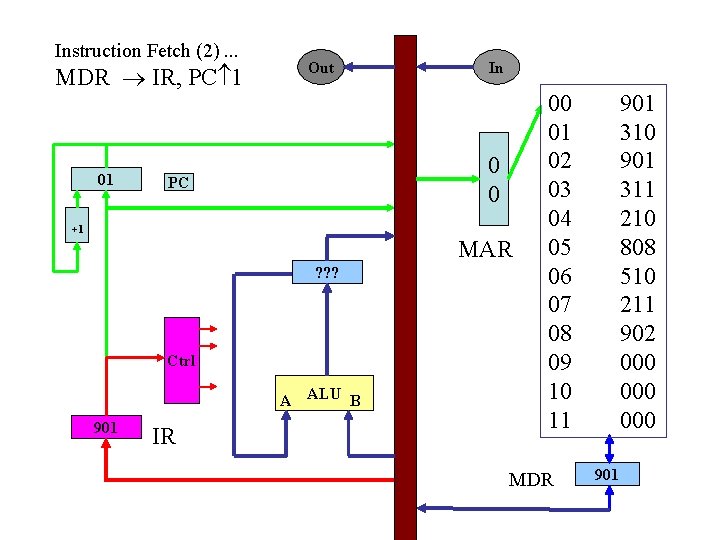

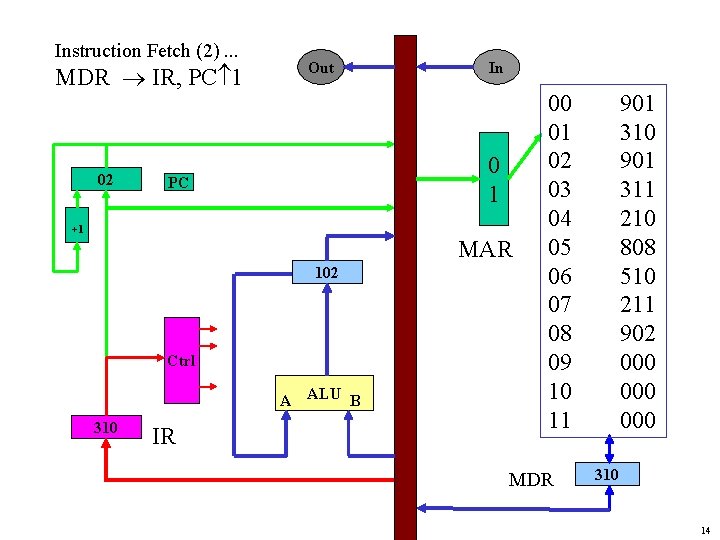

Instruction Execute. . . Out In IR[adr] MAR, Accu MDR, Write 04 1 1 PC +1 MAR 304 ACCU Ctrl A ALU B 311 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 304 23

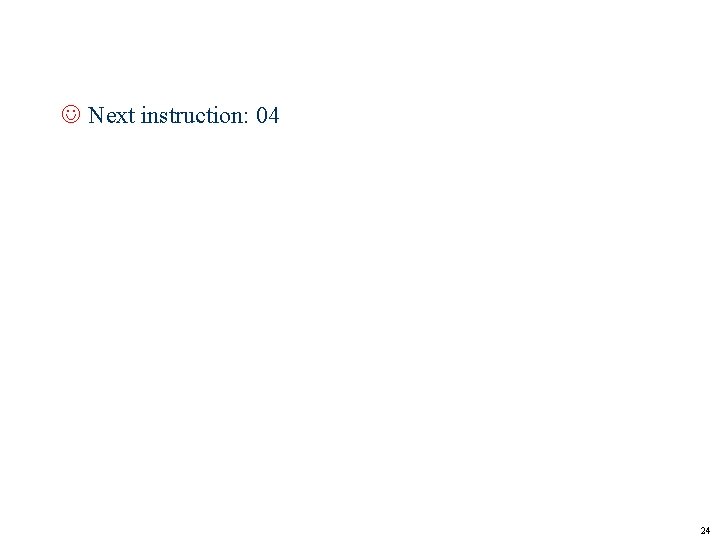

J Next instruction: 04 24

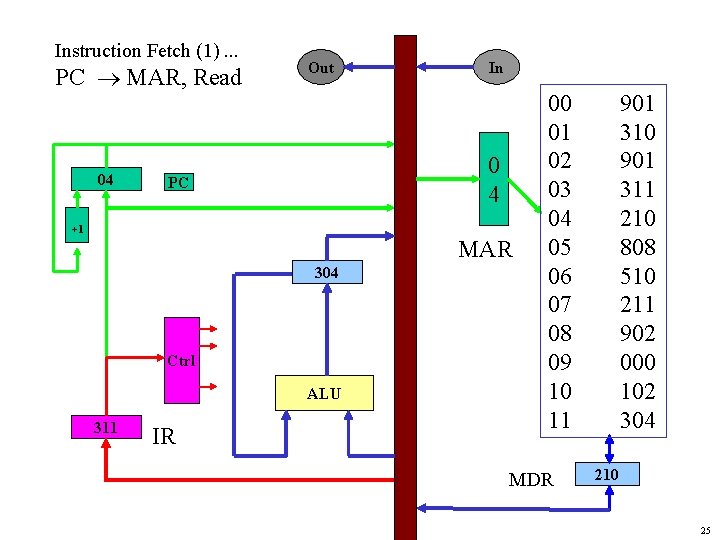

Instruction Fetch (1). . . PC MAR, Read 04 Out In 0 4 PC +1 MAR 304 Ctrl ALU 311 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 304 210 25

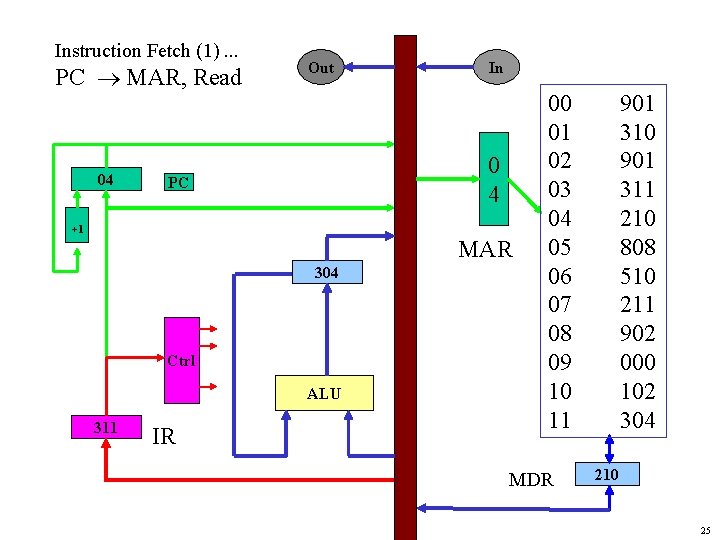

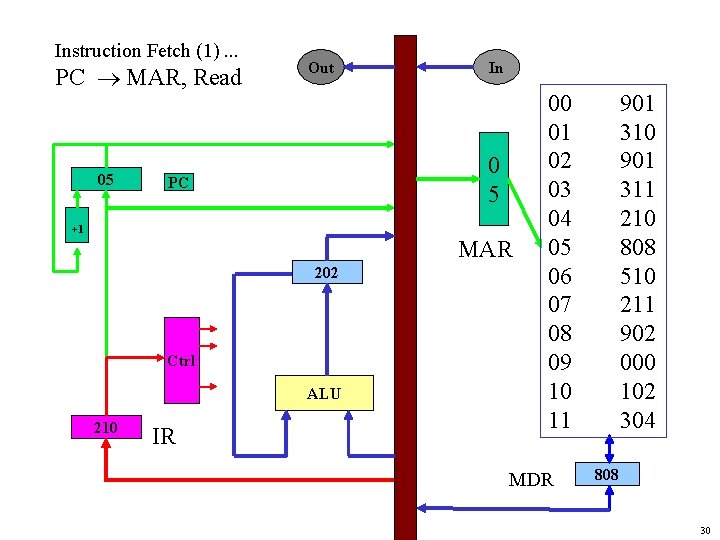

Instruction Fetch (2). . . MDR IR, PC 1 05 Out In 0 4 PC +1 MAR 304 Ctrl A ALU B 210 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 304 210 26

![Instruction Execute 1 IRadress MAR Read 05 Out In 1 0 Instruction Execute (1). . . IR[adress] MAR , Read 05 Out In 1 0](https://slidetodoc.com/presentation_image/a27ee861464f0f30d75af9a753763f57/image-27.jpg)

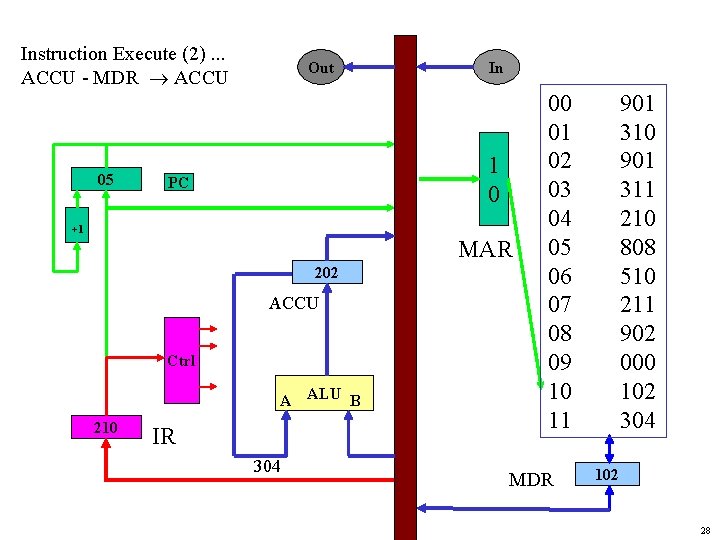

Instruction Execute (1). . . IR[adress] MAR , Read 05 Out In 1 0 PC +1 MAR 304 ACCU Ctrl A ALU B 210 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 304 102 27

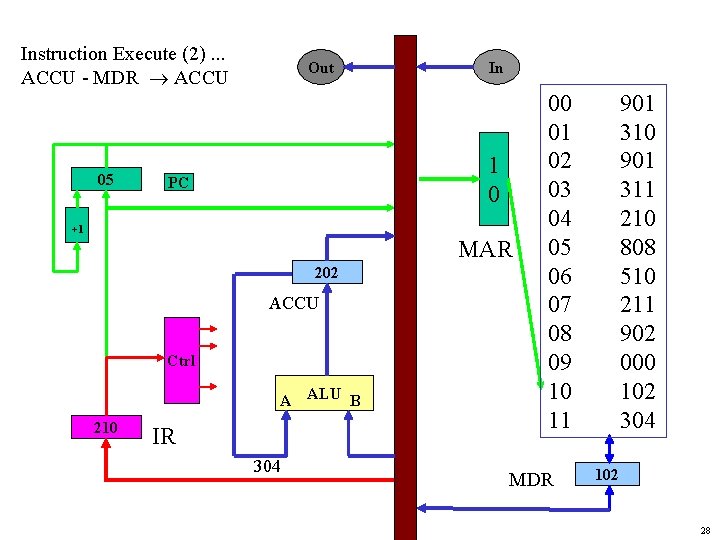

Instruction Execute (2). . . ACCU - MDR ACCU 05 Out In 1 0 PC +1 MAR 202 ACCU Ctrl A ALU B 210 IR 304 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 304 102 28

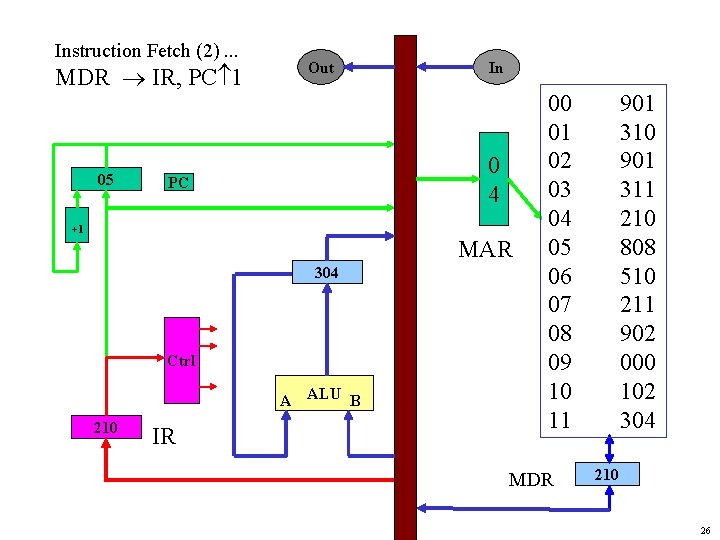

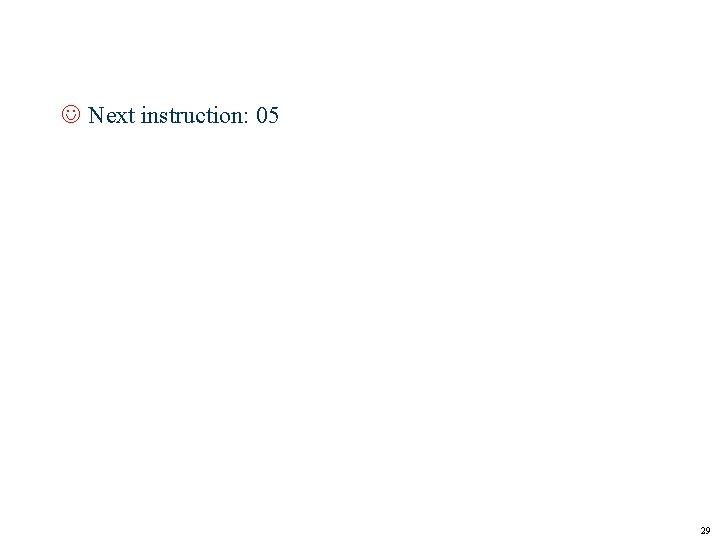

J Next instruction: 05 29

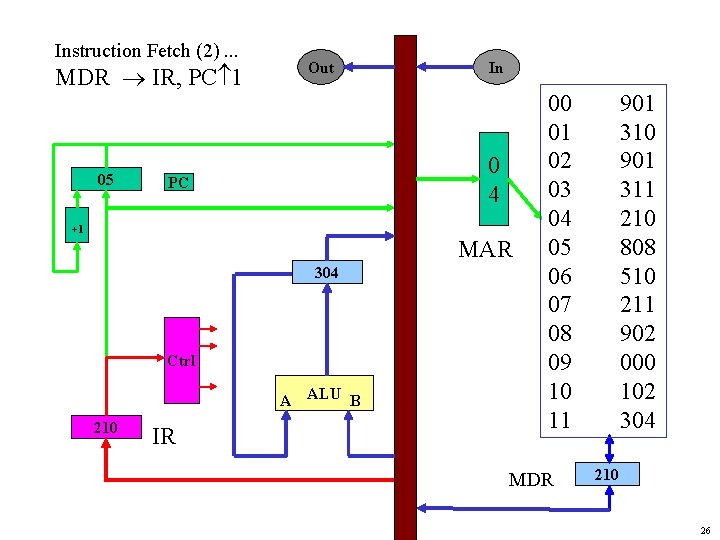

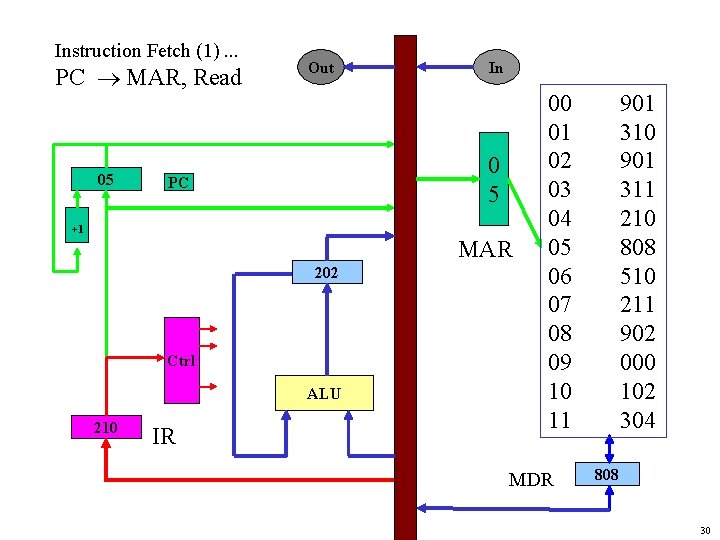

Instruction Fetch (1). . . PC MAR, Read 05 Out In 0 5 PC +1 MAR 202 Ctrl ALU 210 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 304 808 30

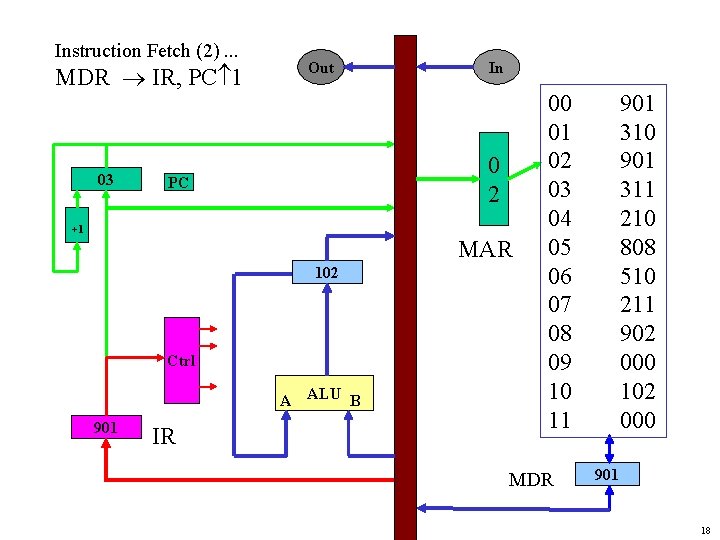

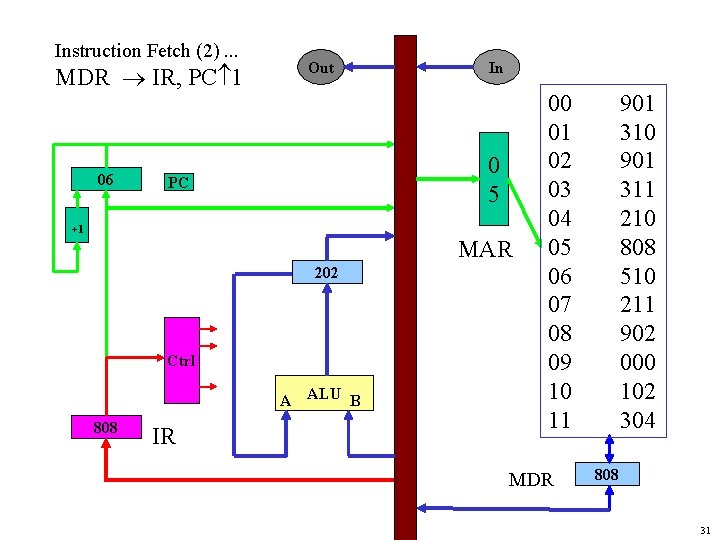

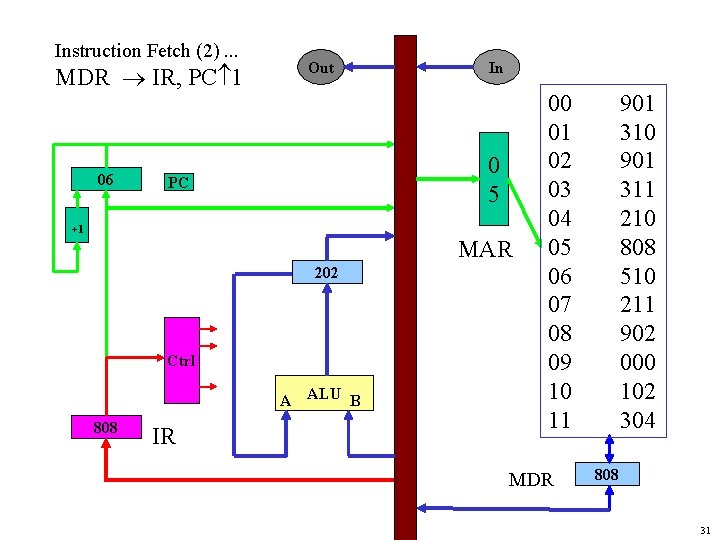

Instruction Fetch (2). . . MDR IR, PC 1 06 Out In 0 5 PC +1 MAR 202 Ctrl A ALU B 808 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 304 808 31

![Instruction Execute acc 0 IRadress PC 08 Out In 0 5 Instruction Execute. . . (acc ≥ 0 IR[adress] PC) 08 Out In 0 5](https://slidetodoc.com/presentation_image/a27ee861464f0f30d75af9a753763f57/image-32.jpg)

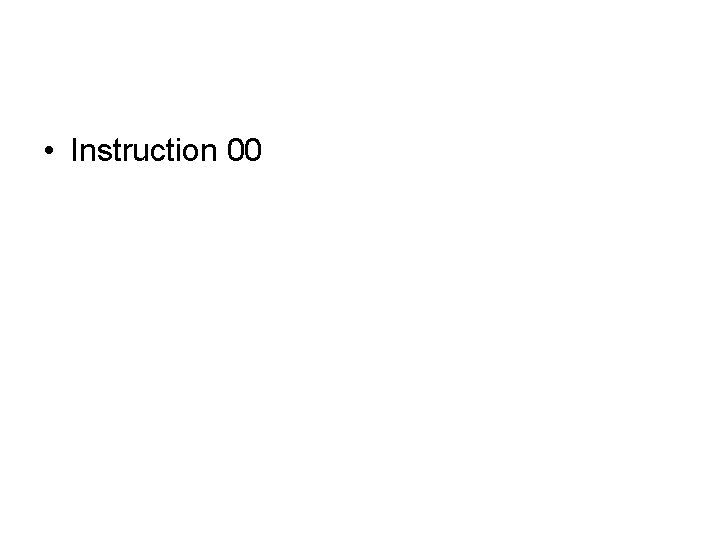

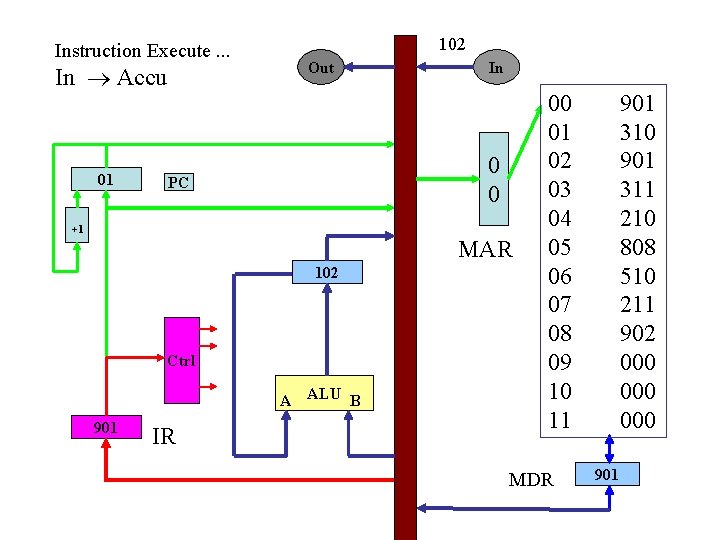

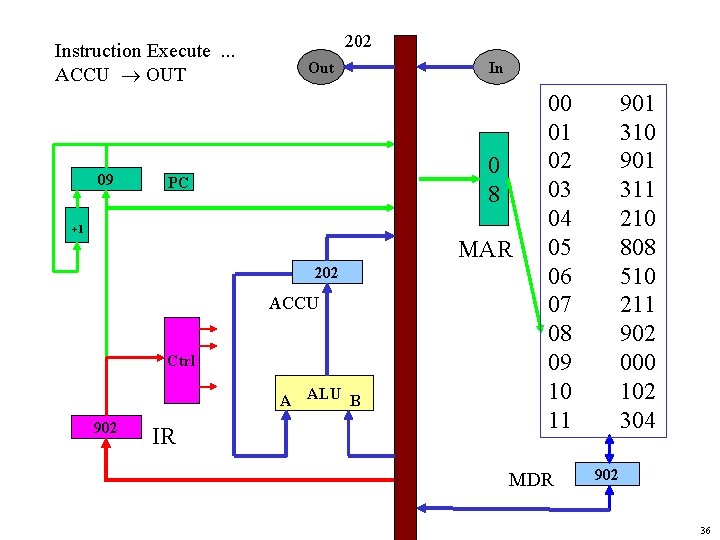

Instruction Execute. . . (acc ≥ 0 IR[adress] PC) 08 Out In 0 5 PC +1 MAR 102 ACCU Ctrl A ALU B 808 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 304 808 32

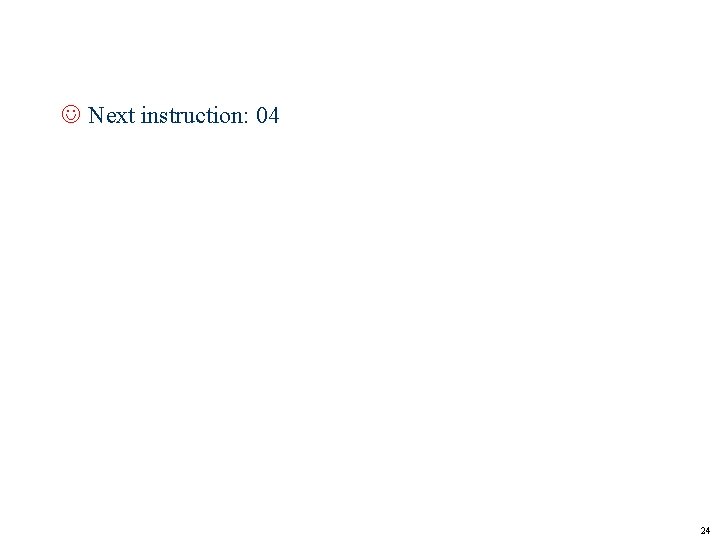

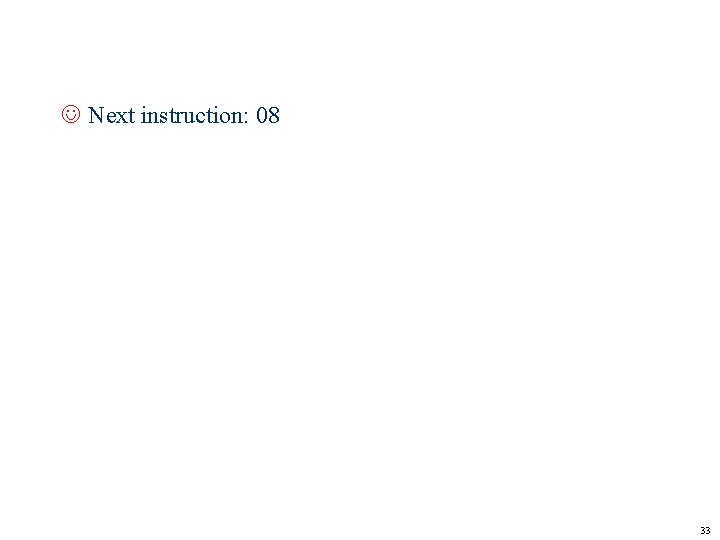

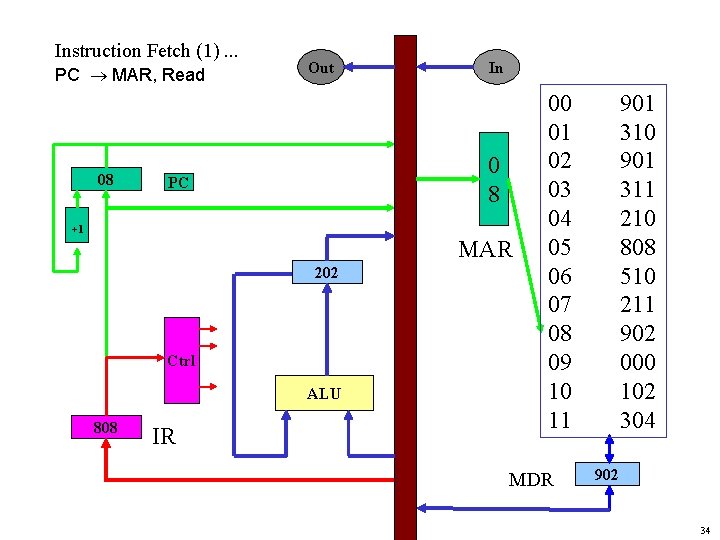

J Next instruction: 08 33

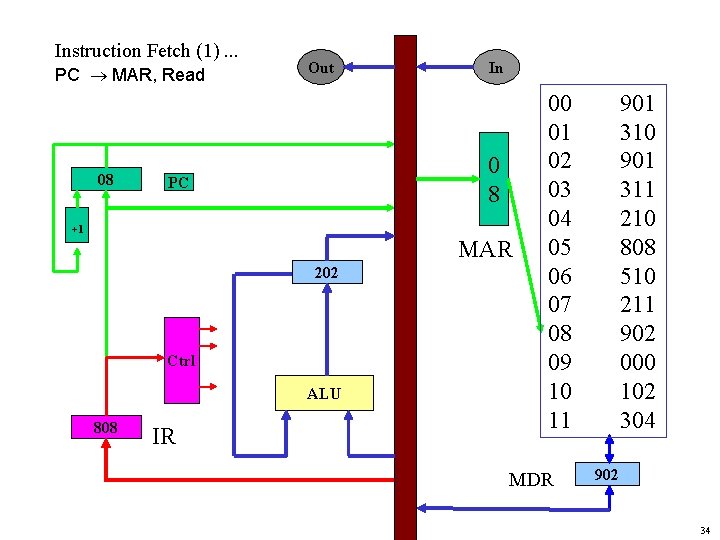

Instruction Fetch (1). . . PC MAR, Read 08 Out In 0 8 PC +1 MAR 202 Ctrl ALU 808 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 304 902 34

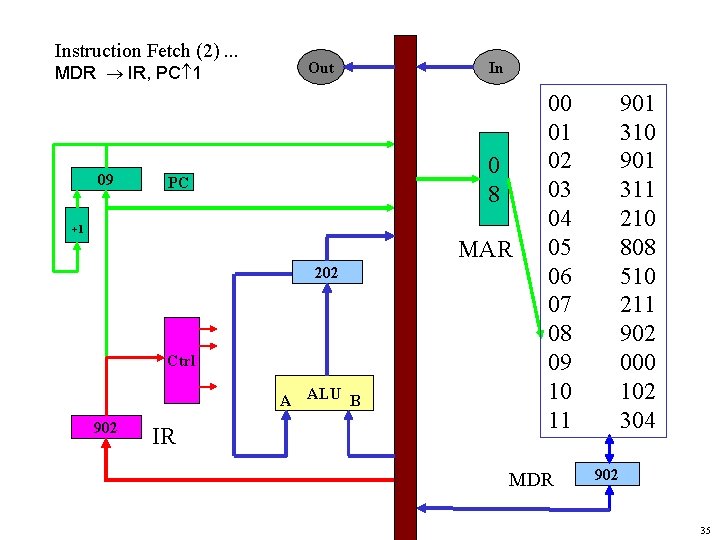

Instruction Fetch (2). . . MDR IR, PC 1 09 Out In 0 8 PC +1 MAR 202 Ctrl A ALU B 902 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 304 902 35

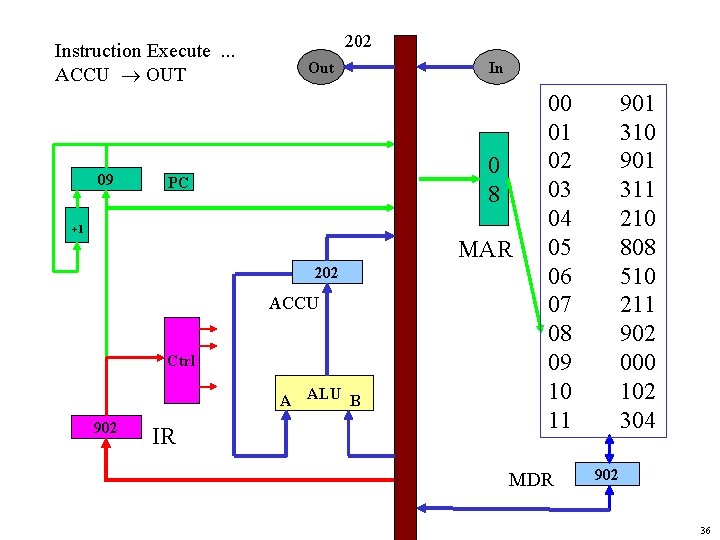

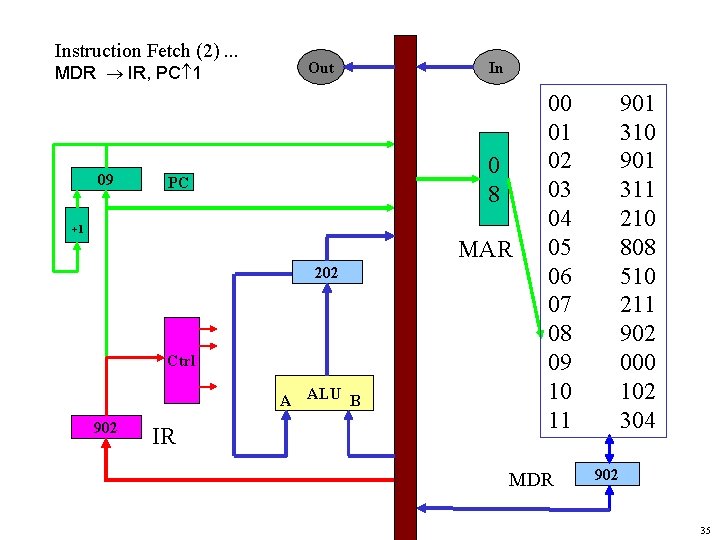

Instruction Execute. . . ACCU OUT 09 202 Out In 0 8 PC +1 MAR 202 ACCU Ctrl A ALU B 902 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 304 902 36

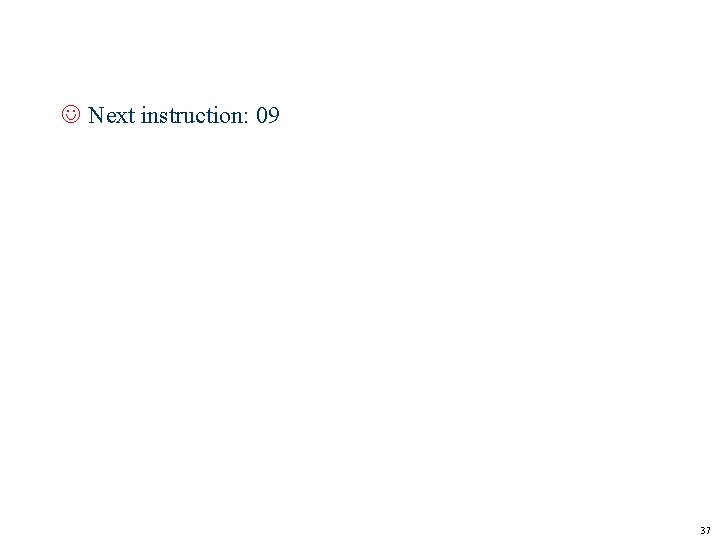

J Next instruction: 09 37

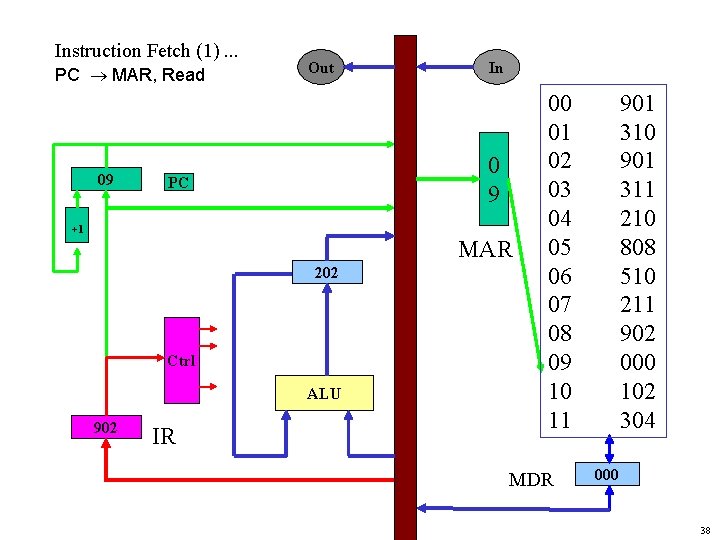

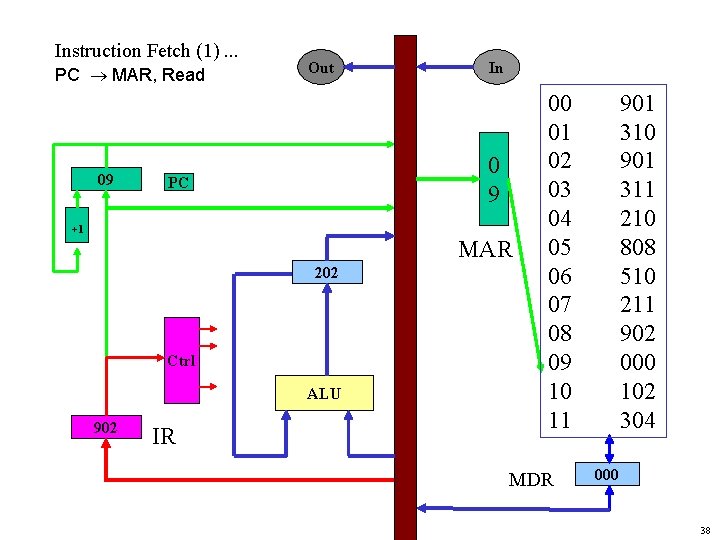

Instruction Fetch (1). . . PC MAR, Read 09 Out In 0 9 PC +1 MAR 202 Ctrl ALU 902 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 304 000 38

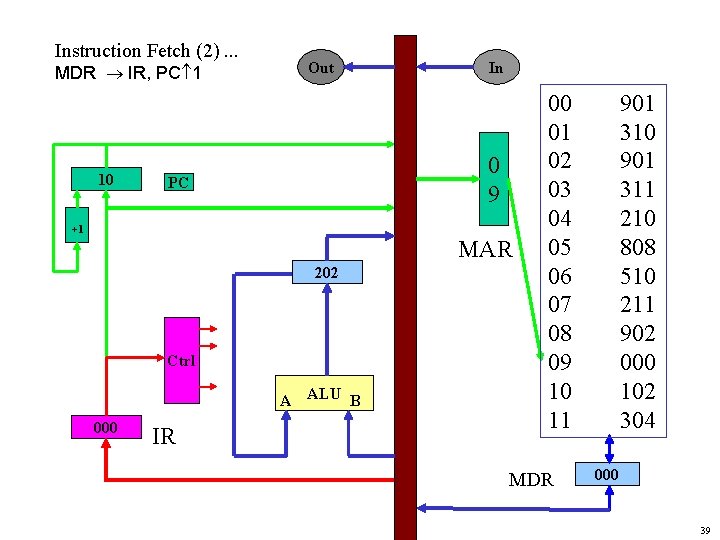

Instruction Fetch (2). . . MDR IR, PC 1 10 Out In 0 9 PC +1 MAR 202 Ctrl A ALU B 000 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 304 000 39

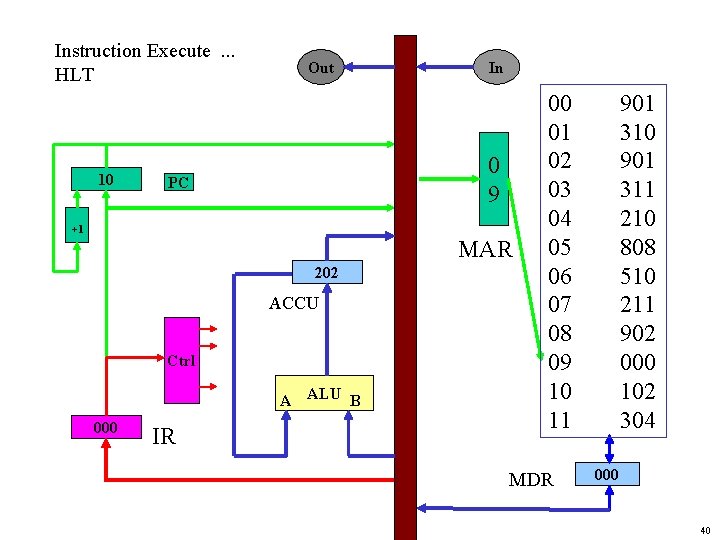

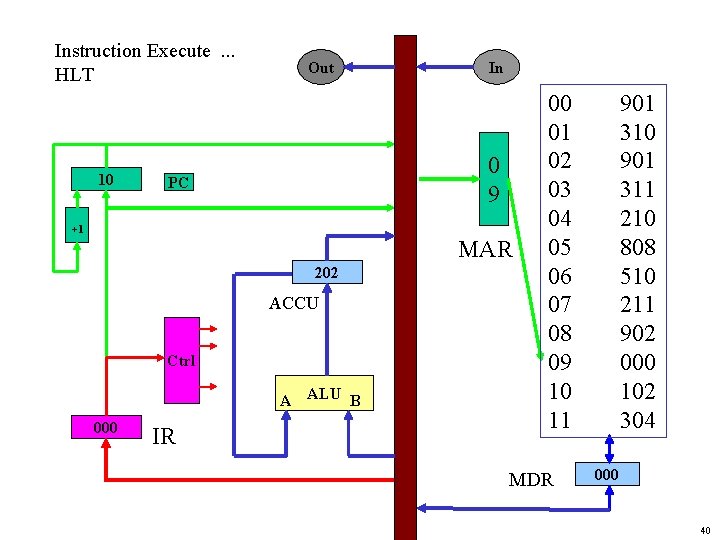

Instruction Execute. . . HLT 10 Out In 0 9 PC +1 MAR 202 ACCU Ctrl A ALU B 000 IR 00 01 02 03 04 05 06 07 08 09 10 11 MDR 901 310 901 311 210 808 510 211 902 000 102 304 000 40