Cpr E 281 Digital Logic Instructor Alexander Stoytchev

![Graphical Symbol and Truth Table [ Figure 4. 2 a-b from the textbook ] Graphical Symbol and Truth Table [ Figure 4. 2 a-b from the textbook ]](https://slidetodoc.com/presentation_image_h/a31d07ff4ba9b19801471c89b07be575/image-20.jpg)

![The long-form truth table [http: //www. absoluteastronomy. com/topics/Multiplexer] The long-form truth table [http: //www. absoluteastronomy. com/topics/Multiplexer]](https://slidetodoc.com/presentation_image_h/a31d07ff4ba9b19801471c89b07be575/image-22.jpg)

![The XOR Logic Gate [ Figure 2. 11 from the textbook ] The XOR Logic Gate [ Figure 2. 11 from the textbook ]](https://slidetodoc.com/presentation_image_h/a31d07ff4ba9b19801471c89b07be575/image-39.jpg)

![The XOR Logic Gate [ Figure 2. 11 from the textbook ] The XOR Logic Gate [ Figure 2. 11 from the textbook ]](https://slidetodoc.com/presentation_image_h/a31d07ff4ba9b19801471c89b07be575/image-40.jpg)

- Slides: 87

Cpr. E 281: Digital Logic Instructor: Alexander Stoytchev http: //www. ece. iastate. edu/~alexs/classes/

Multiplexers Cpr. E 281: Digital Logic Iowa State University, Ames, IA Copyright © Alexander Stoytchev

Administrative Stuff • HW 6 is out Wednesday (Oct 16) • It is due on Monday (Oct 14)

Administrative Stuff • HW 7 is out • It is due next Monday (Oct 21)

Administrative Stuff • Midterm Exam #2 • When: Monday October 28. • Where: This classroom • What: Chapters 1, 2, 3, 4 and 5. 1 -5. 4 • The exam will be open book and open notes (you can bring up to 3 pages of handwritten notes).

2 -1 Multiplexer (Definition) • Has two inputs: x 1 and x 2 • Also has another input line s • If s=0, then the output is equal to x 1 • If s=1, then the output is equal to x 2

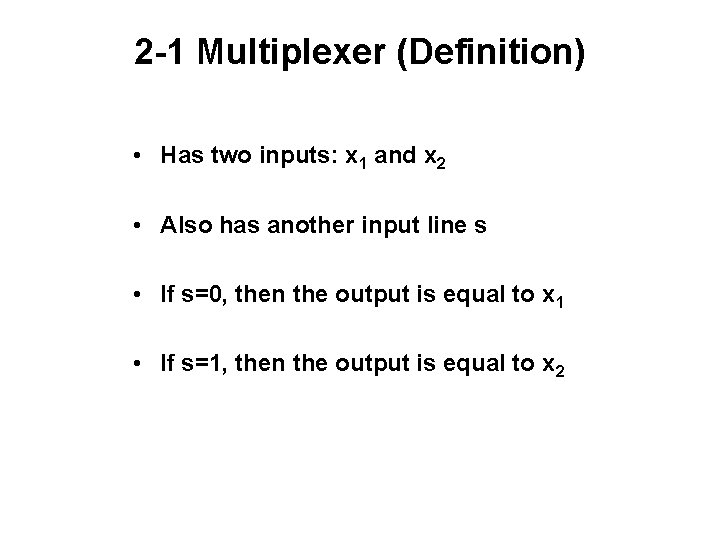

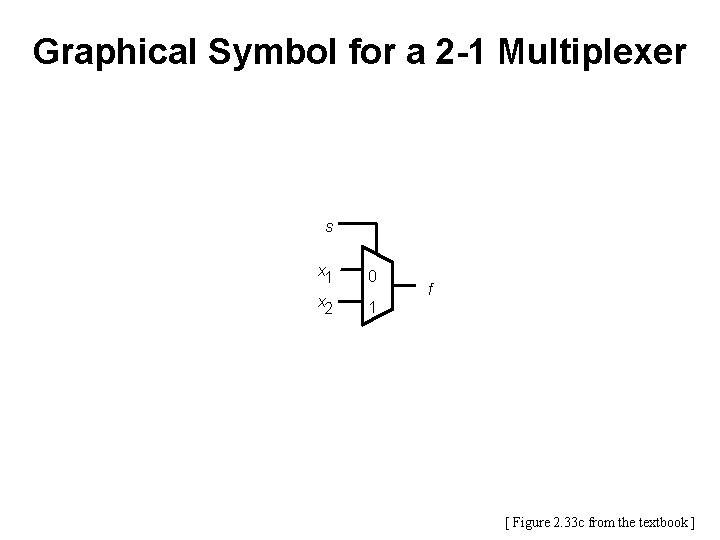

Graphical Symbol for a 2 -1 Multiplexer s x 1 0 x 2 1 f [ Figure 2. 33 c from the textbook ]

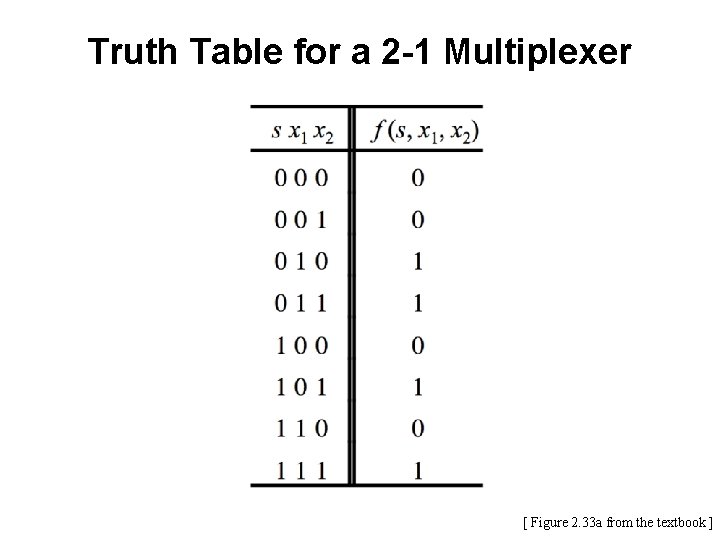

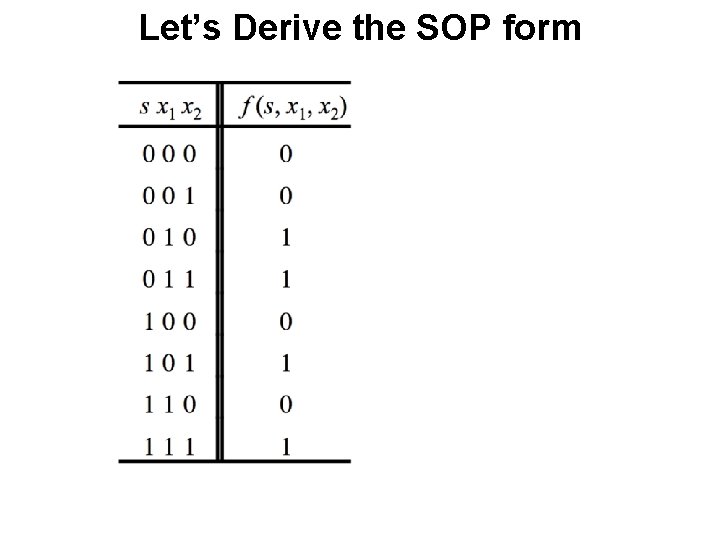

Truth Table for a 2 -1 Multiplexer [ Figure 2. 33 a from the textbook ]

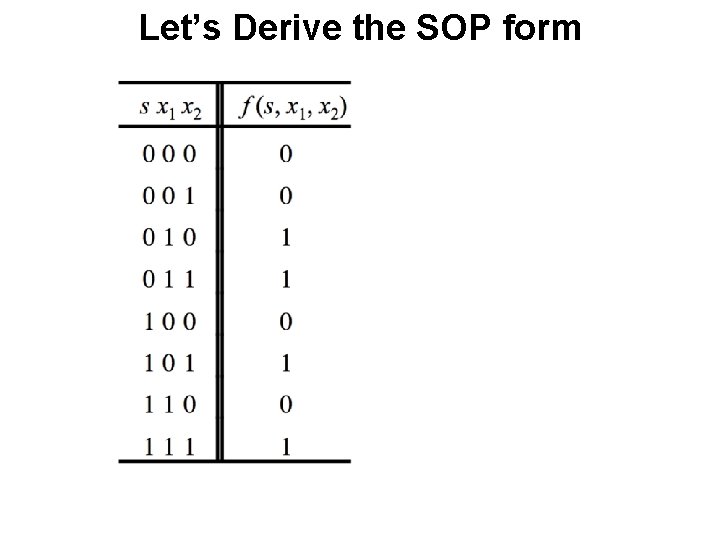

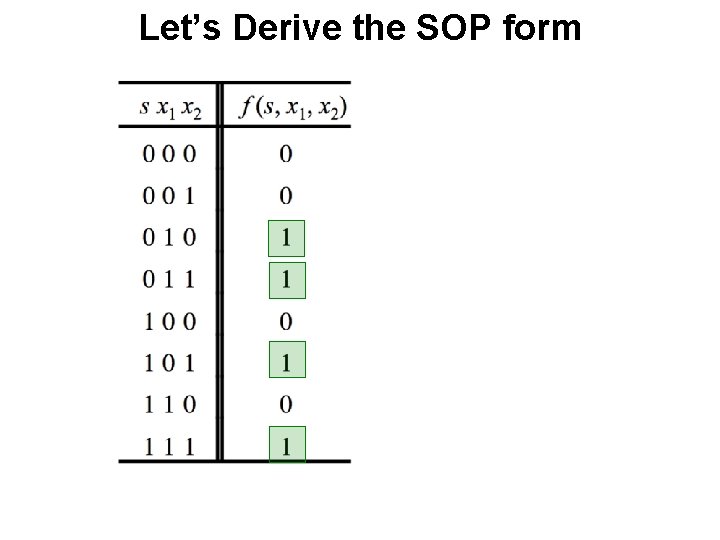

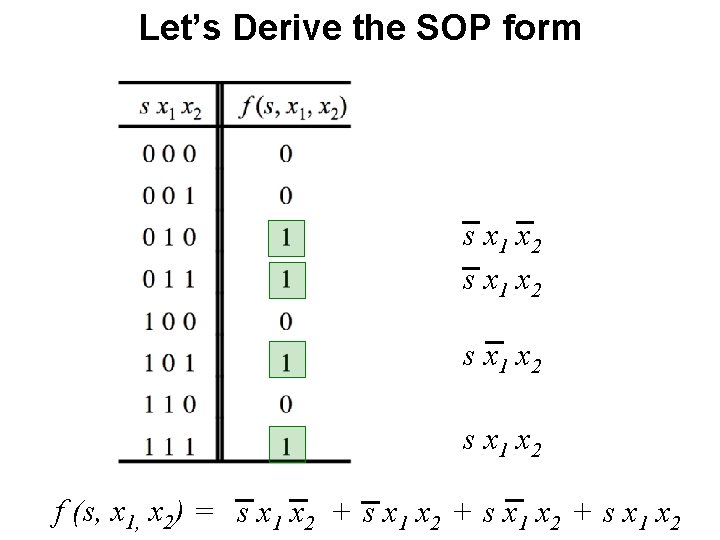

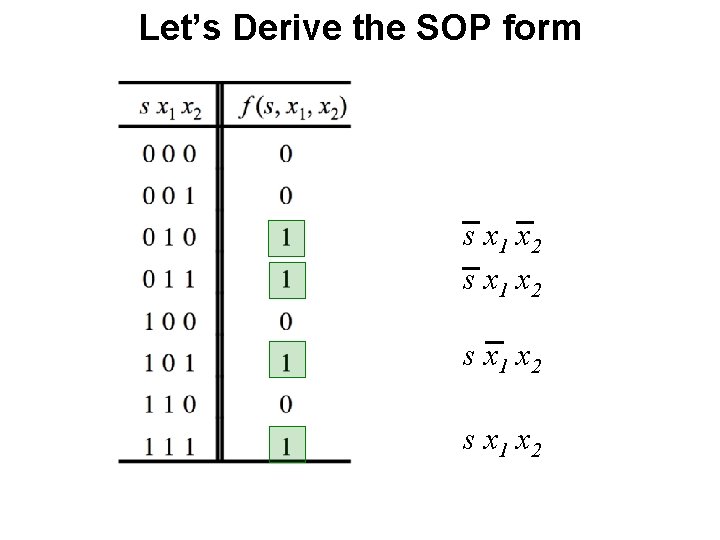

Let’s Derive the SOP form

Let’s Derive the SOP form

Let’s Derive the SOP form Where should we put the negation signs? s x 1 x 2

Let’s Derive the SOP form s x 1 x 2

Let’s Derive the SOP form s x 1 x 2 f (s, x 1, x 2) = s x 1 x 2 + s x 1 x 2

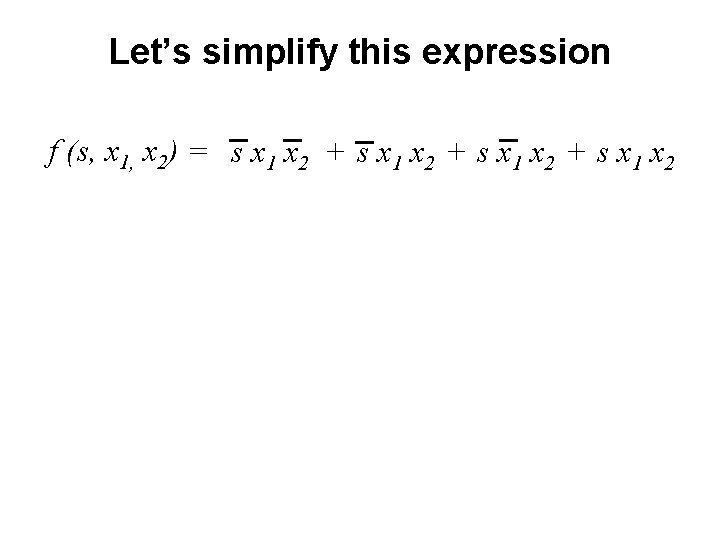

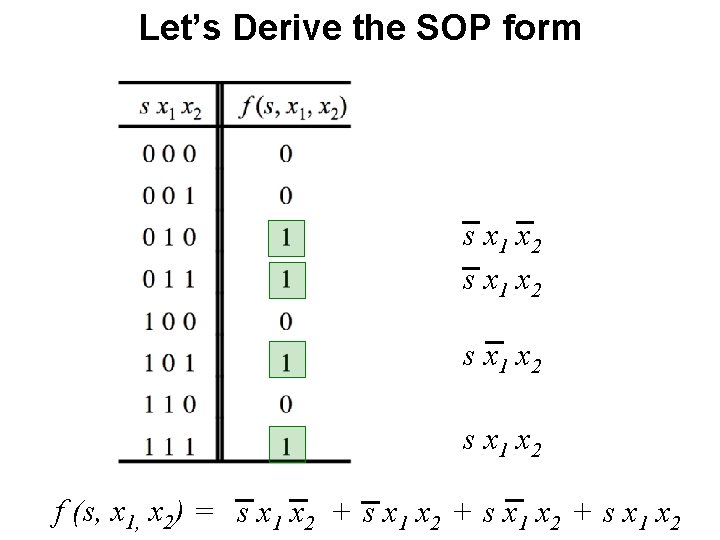

Let’s simplify this expression f (s, x 1, x 2) = s x 1 x 2 + s x 1 x 2

Let’s simplify this expression f (s, x 1, x 2) = s x 1 x 2 + s x 1 x 2 f (s, x 1, x 2) = s x 1 (x 2 + x 2) + s (x 1 +x 1 )x 2

Let’s simplify this expression f (s, x 1, x 2) = s x 1 x 2 + s x 1 x 2 f (s, x 1, x 2) = s x 1 (x 2 + x 2) + s (x 1 +x 1 )x 2 f (s, x 1, x 2) = s x 1 + s x 2

Circuit for 2 -1 Multiplexer x 1 s f s x 2 (b) Circuit x 1 0 x 2 1 f (c) Graphical symbol f (s, x 1, x 2) = s x 1 + s x 2 [ Figure 2. 33 b-c from the textbook ]

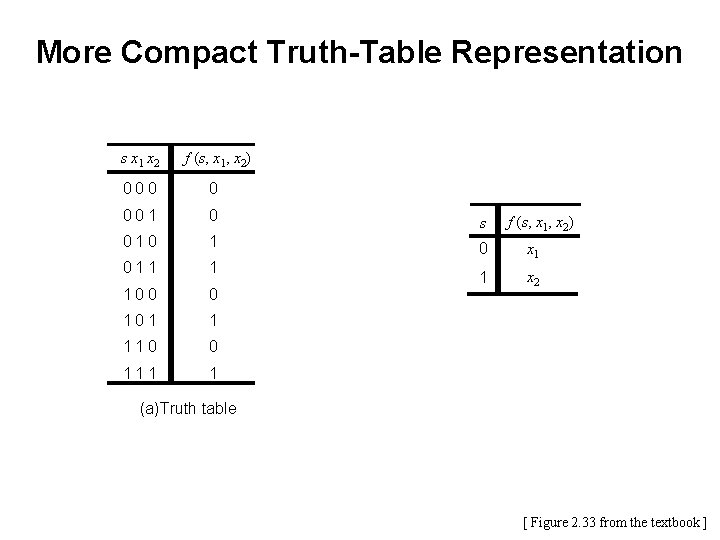

More Compact Truth-Table Representation s x 1 x 2 f (s, x 1, x 2) 000 0 001 0 s 010 1 0 011 1 x 1 100 0 1 x 2 101 1 110 0 111 1 f (s, x 1, x 2) (a)Truth table [ Figure 2. 33 from the textbook ]

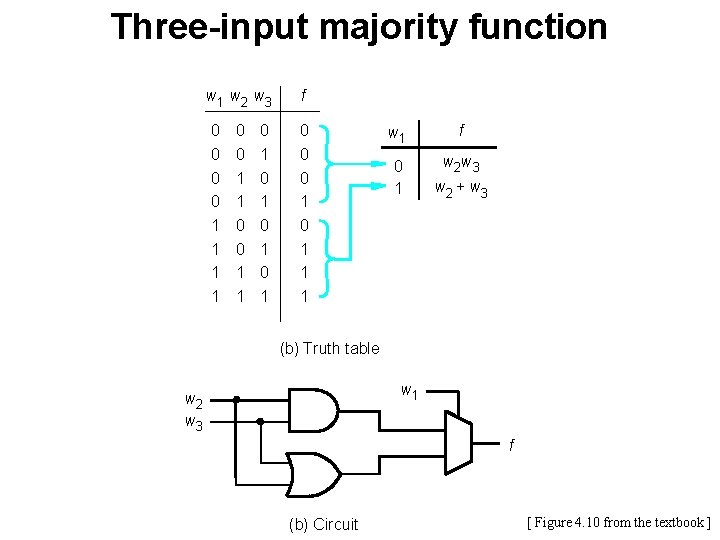

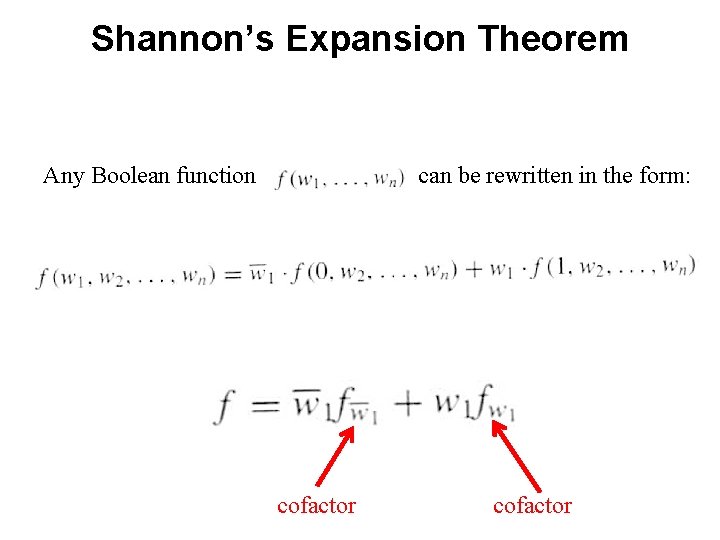

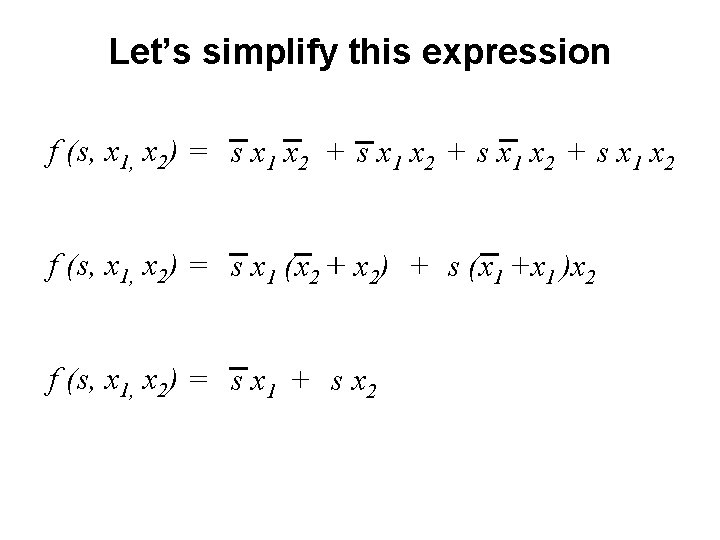

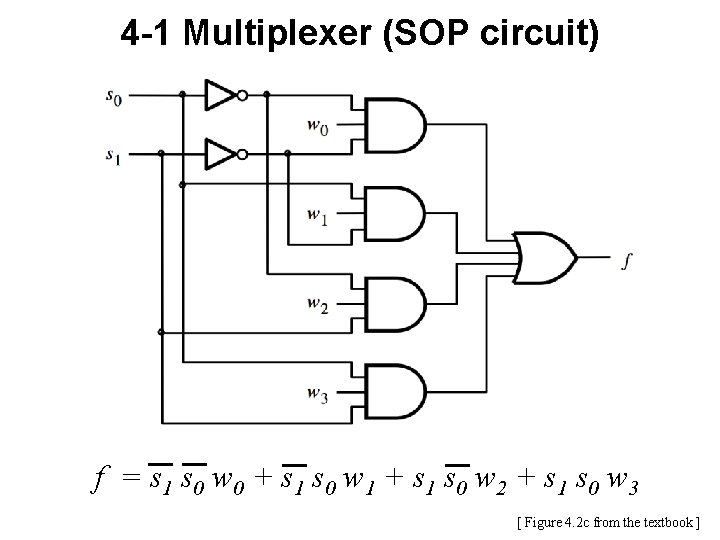

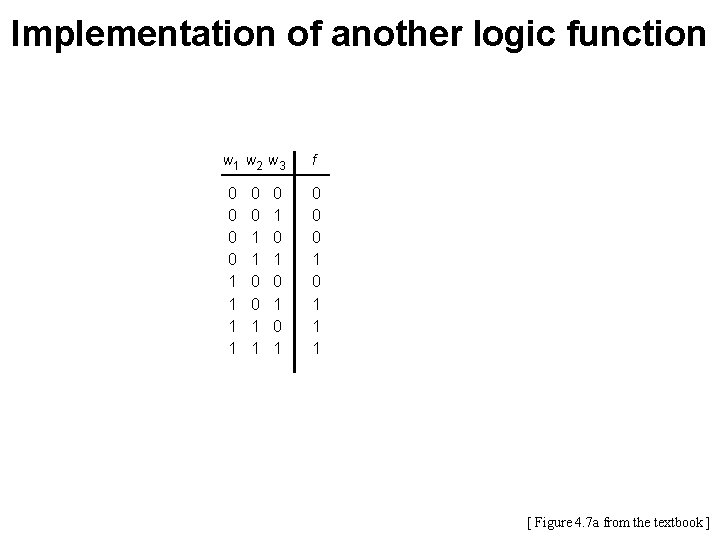

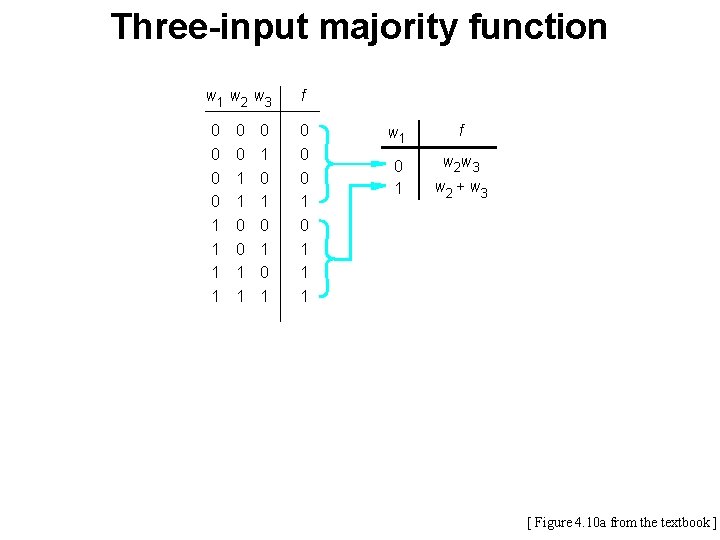

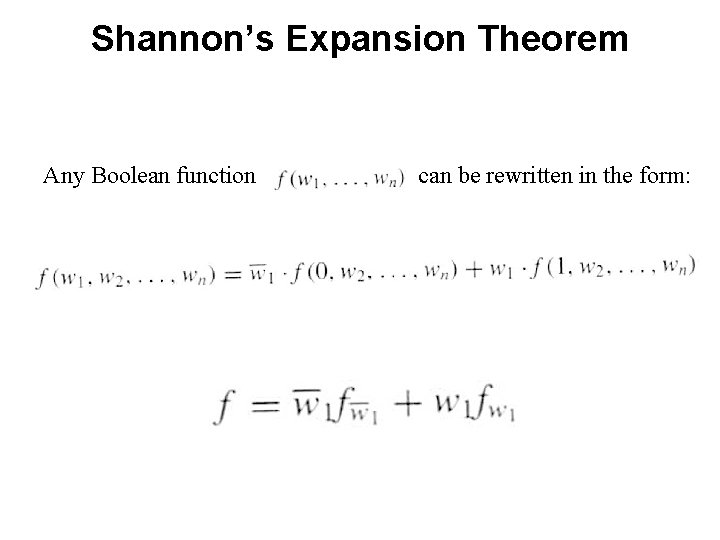

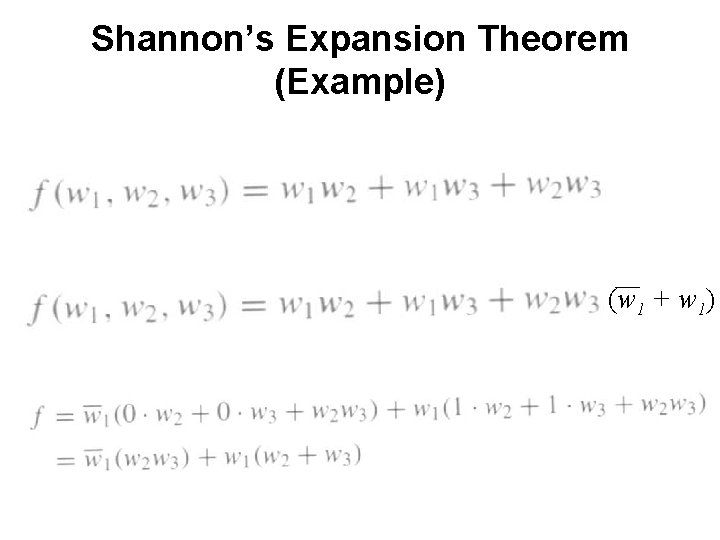

4 -1 Multiplexer (Definition) • Has four inputs: w 0 , w 1, w 2, w 3 • Also has two select lines: s 1 and s 0 • • If s 1=0 and s 0=0, then the output f is equal to w 0 If s 1=0 and s 0=1, then the output f is equal to w 1 If s 1=1 and s 0=0, then the output f is equal to w 2 If s 1=1 and s 0=1, then the output f is equal to w 3

![Graphical Symbol and Truth Table Figure 4 2 ab from the textbook Graphical Symbol and Truth Table [ Figure 4. 2 a-b from the textbook ]](https://slidetodoc.com/presentation_image_h/a31d07ff4ba9b19801471c89b07be575/image-20.jpg)

Graphical Symbol and Truth Table [ Figure 4. 2 a-b from the textbook ]

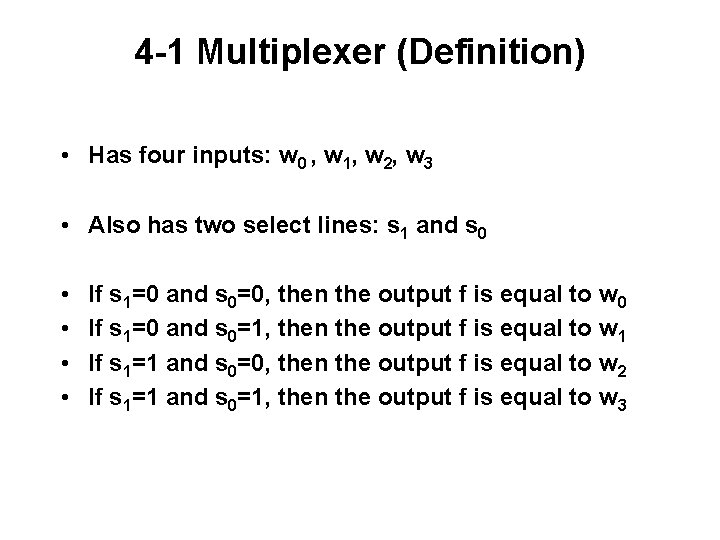

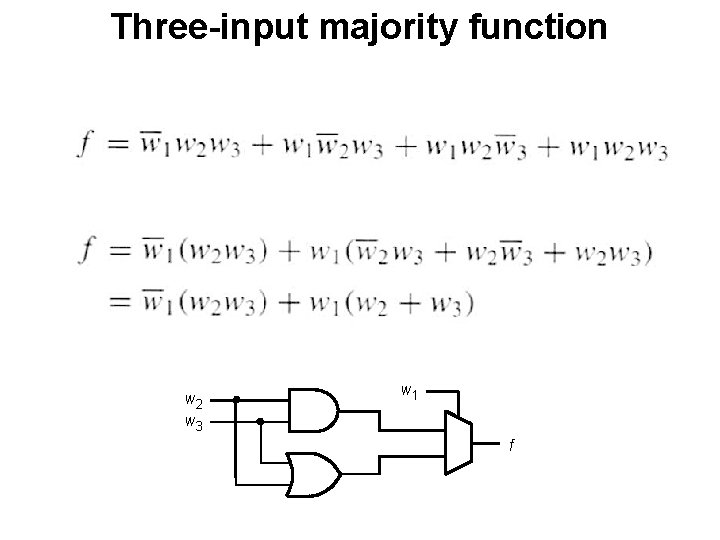

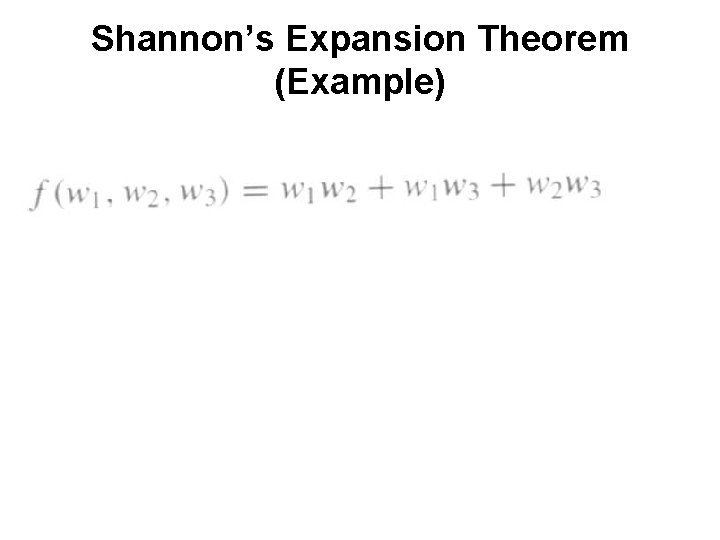

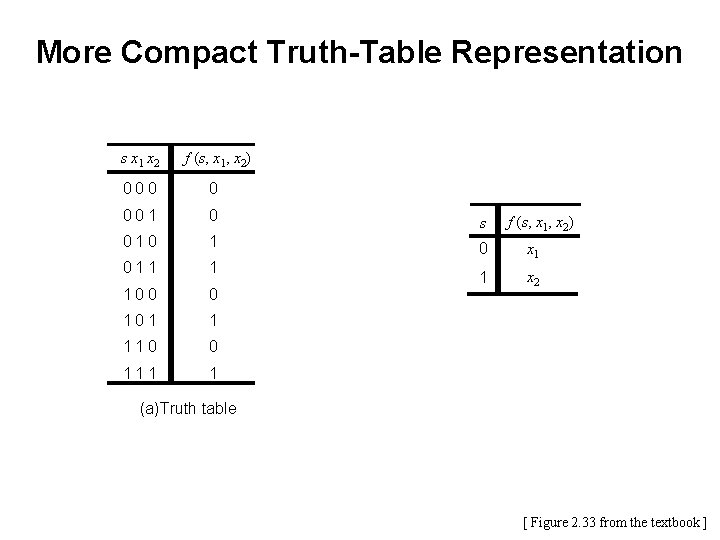

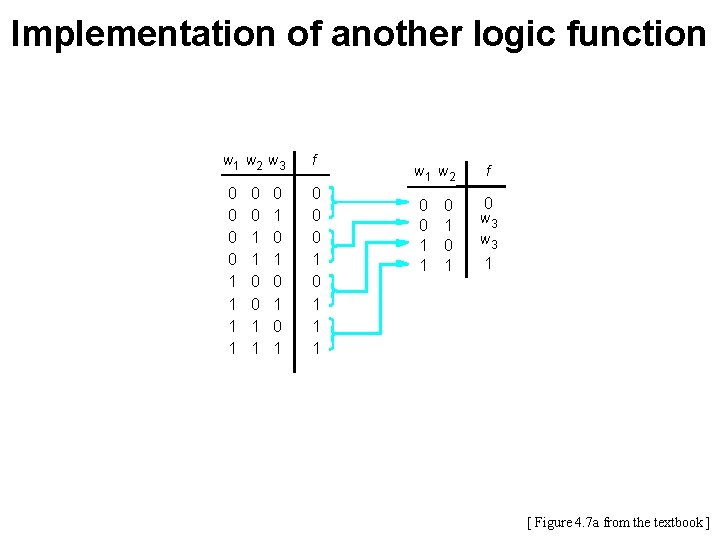

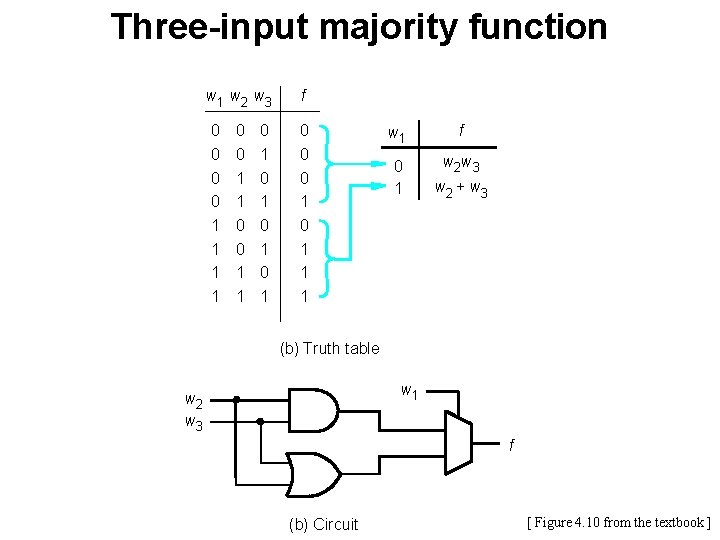

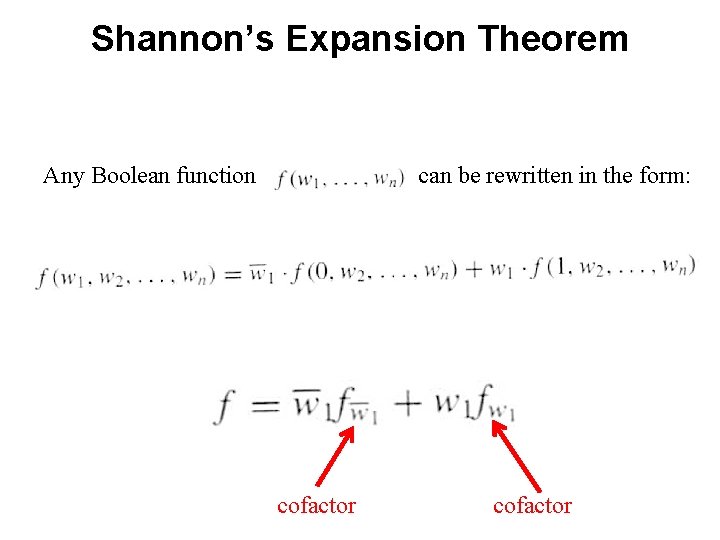

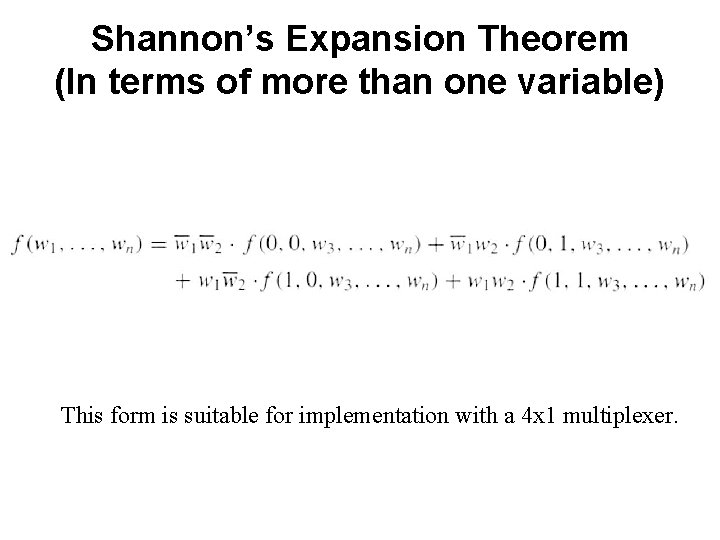

The long-form truth table

![The longform truth table http www absoluteastronomy comtopicsMultiplexer The long-form truth table [http: //www. absoluteastronomy. com/topics/Multiplexer]](https://slidetodoc.com/presentation_image_h/a31d07ff4ba9b19801471c89b07be575/image-22.jpg)

The long-form truth table [http: //www. absoluteastronomy. com/topics/Multiplexer]

4 -1 Multiplexer (SOP circuit) f = s 1 s 0 w 0 + s 1 s 0 w 1 + s 1 s 0 w 2 + s 1 s 0 w 3 [ Figure 4. 2 c from the textbook ]

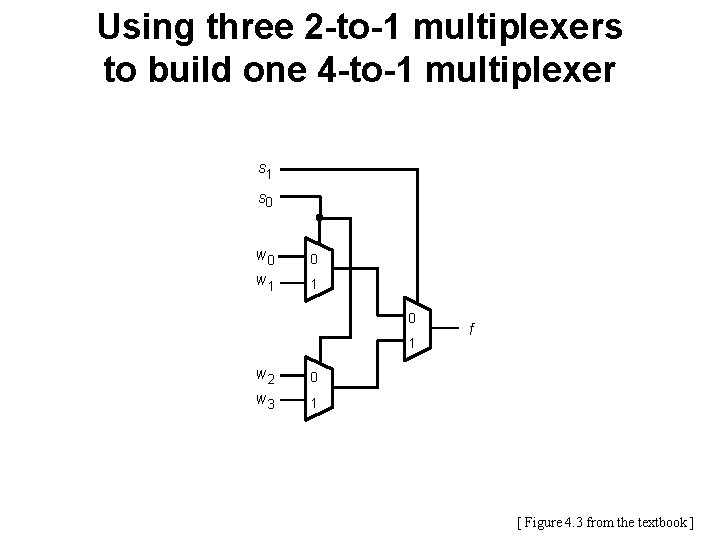

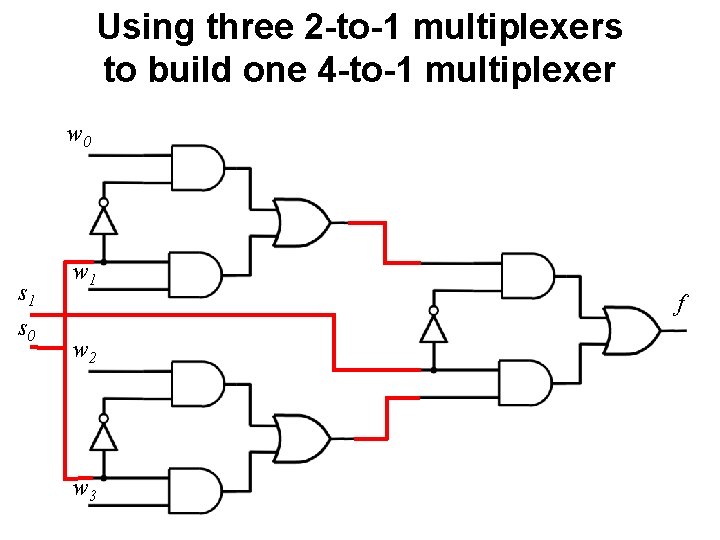

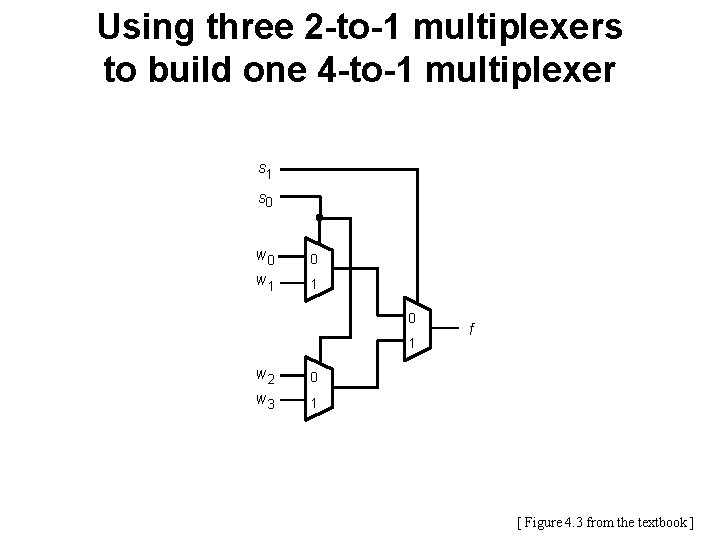

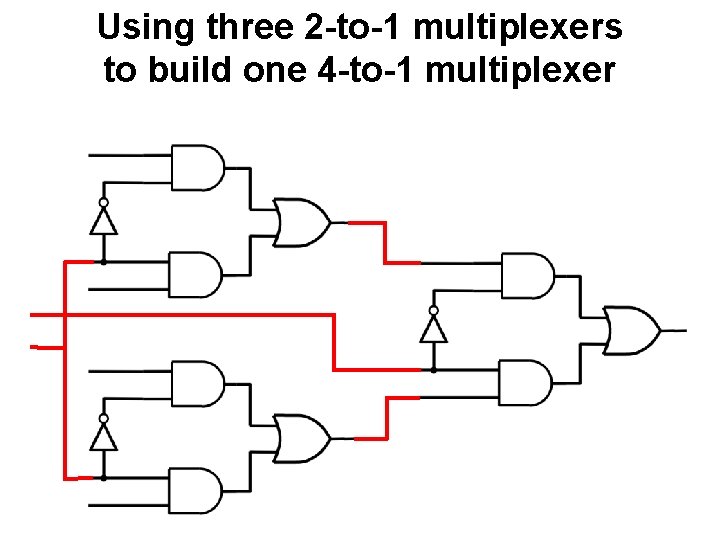

Using three 2 -to-1 multiplexers to build one 4 -to-1 multiplexer s 1 s 0 w 0 0 w 1 1 0 1 w 2 0 w 3 1 f [ Figure 4. 3 from the textbook ]

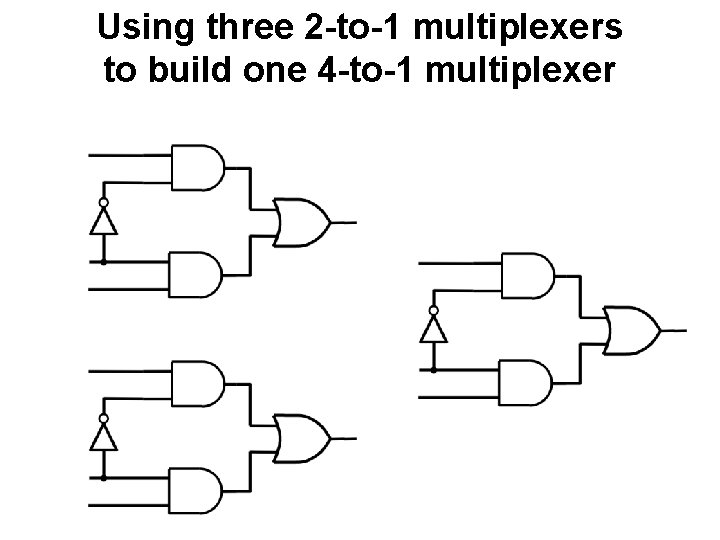

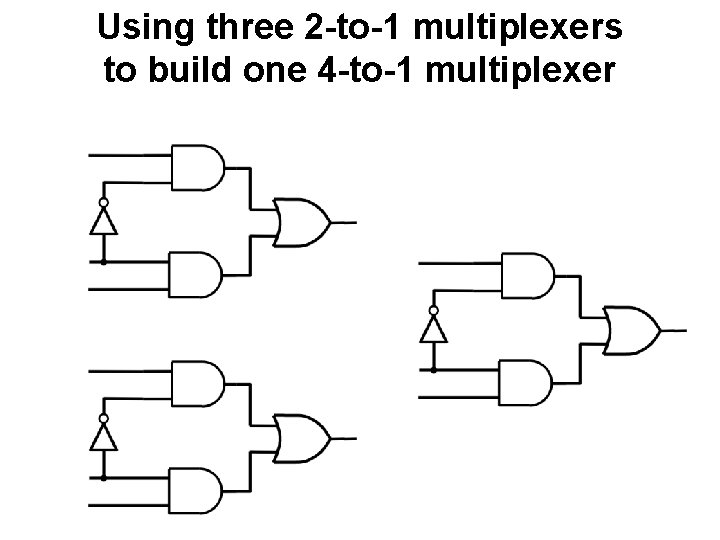

Using three 2 -to-1 multiplexers to build one 4 -to-1 multiplexer

Using three 2 -to-1 multiplexers to build one 4 -to-1 multiplexer

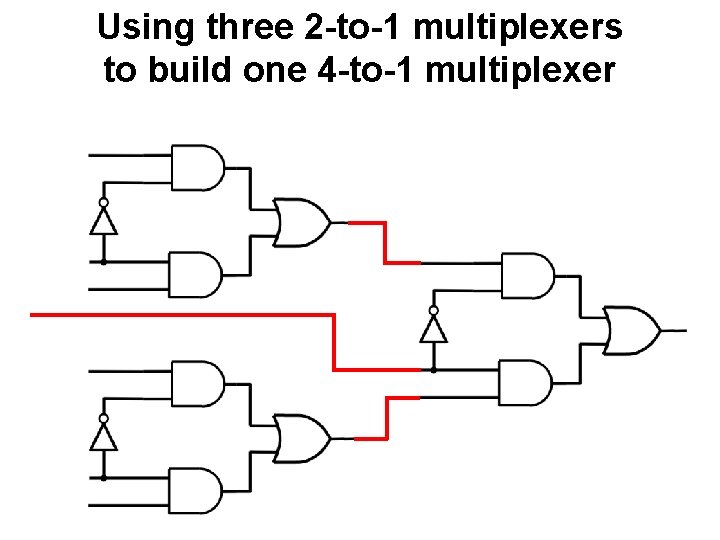

Using three 2 -to-1 multiplexers to build one 4 -to-1 multiplexer

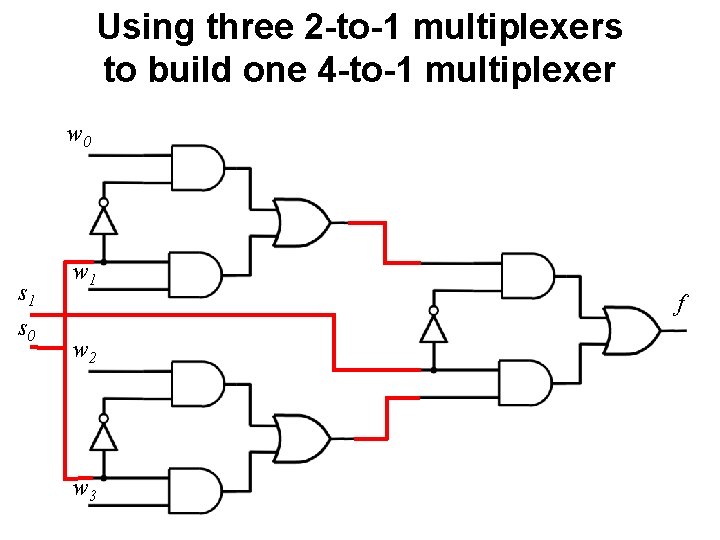

Using three 2 -to-1 multiplexers to build one 4 -to-1 multiplexer w 0 s 1 s 0 w 1 f w 2 w 3

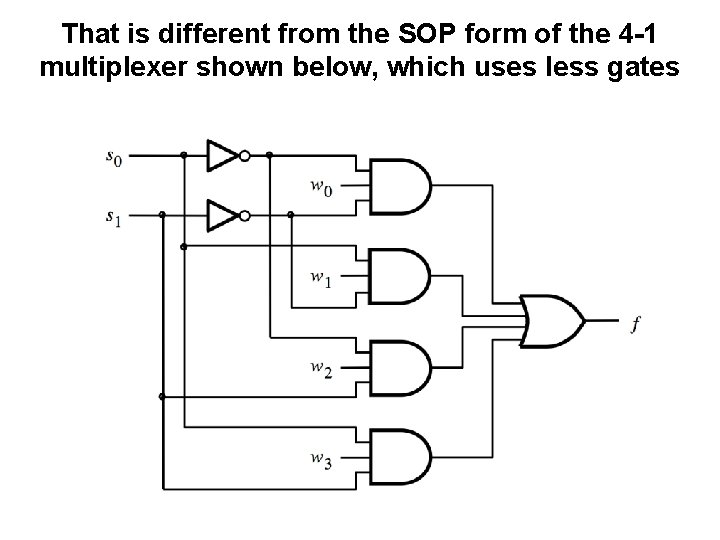

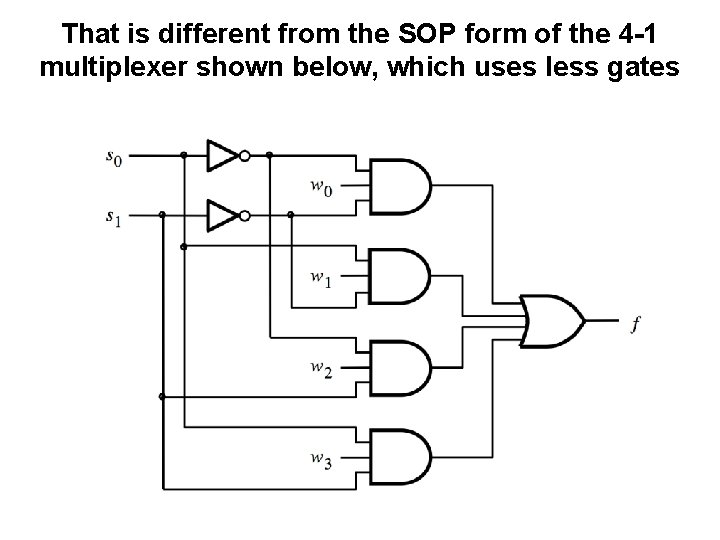

That is different from the SOP form of the 4 -1 multiplexer shown below, which uses less gates

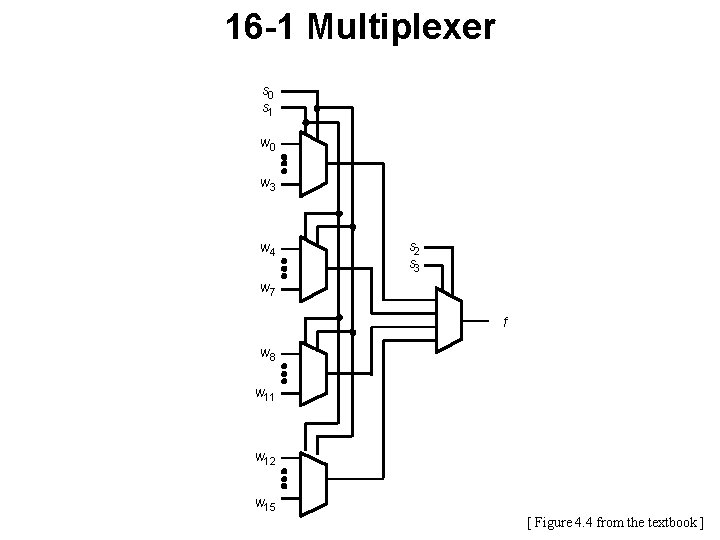

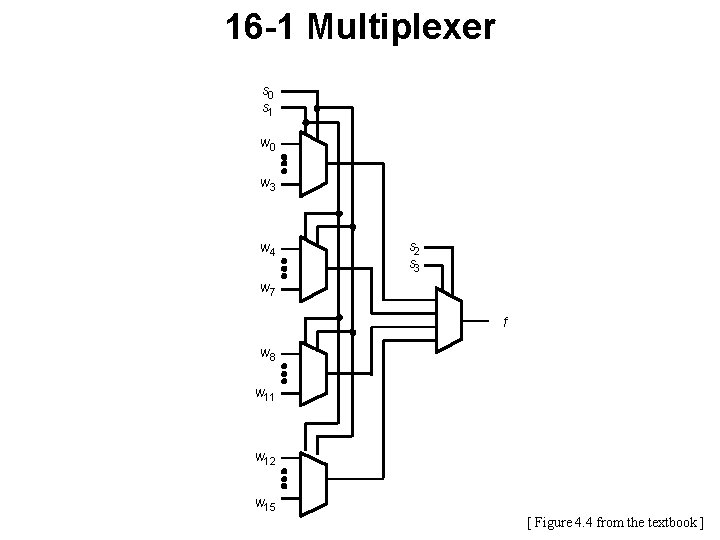

16 -1 Multiplexer s 0 s 1 w 0 w 3 w 4 s 2 s 3 w 7 f w 8 w 11 w 12 w 15 [ Figure 4. 4 from the textbook ]

Synthesis of Logic Circuits Using Multiplexers

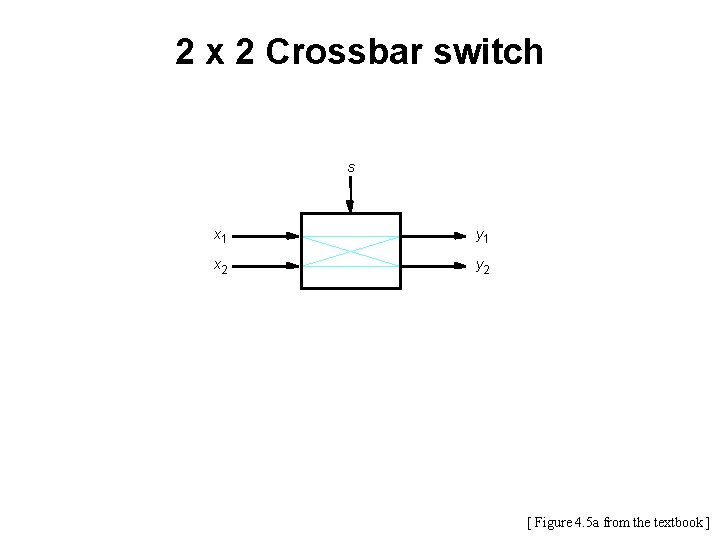

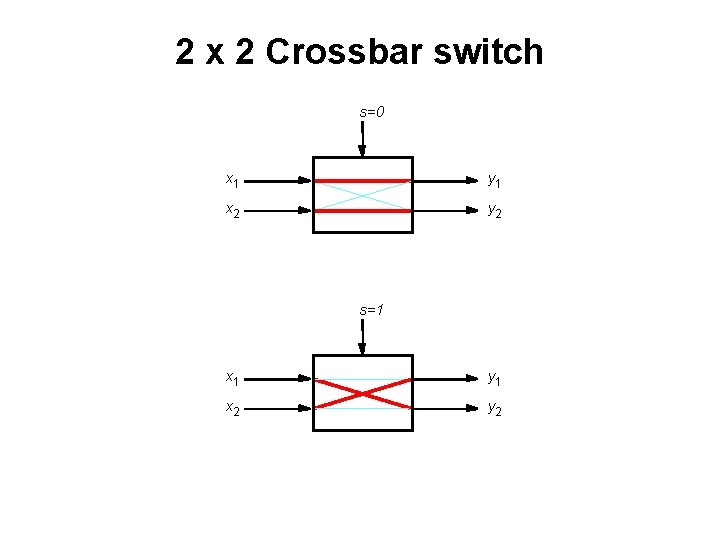

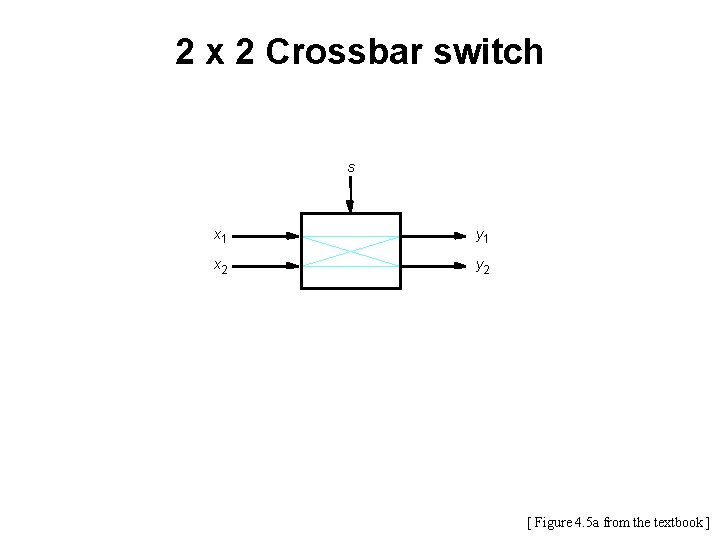

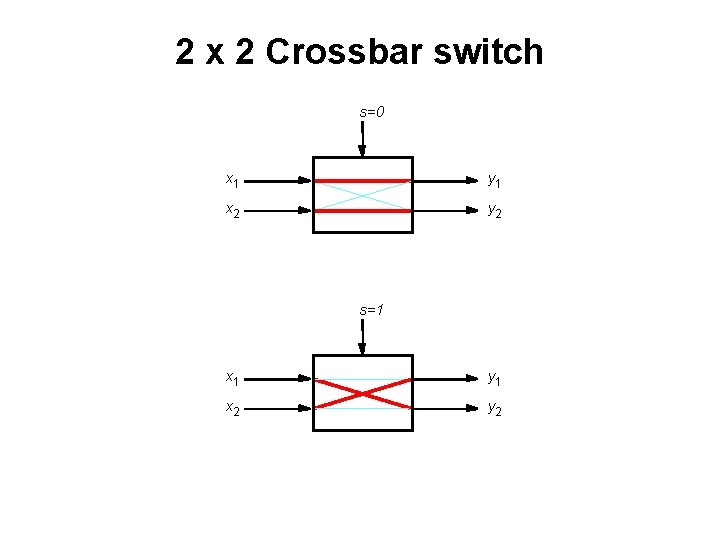

2 x 2 Crossbar switch s x 1 y 1 x 2 y 2 [ Figure 4. 5 a from the textbook ]

2 x 2 Crossbar switch s=0 x 1 y 1 x 2 y 2 s=1 x 1 y 1 x 2 y 2

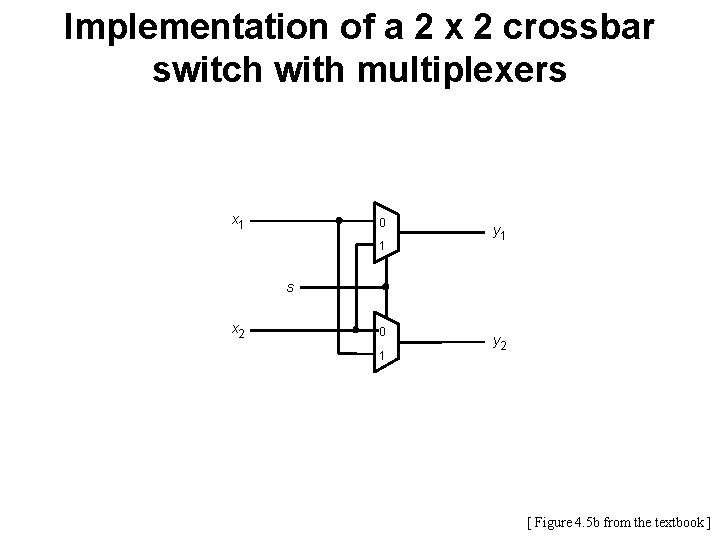

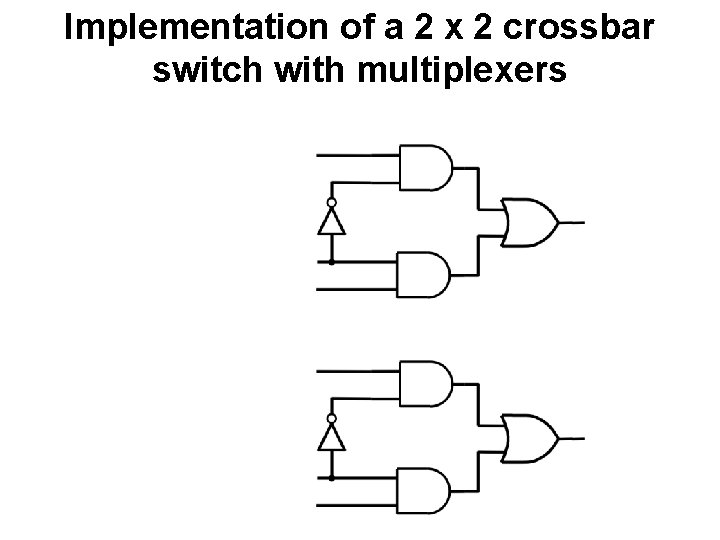

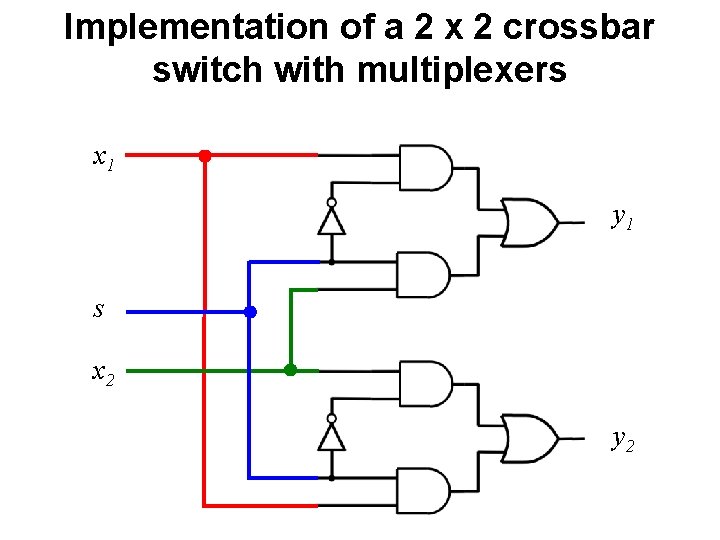

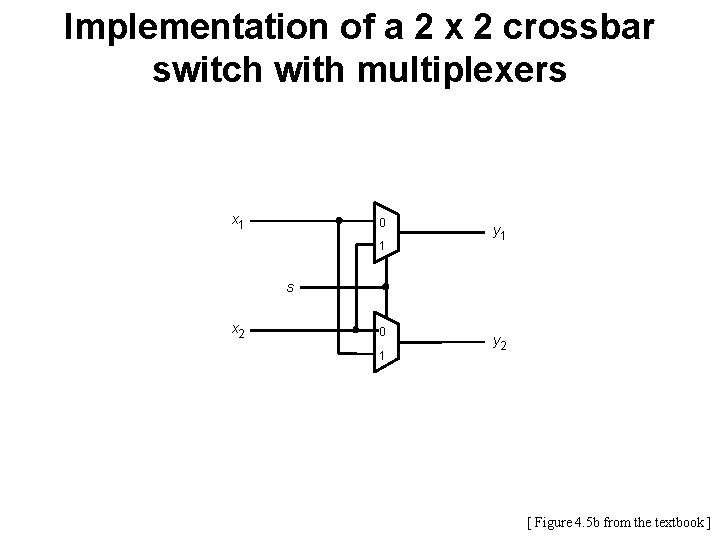

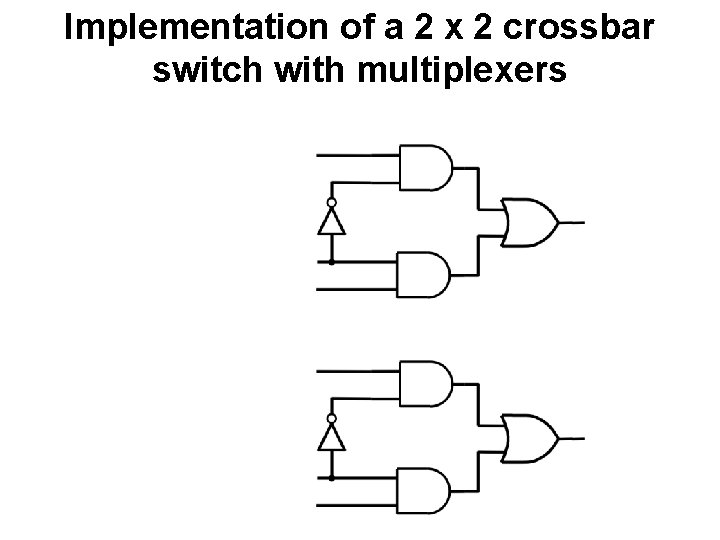

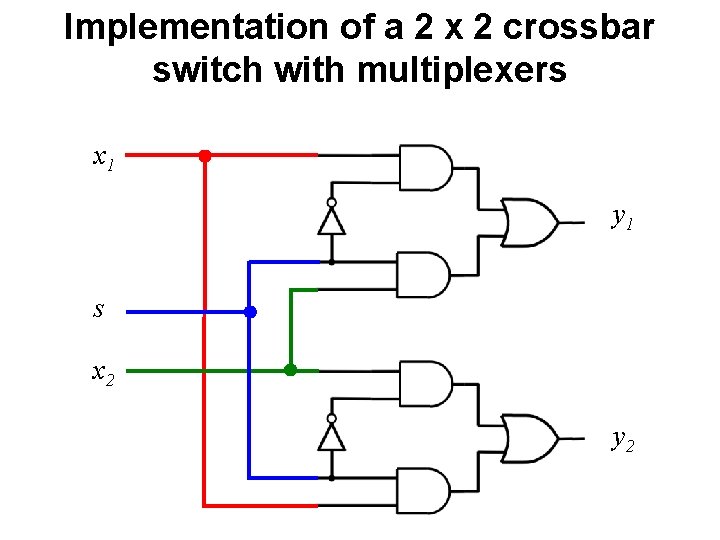

Implementation of a 2 x 2 crossbar switch with multiplexers x 1 0 1 y 1 s x 2 0 1 y 2 [ Figure 4. 5 b from the textbook ]

Implementation of a 2 x 2 crossbar switch with multiplexers

Implementation of a 2 x 2 crossbar switch with multiplexers x 1 y 1 s x 2 y 2

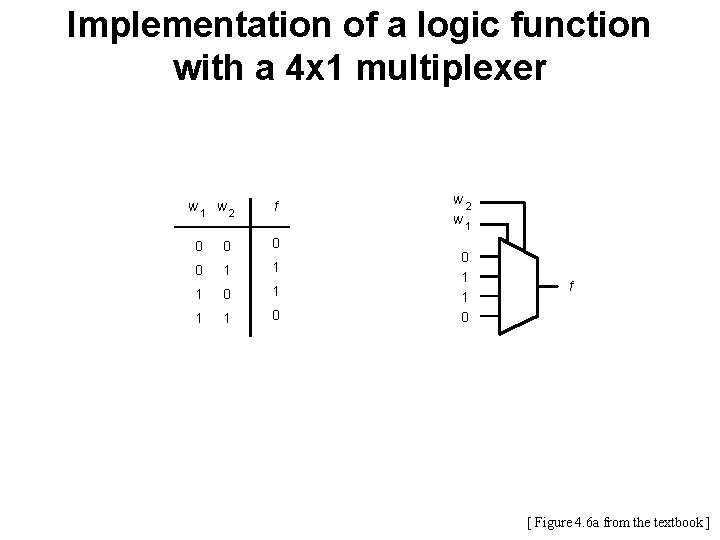

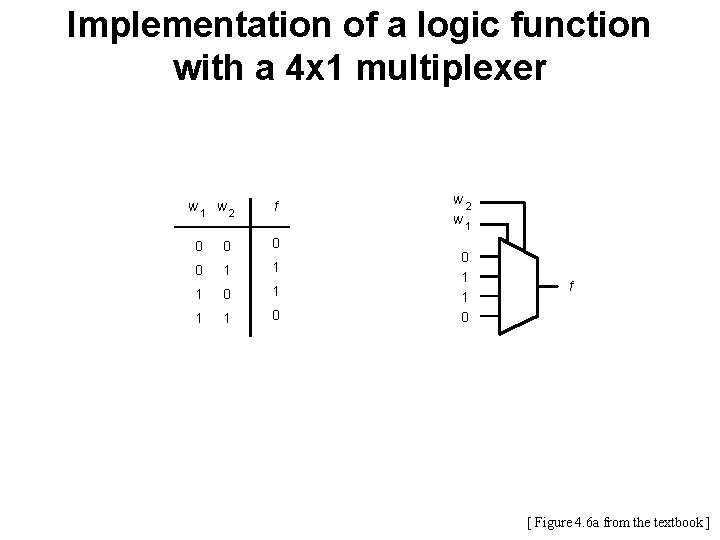

Implementation of a logic function with a 4 x 1 multiplexer w 1 w 2 f 0 0 1 1 1 0 w 2 w 1 0 1 1 0 f [ Figure 4. 6 a from the textbook ]

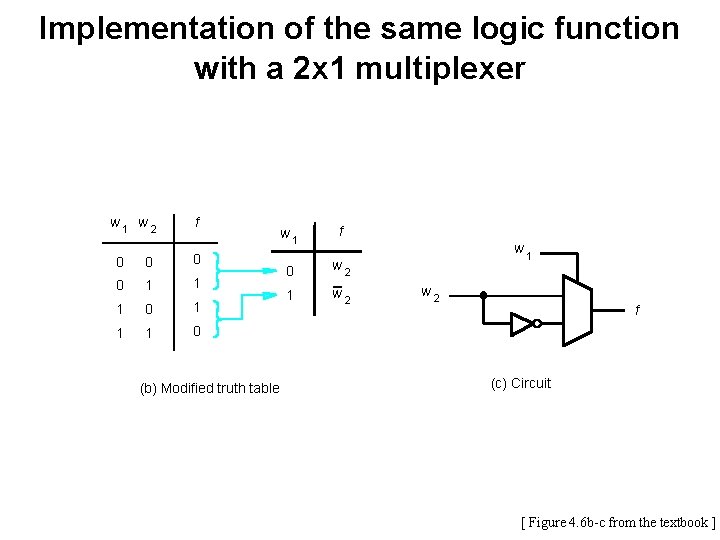

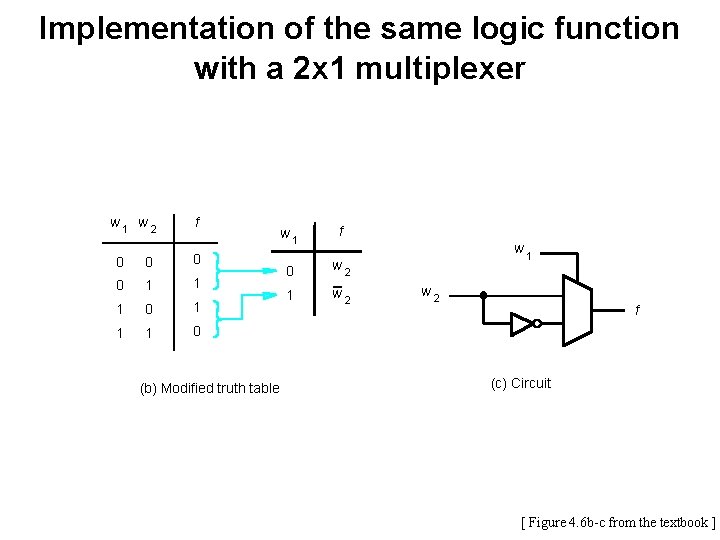

Implementation of the same logic function with a 2 x 1 multiplexer w 1 w 2 f 0 0 1 1 1 0 (b) Modified truth table w 1 f 0 w 2 1 w 2 w 1 w 2 f (c) Circuit [ Figure 4. 6 b-c from the textbook ]

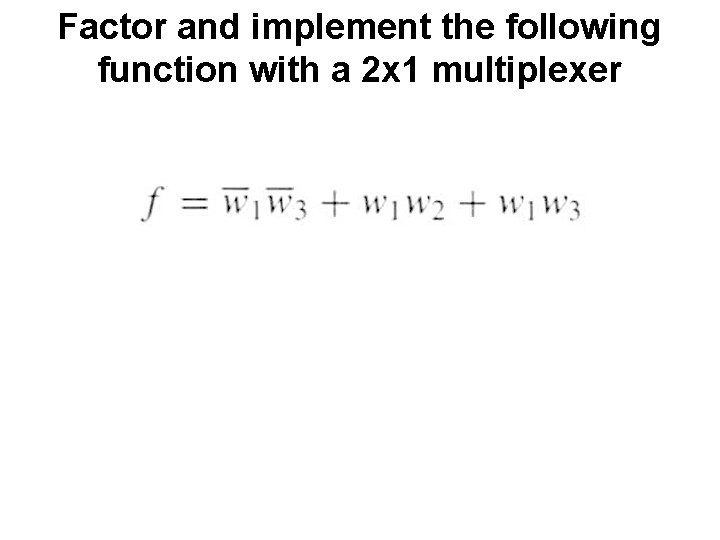

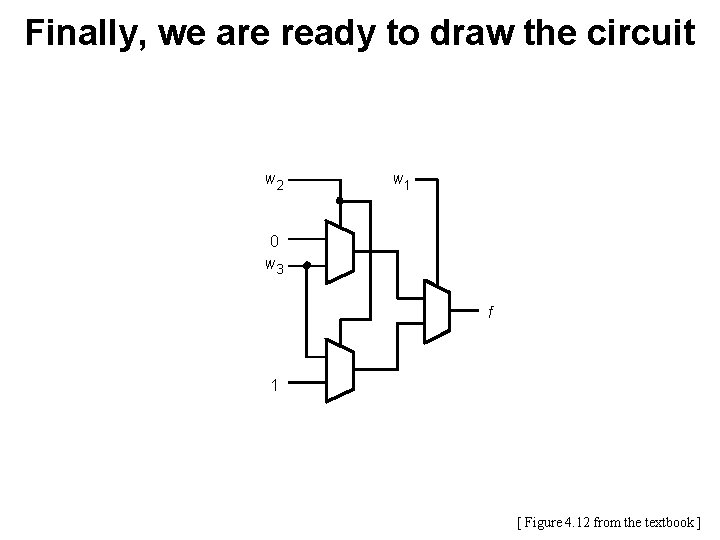

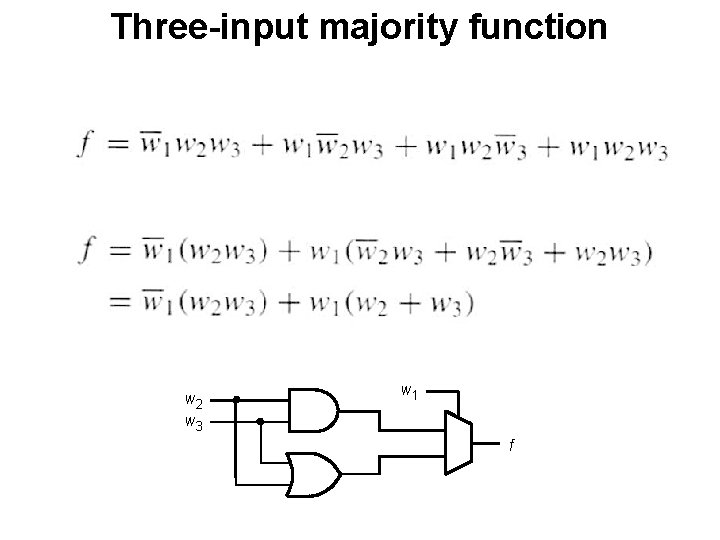

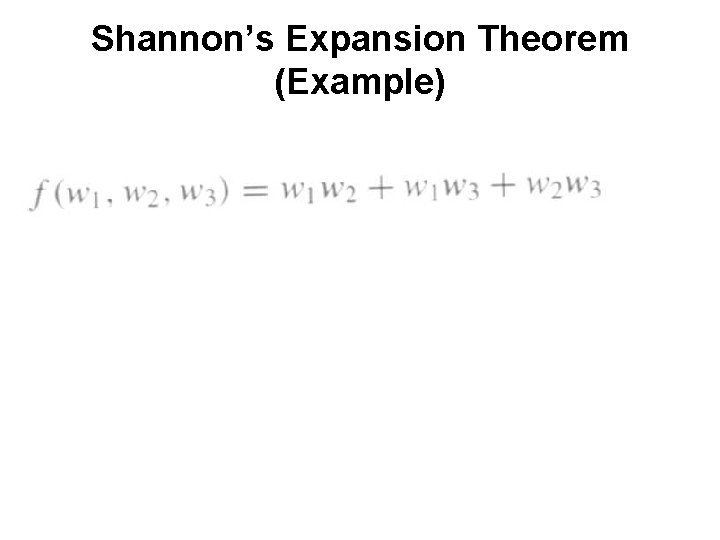

![The XOR Logic Gate Figure 2 11 from the textbook The XOR Logic Gate [ Figure 2. 11 from the textbook ]](https://slidetodoc.com/presentation_image_h/a31d07ff4ba9b19801471c89b07be575/image-39.jpg)

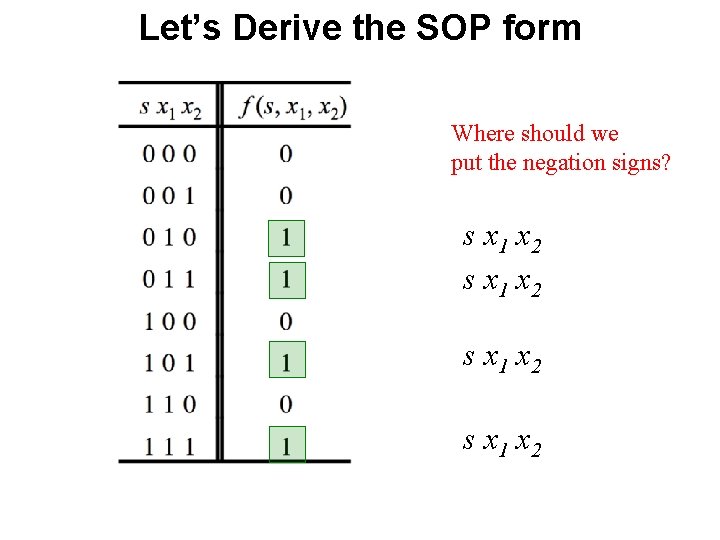

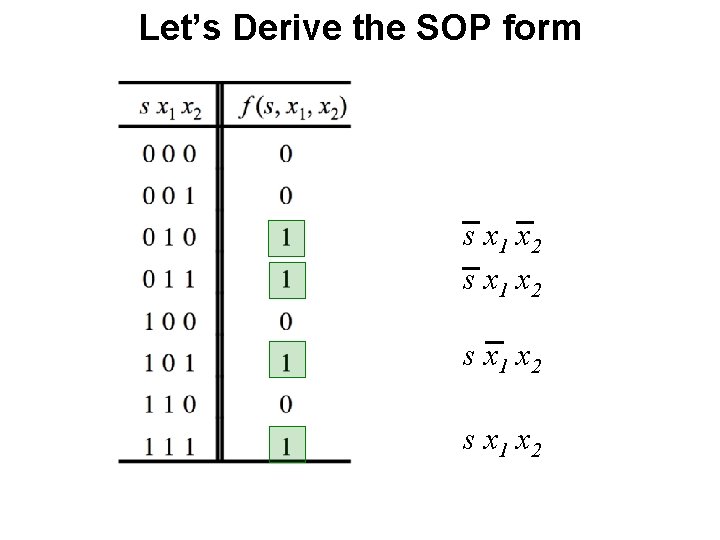

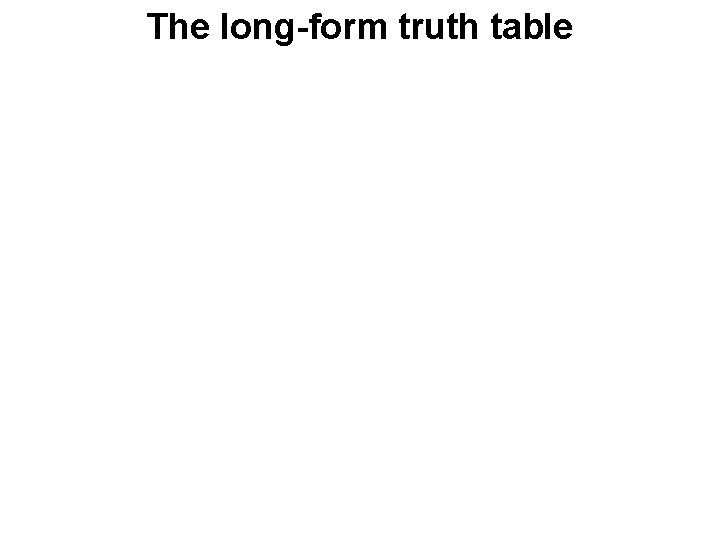

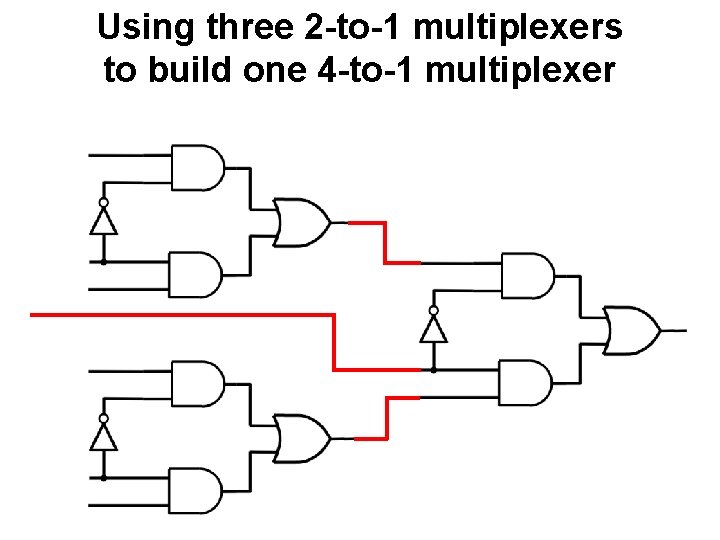

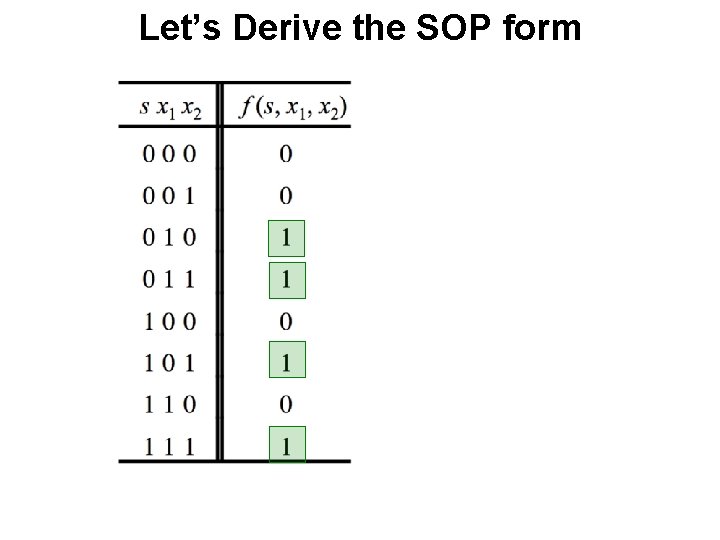

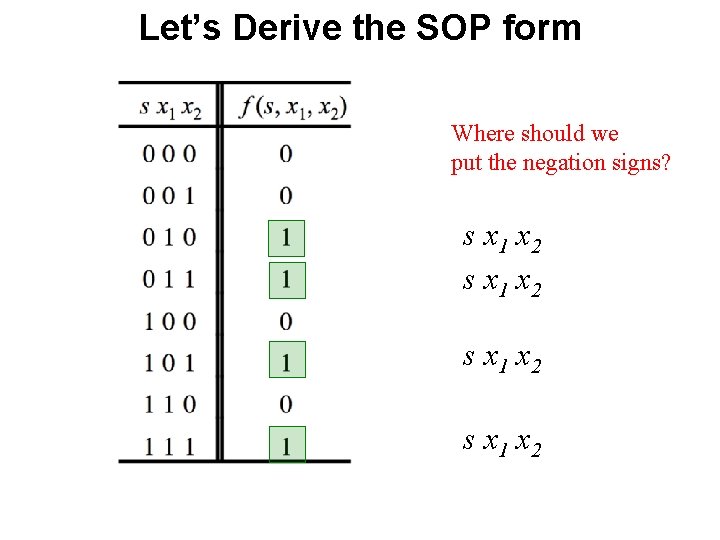

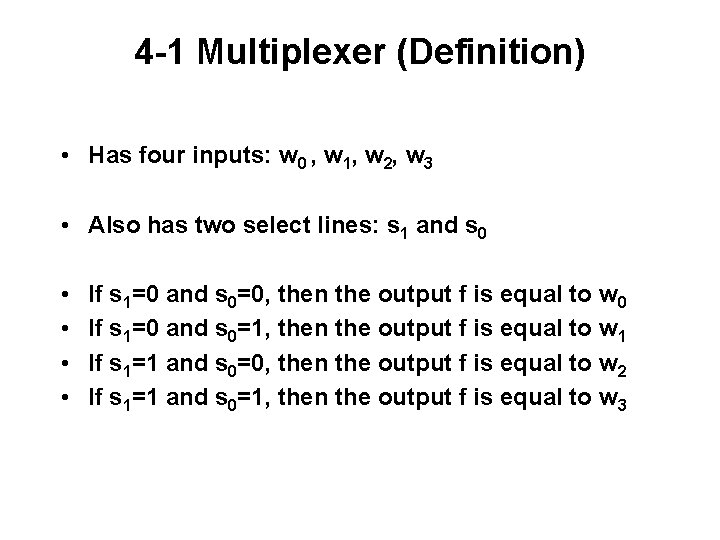

The XOR Logic Gate [ Figure 2. 11 from the textbook ]

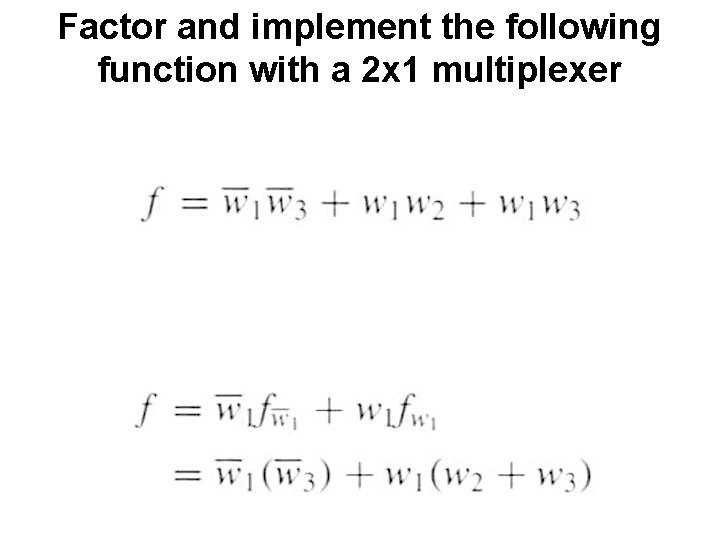

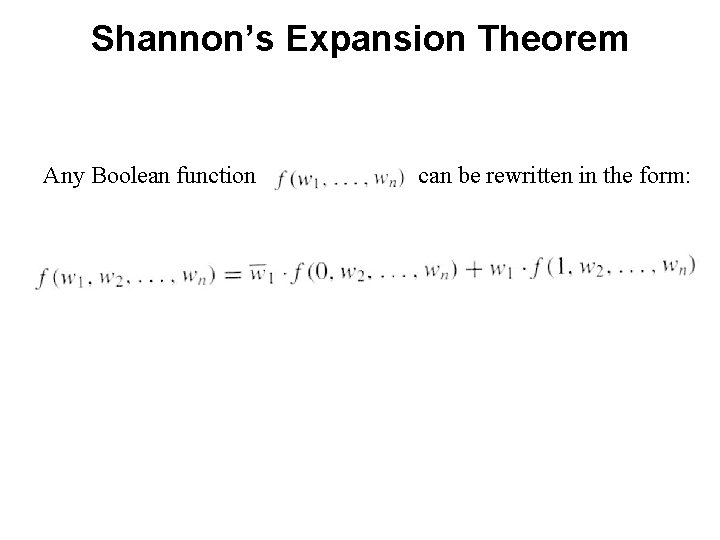

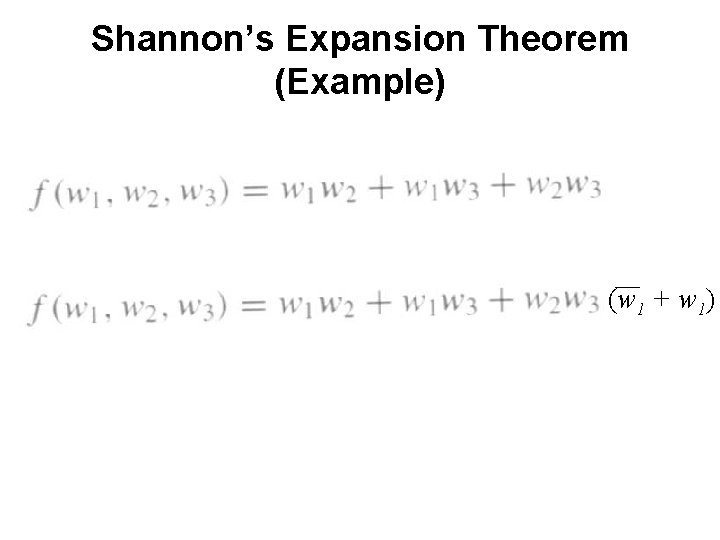

![The XOR Logic Gate Figure 2 11 from the textbook The XOR Logic Gate [ Figure 2. 11 from the textbook ]](https://slidetodoc.com/presentation_image_h/a31d07ff4ba9b19801471c89b07be575/image-40.jpg)

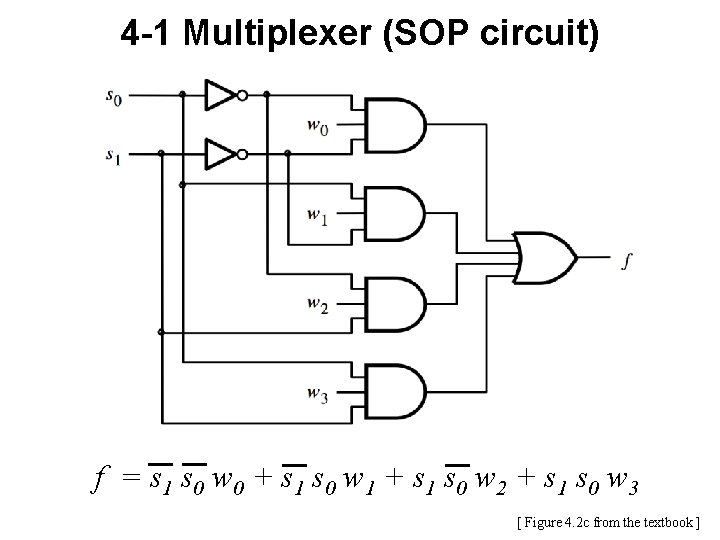

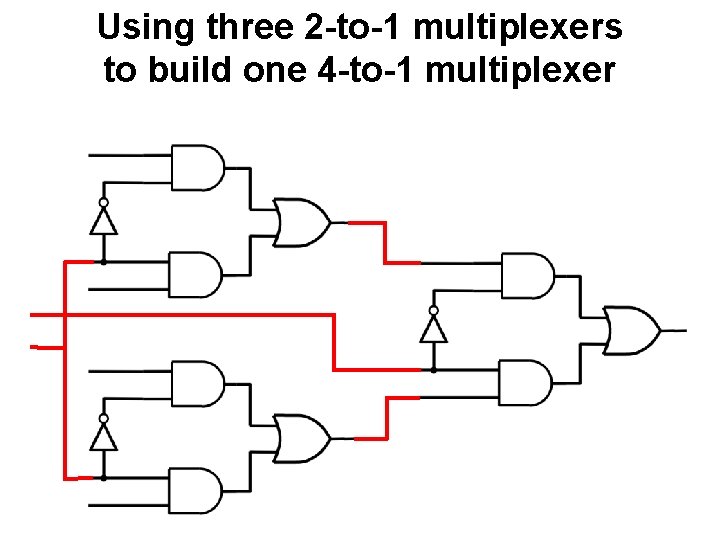

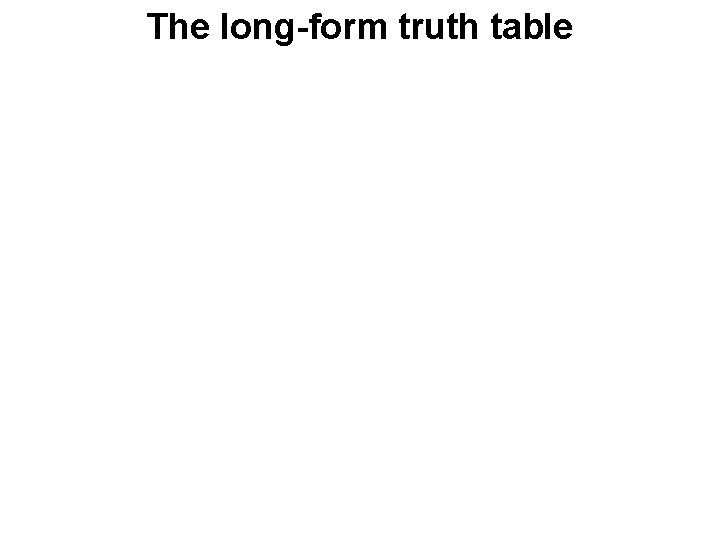

The XOR Logic Gate [ Figure 2. 11 from the textbook ]

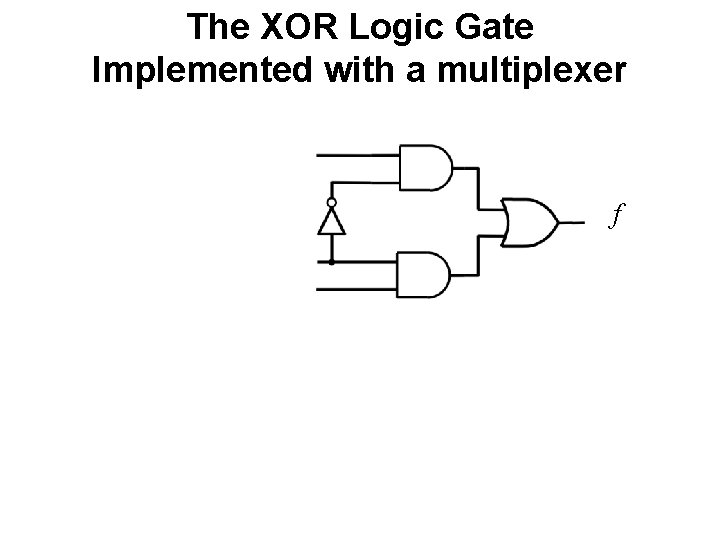

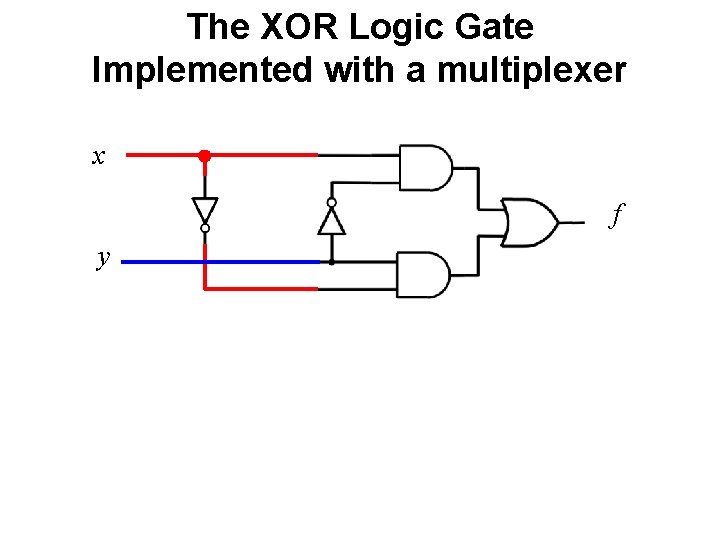

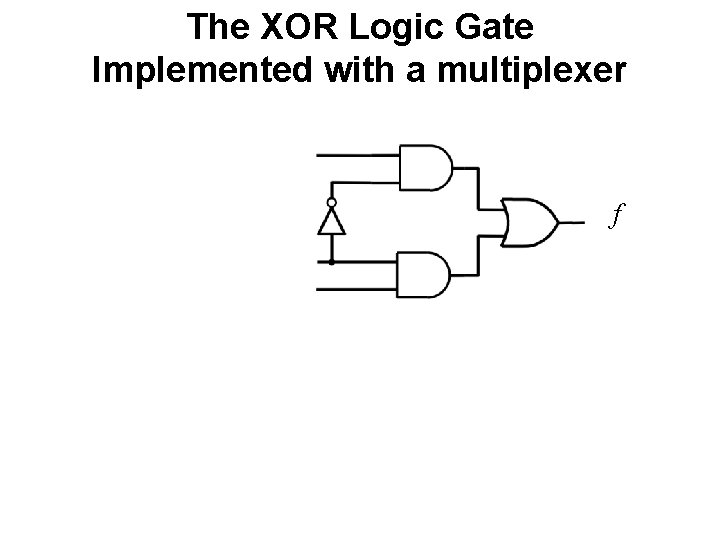

The XOR Logic Gate Implemented with a multiplexer f

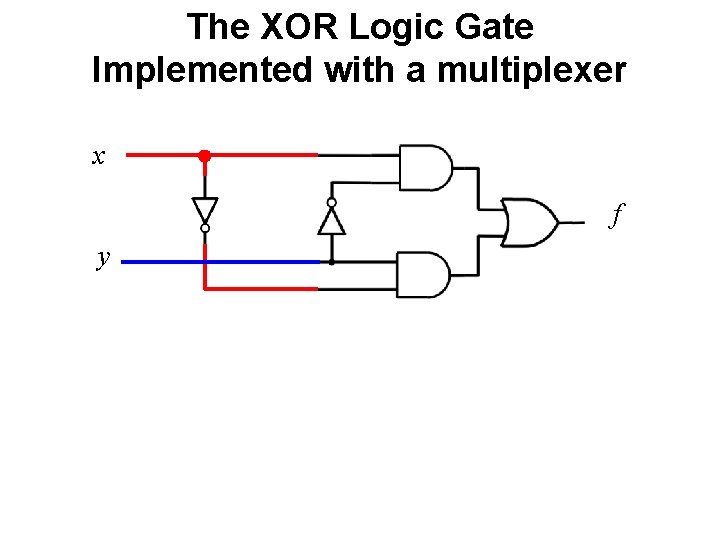

The XOR Logic Gate Implemented with a multiplexer x f y

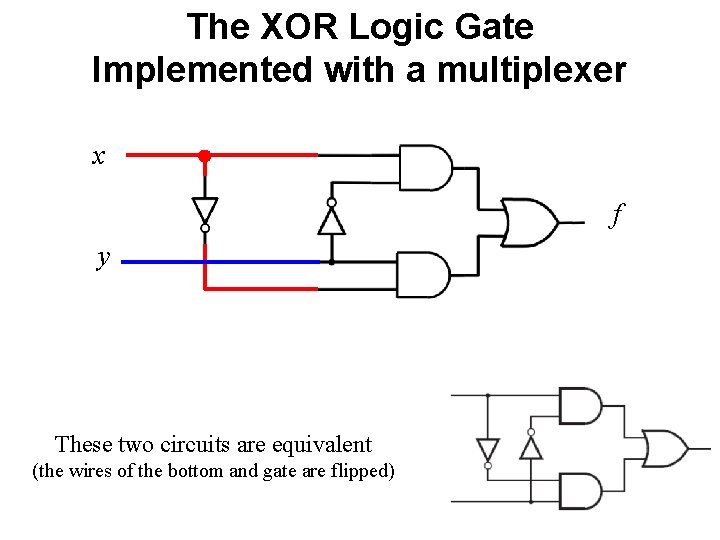

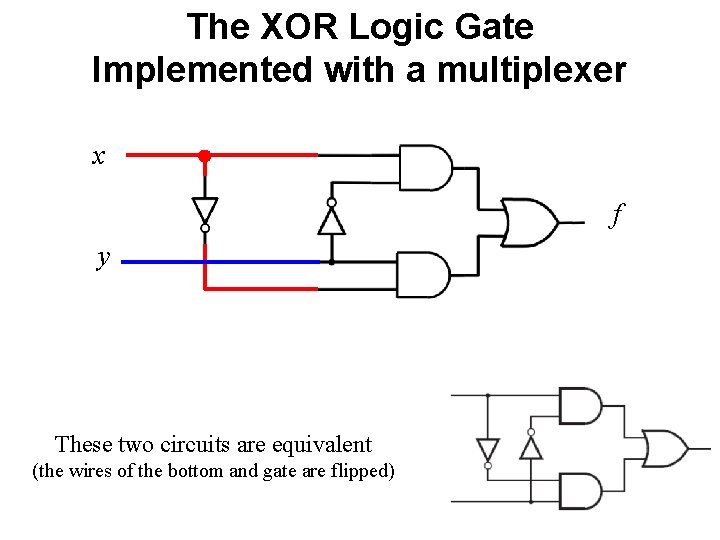

The XOR Logic Gate Implemented with a multiplexer x f y These two circuits are equivalent (the wires of the bottom and gate are flipped)

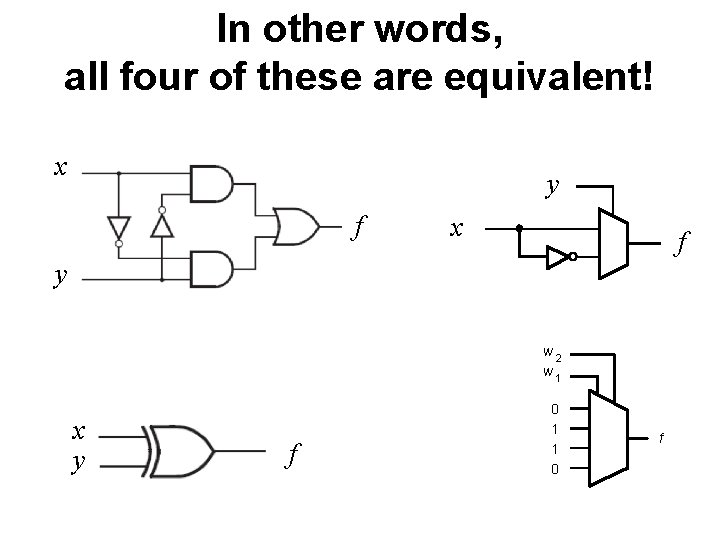

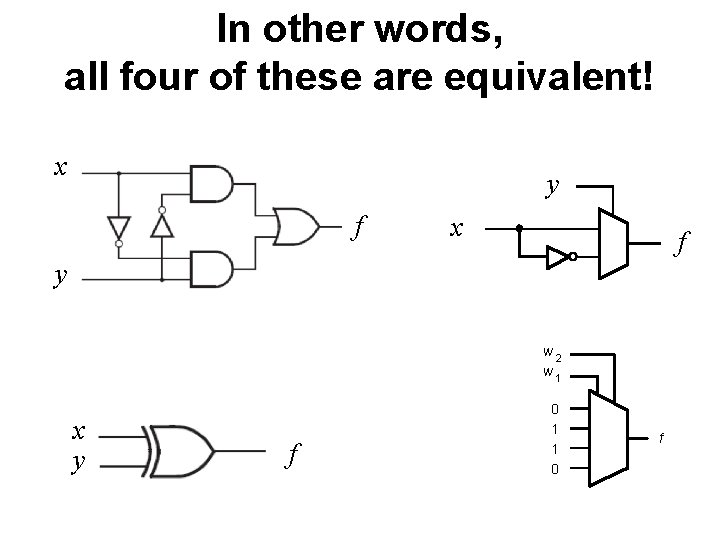

In other words, all four of these are equivalent! x y f x f y w 2 w 1 x y f 0 1 1 0 f

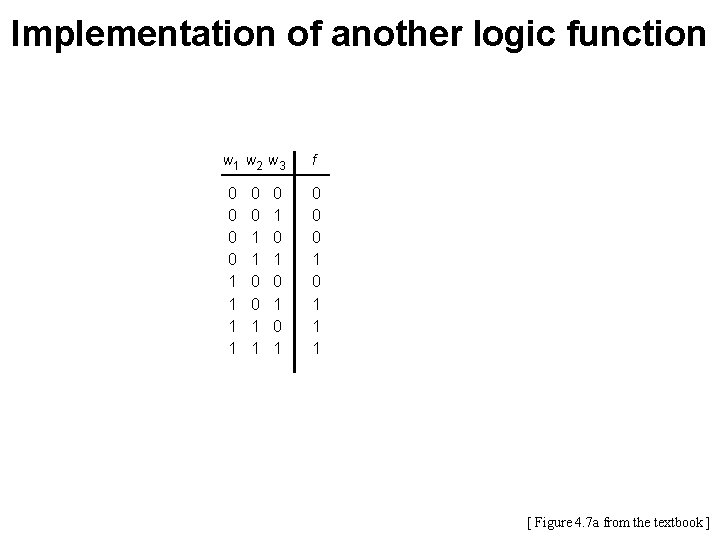

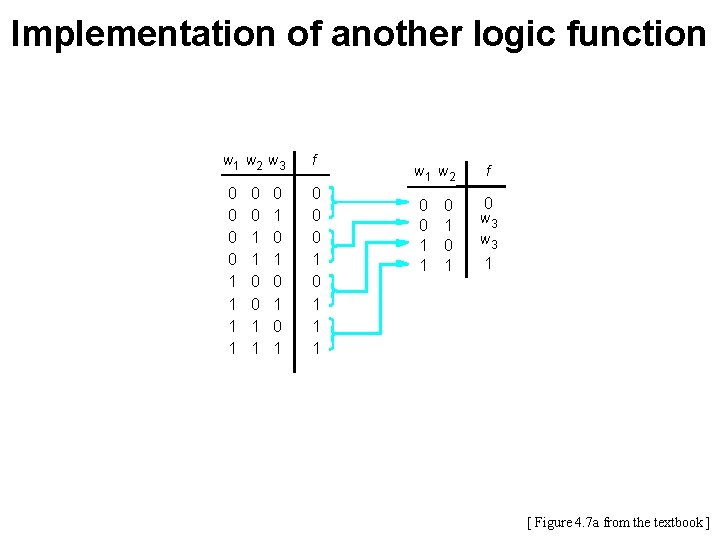

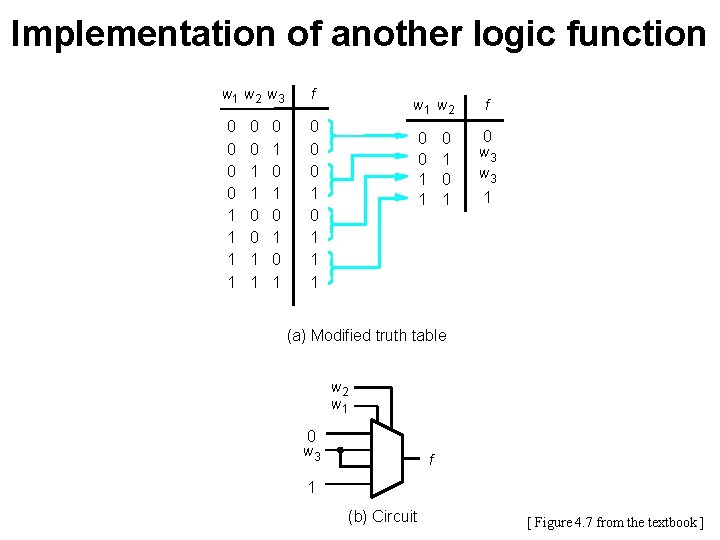

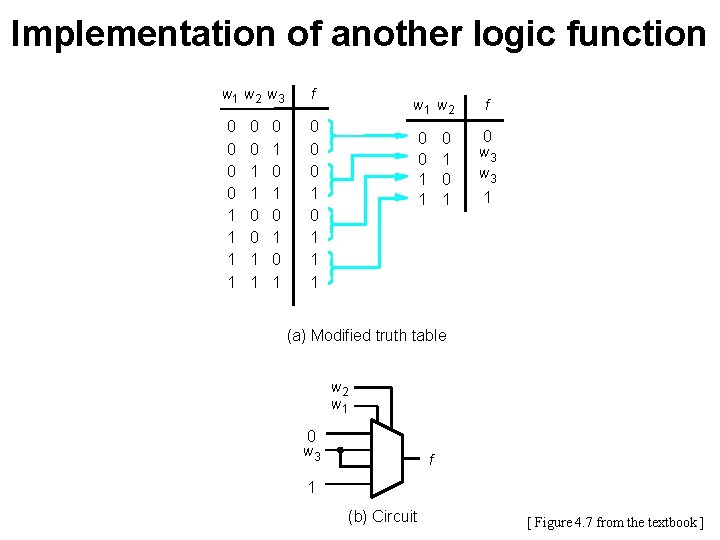

Implementation of another logic function w 1 w 2 w 3 0 0 1 1 0 1 0 1 f 0 0 0 1 1 1 [ Figure 4. 7 a from the textbook ]

Implementation of another logic function w 1 w 2 w 3 0 0 1 1 0 1 0 1 f 0 0 0 1 1 1 w 2 0 0 1 1 0 1 f 0 w 3 1 [ Figure 4. 7 a from the textbook ]

Implementation of another logic function w 1 w 2 w 3 0 0 1 1 0 1 0 1 f w 1 w 2 0 0 0 1 1 1 0 0 1 1 0 1 f 0 w 3 1 (a) Modified truth table w 2 w 1 0 w 3 f 1 (b) Circuit [ Figure 4. 7 from the textbook ]

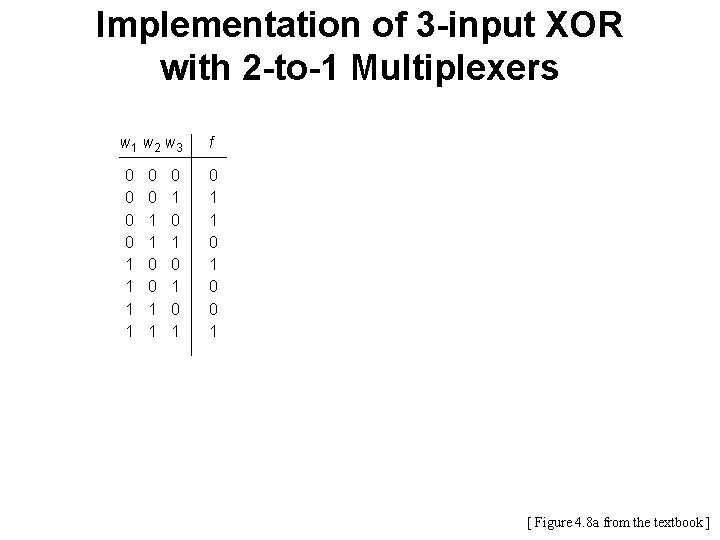

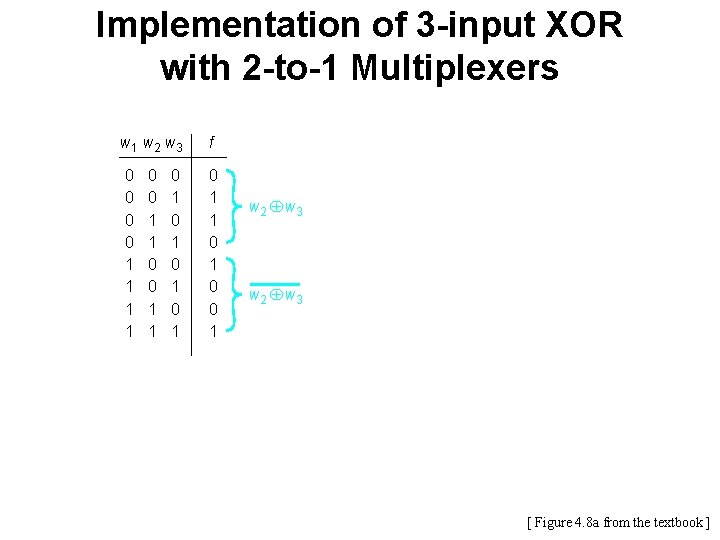

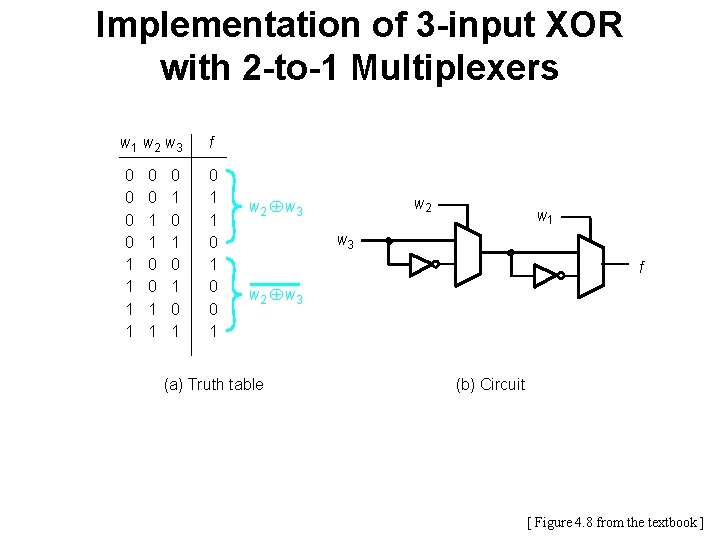

Another Example (3 -input XOR)

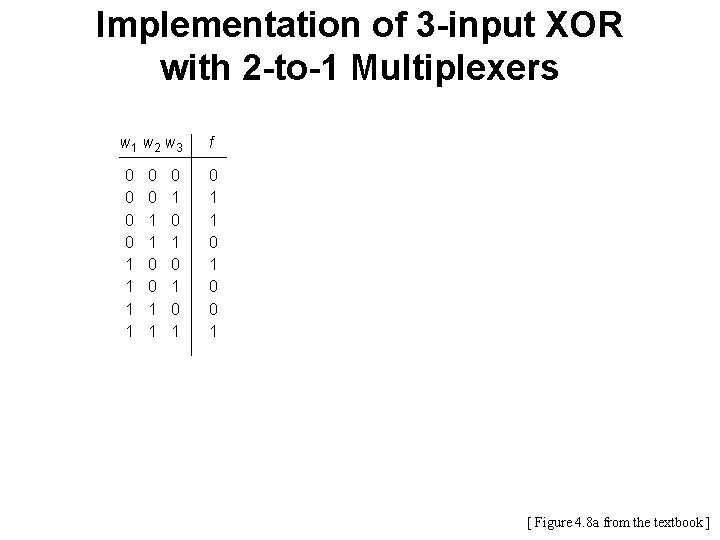

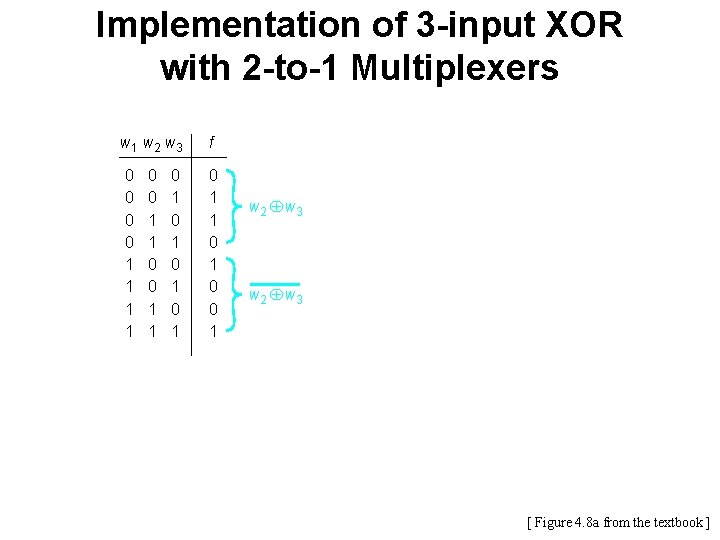

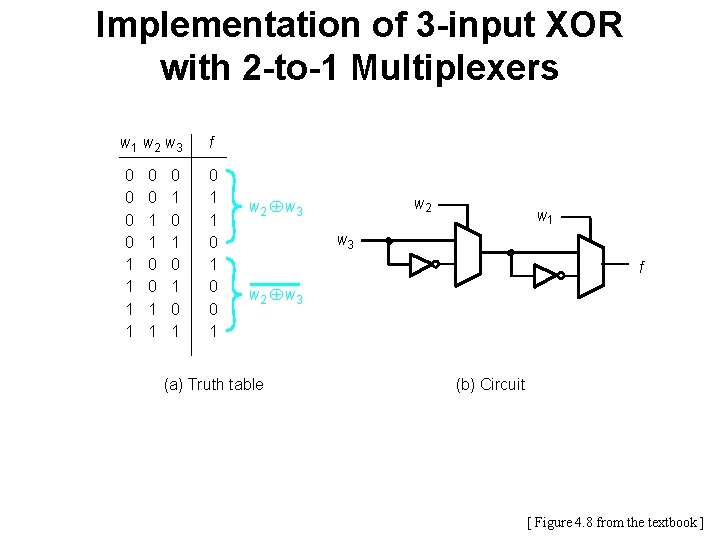

Implementation of 3 -input XOR with 2 -to-1 Multiplexers w 1 w 2 w 3 0 0 1 1 0 1 0 1 f 0 1 1 0 0 1 [ Figure 4. 8 a from the textbook ]

Implementation of 3 -input XOR with 2 -to-1 Multiplexers w 1 w 2 w 3 0 0 1 1 0 1 0 1 f 0 1 1 0 0 1 w 2 Å w 3 [ Figure 4. 8 a from the textbook ]

Implementation of 3 -input XOR with 2 -to-1 Multiplexers w 1 w 2 w 3 0 0 1 1 0 1 0 1 f 0 1 1 0 0 1 w 2 Å w 3 w 1 w 3 f w 2 Å w 3 (a) Truth table (b) Circuit [ Figure 4. 8 from the textbook ]

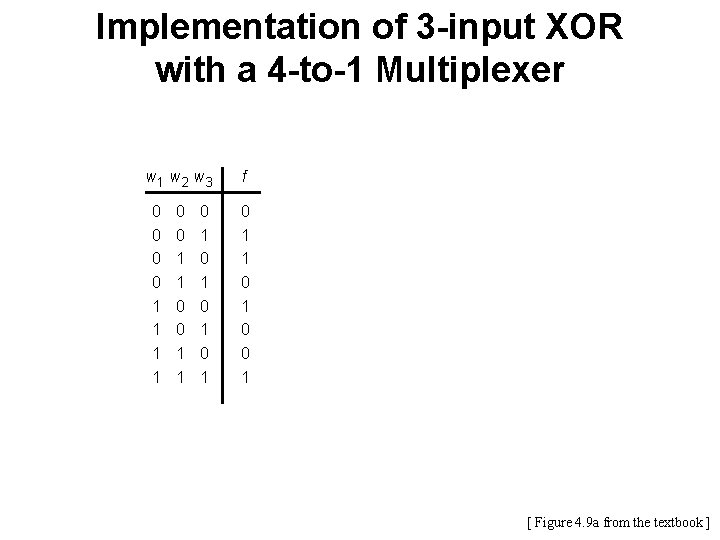

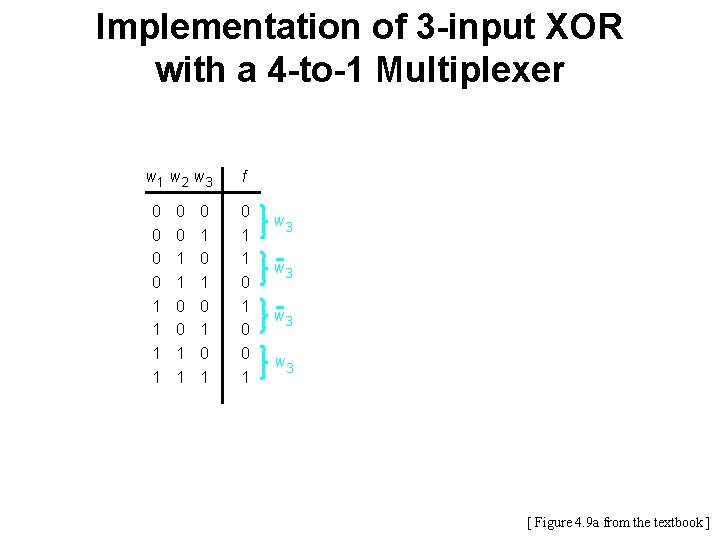

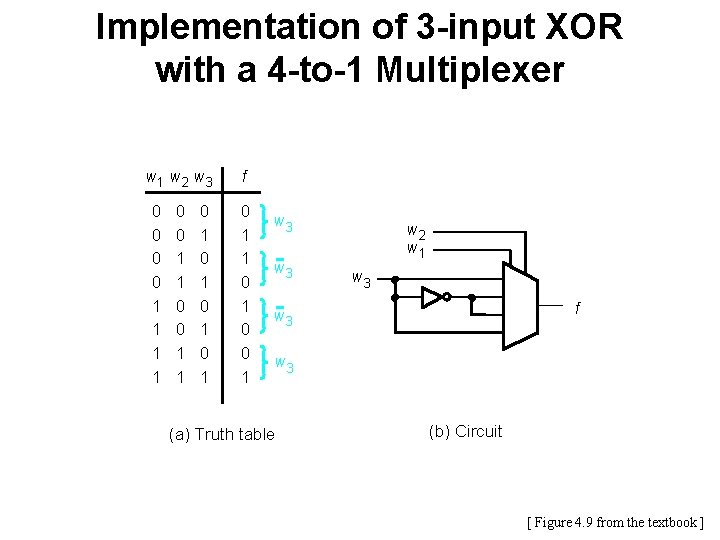

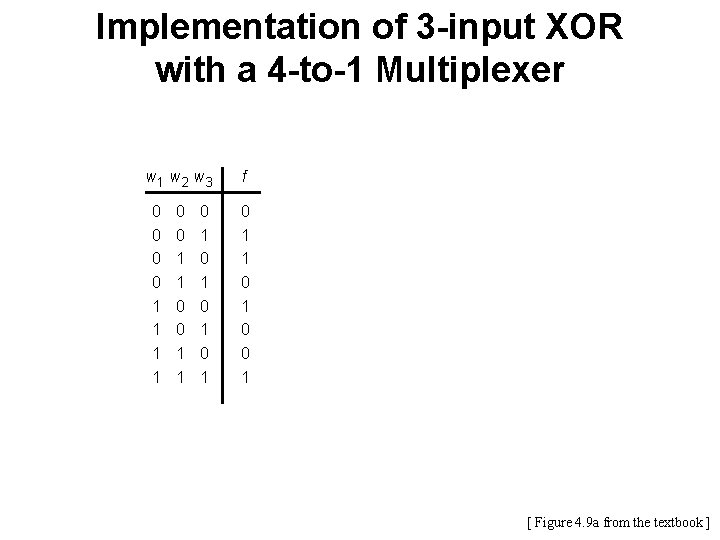

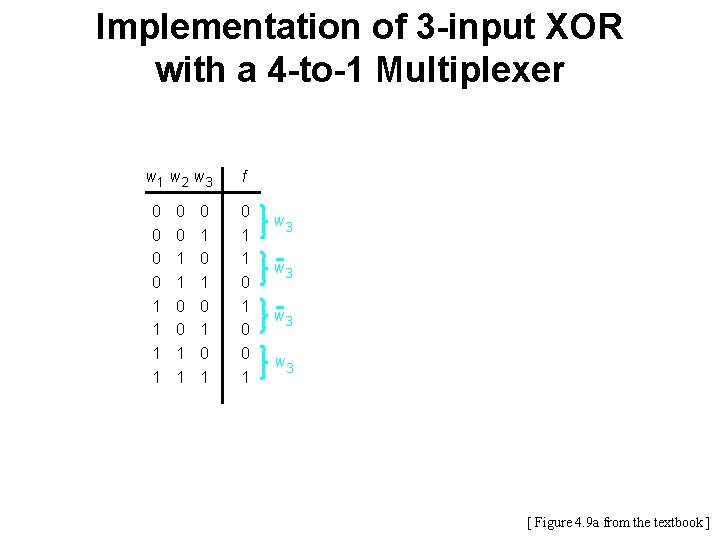

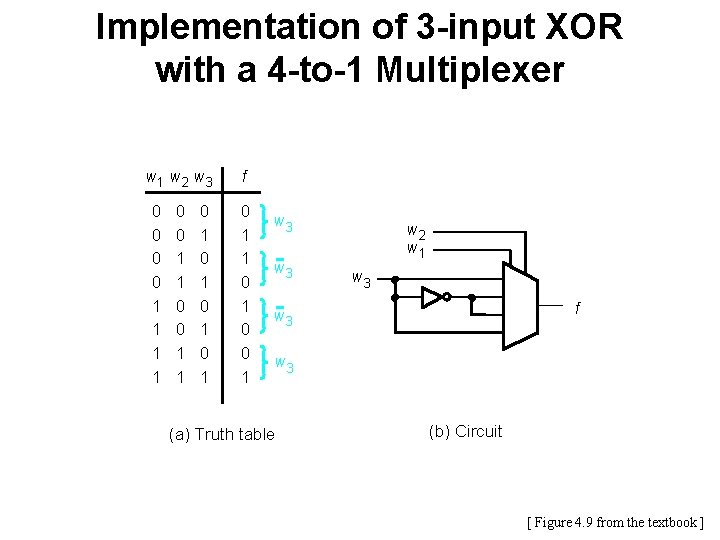

Implementation of 3 -input XOR with a 4 -to-1 Multiplexer w 1 w 2 w 3 0 0 1 1 0 1 0 1 f 0 1 1 0 0 1 [ Figure 4. 9 a from the textbook ]

Implementation of 3 -input XOR with a 4 -to-1 Multiplexer w 1 w 2 w 3 0 0 1 1 0 1 0 1 f 0 1 1 0 0 1 w 3 w 3 [ Figure 4. 9 a from the textbook ]

Implementation of 3 -input XOR with a 4 -to-1 Multiplexer w 1 w 2 w 3 0 0 1 1 0 1 0 1 f 0 1 1 0 0 1 w 3 w 2 w 1 w 3 f w 3 (a) Truth table (b) Circuit [ Figure 4. 9 from the textbook ]

Multiplexor Synthesis Using Shannon’s Expansion

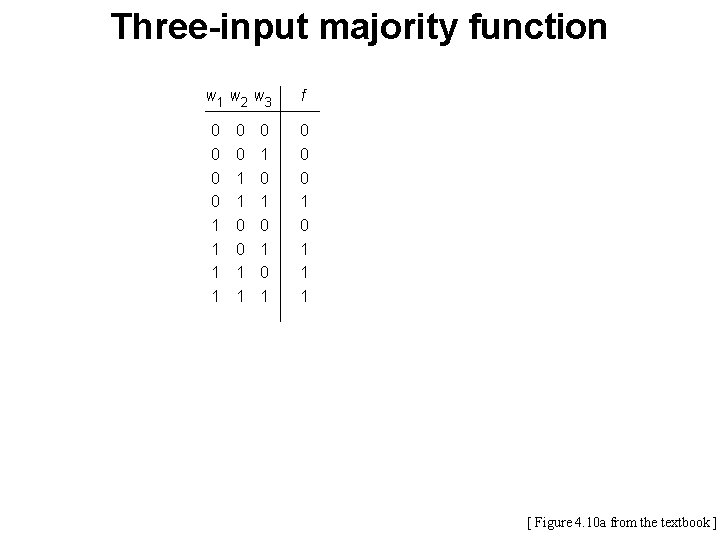

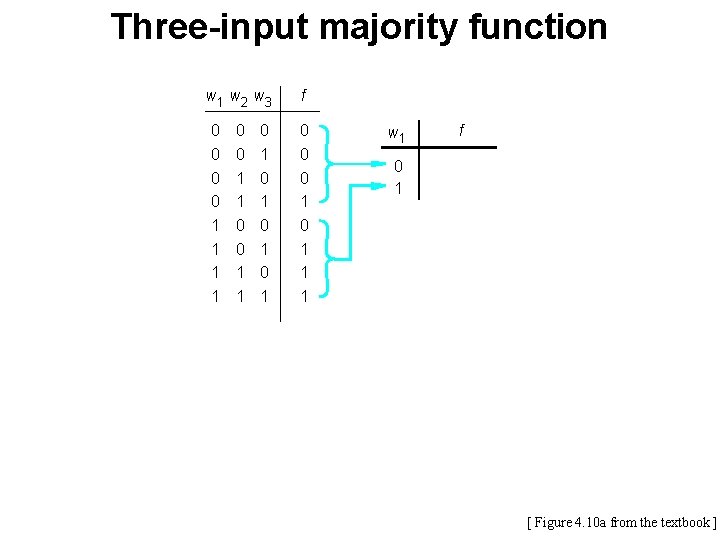

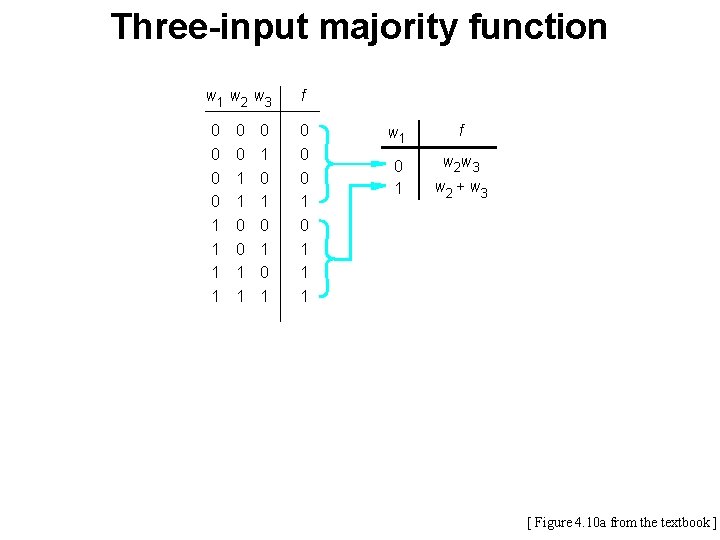

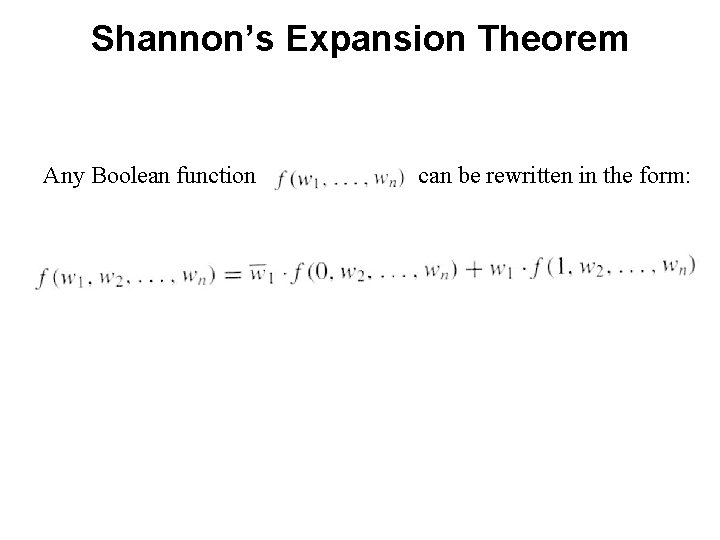

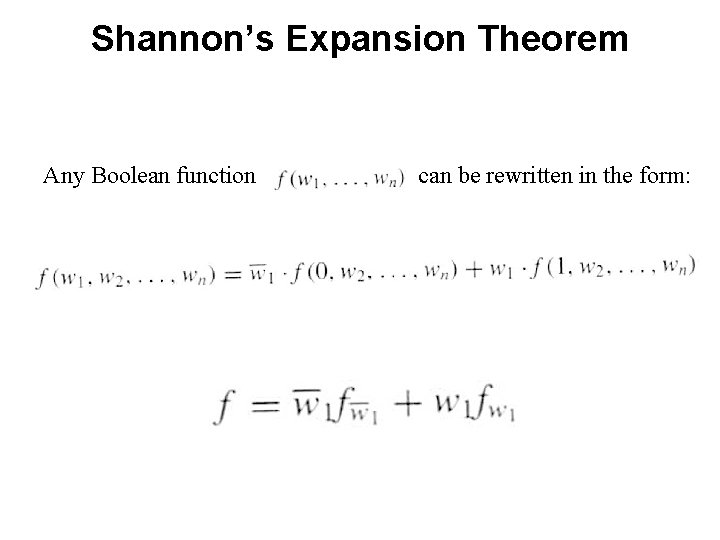

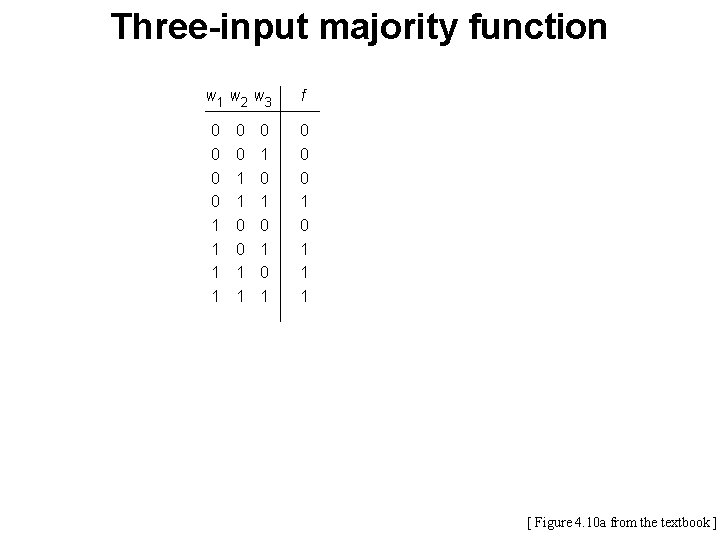

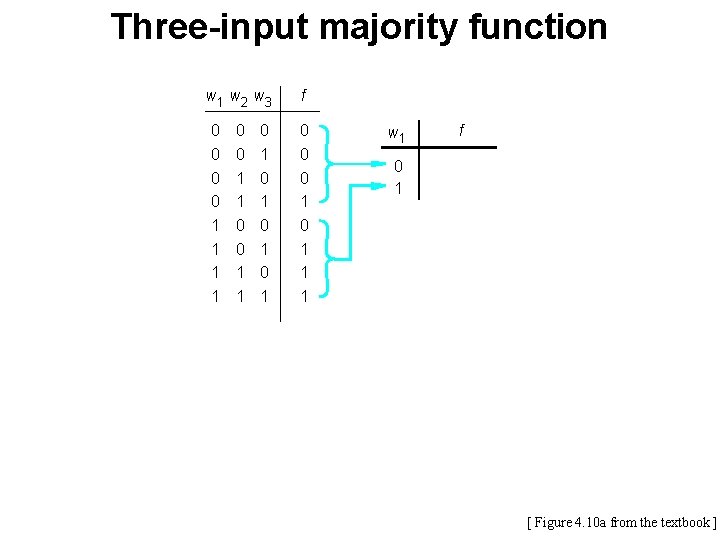

Three-input majority function w 1 w 2 w 3 0 0 1 1 0 1 0 1 f 0 0 0 1 1 1 [ Figure 4. 10 a from the textbook ]

Three-input majority function w 1 w 2 w 3 0 0 1 1 0 1 0 1 f 0 0 0 1 1 1 w 1 f 0 1 [ Figure 4. 10 a from the textbook ]

Three-input majority function w 1 w 2 w 3 0 0 1 1 0 1 0 1 f 0 0 0 1 1 1 w 1 f 0 1 w 2 w 3 w 2 + w 3 [ Figure 4. 10 a from the textbook ]

Three-input majority function w 1 w 2 w 3 0 0 1 1 0 1 0 1 f 0 0 0 1 1 1 w 1 f 0 1 w 2 w 3 w 2 + w 3 (b) Truth table w 1 w 2 w 3 f (b) Circuit [ Figure 4. 10 from the textbook ]

Three-input majority function w 2 w 3 w 1 f

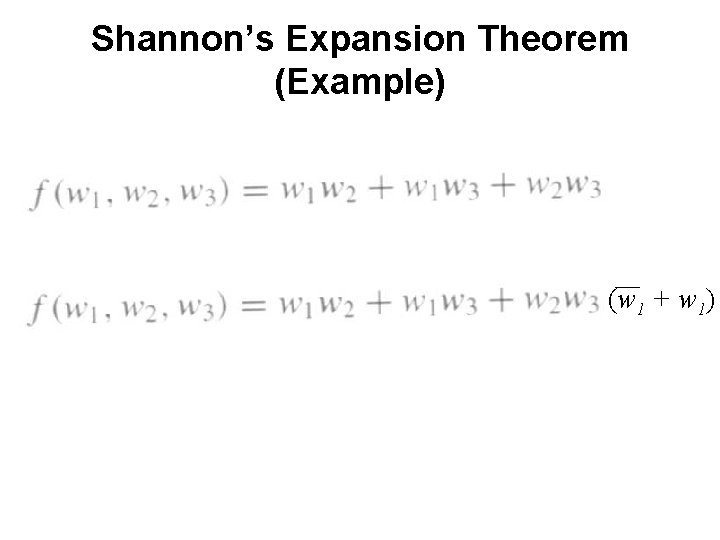

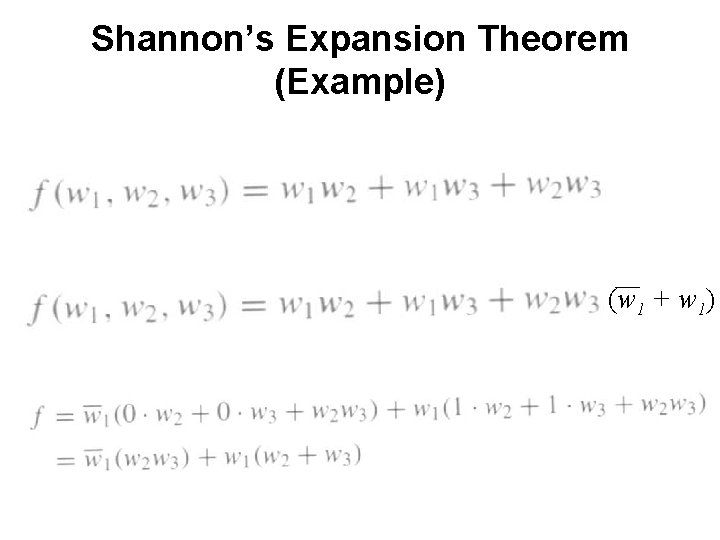

Shannon’s Expansion Theorem Any Boolean function can be rewritten in the form:

Shannon’s Expansion Theorem Any Boolean function can be rewritten in the form:

Shannon’s Expansion Theorem Any Boolean function can be rewritten in the form: cofactor

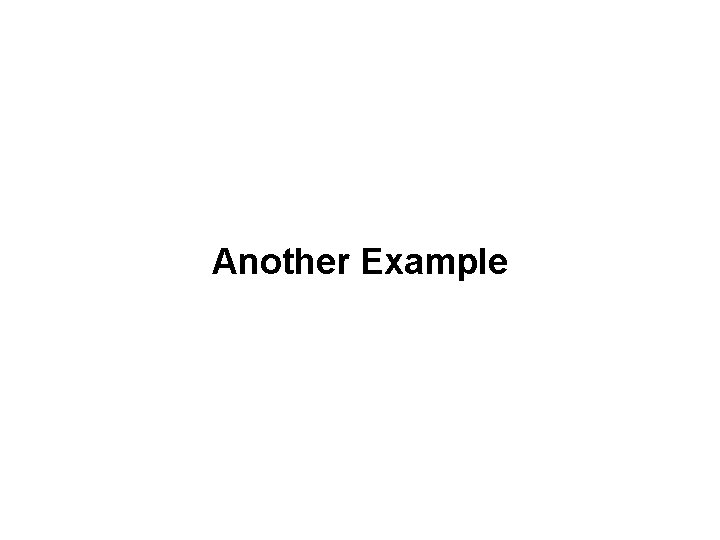

Shannon’s Expansion Theorem (Example)

Shannon’s Expansion Theorem (Example) (w 1 + w 1)

Shannon’s Expansion Theorem (Example) (w 1 + w 1)

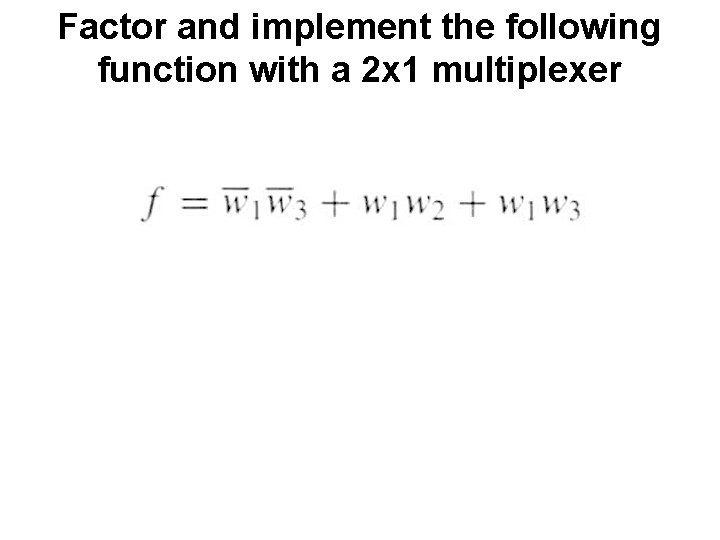

Shannon’s Expansion Theorem (In terms of more than one variable) This form is suitable for implementation with a 4 x 1 multiplexer.

Another Example

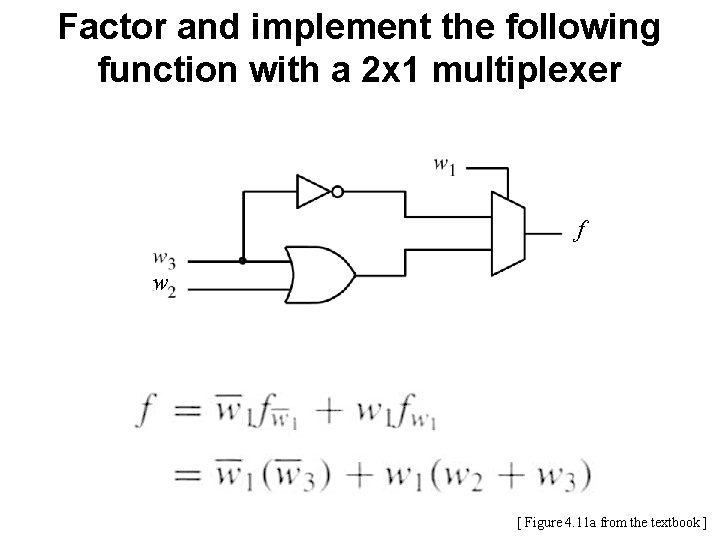

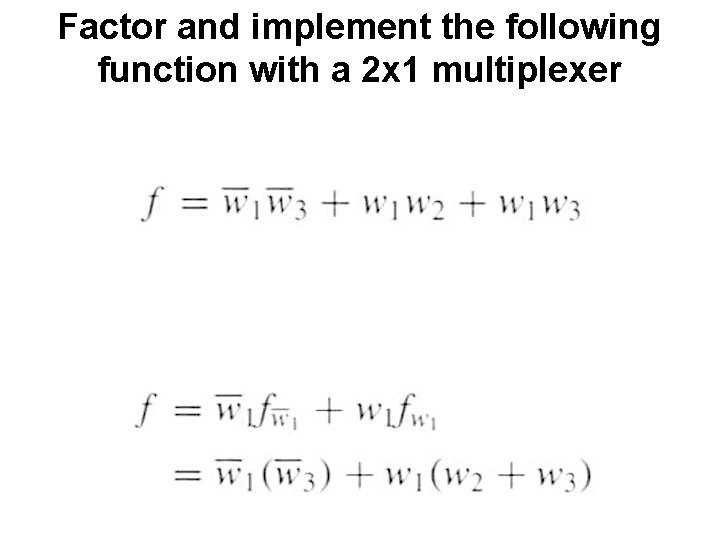

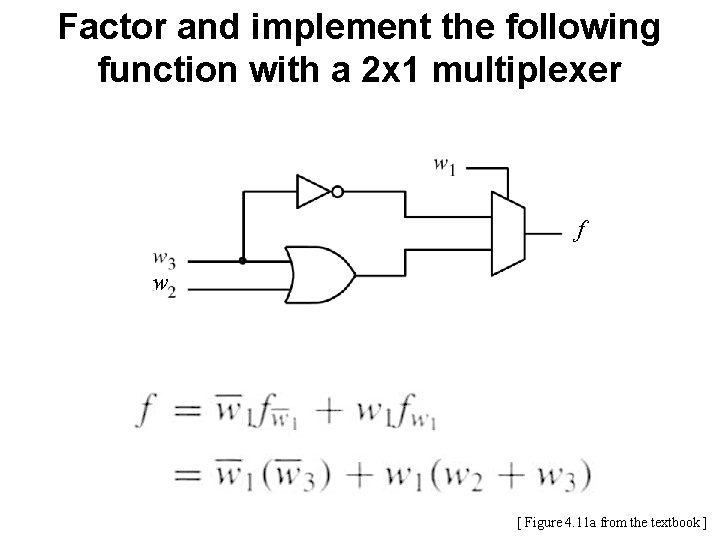

Factor and implement the following function with a 2 x 1 multiplexer

Factor and implement the following function with a 2 x 1 multiplexer

Factor and implement the following function with a 2 x 1 multiplexer f w [ Figure 4. 11 a from the textbook ]

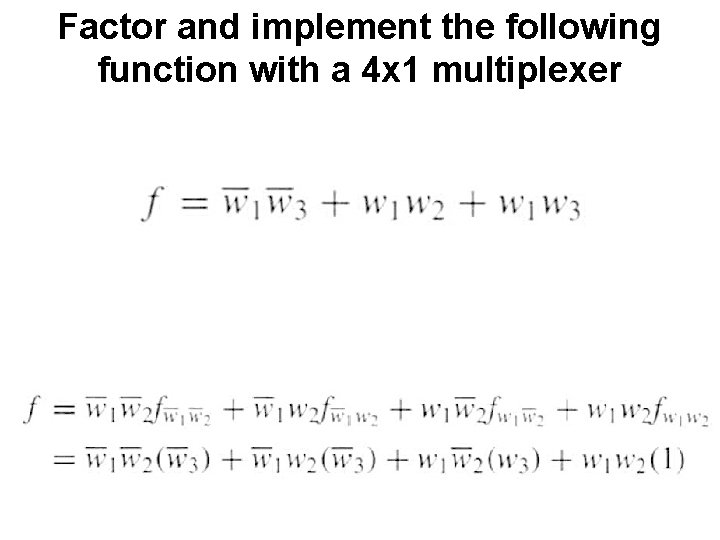

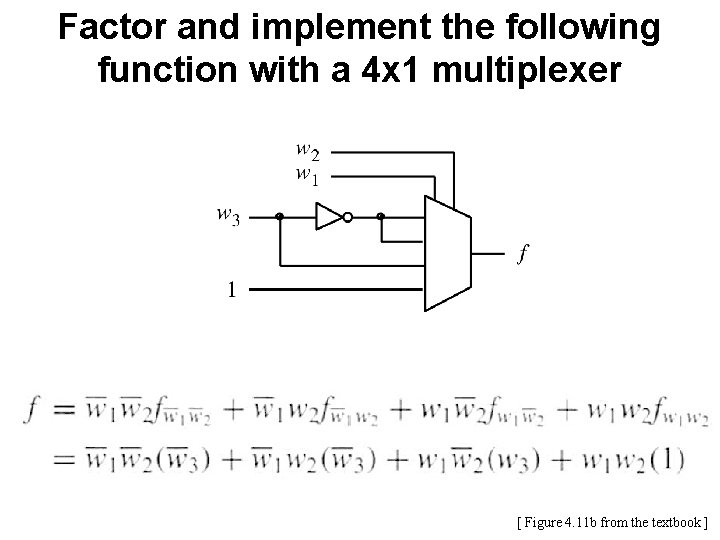

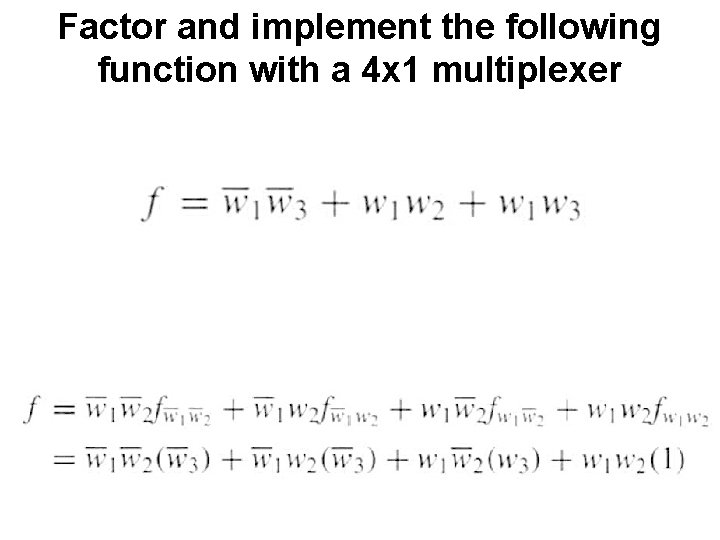

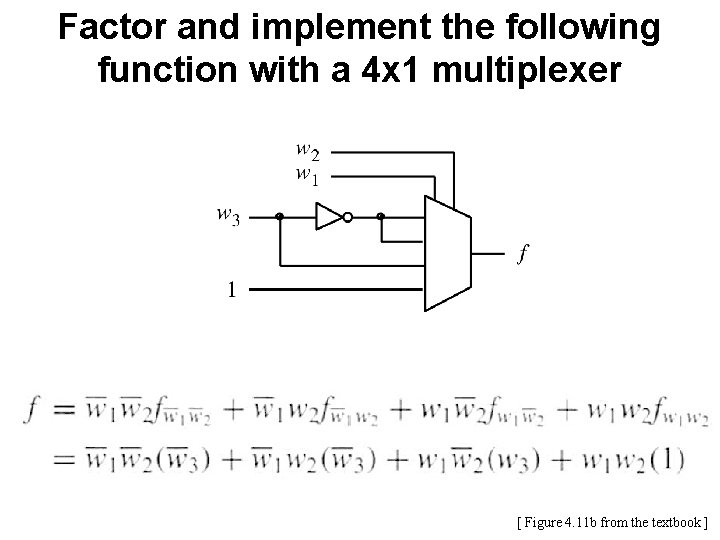

Factor and implement the following function with a 4 x 1 multiplexer

Factor and implement the following function with a 4 x 1 multiplexer

Factor and implement the following function with a 4 x 1 multiplexer [ Figure 4. 11 b from the textbook ]

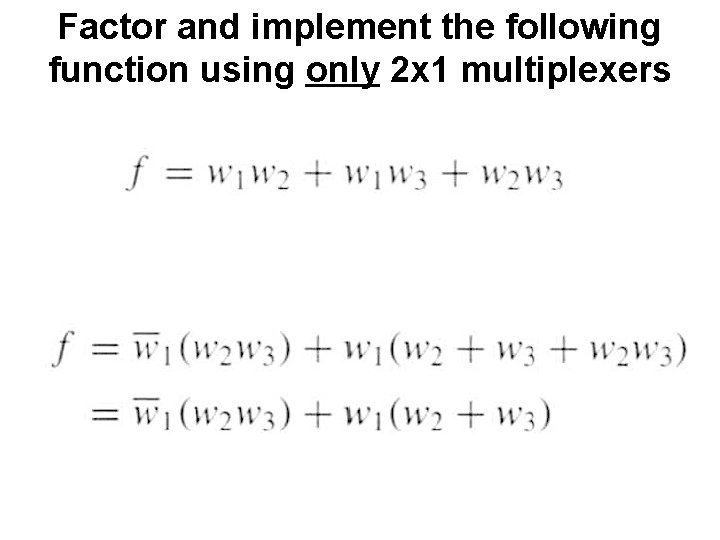

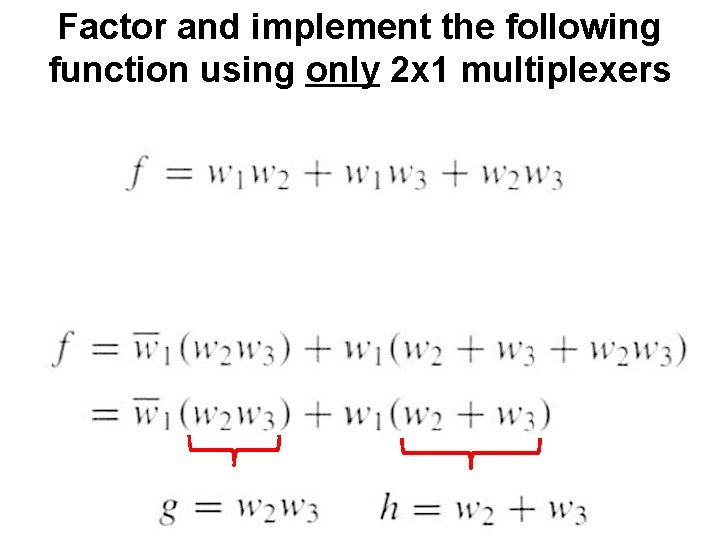

Yet Another Example

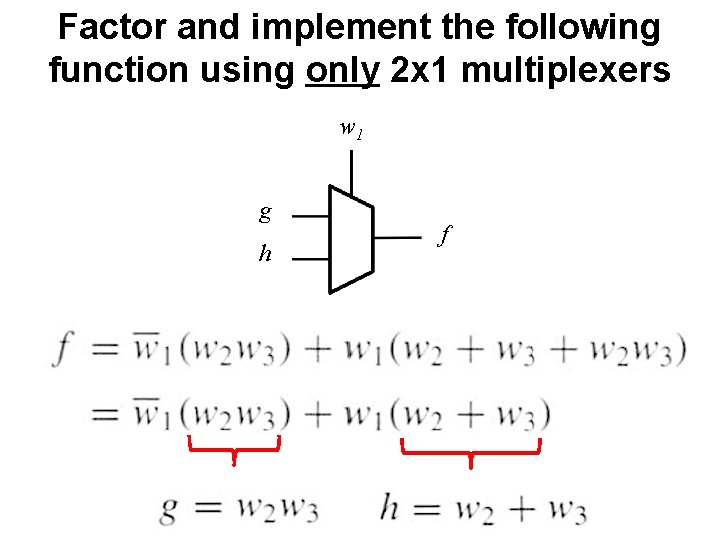

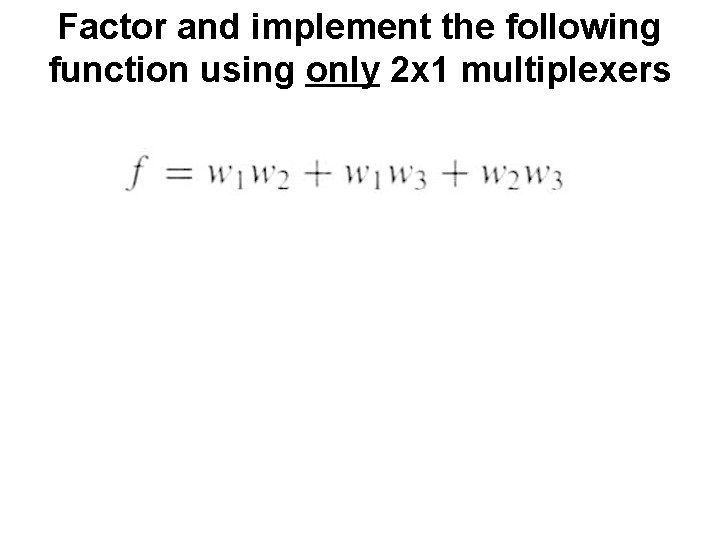

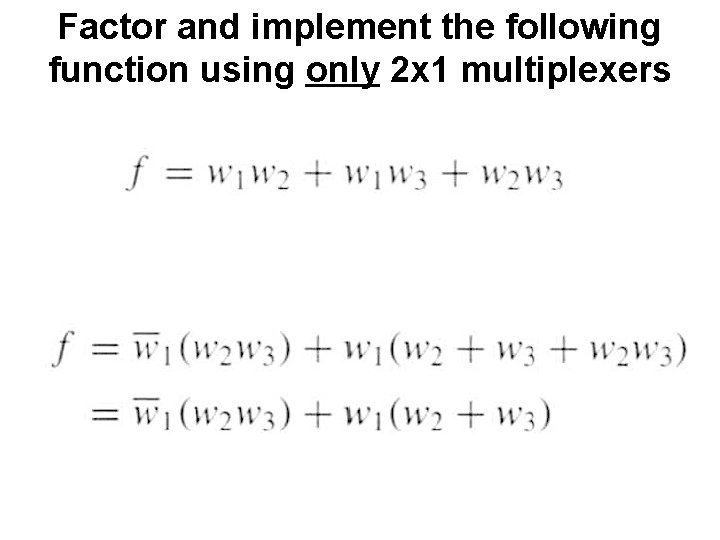

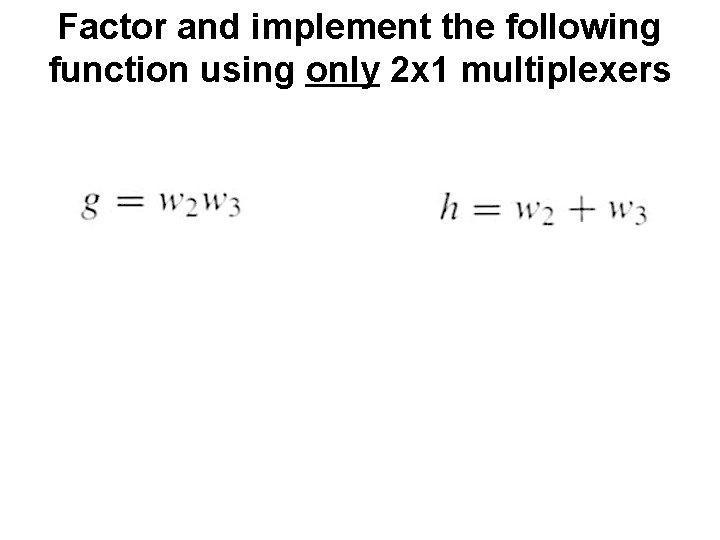

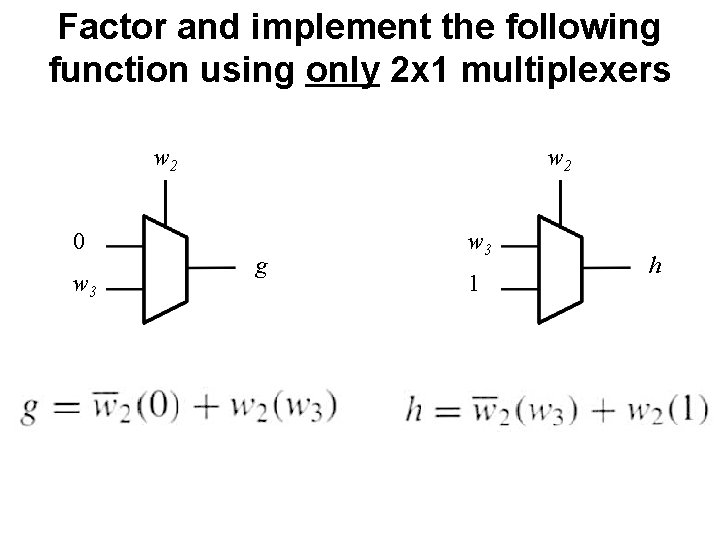

Factor and implement the following function using only 2 x 1 multiplexers

Factor and implement the following function using only 2 x 1 multiplexers

Factor and implement the following function using only 2 x 1 multiplexers

Factor and implement the following function using only 2 x 1 multiplexers w 1 g h f

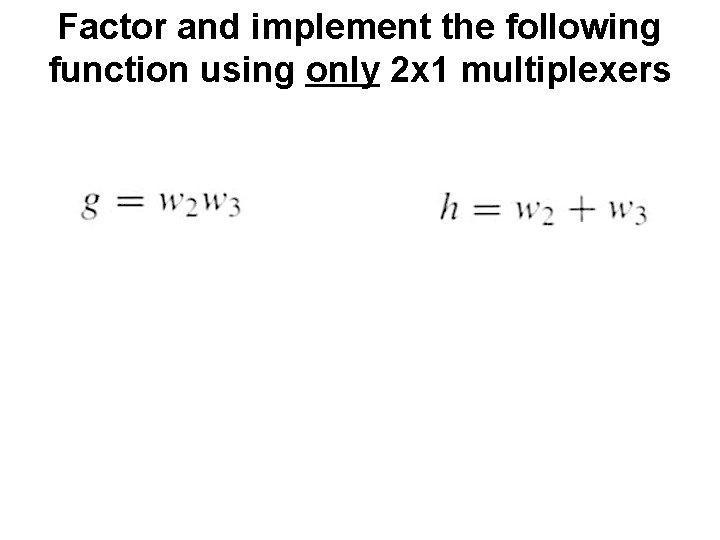

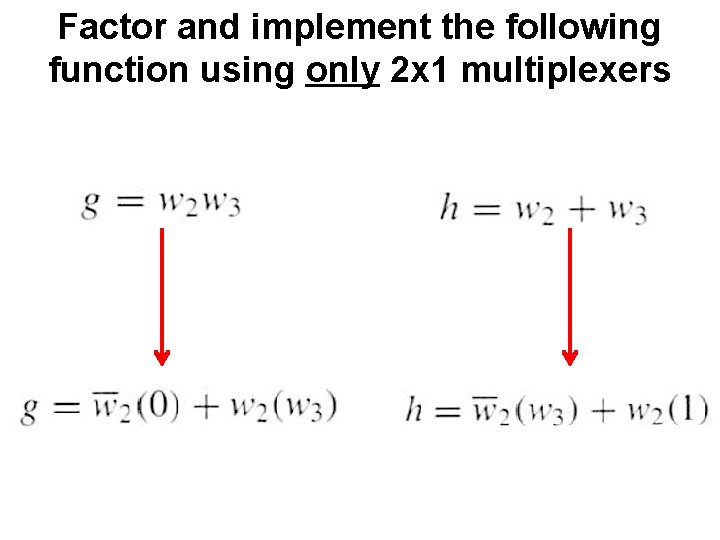

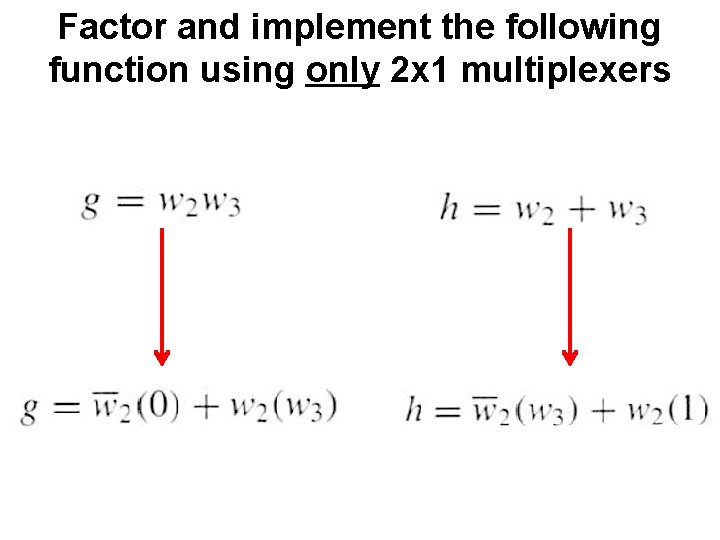

Factor and implement the following function using only 2 x 1 multiplexers

Factor and implement the following function using only 2 x 1 multiplexers

Factor and implement the following function using only 2 x 1 multiplexers w 2 0 w 3 w 2 g w 3 1 h

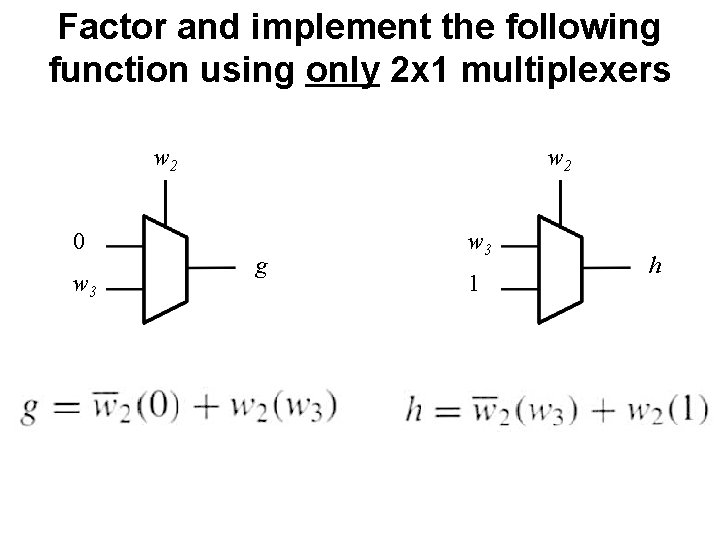

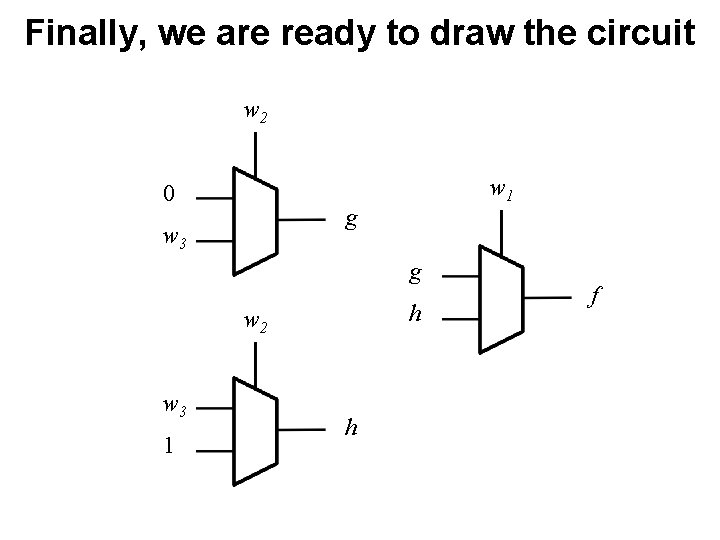

Finally, we are ready to draw the circuit w 2 0 w 1 g w 3 g h w 2 w 3 1 h f

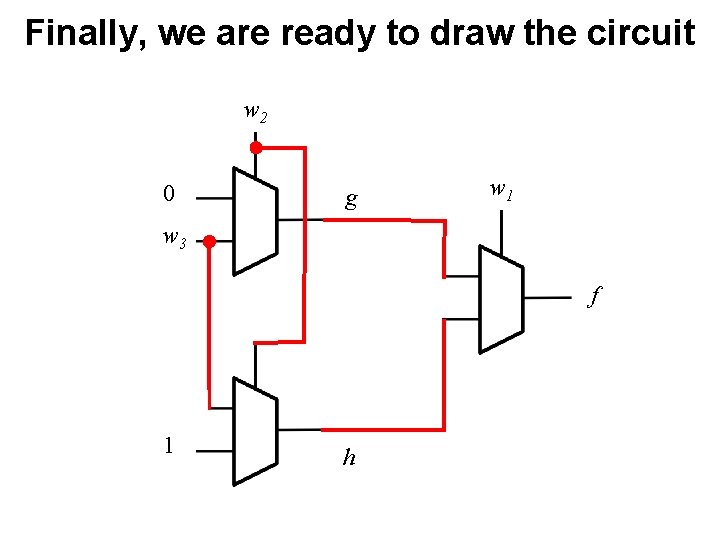

Finally, we are ready to draw the circuit w 2 0 g w 1 w 3 f 1 h

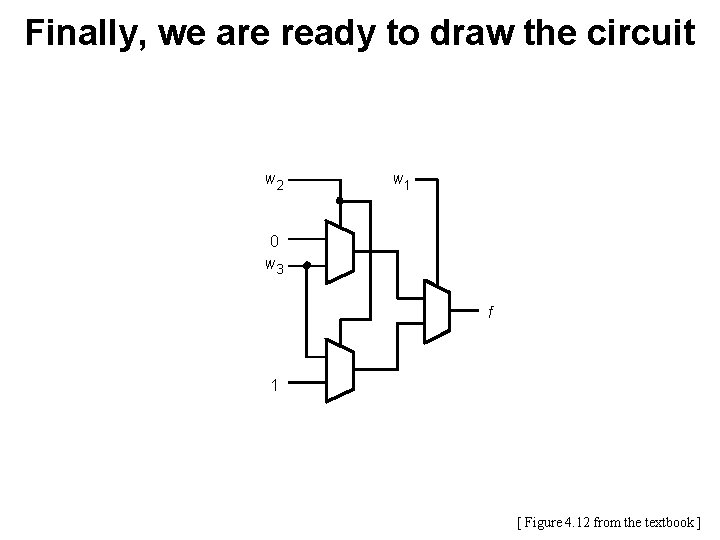

Finally, we are ready to draw the circuit w 2 w 1 0 w 3 f 1 [ Figure 4. 12 from the textbook ]

Questions?

THE END