CPE 323 Introduction to Embedded Computer Systems Introduction

CPE 323 Introduction to Embedded Computer Systems: Introduction Instructor: Dr Aleksandar Milenkovic Lecture Notes CPE/EE 421/521 Microcomputers

CPE 323 n Syllabus n n n Prerequisites n n n textbook & other references grading policy important dates course outline memory organization decoding combinatorial and sequential logic important for system architecture Microcomputer Lab (EB 106) n n Introduction sessions Lab instructor CPE/EE 421/521 Microcomputers 2

CPE 323 n LAB Session n n on-line LAB manual Access cards Accounts Lab Assistant: Joel Wilder Lab sessions n n #1 - Mon: 5: 30 – 7: 00 pm #2 - Tues: 5: 30 - 7: 00 pm Backup - Tues: 7: 00 – 8: 30 pm Sign-up sheet - if needed CPE/EE 421/521 Microcomputers 3

Outline n n Embedded systems: structure and organization Applications Technology Trends Historical perspective CPE/EE 421/521 Microcomputers 4

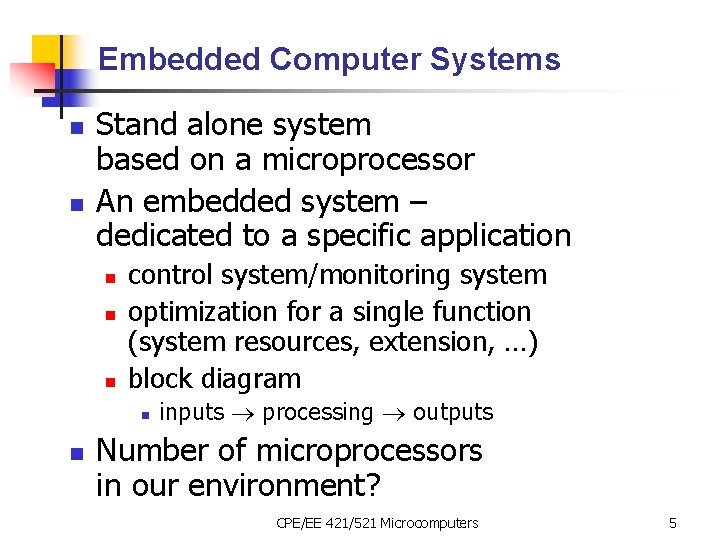

Embedded Computer Systems n n Stand alone system based on a microprocessor An embedded system – dedicated to a specific application n control system/monitoring system optimization for a single function (system resources, extension, …) block diagram n n inputs processing outputs Number of microprocessors in our environment? CPE/EE 421/521 Microcomputers 5

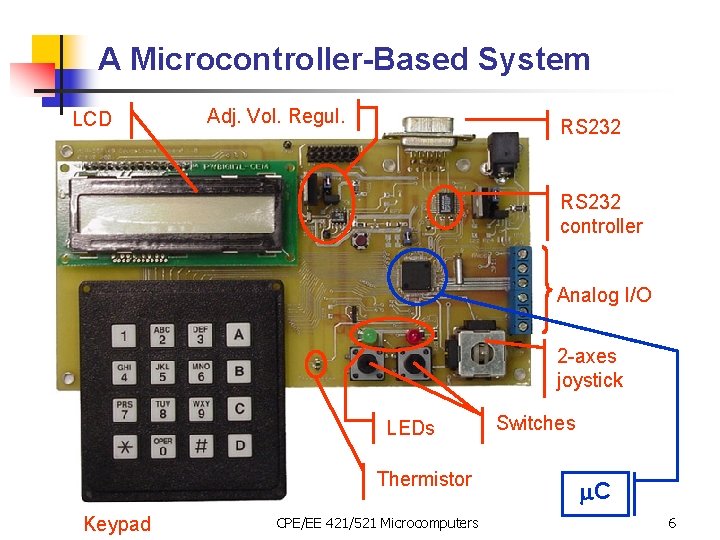

A Microcontroller-Based System LCD Adj. Vol. Regul. RS 232 controller Analog I/O 2 -axes joystick LEDs Thermistor Keypad CPE/EE 421/521 Microcomputers Switches m. C 6

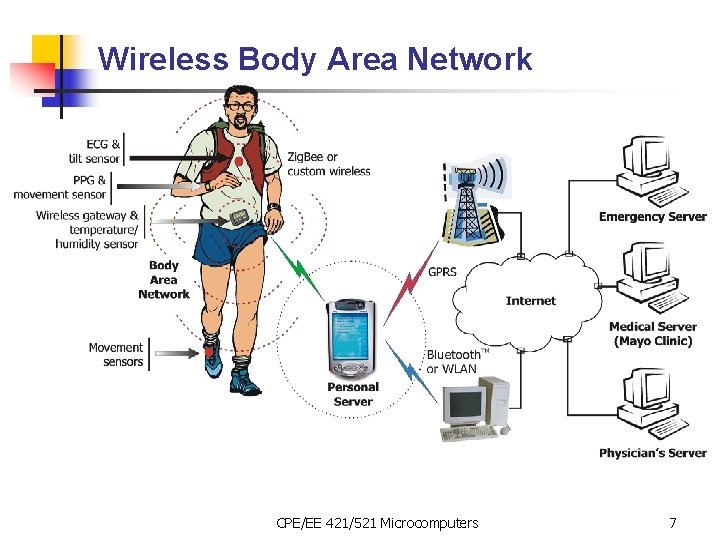

Wireless Body Area Network CPE/EE 421/521 Microcomputers 7

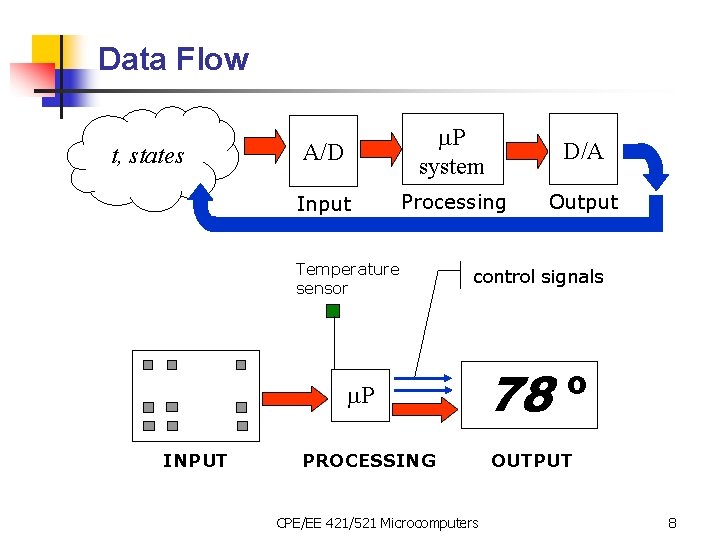

Data Flow t, states A/D m. P system D/A Input Processing Output Temperature sensor control signals m. P INPUT PROCESSING CPE/EE 421/521 Microcomputers 78 º OUTPUT 8

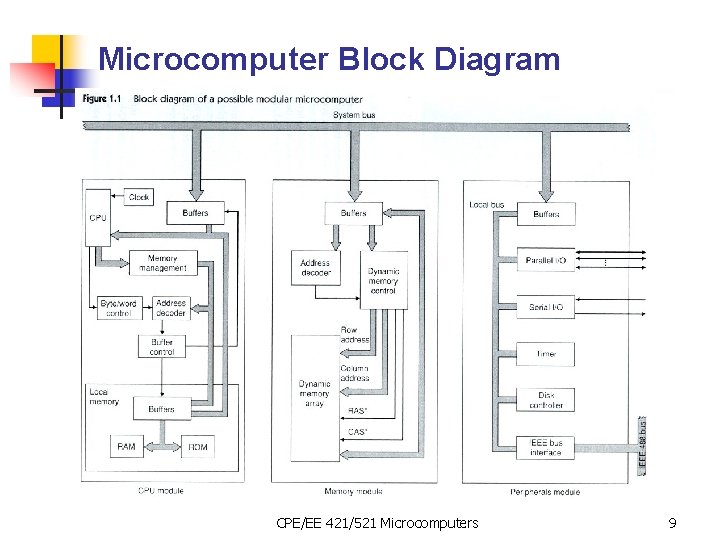

Microcomputer Block Diagram CPE/EE 421/521 Microcomputers 9

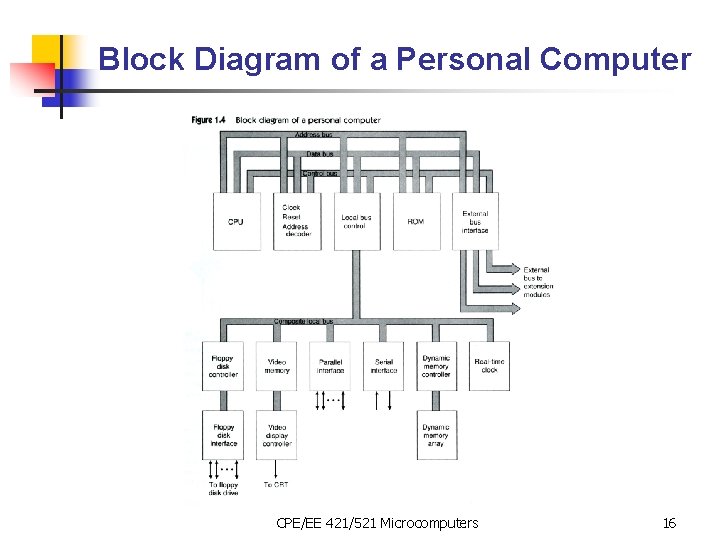

Microprocessor System Architecture n n n System bus n n n Single Board Computers (SBC) block diagram (modules, cards) Multibus, VME, ISA, PCI, … Multiple masters CPU n Clock and CPU Control Circuits n n n 1 MHz - 1 GHz power-up and reset circuits Address Decoder Address and Data Bus Buffers Bus Arbitration Control Memory management CPE/EE 421/521 Microcomputers 10

Microprocessor System Architecture n Memory Module n n Virtual memory / Physical memory ROM, RAM, video memory static/dynamic Peripheral Module n serial interface n n parallel interface n n RS 232 (CRT, mouse), USB, Firewire (IEEE 1394) printerface timer n time/frequency measurement CPE/EE 421/521 Microcomputers 11

Microprocessor System Architecture n PC architecture CPU Memory PCI ISA CPE/EE 421/521 Microcomputers 12

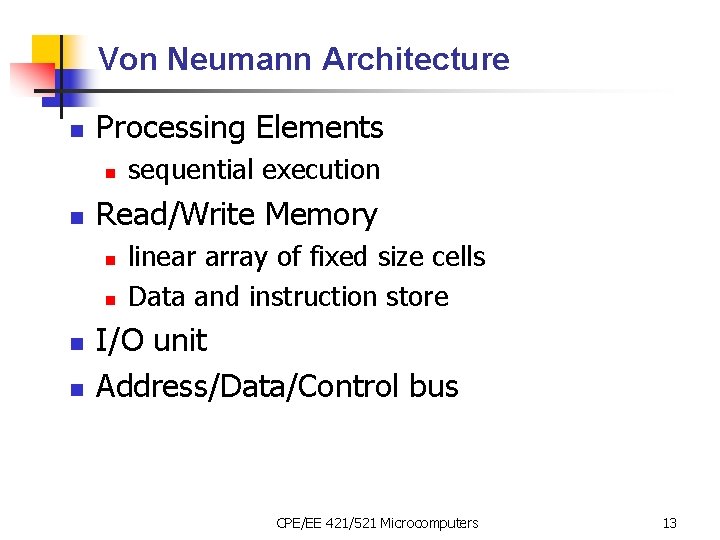

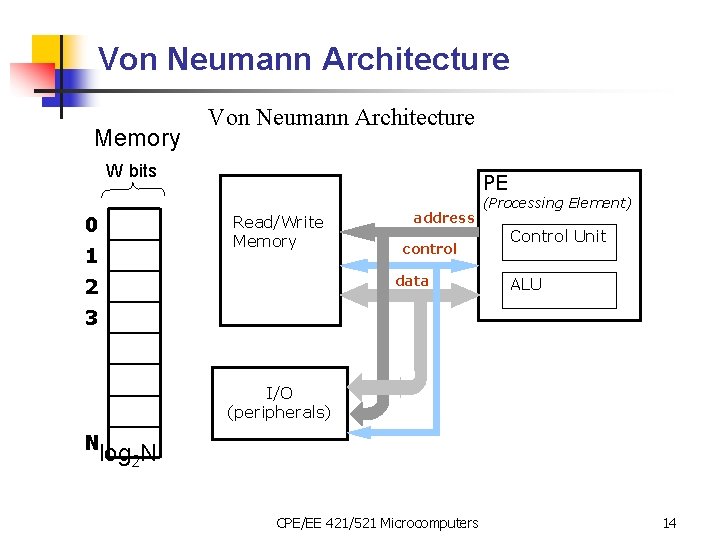

Von Neumann Architecture n Processing Elements n n Read/Write Memory n n sequential execution linear array of fixed size cells Data and instruction store I/O unit Address/Data/Control bus CPE/EE 421/521 Microcomputers 13

Von Neumann Architecture Memory Von Neumann Architecture W bits 0 PE Read/Write Memory 1 address control data 2 (Processing Element) Control Unit ALU 3 I/O (peripherals) N log 2 N CPE/EE 421/521 Microcomputers 14

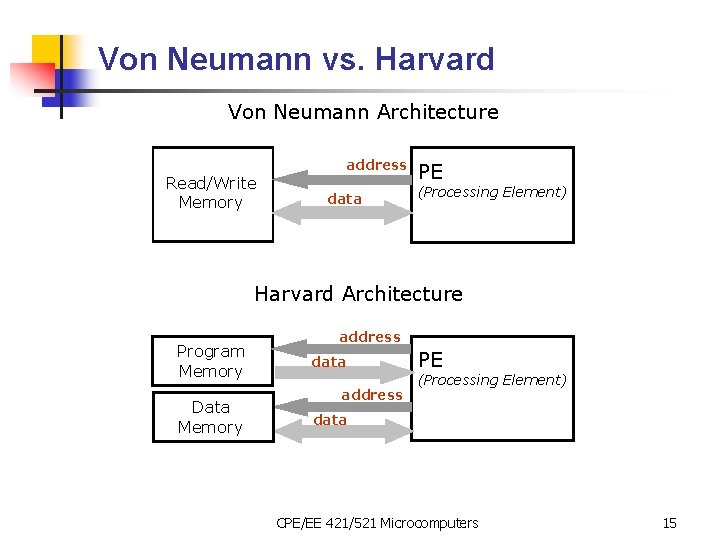

Von Neumann vs. Harvard Von Neumann Architecture Read/Write Memory address data PE (Processing Element) Harvard Architecture Program Memory Data Memory address data address PE (Processing Element) data CPE/EE 421/521 Microcomputers 15

Block Diagram of a Personal Computer CPE/EE 421/521 Microcomputers 16

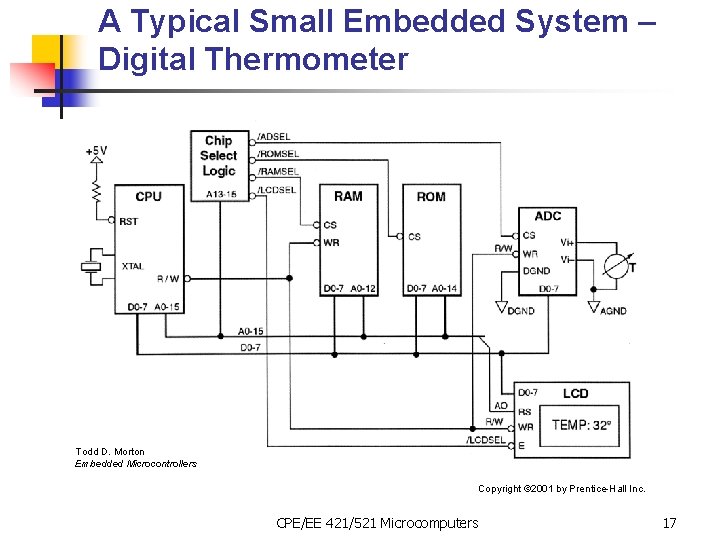

A Typical Small Embedded System – Digital Thermometer Todd D. Morton Embedded Microcontrollers Copyright © 2001 by Prentice-Hall Inc. CPE/EE 421/521 Microcomputers 17

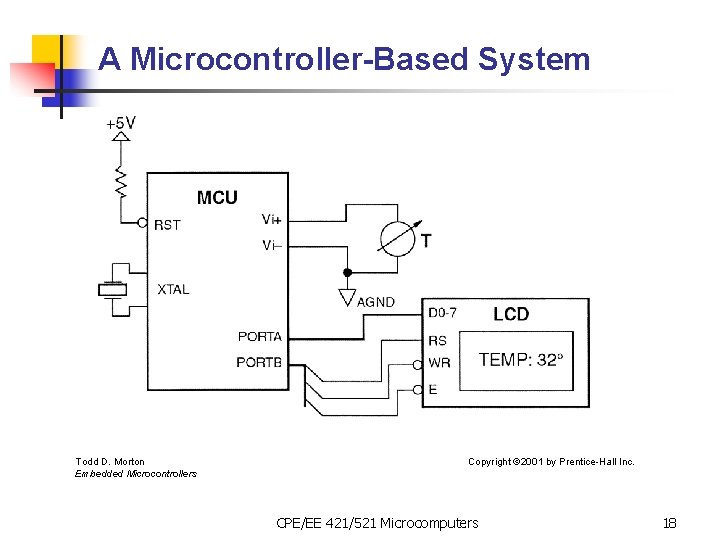

A Microcontroller-Based System Todd D. Morton Embedded Microcontrollers Copyright © 2001 by Prentice-Hall Inc. CPE/EE 421/521 Microcomputers 18

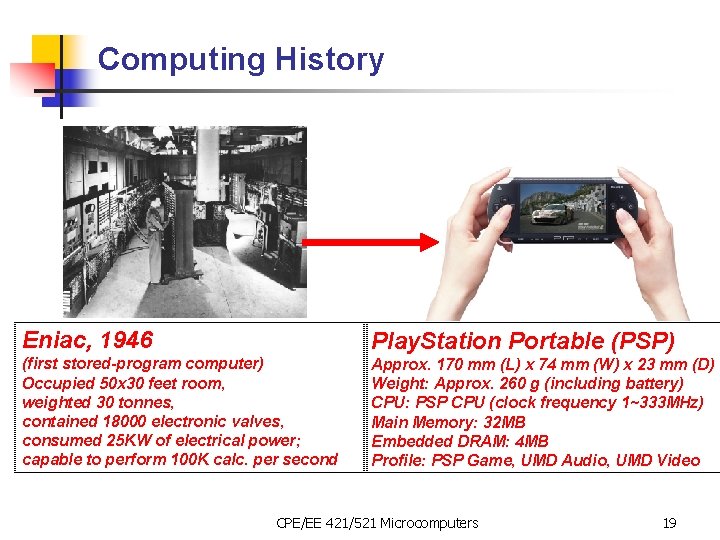

Computing History Eniac, 1946 Play. Station Portable (PSP) (first stored-program computer) Occupied 50 x 30 feet room, weighted 30 tonnes, contained 18000 electronic valves, consumed 25 KW of electrical power; capable to perform 100 K calc. per second Approx. 170 mm (L) x 74 mm (W) x 23 mm (D) Weight: Approx. 260 g (including battery) CPU: PSP CPU (clock frequency 1~333 MHz) Main Memory: 32 MB Embedded DRAM: 4 MB Profile: PSP Game, UMD Audio, UMD Video CPE/EE 421/521 Microcomputers 19

Understanding computers …. n User perspective n n Applications: What do we do with them? Price: How much do they cost? n n n To purchase and to operate Convenience: How difficult is to use them? Designer perspective n n Size: How large are they? (UP) Speed: How many operations …? (UP) Power: What is energy consumed? (UP) Complexity: How complex are they to build? CPE/EE 421/521 Microcomputers 20

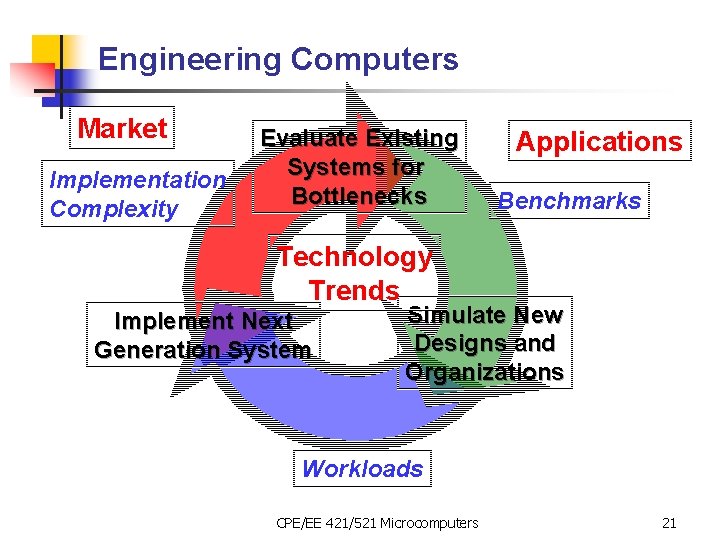

Engineering Computers Market Implementation Complexity Evaluate Existing Systems for Bottlenecks Applications Benchmarks Technology Trends Implement Next Generation System Simulate New Designs and Organizations Workloads CPE/EE 421/521 Microcomputers 21

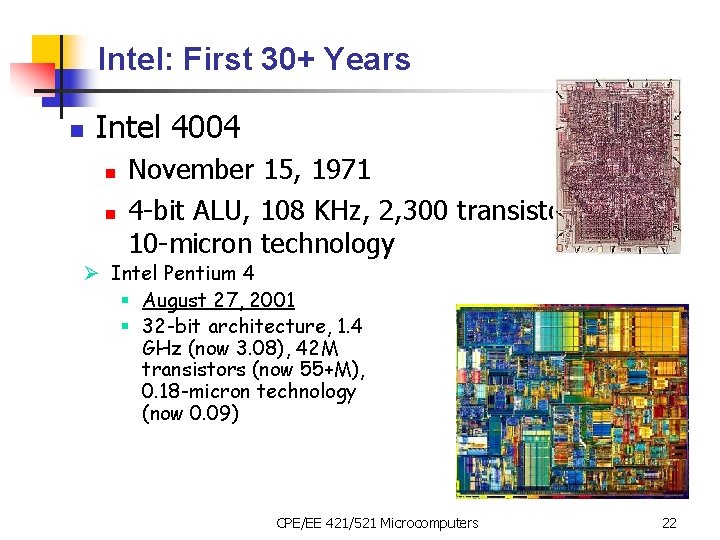

Intel: First 30+ Years n Intel 4004 n n November 15, 1971 4 -bit ALU, 108 KHz, 2, 300 transistors, 10 -micron technology Ø Intel Pentium 4 § August 27, 2001 § 32 -bit architecture, 1. 4 GHz (now 3. 08), 42 M transistors (now 55+M), 0. 18 -micron technology (now 0. 09) CPE/EE 421/521 Microcomputers 22

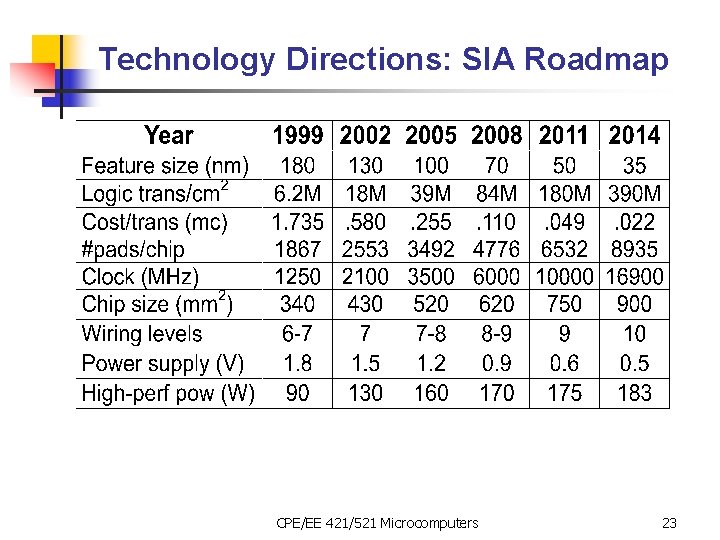

Technology Directions: SIA Roadmap CPE/EE 421/521 Microcomputers 23

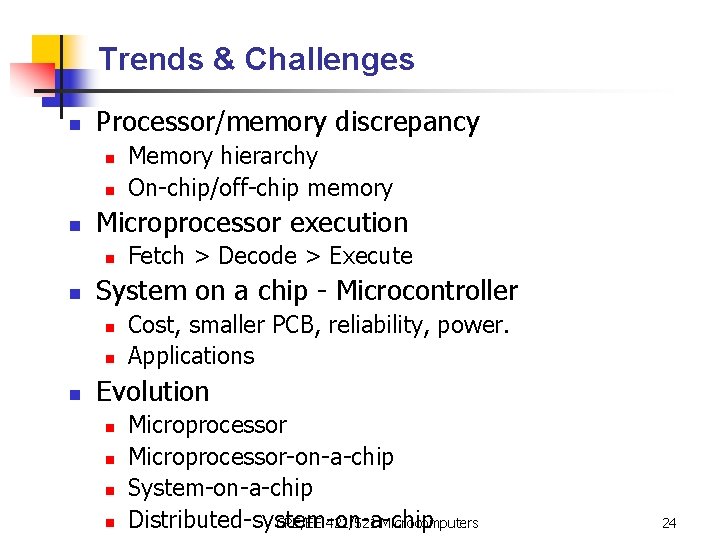

Trends & Challenges n Processor/memory discrepancy n n n Microprocessor execution n n Fetch > Decode > Execute System on a chip - Microcontroller n n n Memory hierarchy On-chip/off-chip memory Cost, smaller PCB, reliability, power. Applications Evolution n n Microprocessor-on-a-chip System-on-a-chip CPE/EE 421/521 Microcomputers Distributed-system-on-a-chip 24

More on Challenges n Scalability n n n Availability n n n billions of small devices performance hardware changes system upgrade failures code enhancements Fault tolerance CPE/EE 421/521 Microcomputers 25

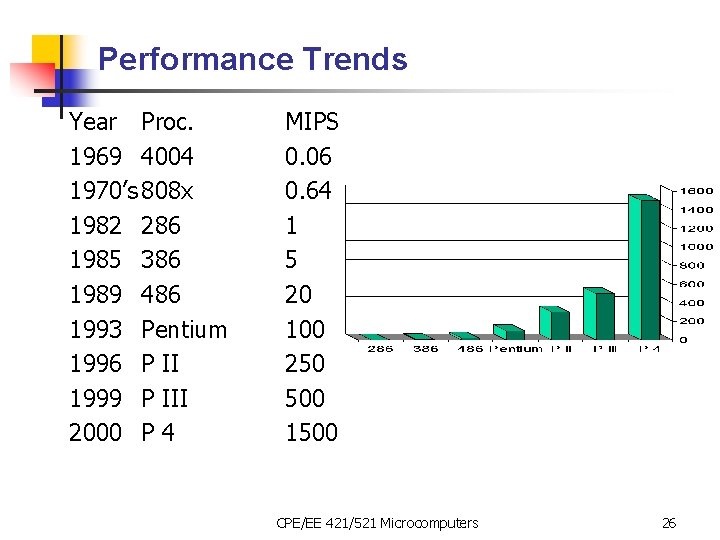

Performance Trends Year Proc. 1969 4004 1970’s 808 x 1982 286 1985 386 1989 486 1993 Pentium 1996 P II 1999 P III 2000 P 4 MIPS 0. 06 0. 64 1 5 20 100 250 500 1500 CPE/EE 421/521 Microcomputers 26

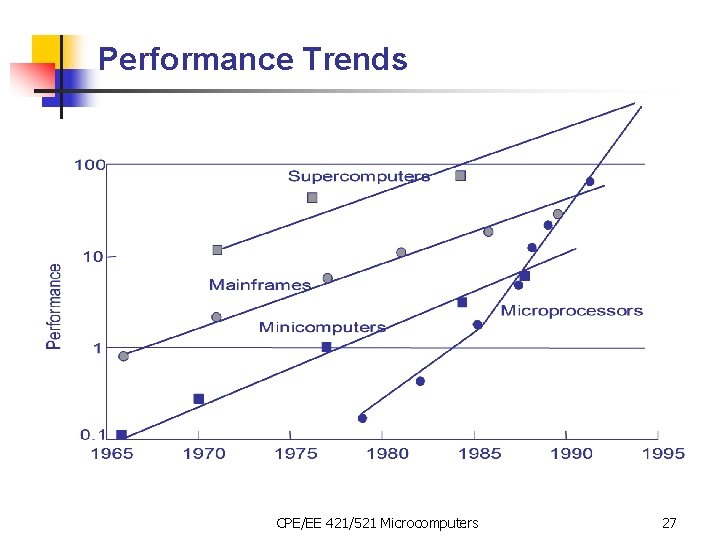

Performance Trends CPE/EE 421/521 Microcomputers 27

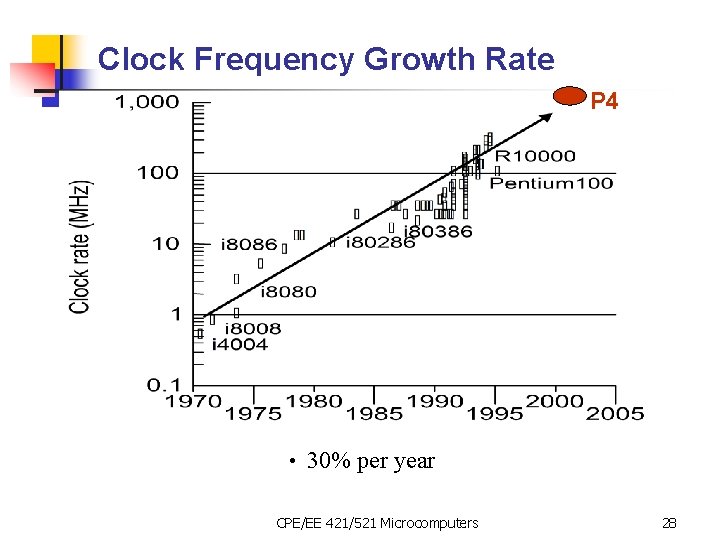

Clock Frequency Growth Rate P 4 • 30% per year CPE/EE 421/521 Microcomputers 28

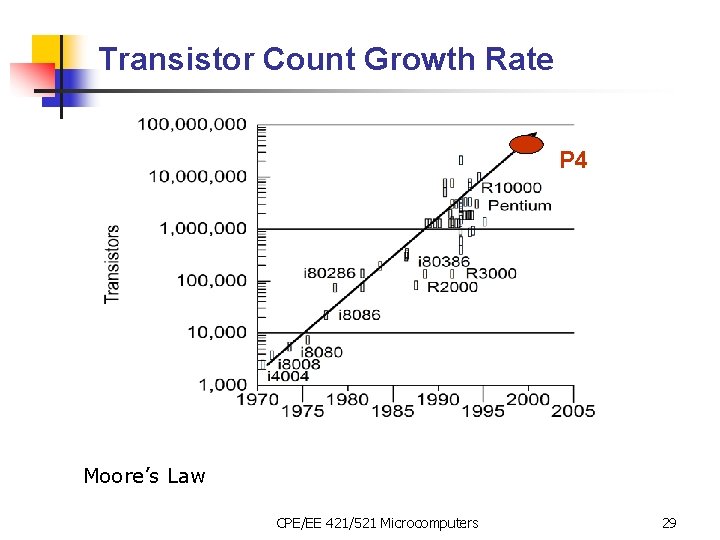

Transistor Count Growth Rate P 4 Moore’s Law CPE/EE 421/521 Microcomputers 29

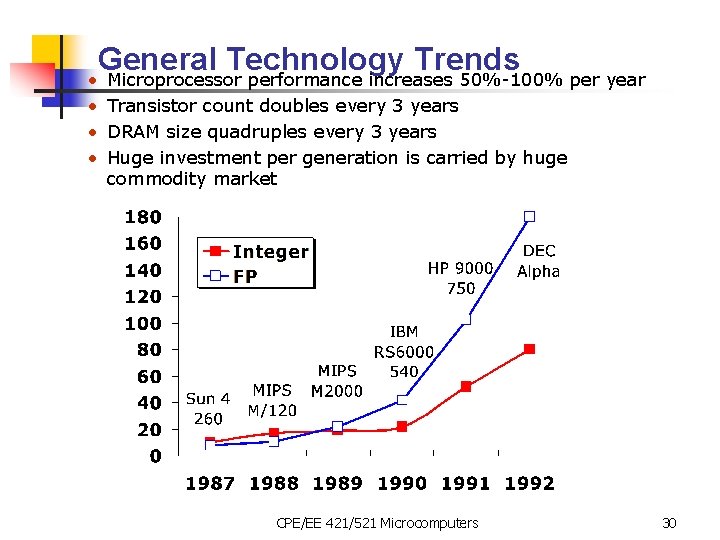

General Technology Trends • • Microprocessor performance increases 50%-100% per year Transistor count doubles every 3 years DRAM size quadruples every 3 years Huge investment per generation is carried by huge commodity market CPE/EE 421/521 Microcomputers 30

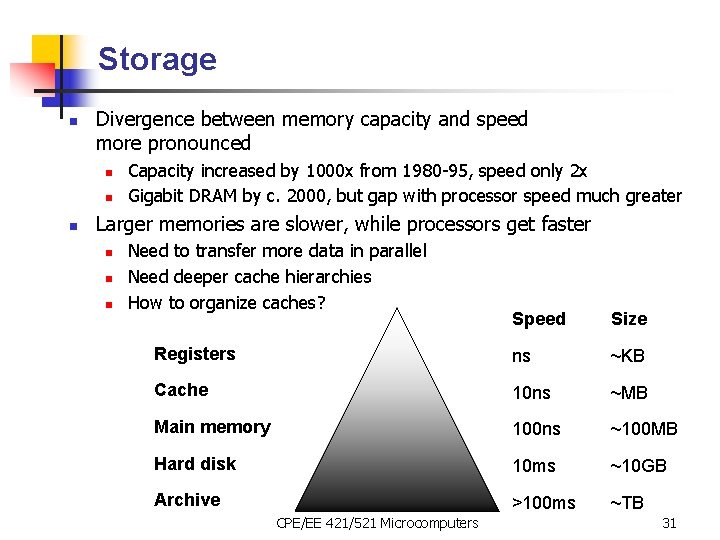

Storage n Divergence between memory capacity and speed more pronounced n n n Capacity increased by 1000 x from 1980 -95, speed only 2 x Gigabit DRAM by c. 2000, but gap with processor speed much greater Larger memories are slower, while processors get faster n n n Need to transfer more data in parallel Need deeper cache hierarchies How to organize caches? Speed Size Registers ns ~KB Cache 10 ns ~MB Main memory 100 ns ~100 MB Hard disk 10 ms ~10 GB Archive >100 ms ~TB CPE/EE 421/521 Microcomputers 31

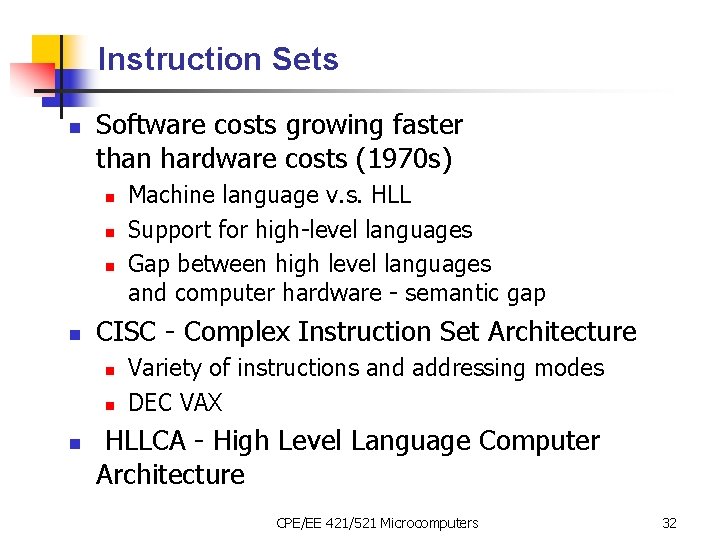

Instruction Sets n Software costs growing faster than hardware costs (1970 s) n n CISC - Complex Instruction Set Architecture n n n Machine language v. s. HLL Support for high-level languages Gap between high level languages and computer hardware - semantic gap Variety of instructions and addressing modes DEC VAX HLLCA - High Level Language Computer Architecture CPE/EE 421/521 Microcomputers 32

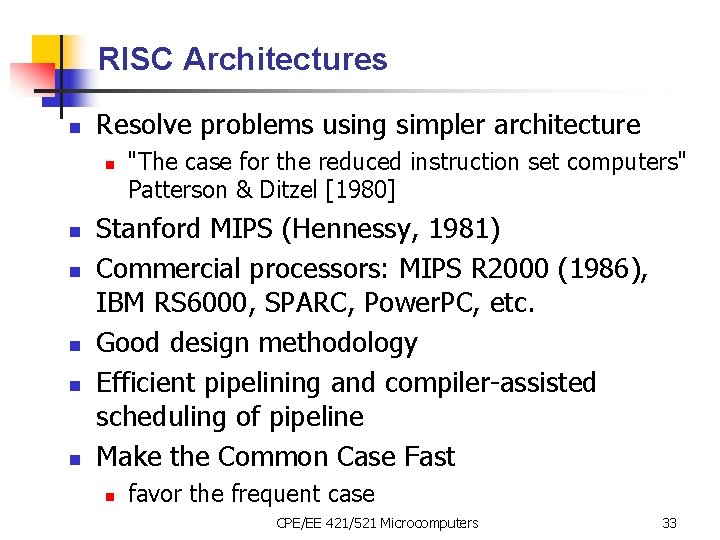

RISC Architectures n Resolve problems using simpler architecture n n n "The case for the reduced instruction set computers" Patterson & Ditzel [1980] Stanford MIPS (Hennessy, 1981) Commercial processors: MIPS R 2000 (1986), IBM RS 6000, SPARC, Power. PC, etc. Good design methodology Efficient pipelining and compiler-assisted scheduling of pipeline Make the Common Case Fast n favor the frequent case CPE/EE 421/521 Microcomputers 33

![Program Execution Time For all instructions in the instruction set processor cycle time [s] Program Execution Time For all instructions in the instruction set processor cycle time [s]](http://slidetodoc.com/presentation_image_h/c2a999d42e2907bc9123fa3da27539d0/image-34.jpg)

Program Execution Time For all instructions in the instruction set processor cycle time [s] cycles per instruction count CPE/EE 421/521 Microcomputers 34

![80 x 86 Instruction Mix for SPECint 92 Programs [Pat. Hen 96] 42% 70% 80 x 86 Instruction Mix for SPECint 92 Programs [Pat. Hen 96] 42% 70%](http://slidetodoc.com/presentation_image_h/c2a999d42e2907bc9123fa3da27539d0/image-35.jpg)

80 x 86 Instruction Mix for SPECint 92 Programs [Pat. Hen 96] 42% 70% CPE/EE 421/521 Microcomputers 35

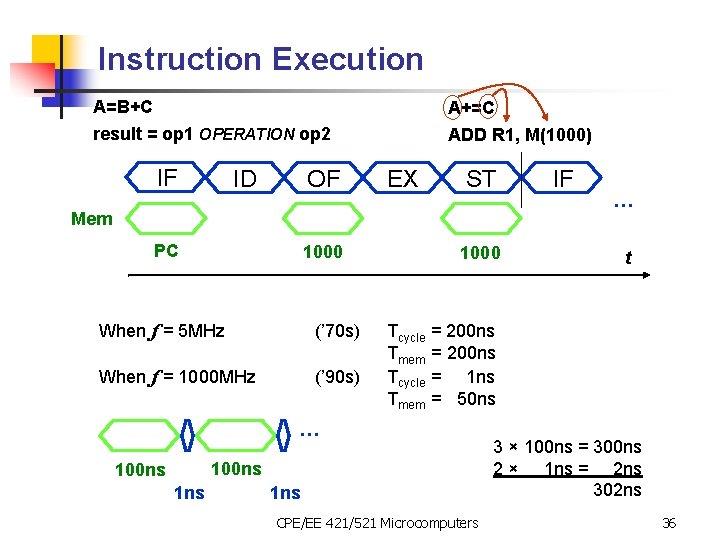

Instruction Execution A=B+C result = op 1 OPERATION op 2 IF ID OF A+=C ADD R 1, M(1000) EX ST Mem PC 1000 When f = 5 MHz (’ 70 s) When f = 1000 MHz (’ 90 s) 1000 100 ns 1 ns … t Tcycle = 200 ns Tmem = 200 ns Tcycle = 1 ns Tmem = 50 ns … 100 ns IF 1 ns CPE/EE 421/521 Microcomputers 3 × 100 ns = 300 ns 2 × 1 ns = 2 ns 302 ns 36

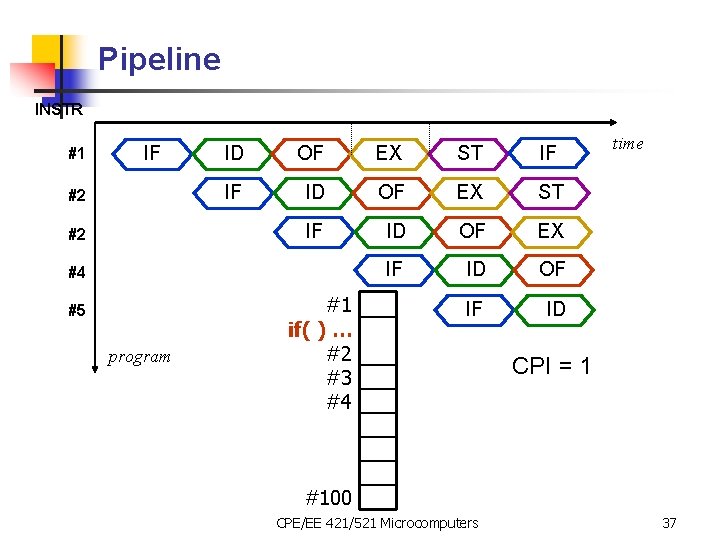

Pipeline INSTR #1 IF #2 #2 ID OF EX ST IF IF ID OF EX ST IF ID OF EX IF ID OF IF ID #4 #5 program #1 if( ) … #2 #3 #4 time CPI = 1 #100 CPE/EE 421/521 Microcomputers 37

- Slides: 37