CPCS 361 Operating Systems I Chapter 8 Main

- Slides: 54

ﺑﺴﻢ ﺍﻟﻠﻪ ﺍﻟﺮﺣﻤﻦ ﺍﻟﺮﺣﻴﻢ CPCS 361 – Operating Systems I Chapter 8: Main Memory Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

Chapter 8: Memory Management Background Swapping Contiguous Memory Allocation Paging Structure of the Page Table Segmentation Example: The Intel Pentium Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 2

Objectives To provide a detailed description of various ways of organizing memory hardware To discuss various memory-management techniques, including paging and segmentation To provide a detailed description of the Intel Pentium, which supports both pure segmentation and segmentation with paging Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 3

Background Memory is central to the operation of a modern computer system Memory consists of a large array of words or bytes each of with its own address Instruction-execution cycle: Fetching instructions from memory, may be the operands, and storing the results back to the memory Program must be brought (from disk) into memory and placed within a process for it to be run Main memory and registers are only storage CPU can access directly. If the data are not in the memory, they must be moved there before the CPU can operate on them 4 Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

Background Register access in one CPU clock (or less) Main memory can take many cycles of the CPU clock to complete CPU needs to stall since it does not have the required data to complete the instruction. This situation is intolerable because of the frequency of memory access. The remedy is to add fast memory: cache Cache sits between main memory and CPU registers Protection of memory required to ensure correct operation Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 5

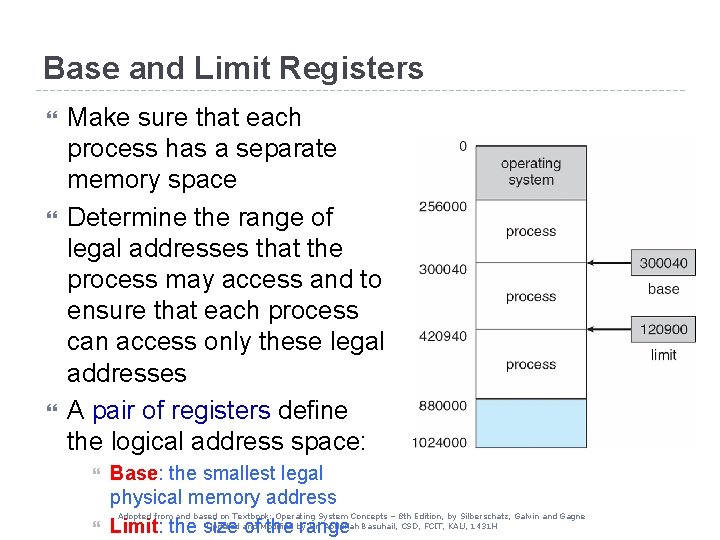

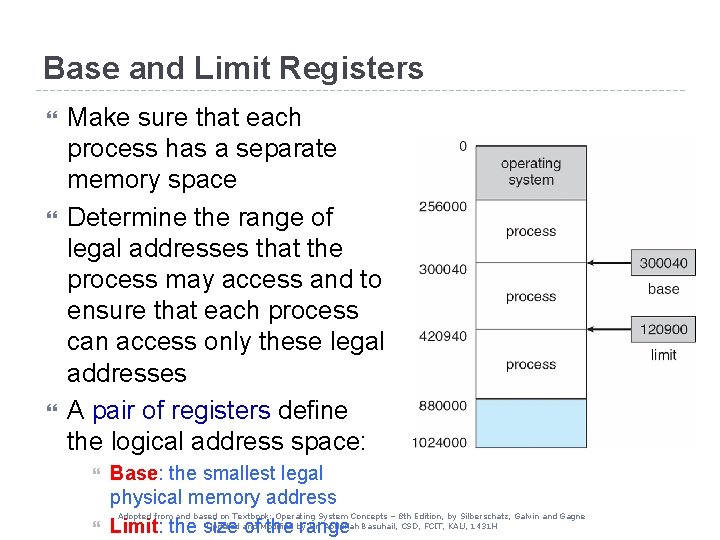

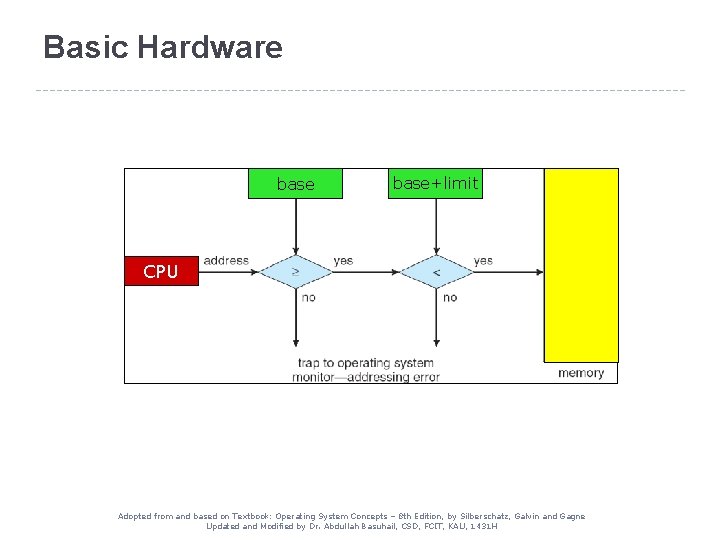

Base and Limit Registers Make sure that each process has a separate memory space Determine the range of legal addresses that the process may access and to ensure that each process can access only these legal addresses A pair of registers define the logical address space: Base: the smallest legal physical memory address Limit: the size of the range Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

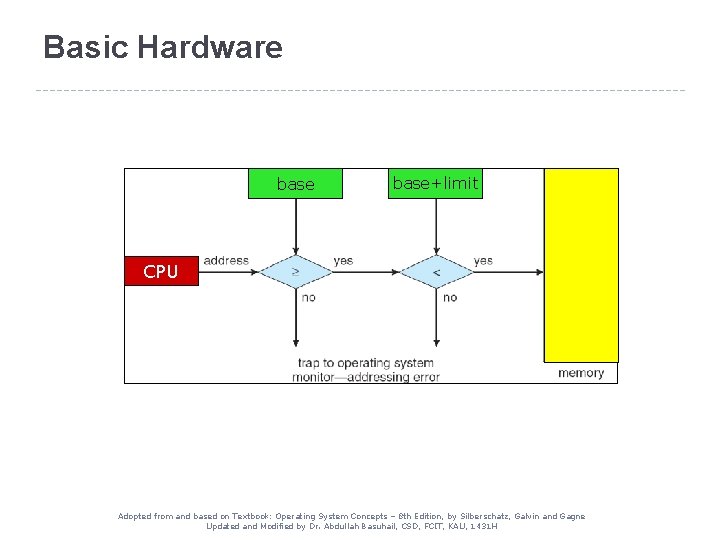

Basic Hardware Protection of memory space is accomplished by having the CPU hardware compare every address generated in user mode with the registers An attempt by a program executing in user mode to access operating system memory or other users’ memory results in a trap to the operating system, which treats the attempt as a fatal error Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

Basic Hardware base+limit CPU Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

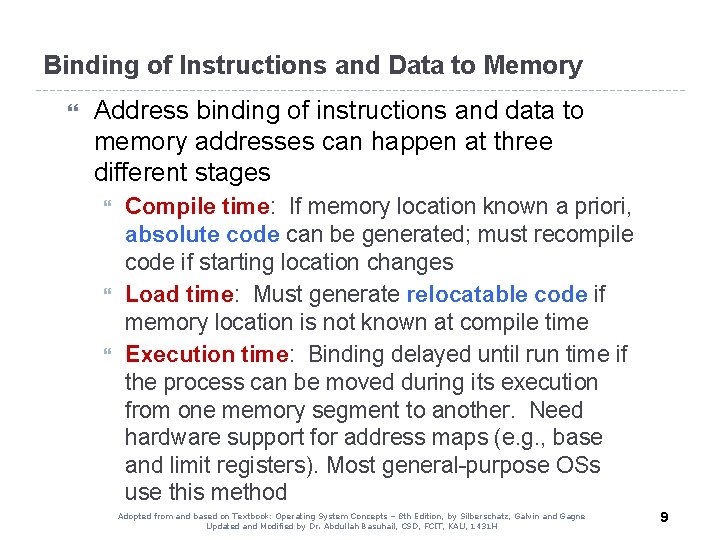

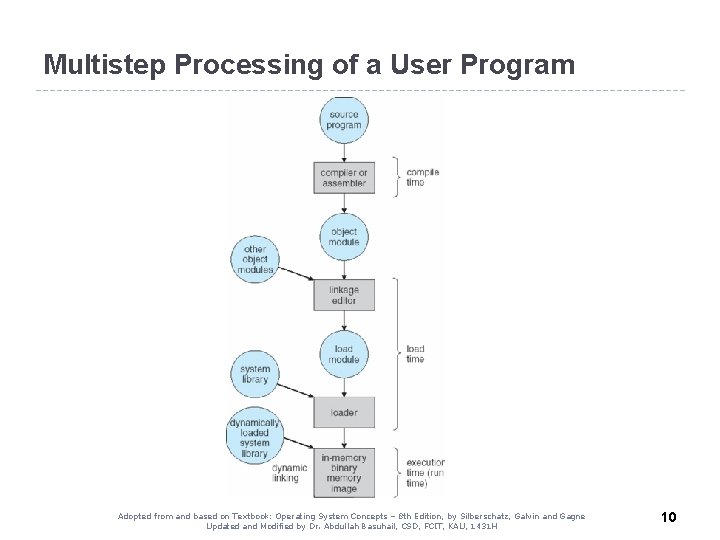

Binding of Instructions and Data to Memory Address binding of instructions and data to memory addresses can happen at three different stages Compile time: If memory location known a priori, absolute code can be generated; must recompile code if starting location changes Load time: Must generate relocatable code if memory location is not known at compile time Execution time: Binding delayed until run time if the process can be moved during its execution from one memory segment to another. Need hardware support for address maps (e. g. , base and limit registers). Most general-purpose OSs use this method Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 9

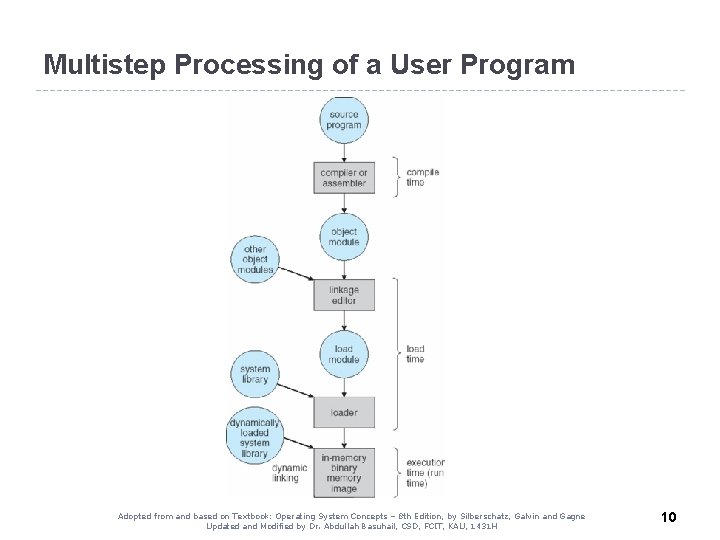

Multistep Processing of a User Program Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 10

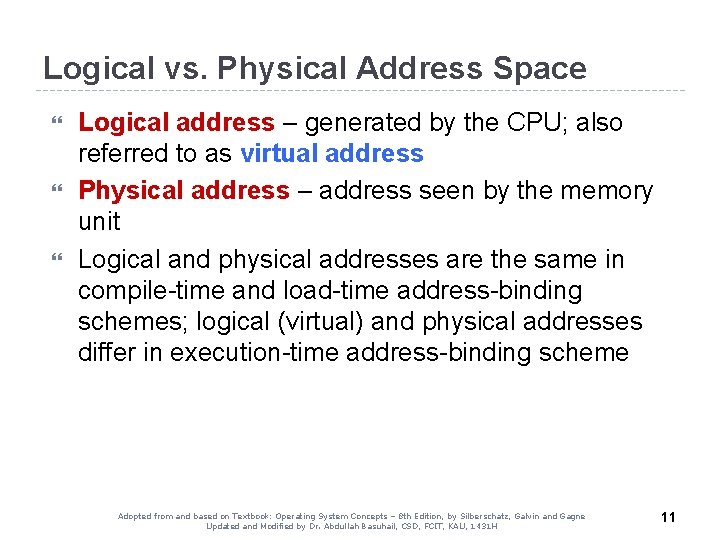

Logical vs. Physical Address Space Logical address – generated by the CPU; also referred to as virtual address Physical address – address seen by the memory unit Logical and physical addresses are the same in compile-time and load-time address-binding schemes; logical (virtual) and physical addresses differ in execution-time address-binding scheme Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 11

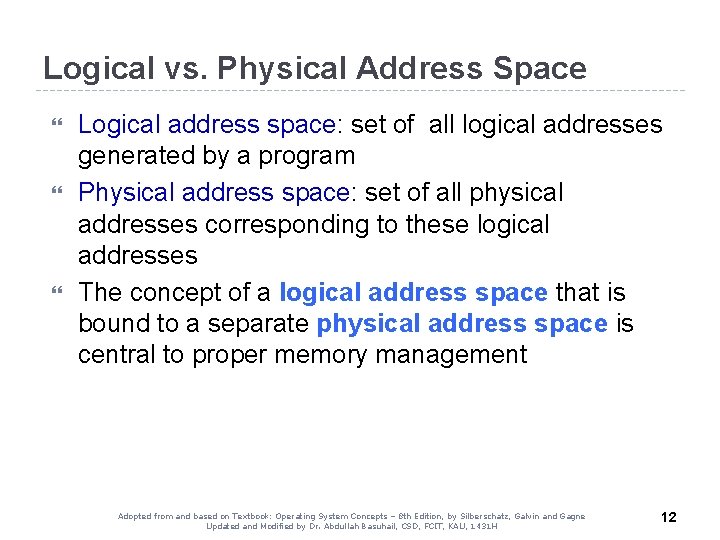

Logical vs. Physical Address Space Logical address space: set of all logical addresses generated by a program Physical address space: set of all physical addresses corresponding to these logical addresses The concept of a logical address space that is bound to a separate physical address space is central to proper memory management Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 12

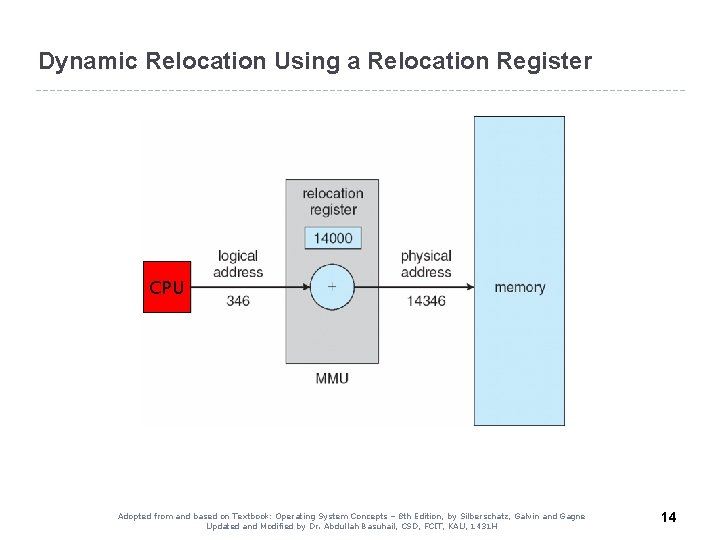

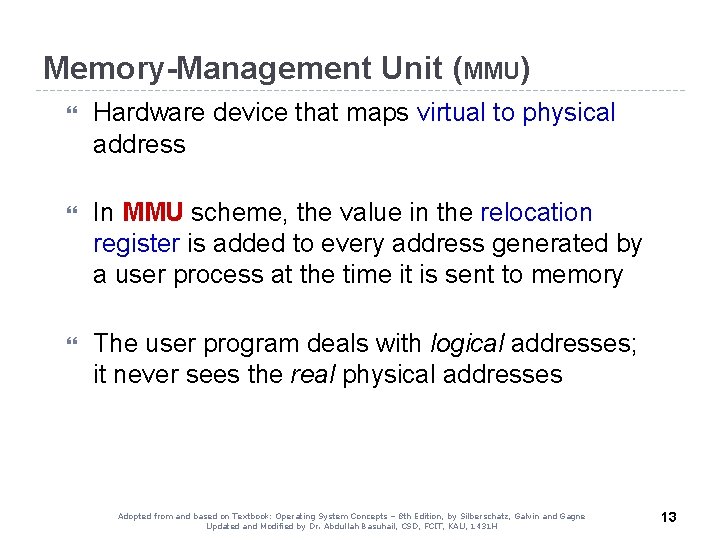

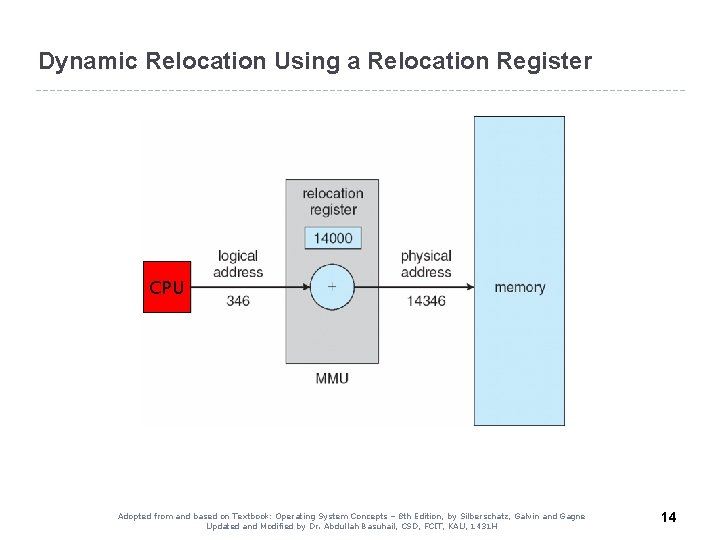

Memory-Management Unit (MMU) Hardware device that maps virtual to physical address In MMU scheme, the value in the relocation register is added to every address generated by a user process at the time it is sent to memory The user program deals with logical addresses; it never sees the real physical addresses Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 13

Dynamic Relocation Using a Relocation Register CPU Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 14

Dynamic Loading Routine is not loaded until it is called Advantage: better memory-space utilization; unused routine is never loaded Useful when large amounts of code are needed to handle infrequently occurring cases No special support from the operating system is required; implemented through program design Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 15

Dynamic Linking postponed until execution time Small piece of code, stub, used to locate the appropriate memory-resident library routine Stub replaces itself with the address of the routine, and executes the routine The next time that particular code segment is reached, the library routine is executed directly, incurring no cost for dynamic linking Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 16

Dynamic Linking Under this scheme, all processes that use a language library execute only one copy of the library code Operating system needed to check if routine is in processes’ memory address Dynamic linking is particularly useful for libraries System also known as shared libraries Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 17

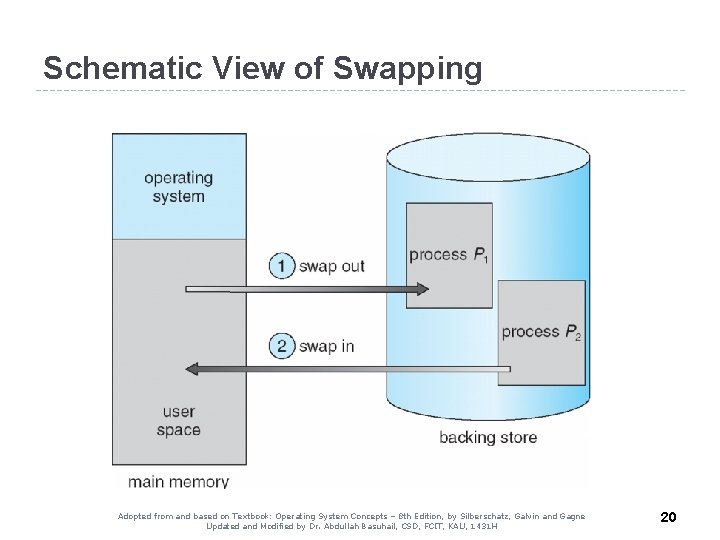

Swapping A process can be swapped temporarily out of memory to a backing store, and then brought back into memory for continued execution Roll out, roll in – swapping variant used for prioritybased scheduling algorithms; lower-priority process is swapped out so higher-priority process can be loaded and executed Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

Swapping Normally, a process swapped back into the same memory space it occupied previously. This restriction is dictated by the method address binding: If binding is done at assembly or load time, then the process cannot be easily moved to a different location If execution time binding is used, the process can be swapped into a different memory space, because the physical addresses are computed during execution time Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

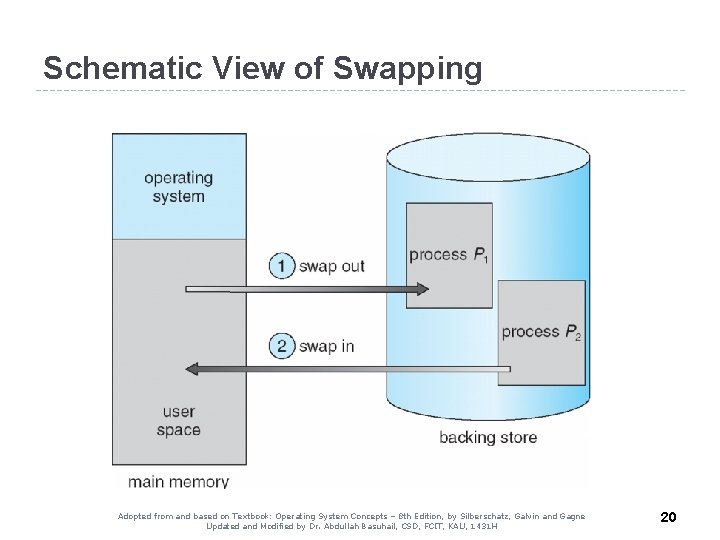

Schematic View of Swapping Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 20

Swapping requires a Backing store – fast disk large enough to accommodate copies of all memory images for all users; must provide direct access to these memory images Whenever the CPU scheduler decides to execute a process, it calls the dispatcher which checks to see whether the next process is in memory. If it is not, and if there is no free memory region, the dispatcher swaps out a process currently in memory and swaps in the desired process. It then reloads registers and transfers control to the selected process Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

Swapping Major part of swap time is transfer time (contextswitch time); total transfer time is directly proportional to the amount of memory swapped Example: User process of 10 MB in size, backing store transfer rate of 40 MB/second. Transfer time = 10 MB / 40 MB/second = ¼ sec. = 250 ms Assuming no head seeks are necessary, and assuming an average latency of 8 ms, the swap time is 258 ms. Since one must both swap out and swap in, the total swap time is about 516 ms (0. 516 sec. ). e. g. , In RR scheduling, time quantum should be substantially > 0. 516 seconds. Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

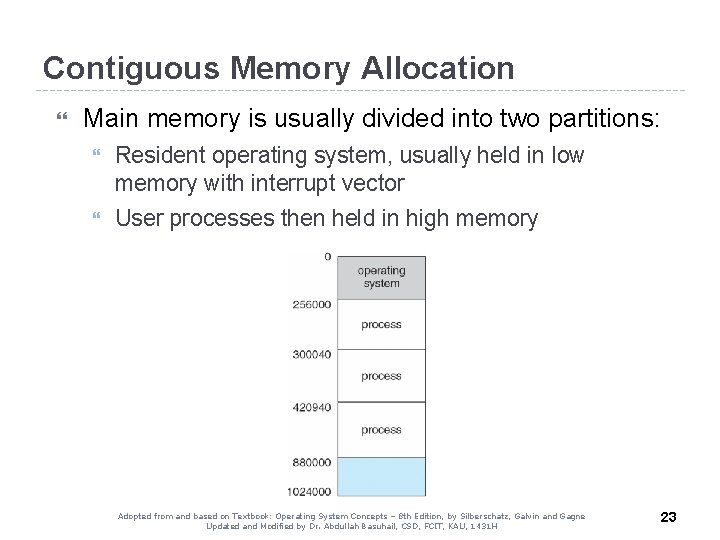

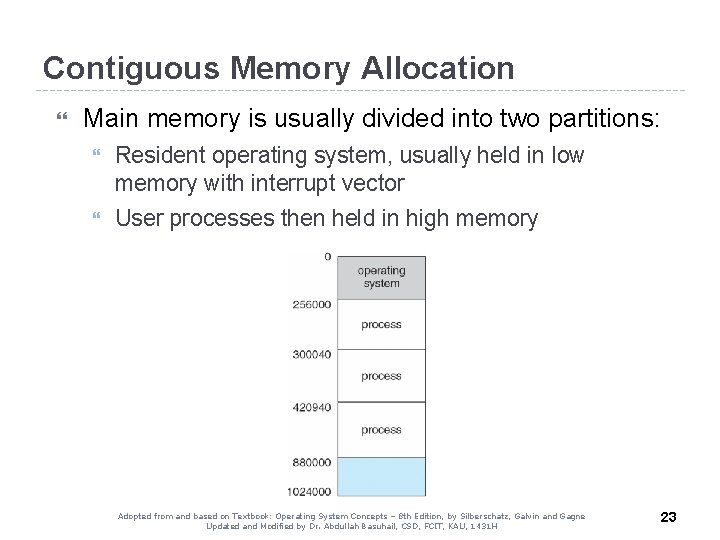

Contiguous Memory Allocation Main memory is usually divided into two partitions: Resident operating system, usually held in low memory with interrupt vector User processes then held in high memory Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 23

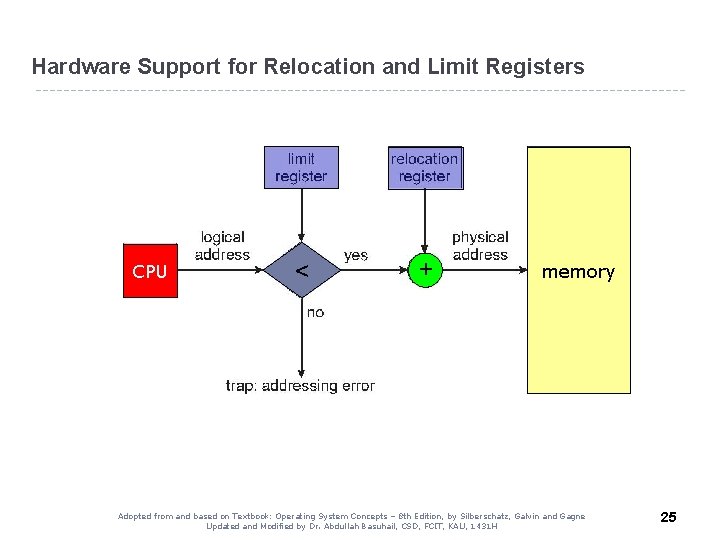

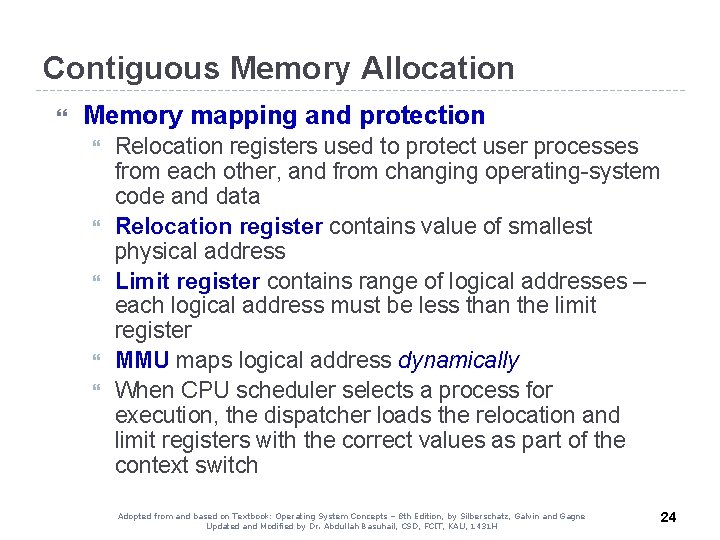

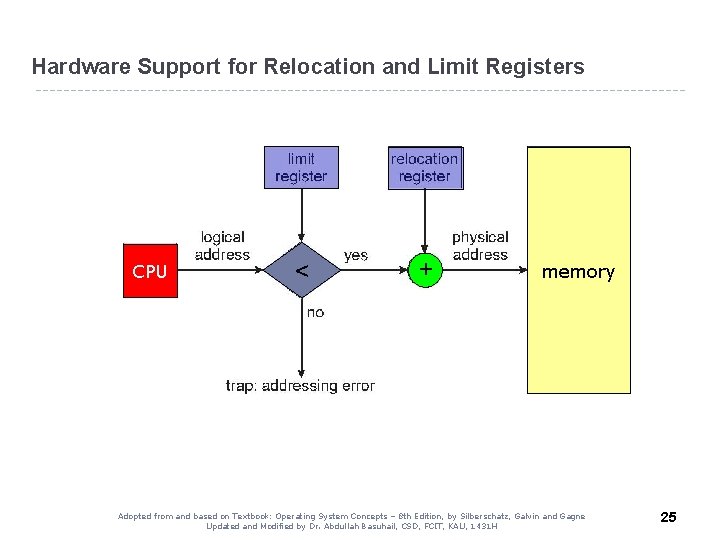

Contiguous Memory Allocation Memory mapping and protection Relocation registers used to protect user processes from each other, and from changing operating-system code and data Relocation register contains value of smallest physical address Limit register contains range of logical addresses – each logical address must be less than the limit register MMU maps logical address dynamically When CPU scheduler selects a process for execution, the dispatcher loads the relocation and limit registers with the correct values as part of the context switch Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 24

Hardware Support for Relocation and Limit Registers CPU < + memory Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 25

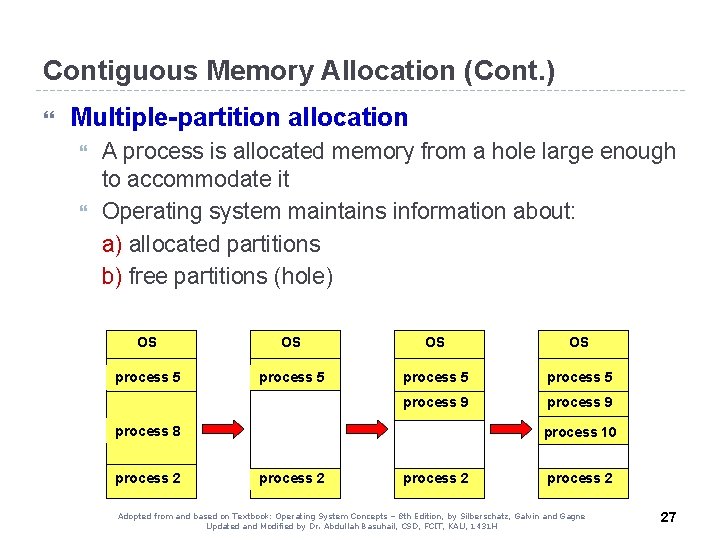

Contiguous Memory Allocation Multiple-partition allocation One of the simplest memory allocation methods is to divide memory into several fixed-sized partitions Each partition may contain exactly one process Degree of multiprogramming is bound by the # partitions Hole – block of available memory; holes of various size are scattered throughout memory Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 26

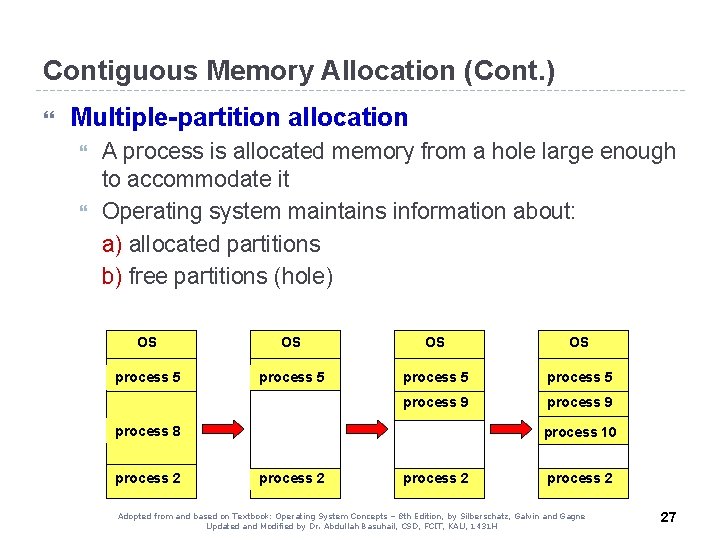

Contiguous Memory Allocation (Cont. ) Multiple-partition allocation A process is allocated memory from a hole large enough to accommodate it Operating system maintains information about: a) allocated partitions b) free partitions (hole) OS OS process 5 process 9 process 8 process 2 process 10 process 2 Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 27

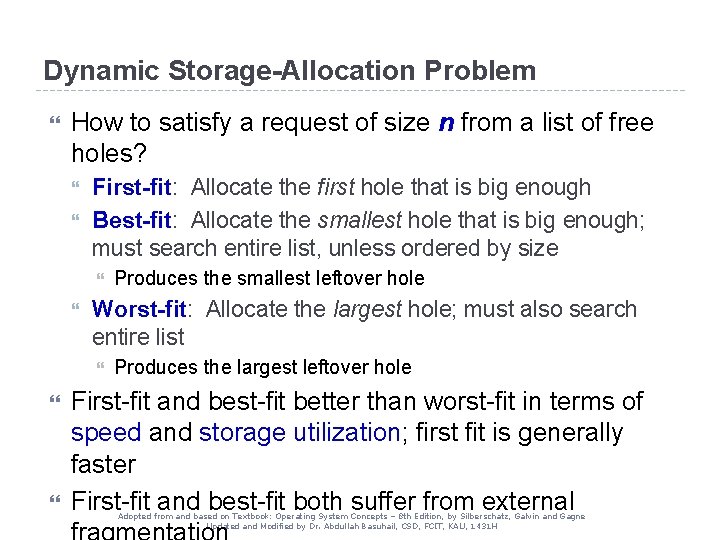

Dynamic Storage-Allocation Problem How to satisfy a request of size n from a list of free holes? First-fit: Allocate the first hole that is big enough Best-fit: Allocate the smallest hole that is big enough; must search entire list, unless ordered by size Worst-fit: Allocate the largest hole; must also search entire list Produces the smallest leftover hole Produces the largest leftover hole First-fit and best-fit better than worst-fit in terms of speed and storage utilization; first fit is generally faster First-fit and best-fit both suffer from external Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

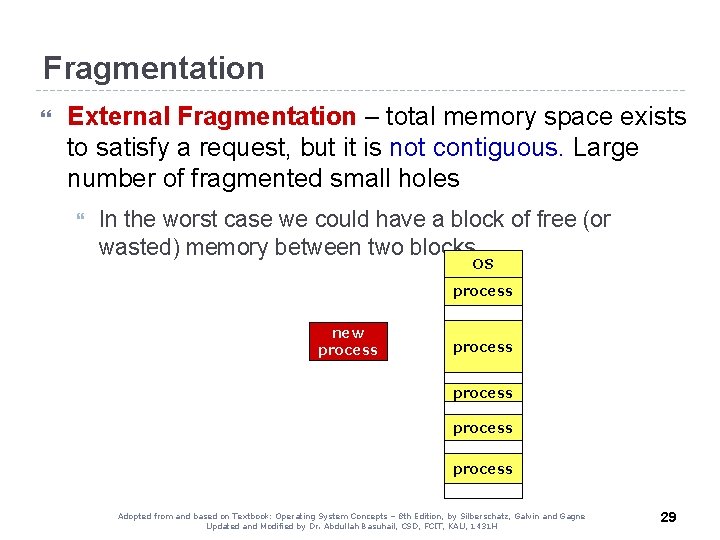

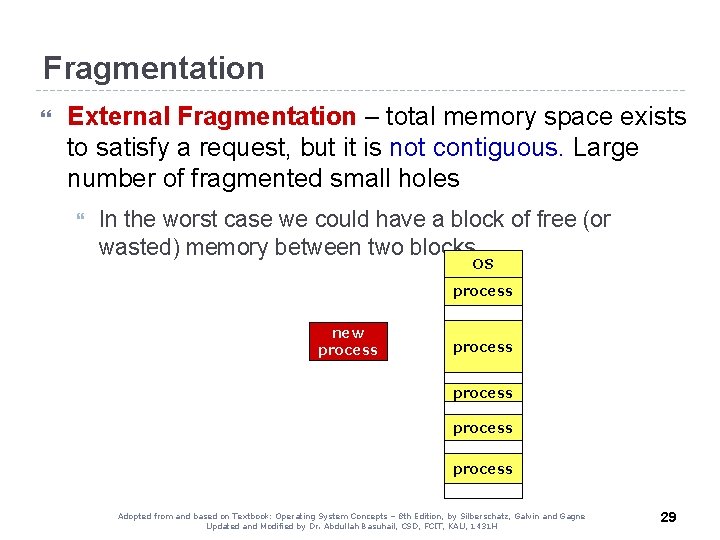

Fragmentation External Fragmentation – total memory space exists to satisfy a request, but it is not contiguous. Large number of fragmented small holes In the worst case we could have a block of free (or wasted) memory between two blocks OS process new process process Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 29

Fragmentation External Fragmentation 50 -percent rule: statistical analysis of first-fit rule reveals that, given N allocated blocks, another 0. 5 N blocks will be lost to fragmentation If all these small pieces of memory were in one big free block instead, we might be able to run several more processes Reduce external fragmentation by compaction Shuffle memory contents to place all free memory together in one large block Compaction is possible only if relocation is dynamic, and is done at execution time (cannot be done if relocation is static and done at assembly or load time) Can be expensive Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 30

Fragmentation Internal Fragmentation – allocated memory may be slightly larger than requested memory; this size difference is memory internal to a partition, but not being used (overhead to keep track of this hole will be substantially larger than the hole itself) e. g. A hole of 18, 564 bytes, and the next process request 18, 562 bytes, we are left with a hole of 2 bytes Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 31

Paging is a memory-management scheme that permits the physical address of a process to be noncontiguous Logical address space of a process can be noncontiguous; process is allocated physical memory whenever the latter is available Basic method: Divide physical memory into fixed-sized blocks called frames (size is power of 2, between 512 bytes and 16 Mbytes) Divide logical memory into blocks of same size called pages Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

Paging When a process is to be executed, its pages are loaded into any available memory frames from the backing store The backing store is divided into fixed-sized blocks that are of the same size as the memory frames To run a program of size n pages, need to find n free frames and load program Set up a page table to translate logical to physical addresses Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

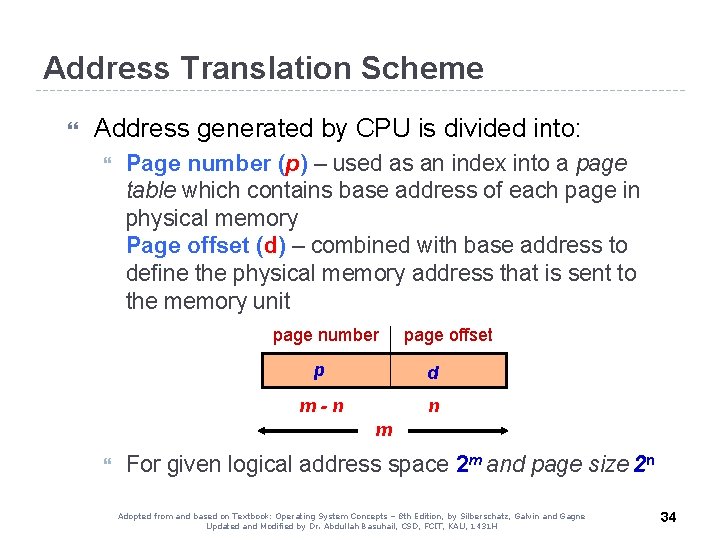

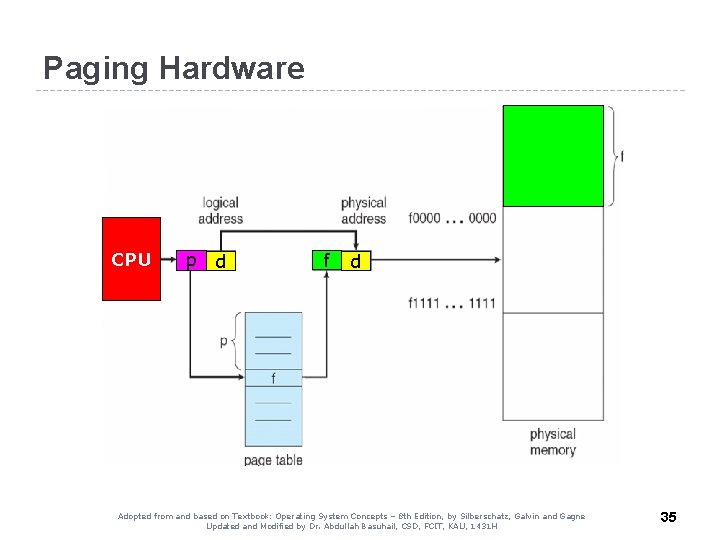

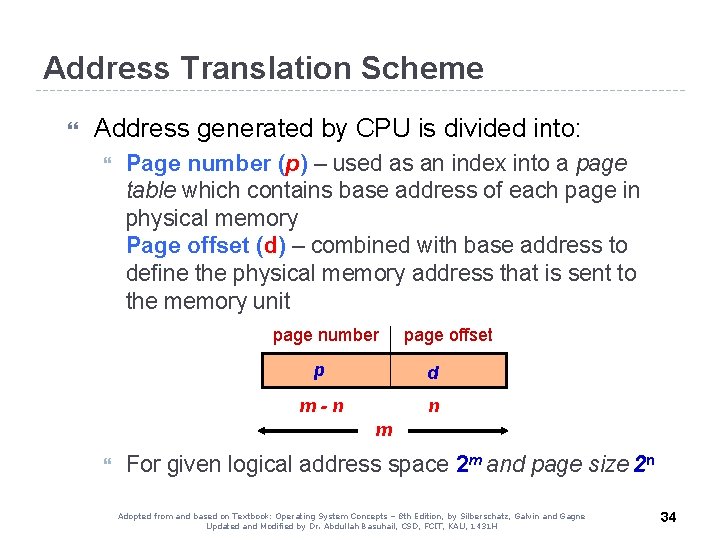

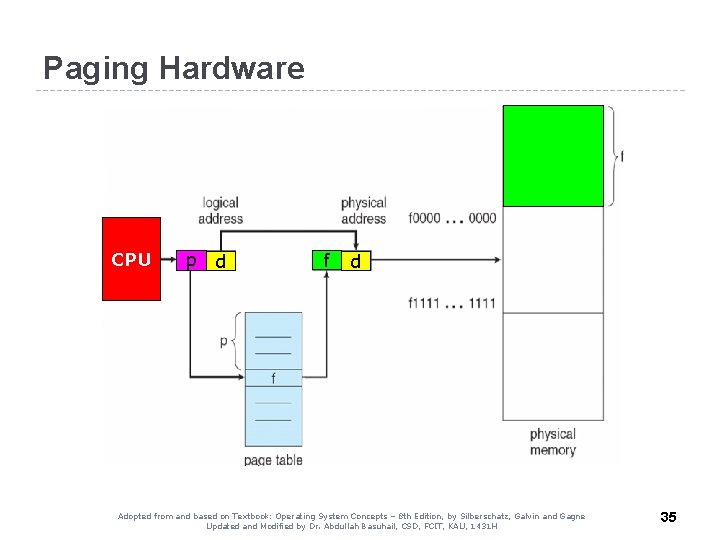

Address Translation Scheme Address generated by CPU is divided into: Page number (p) – used as an index into a page table which contains base address of each page in physical memory Page offset (d) – combined with base address to define the physical memory address that is sent to the memory unit page number page offset p d m-n n m For given logical address space 2 m and page size 2 n Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 34

Paging Hardware CPU p d f d Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 35

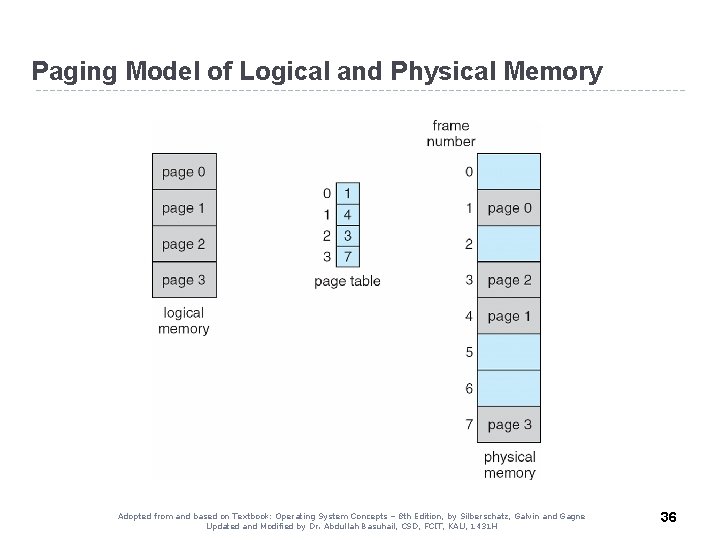

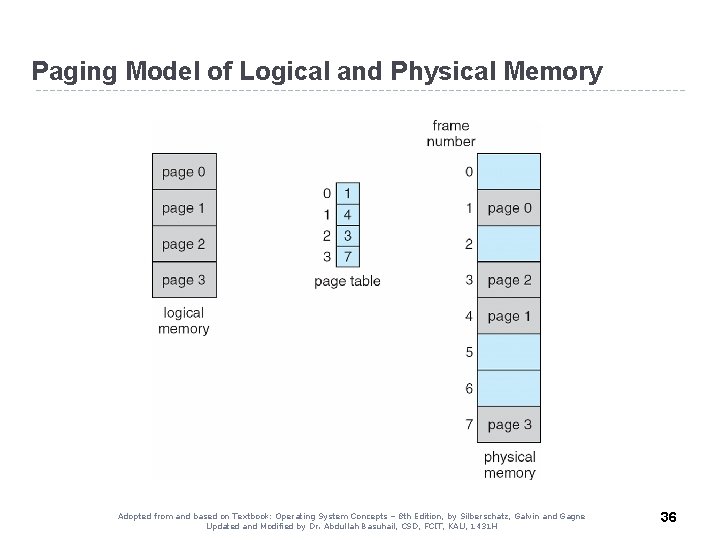

Paging Model of Logical and Physical Memory Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 36

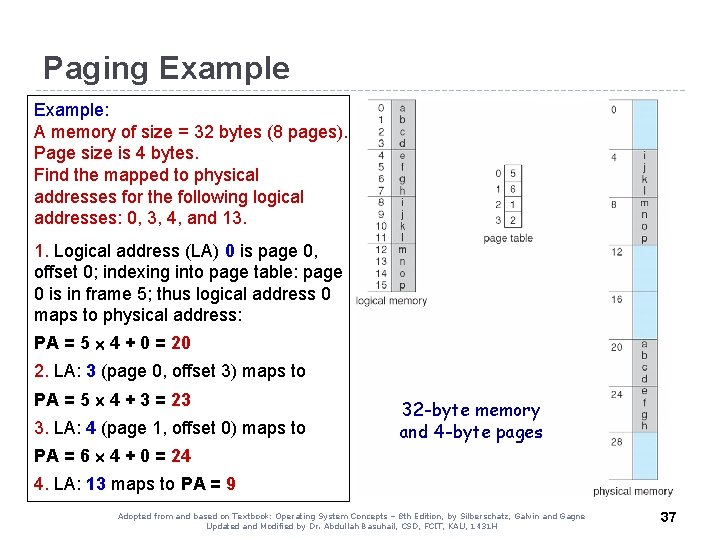

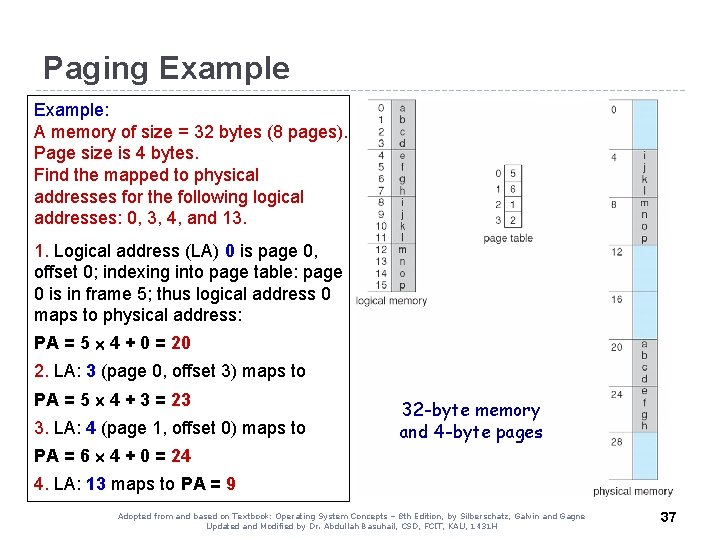

Paging Example: A memory of size = 32 bytes (8 pages). Page size is 4 bytes. Find the mapped to physical addresses for the following logical addresses: 0, 3, 4, and 13. 1. Logical address (LA) 0 is page 0, offset 0; indexing into page table: page 0 is in frame 5; thus logical address 0 maps to physical address: PA = 5 4 + 0 = 20 2. LA: 3 (page 0, offset 3) maps to PA = 5 4 + 3 = 23 3. LA: 4 (page 1, offset 0) maps to 32 -byte memory and 4 -byte pages PA = 6 4 + 0 = 24 4. LA: 13 maps to PA = 9 Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 37

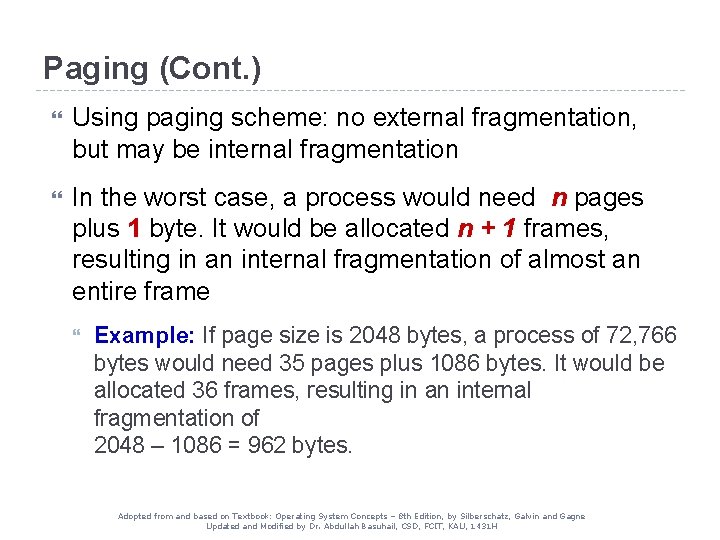

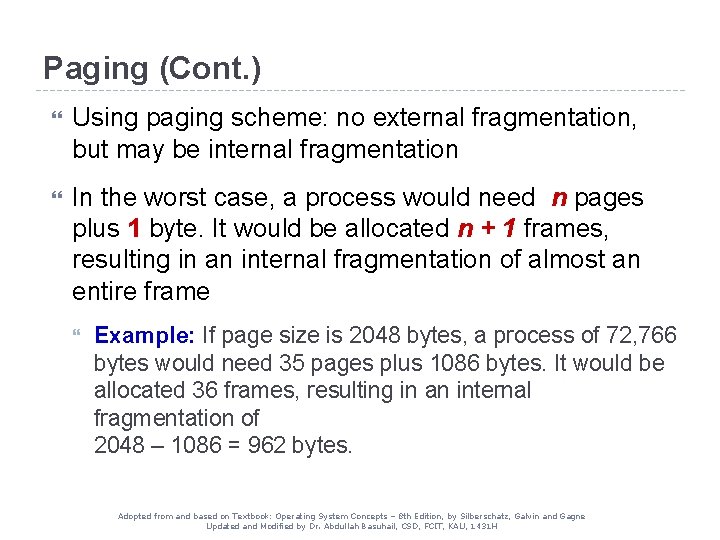

Paging (Cont. ) Using paging scheme: no external fragmentation, but may be internal fragmentation In the worst case, a process would need n pages plus 1 byte. It would be allocated n + 1 frames, resulting in an internal fragmentation of almost an entire frame Example: If page size is 2048 bytes, a process of 72, 766 bytes would need 35 pages plus 1086 bytes. It would be allocated 36 frames, resulting in an internal fragmentation of 2048 – 1086 = 962 bytes. Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

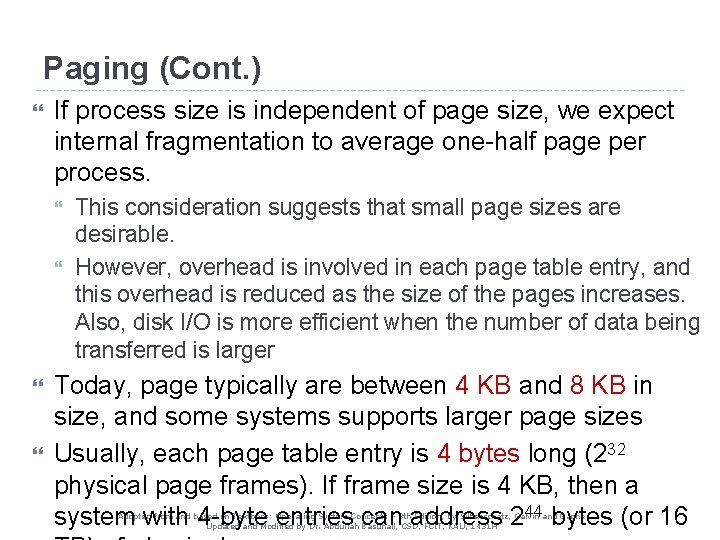

Paging (Cont. ) If process size is independent of page size, we expect internal fragmentation to average one-half page per process. This consideration suggests that small page sizes are desirable. However, overhead is involved in each page table entry, and this overhead is reduced as the size of the pages increases. Also, disk I/O is more efficient when the number of data being transferred is larger Today, page typically are between 4 KB and 8 KB in size, and some systems supports larger page sizes Usually, each page table entry is 4 bytes long (232 physical page frames). If frame size is 4 KB, then a system with 4 -byte entries can address 244 bytes (or 16 Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

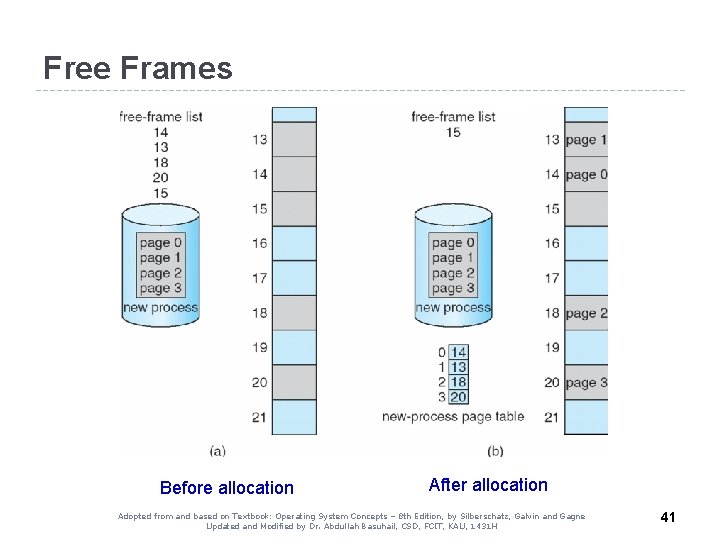

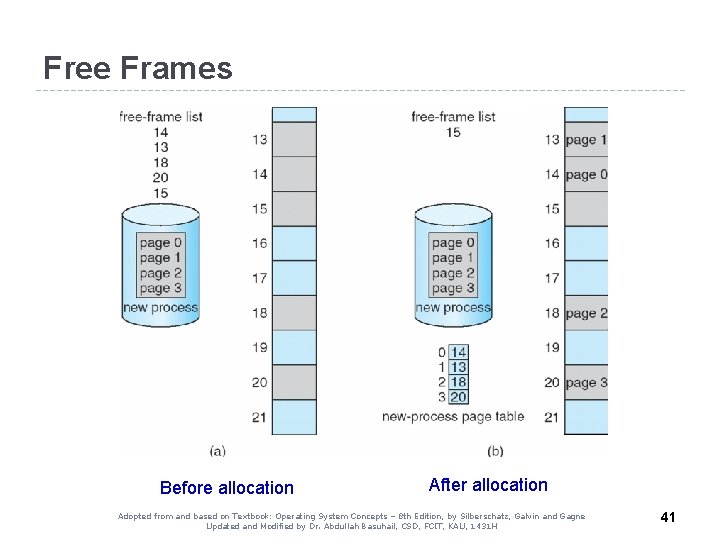

Paging (Cont. ) When a process arrives in the system to be executed Its size, expressed in pages, is examined Each page of the process needs one frame. Thus if the process requires n pages, at least n frames must be available in memory If n frames are available, they are allocated to this arriving process The first page of the process is loaded into one of the allocated frames, and the frame number is put in the page table for this process The next page is loaded into another frame, and its frame number is put in the page table, and so on Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

Free Frames Before allocation After allocation Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 41

Segmentation Do users think of memory as a linear array of bytes, some containing instructions other containing data? Most people would say no Users prefer to view memory as a collection of variable-sized segments, with no necessary ordering among segments Elements within a segment are identified by their offset from the beginning of the segment For example: The 1 st statement of the program The 5 th instruction of the sqrt() Memory-management scheme that supports user view of memory Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

Segmentation (Cont. ) A program is a collection of segments A segment is a logical unit such as: main program procedure function method object local variables, global variables common block stack symbol table arrays Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 43

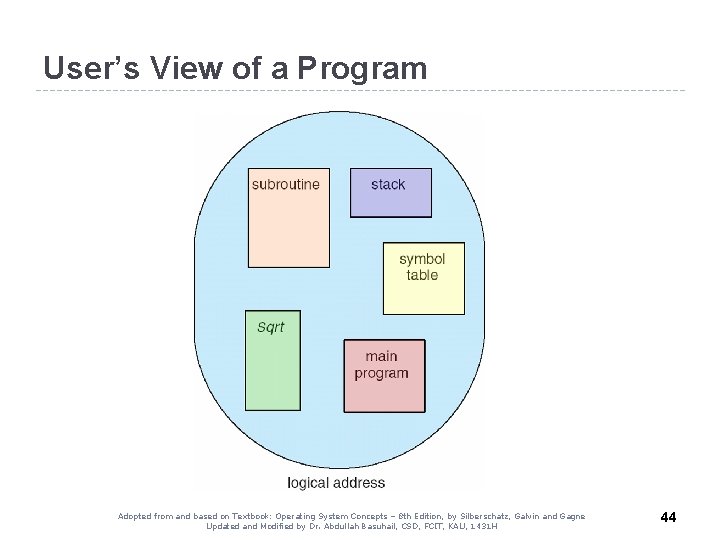

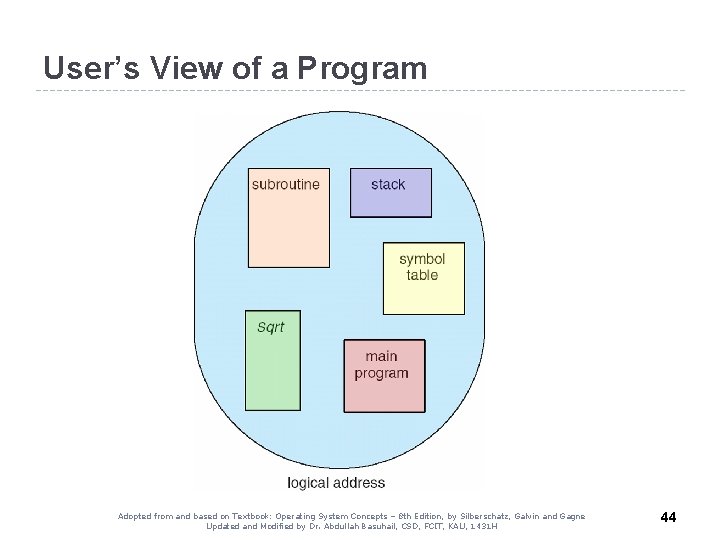

User’s View of a Program Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 44

Segmentation Architecture A logical address space is a collection of segments Each segment has a name and a length The addresses specify both the segment name and the offset within the segment The user specifies each address by two quantities (contrast this with the paging system): Segment name Offset For simplicity of implementation, segments are numbered and are referred to by a segment number rather than by a segment name Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

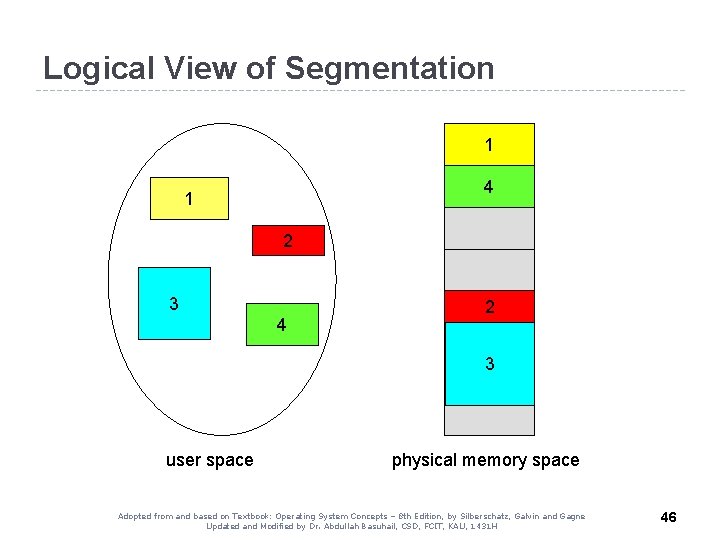

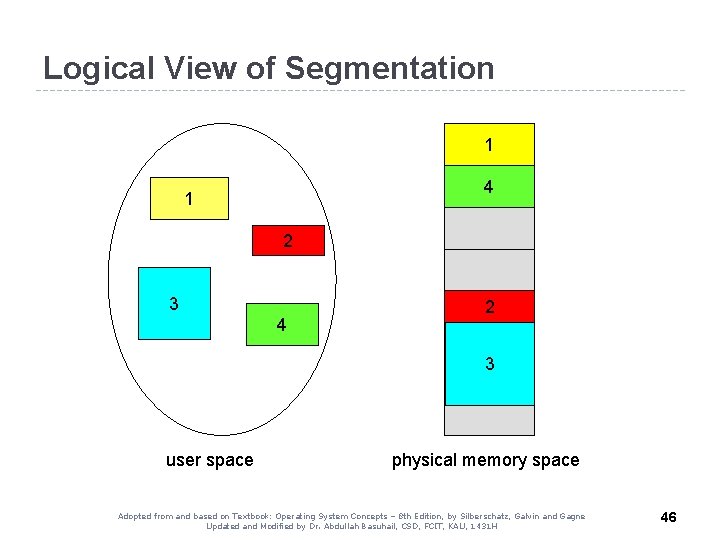

Logical View of Segmentation 11 44 1 2 3 4 22 33 user space physical memory space Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 46

Segmentation Architecture (Cont. ) Logical address consists of a two tuple: < segment-number, segment-number offset > Normally, the user program is compiled, and the compiler automatically constructs segments reflecting the input program C program might create separate segments for the following: 1. 2. 3. 4. 5. Code Global variables Heap, from which memory is allocated Stacks used by each thread Standard C library The loader would take all these segments and assign them segment numbers Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

Segmentation Architecture (Cont. ) Although the user can now refer to objects in the program by a two-dimensional address, the actual physical memory is still a one-dimensional sequence of bytes Implementation to map 2 -D (user) into 1 -D (physical) addresses is needed Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

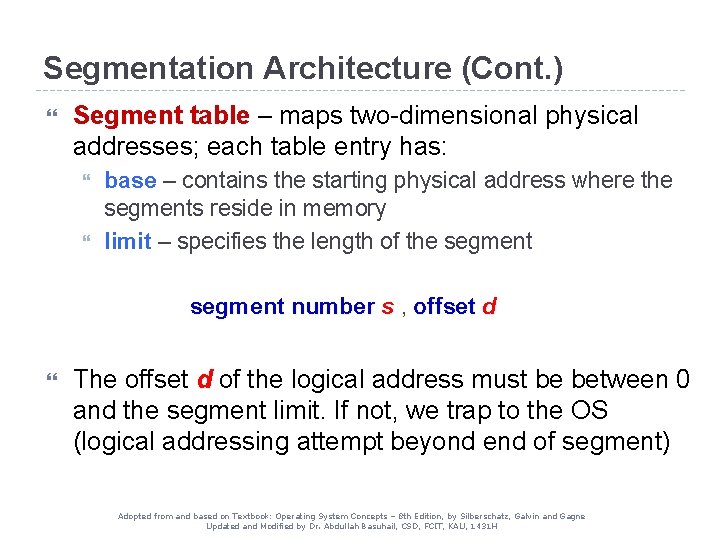

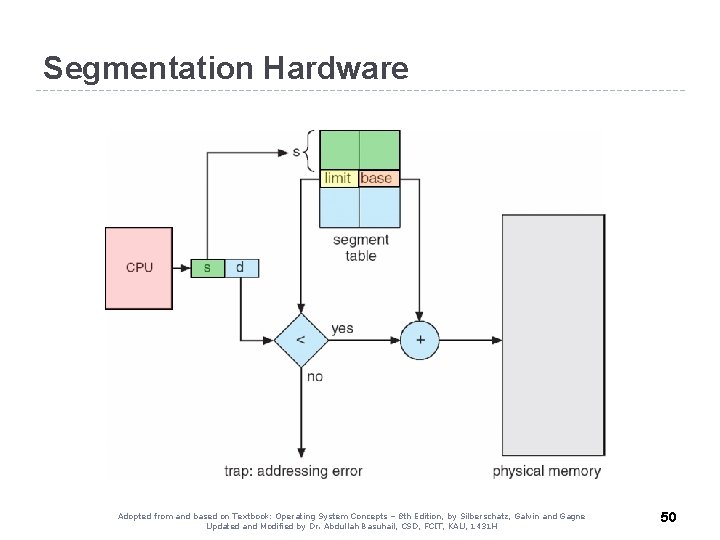

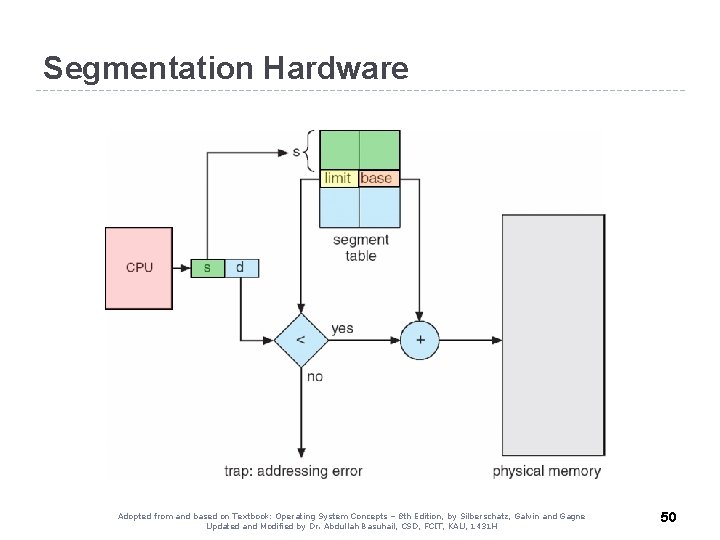

Segmentation Architecture (Cont. ) Segment table – maps two-dimensional physical addresses; each table entry has: base – contains the starting physical address where the segments reside in memory limit – specifies the length of the segment number s , offset d The offset d of the logical address must be between 0 and the segment limit. If not, we trap to the OS (logical addressing attempt beyond end of segment) Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

Segmentation Hardware Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 50

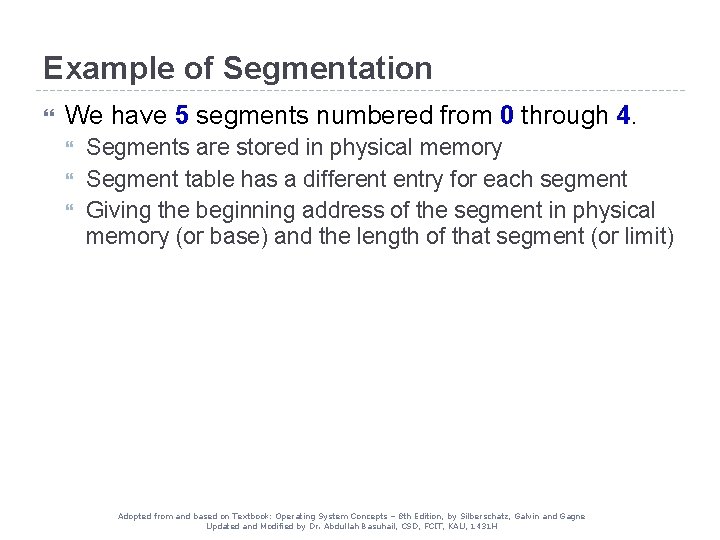

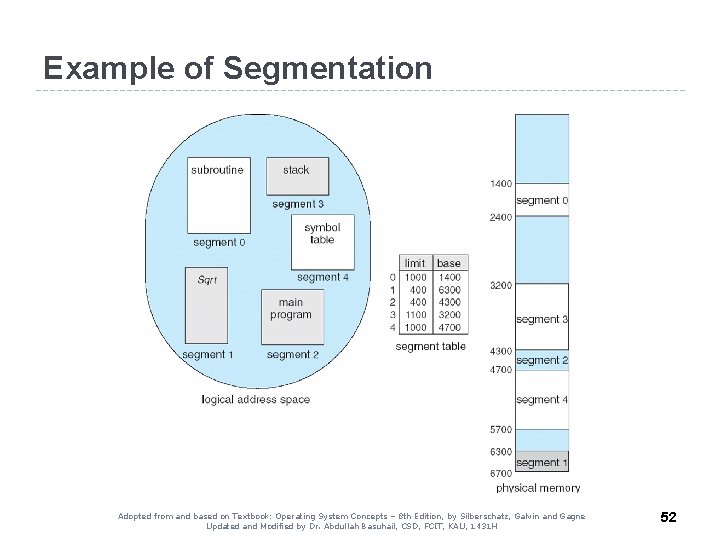

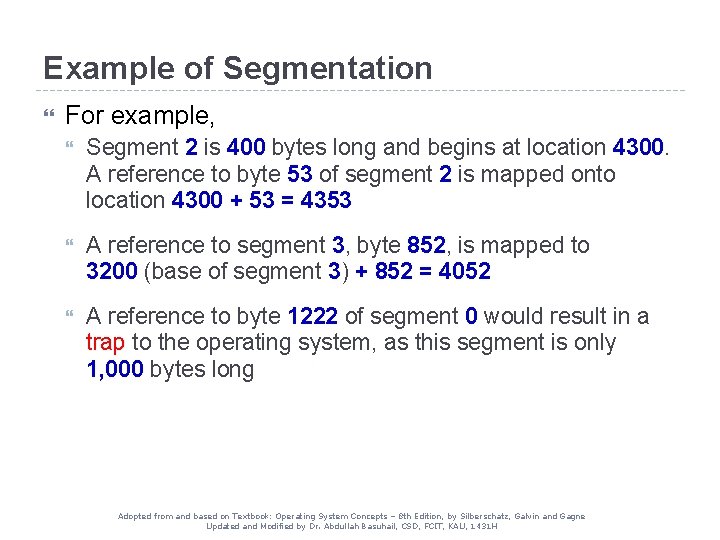

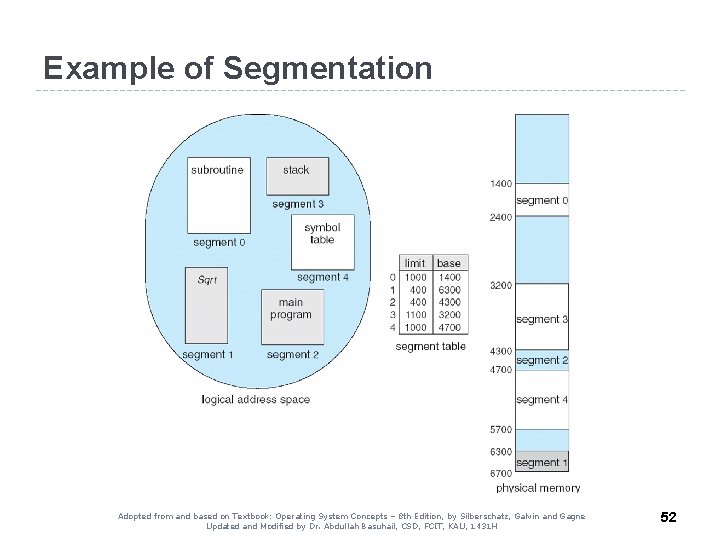

Example of Segmentation We have 5 segments numbered from 0 through 4. Segments are stored in physical memory Segment table has a different entry for each segment Giving the beginning address of the segment in physical memory (or base) and the length of that segment (or limit) Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

Example of Segmentation Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H 52

Example of Segmentation For example, Segment 2 is 400 bytes long and begins at location 4300. A reference to byte 53 of segment 2 is mapped onto location 4300 + 53 = 4353 A reference to segment 3, byte 852, is mapped to 3200 (base of segment 3) + 852 = 4052 A reference to byte 1222 of segment 0 would result in a trap to the operating system, as this segment is only 1, 000 bytes long Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H

End of Chapter 8 Adopted from and based on Textbook: Operating System Concepts – 8 th Edition, by Silberschatz, Galvin and Gagne Updated and Modified by Dr. Abdullah Basuhail, CSD, FCIT, KAU, 1431 H