CourtesyThanks to Texas Instruments C 10 Set instructiuni

![Instructiuni Logice • Operatii Logice cu acumulatorul field 4=field 3 [ + ] field Instructiuni Logice • Operatii Logice cu acumulatorul field 4=field 3 [ + ] field](https://slidetodoc.com/presentation_image_h2/8b0dd8da7a5aa5a5c0b749fd8bc193ea/image-33.jpg)

- Slides: 42

Courtesy/Thanks to: Texas Instruments C 10. Set instructiuni TMS 320 C 54 X Obiective: • Prezentarea modurilor de adresare • Principalele moduri de adresare • Instructiuni si exemple pentru a folosi instr. • Exercitii • Referinte: www. TI. com ; spru 172 c. pdf 1

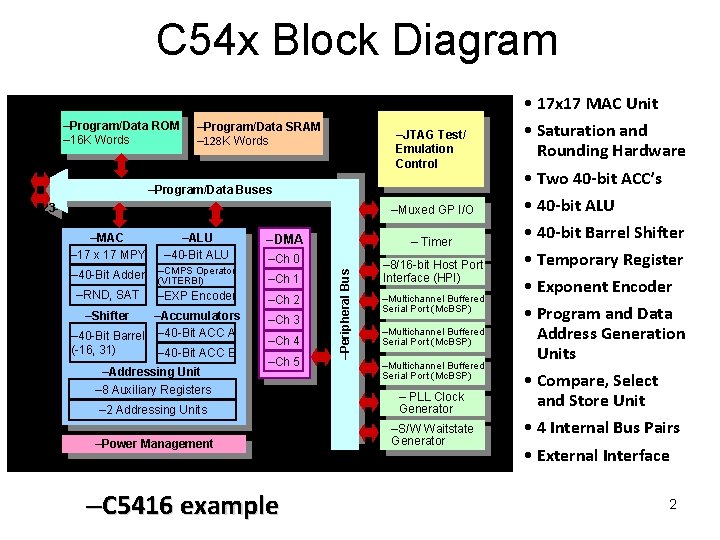

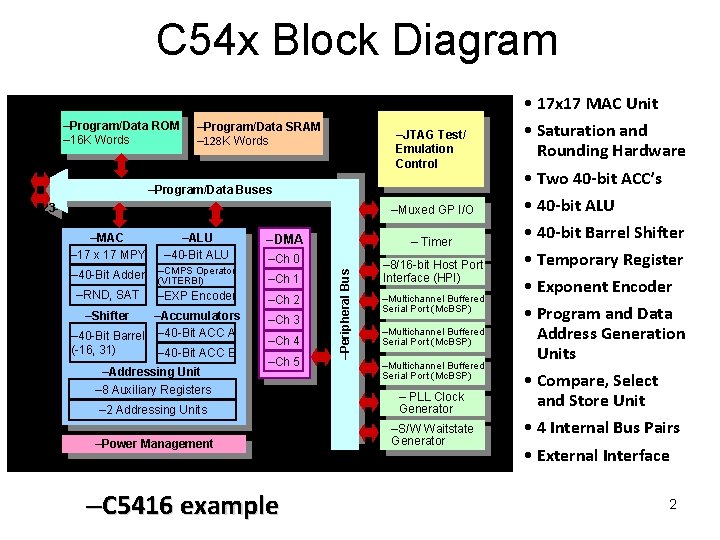

C 54 x Block Diagram –Program/Data ROM – 16 K Words –Program/Data SRAM – 128 K Words –JTAG Test/ Emulation Control –D(150) –Program/Data Buses –A(230) –Muxed GP I/O –ALU – 40 -Bit Adder –CMPS Operator (VITERBI) –RND, SAT –EXP Encoder –Shifter –Accumulators – 40 -Bit Barrel – 40 -Bit ACC A (-16, 31) – 40 -Bit ACC B –Addressing Unit – 8 Auxiliary Registers –DMA – Timer –Ch 0 –Ch 1 –Ch 2 –Ch 3 –Ch 4 –Ch 5 –Peripheral Bus –MAC – 17 x 17 MPY – 8/16 -bit Host Port Interface (HPI) –Multichannel Buffered Serial Port (Mc. BSP) – 2 Addressing Units – PLL Clock Generator –Power Management –S/W Waitstate Generator –C 5416 example • 17 x 17 MAC Unit • Saturation and Rounding Hardware • Two 40 -bit ACC’s • 40 -bit ALU • 40 -bit Barrel Shifter • Temporary Register • Exponent Encoder • Program and Data Address Generation Units • Compare, Select and Store Unit • 4 Internal Bus Pairs • External Interface 2

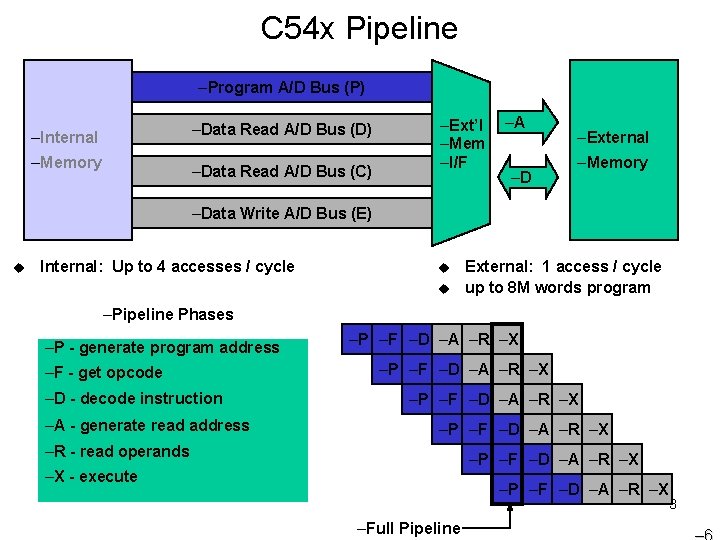

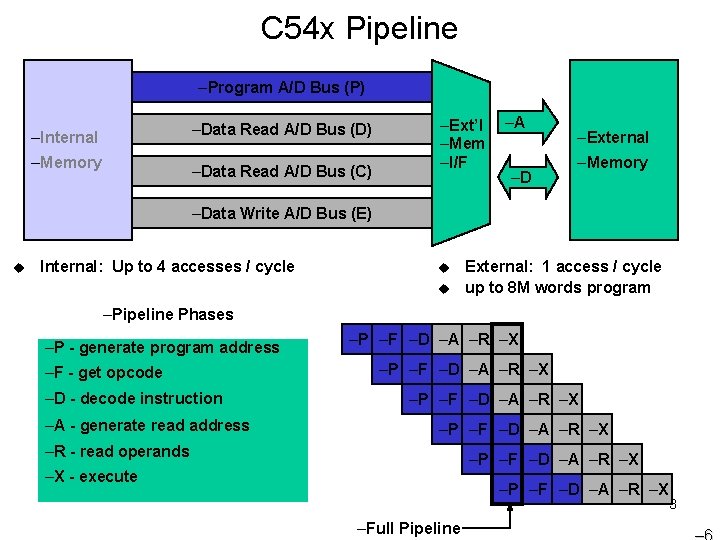

C 54 x Pipeline –Program A/D Bus (P) –Data Read A/D Bus (D) –Internal –Memory –Data Read A/D Bus (C) –Ext’l –Mem –I/F –A –D –External –Memory –Data Write A/D Bus (E) Internal: Up to 4 accesses / cycle External: 1 access / cycle up to 8 M words program –Pipeline Phases –P - generate program address –F - get opcode –D - decode instruction –A - generate read address –P –F –D –A –R –X –R - read operands –P –F –D –A –R –X –X - execute –P –F –D –A –R –X 3 –Full Pipeline

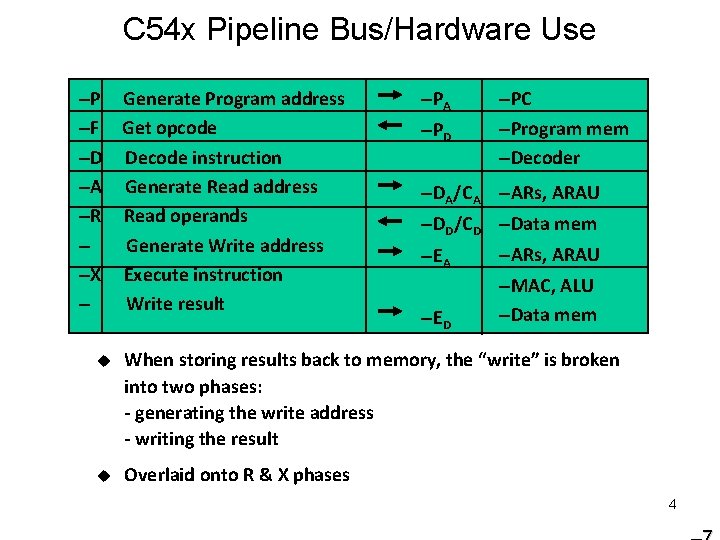

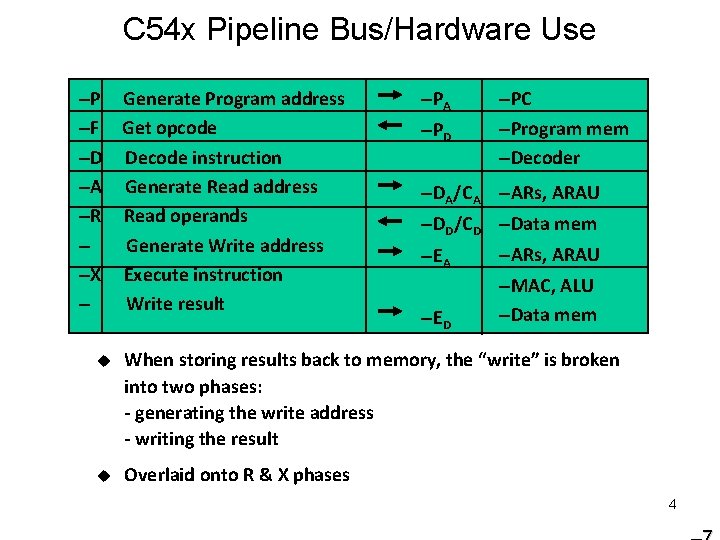

C 54 x Pipeline Bus/Hardware Use –P Generate Program address –F Get opcode –D Decode instruction –A Generate Read address –R Read operands – Generate Write address –X Execute instruction – Write result –P A –P D –PC –Program mem –Decoder –DA/CA –ARs, ARAU –DD/CD –Data mem –E A –ARs, ARAU –E D –MAC, ALU –Data mem When storing results back to memory, the “write” is broken into two phases: - generating the write address - writing the result Overlaid onto R & X phases 4

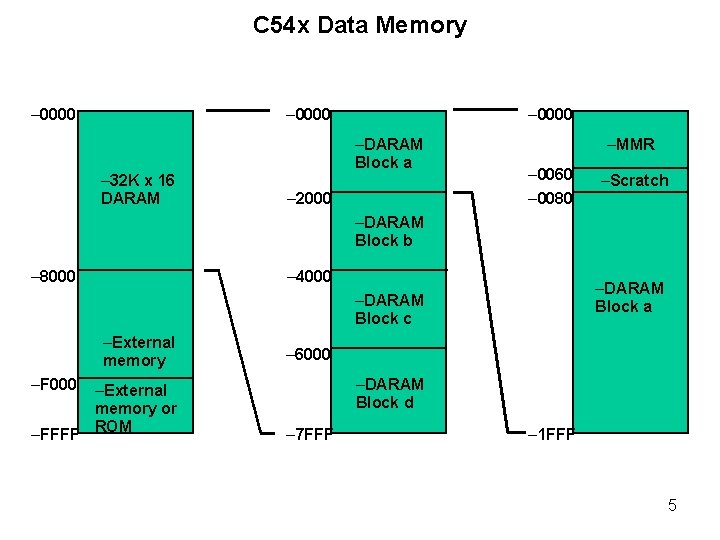

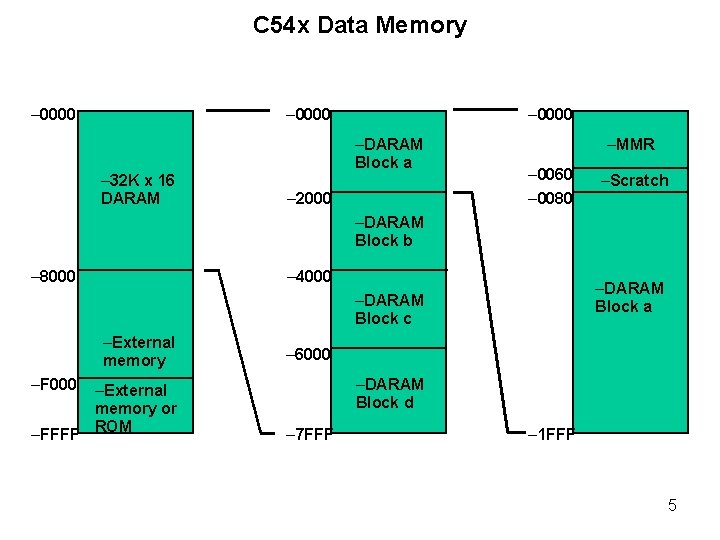

C 54 x Data Memory – 0000 –DARAM Block a – 32 K x 16 DARAM – 2000 –MMR – 0060 – 0080 –Scratch –DARAM Block b – 8000 – 4000 –DARAM Block a –DARAM Block c –External memory –F 000 –FFFF –External memory or ROM – 6000 –DARAM Block d – 7 FFF – 1 FFF 5

Registrii MMR Name Addr. (Hex) Description IMR 0000 Interrupt Mask Register AR 0 0010 Address Register 0 IFR 0001 Interrupt Flag Register AR 1 0011 Address Register 1 ----- 2 -5 Reserved AR 2 0012 Address Register 2 ST 0 0006 Status 0 Register AR 3 0013 Address Register 3 ST 1 0007 Status 1 Register AR 4 0014 Address Register 4 AL 0008 A accumulator low (A[15: 00]) AR 5 0015 Address Register 5 AH 0009 A accumulator high (A[31: 16]) AR 6 0016 Address Register 6 AG 000 A A accumulator guard (A[39: 32]) AR 7 0017 Address Register 7 BL 000 B B accumulator low (B[15: 00]) SP 0018 Stack Pointer Register BH 000 C B accumulator high (B[31: 16]) BK 0019 Circular Size Register BG 000 D B accumulator guard (B[39: 32]) BRC 001 A Block Repeat Counter T 000 E Temporary Register RSA 001 B Block Repeat Start Address TRN 000 F Transition Register REA 001 C Block Repeat End Address PMST 001 D PMST Register ------- 01 E-01 F Reserved 6

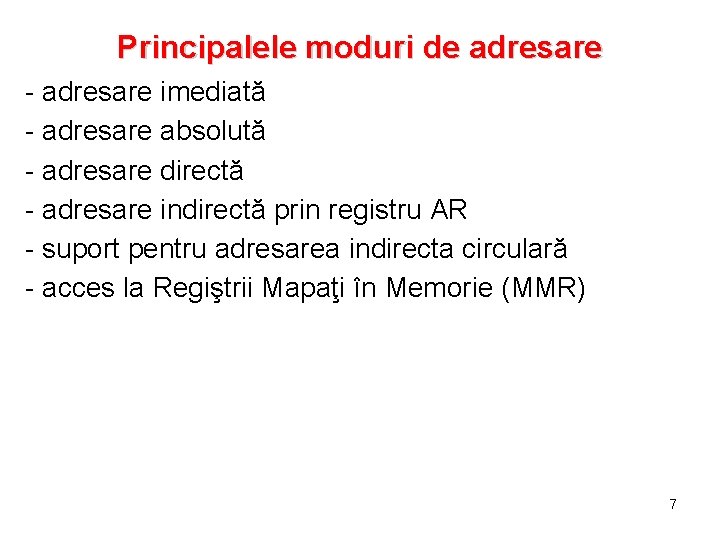

Principalele moduri de adresare - adresare imediată - adresare absolută - adresare directă - adresare indirectă prin registru AR - suport pentru adresarea indirecta circulară - acces la Regiştrii Mapaţi în Memorie (MMR) 7

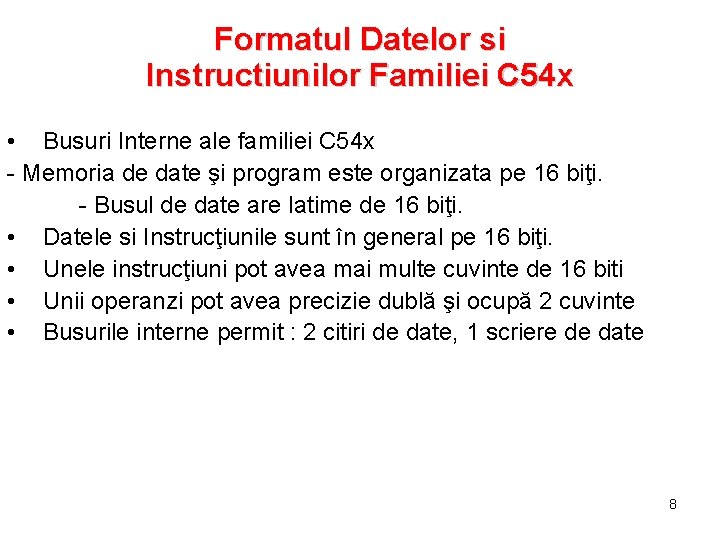

Formatul Datelor si Instructiunilor Familiei C 54 x • Busuri Interne ale familiei C 54 x - Memoria de date şi program este organizata pe 16 biţi. - Busul de date are latime de 16 biţi. • Datele si Instrucţiunile sunt în general pe 16 biţi. • Unele instrucţiuni pot avea mai multe cuvinte de 16 biti • Unii operanzi pot avea precizie dublă şi ocupă 2 cuvinte • Busurile interne permit : 2 citiri de date, 1 scriere de date 8

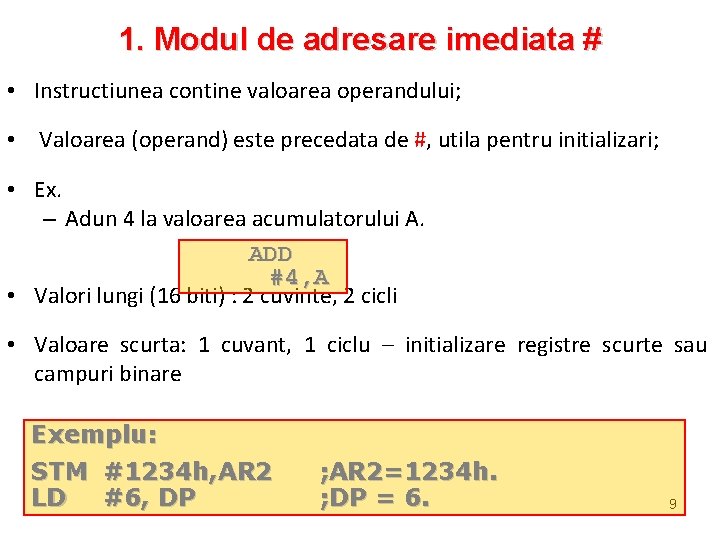

1. Modul de adresare imediata # • Instructiunea contine valoarea operandului; • Valoarea (operand) este precedata de #, utila pentru initializari; • Ex. – Adun 4 la valoarea acumulatorului A. ADD #4, A • Valori lungi (16 biti) : 2 cuvinte, 2 cicli • Valoare scurta: 1 cuvant, 1 ciclu – initializare registre scurte sau campuri binare Exemplu: STM #1234 h, AR 2 LD #6, DP ; AR 2=1234 h. ; DP = 6. 9

2. Modul de adresare direct @ • Adresare directa = acces aleator la o adresa, fata de o baza specificata • Instrucţiunea conţine un offset relativ la adresa de bază. • Adresa de bază poate fi începutul paginii memoriei de date sau pointerul stivei. • Memoria de date este divizata virtual în 512 pag. de 128 cuvinte (512 x 128=216) 10

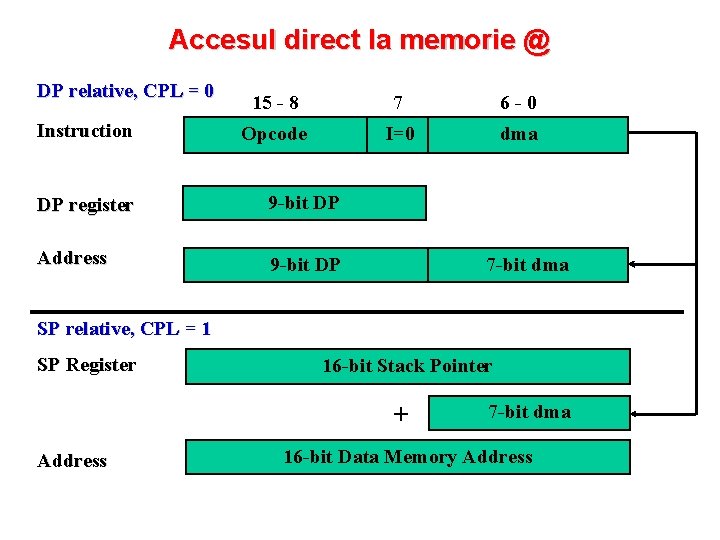

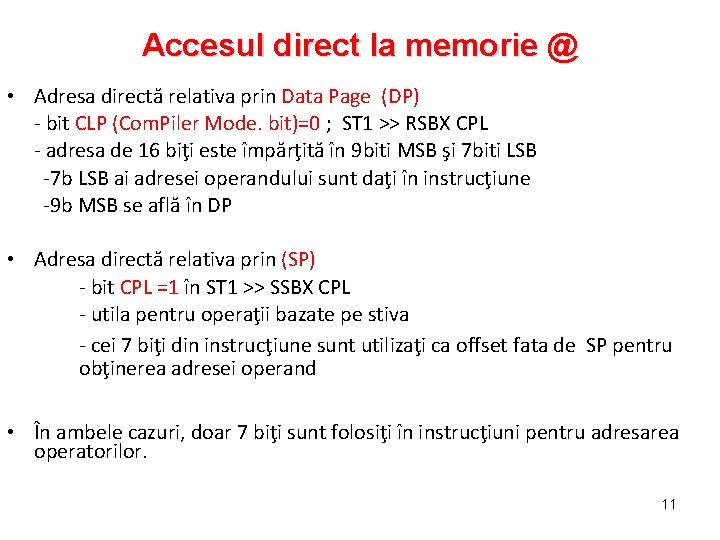

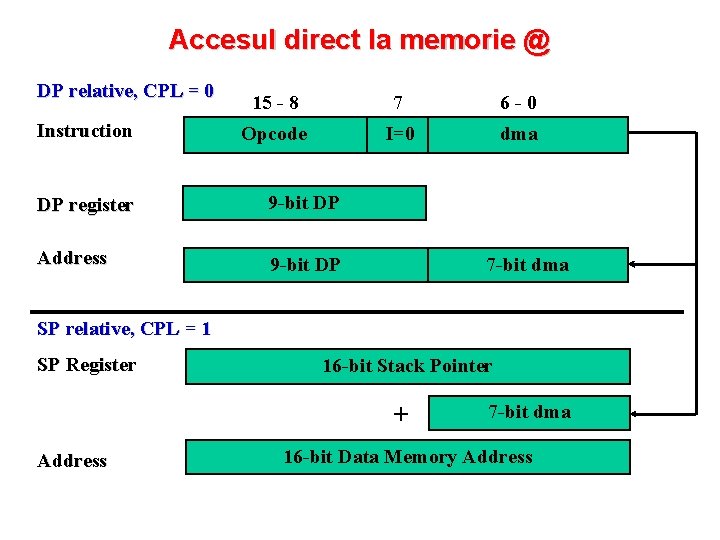

Accesul direct la memorie @ • Adresa directă relativa prin Data Page (DP) - bit CLP (Com. Piler Mode. bit)=0 ; ST 1 >> RSBX CPL - adresa de 16 biţi este împărţită în 9 biti MSB şi 7 biti LSB -7 b LSB ai adresei operandului sunt daţi în instrucţiune -9 b MSB se află în DP • Adresa directă relativa prin (SP) - bit CPL =1 în ST 1 >> SSBX CPL - utila pentru operaţii bazate pe stiva - cei 7 biţi din instrucţiune sunt utilizaţi ca offset fata de SP pentru obţinerea adresei operand • În ambele cazuri, doar 7 biţi sunt folosiţi în instrucţiuni pentru adresarea operatorilor. 11

Accesul direct la memorie @ DP relative, CPL = 0 Instruction 15 - 8 7 6 -0 Opcode I=0 dma DP register 9 -bit DP Address 9 -bit DP 7 -bit dma SP relative, CPL = 1 SP Register 16 -bit Stack Pointer + Address 7 -bit dma 16 -bit Data Memory Address

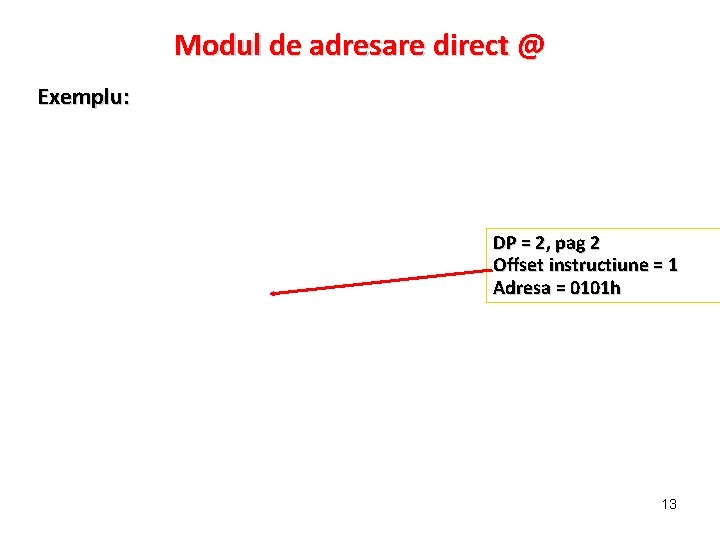

Modul de adresare direct @ Exemplu: DP = 2, pag 2 Offset instructiune = 1 Adresa = 0101 h 13

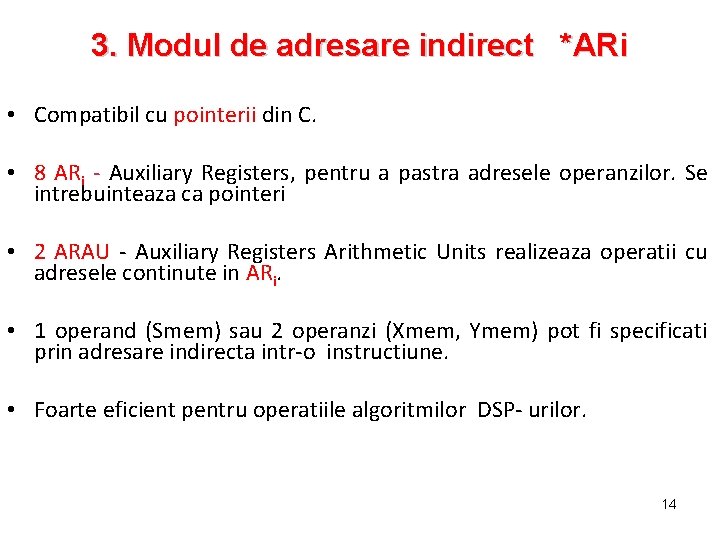

3. Modul de adresare indirect *ARi • Compatibil cu pointerii din C. • 8 ARi - Auxiliary Registers, pentru a pastra adresele operanzilor. Se intrebuinteaza ca pointeri • 2 ARAU - Auxiliary Registers Arithmetic Units realizeaza operatii cu adresele continute in ARi. • 1 operand (Smem) sau 2 operanzi (Xmem, Ymem) pot fi specificati prin adresare indirecta intr-o instructiune. • Foarte eficient pentru operatiile algoritmilor DSP- urilor. 14

Modul de adresare indirect *ARi • AR 0 poate fi intrebuintat ca index. • Suport pentru adresare circulara • Adresare bit reversed (BR) pentru FFT • ARi poate fi modificat in decursul instructiunii – Modificarile posibile sau operatiile ARi depind de numarul de operanzi specificati cu adresare indirecta in instructiune. • Pointerii (ARi) trebuie initializati inaintea utilizarii. 15

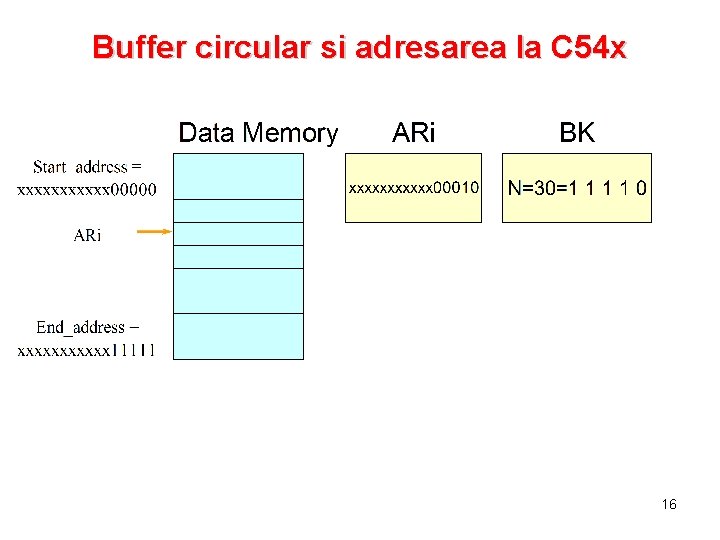

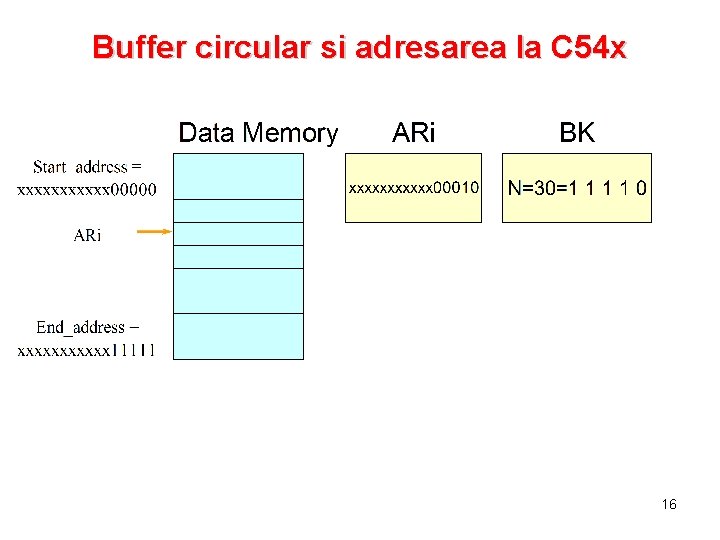

Buffer circular si adresarea la C 54 x 16

Adresare circulara % la C 54 x • Mod de adresare indirecta circulara : - %, *ARi-%, *ARi+%, *ARi-0%, *ARi+0%, *ARi(lk)% • In modul cu operand dublu Xmem, Ymem: - *ARi+0% mod valabil; valabil pentru decrementare, se stocheaza o valoare negativa in AR 0. • registrul BK : – Contine dimensiunea N a bufferului circular. – Trebuie initializat inaintea folosirii. – Pot fi mai multe buffere circulare simultan la adrese diferite cu aceeasi lungime 17

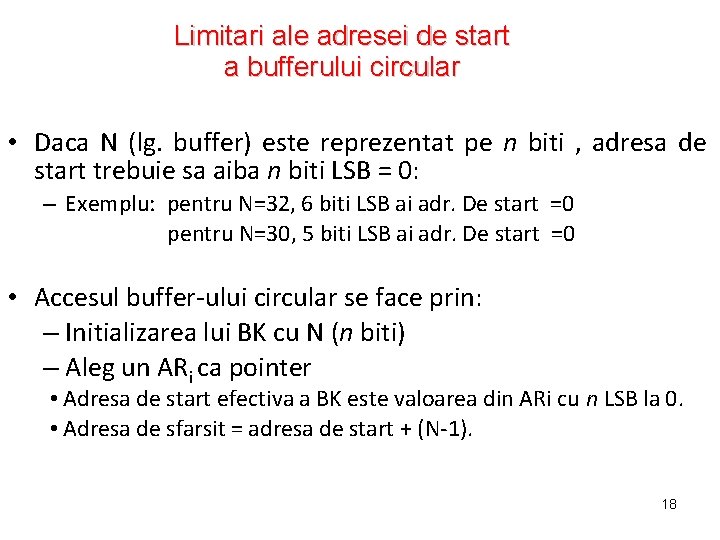

Limitari ale adresei de start a bufferului circular • Daca N (lg. buffer) este reprezentat pe n biti , adresa de start trebuie sa aiba n biti LSB = 0: – Exemplu: pentru N=32, 6 biti LSB ai adr. De start =0 pentru N=30, 5 biti LSB ai adr. De start =0 • Accesul buffer-ului circular se face prin: – Initializarea lui BK cu N (n biti) – Aleg un ARi ca pointer • Adresa de start efectiva a BK este valoarea din ARi cu n LSB la 0. • Adresa de sfarsit = adresa de start + (N-1). 18

Optiunile pentru modificarea ARi Instructiuni cu un singur operand - Smem 19

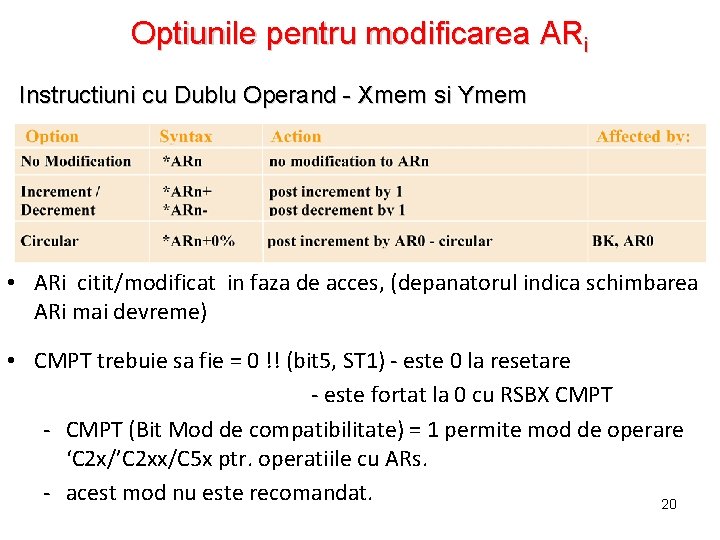

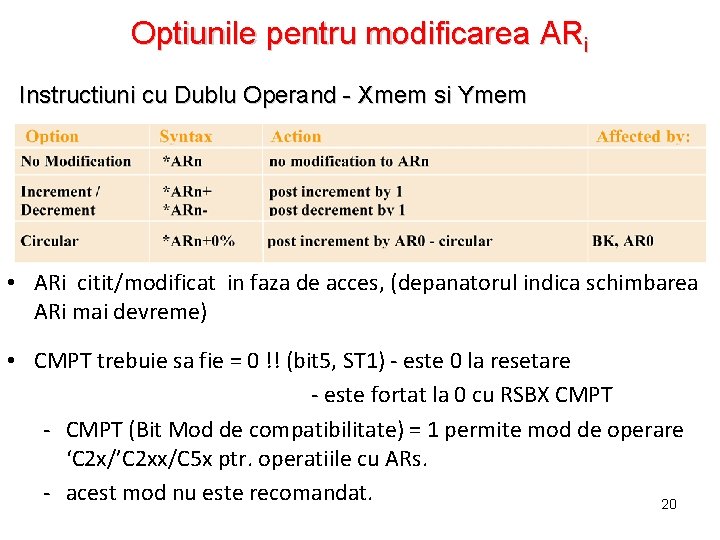

Optiunile pentru modificarea ARi Instructiuni cu Dublu Operand - Xmem si Ymem • ARi citit/modificat in faza de acces, (depanatorul indica schimbarea ARi mai devreme) • CMPT trebuie sa fie = 0 !! (bit 5, ST 1) - este 0 la resetare - este fortat la 0 cu RSBX CMPT - CMPT (Bit Mod de compatibilitate) = 1 permite mod de operare ‘C 2 x/’C 2 xx/C 5 x ptr. operatiile cu ARs. - acest mod nu este recomandat. 20

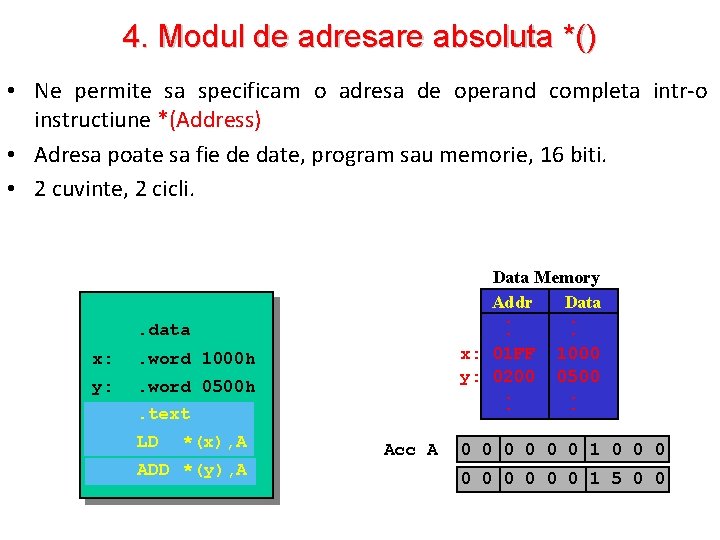

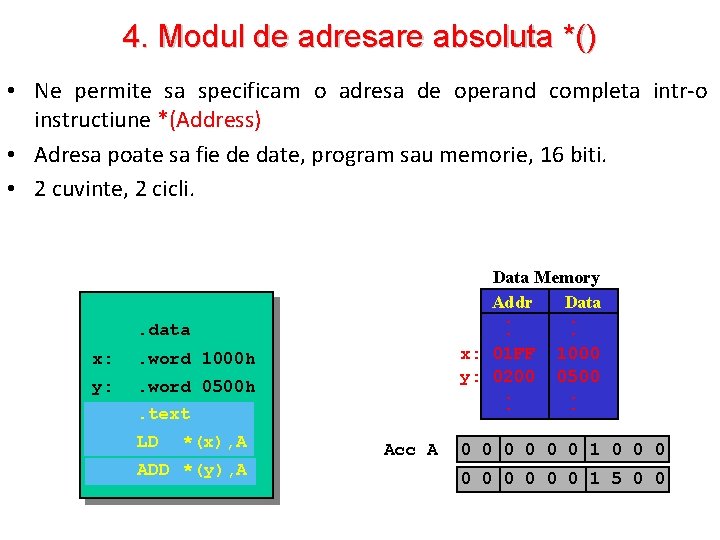

4. Modul de adresare absoluta *() • Ne permite sa specificam o adresa de operand completa intr-o instructiune *(Address) • Adresa poate sa fie de date, program sau memorie, 16 biti. • 2 cuvinte, 2 cicli. Data Memory Addr Data. . x: 01 FF 1000 y: 0200 0500. . . data x: . word 1000 h y: . word 0500 h. text LD *(x), A ADD *(y), A Acc A 0 0 0 1 0 0 0 0 0 1 5 0 0

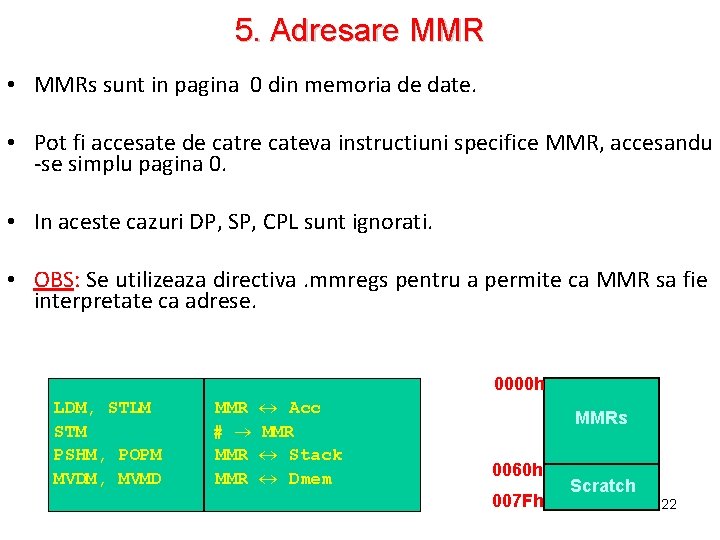

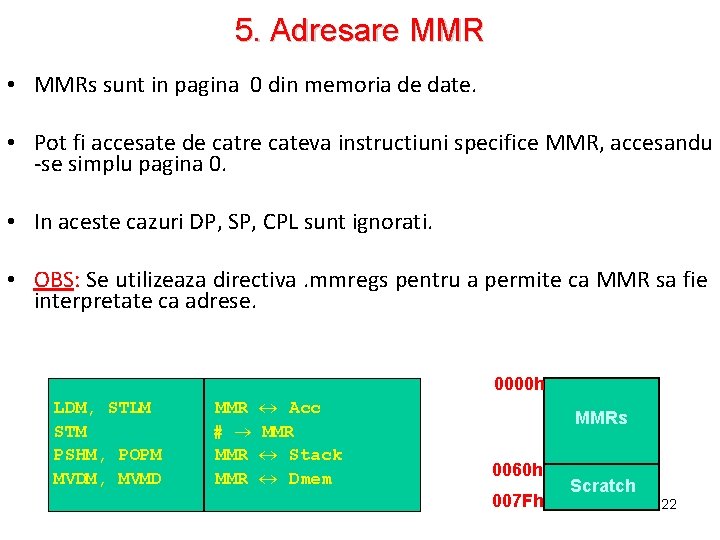

5. Adresare MMR • MMRs sunt in pagina 0 din memoria de date. • Pot fi accesate de catre cateva instructiuni specifice MMR, accesandu -se simplu pagina 0. • In aceste cazuri DP, SP, CPL sunt ignorati. • OBS: Se utilizeaza directiva. mmregs pentru a permite ca MMR sa fie interpretate ca adrese. 0000 h LDM, STLM STM PSHM, POPM MVDM, MVMD MMR # ® MMR « Acc MMR « Stack « Dmem MMRs 0060 h 007 Fh Scratch 22

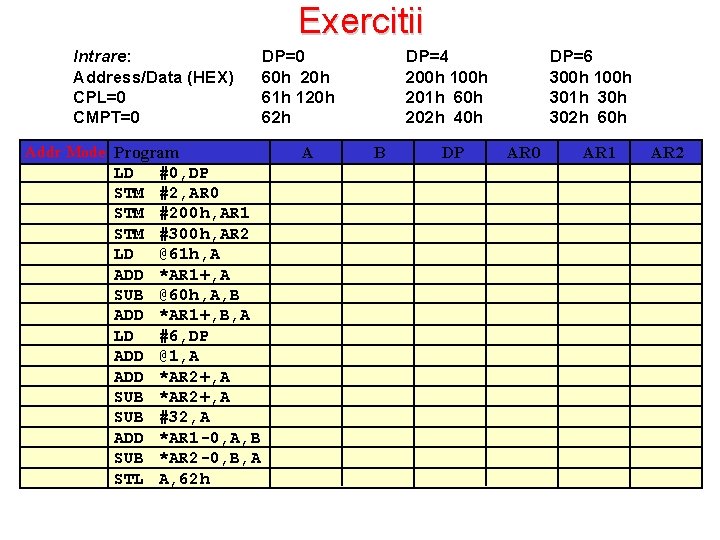

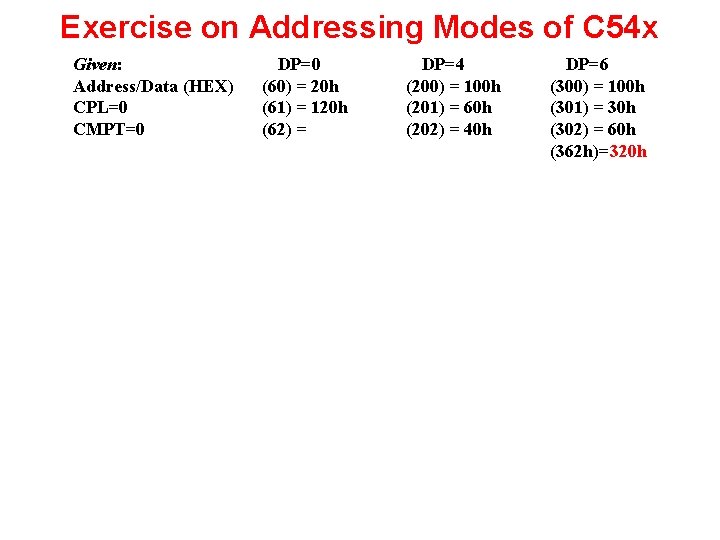

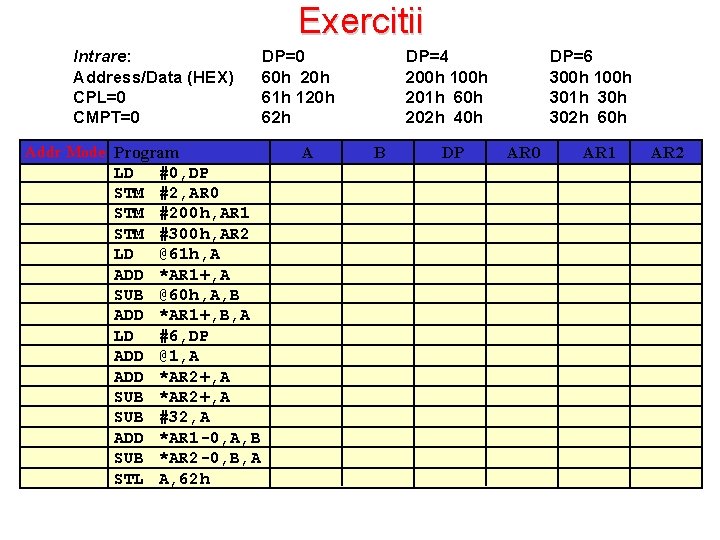

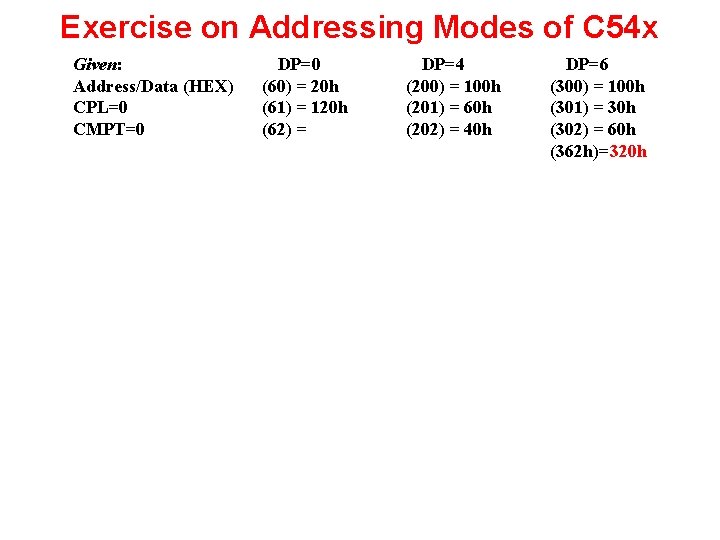

Exercitii Intrare: Address/Data (HEX) CPL=0 CMPT=0 Addr Mode Program LD STM STM LD ADD SUB ADD SUB STL #0, DP #2, AR 0 #200 h, AR 1 #300 h, AR 2 @61 h, A *AR 1+, A @60 h, A, B *AR 1+, B, A #6, DP @1, A *AR 2+, A #32, A *AR 1 -0, A, B *AR 2 -0, B, A A, 62 h DP=0 60 h 20 h 61 h 120 h 62 h A DP=4 200 h 100 h 201 h 60 h 202 h 40 h B DP DP=6 300 h 100 h 301 h 302 h 60 h AR 0 AR 1 AR 2

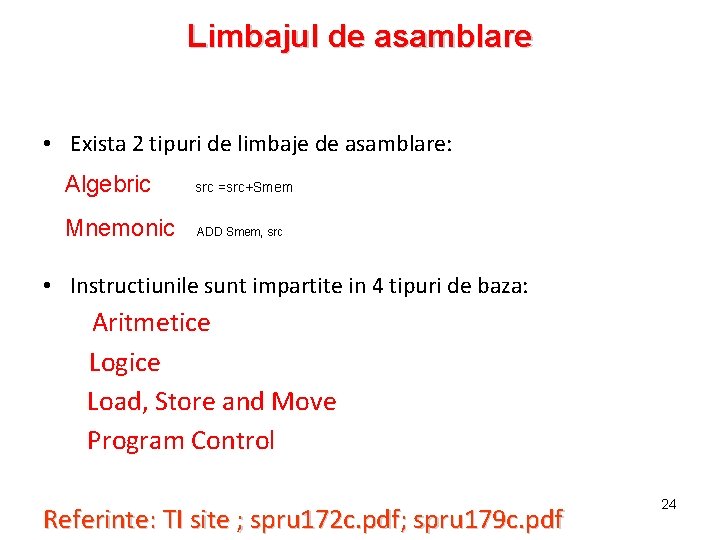

Limbajul de asamblare • Exista 2 tipuri de limbaje de asamblare: Algebric src =src+Smem Mnemonic ADD Smem, src • Instructiunile sunt impartite in 4 tipuri de baza: Aritmetice Logice Load, Store and Move Program Control Referinte: TI site ; spru 172 c. pdf; spru 179 c. pdf 24

Instructiuni si Operanzi • Sintaxa generala a instructiunilor: – Instr Op 1, [Op 2, [Op 3, […]]] • Sinataxa operanzilor: 25

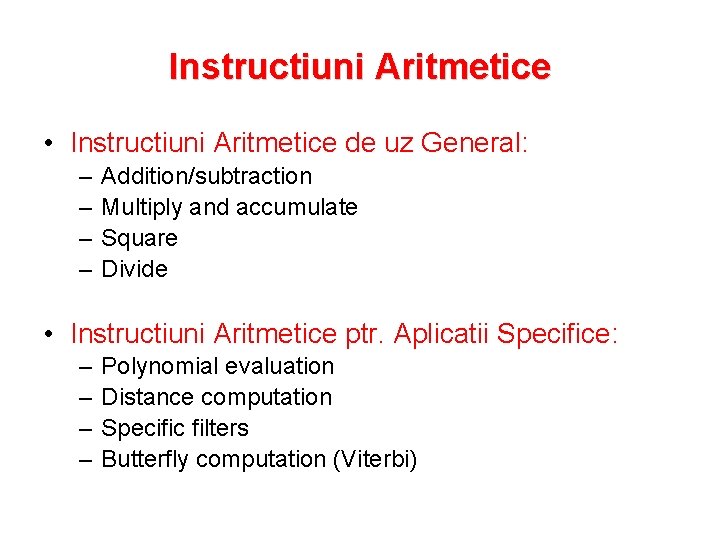

Instructiuni Aritmetice • Instructiuni Aritmetice de uz General: – – Addition/subtraction Multiply and accumulate Square Divide • Instructiuni Aritmetice ptr. Aplicatii Specifice: – – Polynomial evaluation Distance computation Specific filters Butterfly computation (Viterbi)

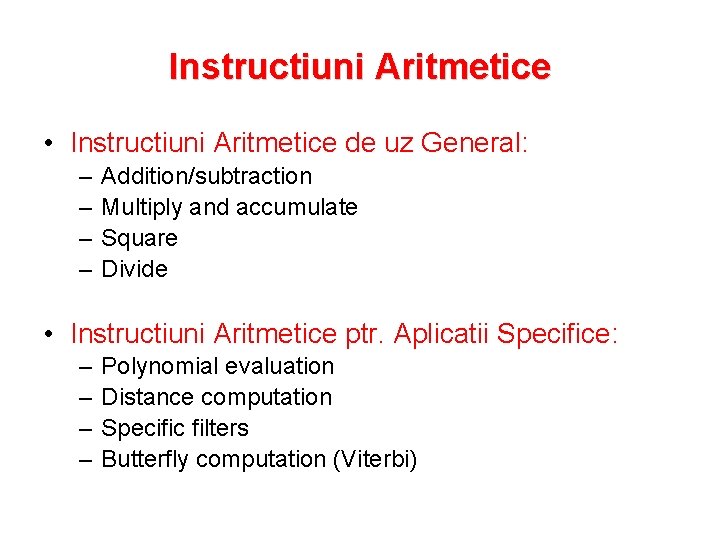

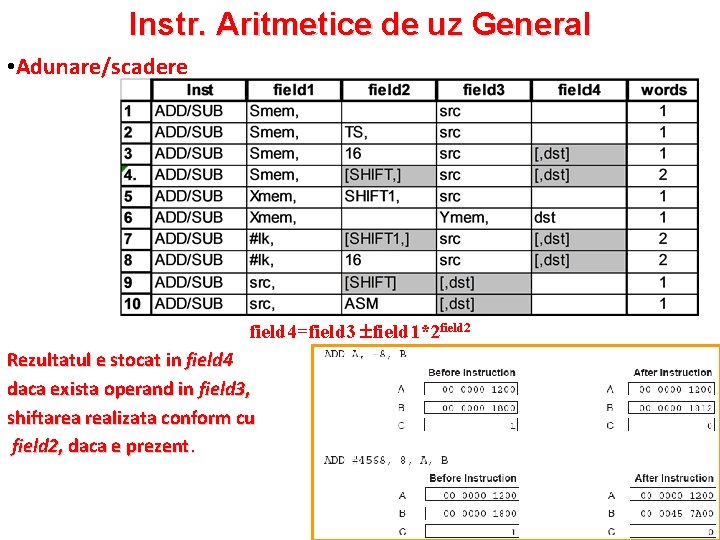

Instr. Aritmetice de uz General • Adunare/scadere field 4=field 3 field 1*2 field 2 Rezultatul e stocat in field 4 daca exista operand in field 3, shiftarea realizata conform cu field 2, daca e prezent. 27

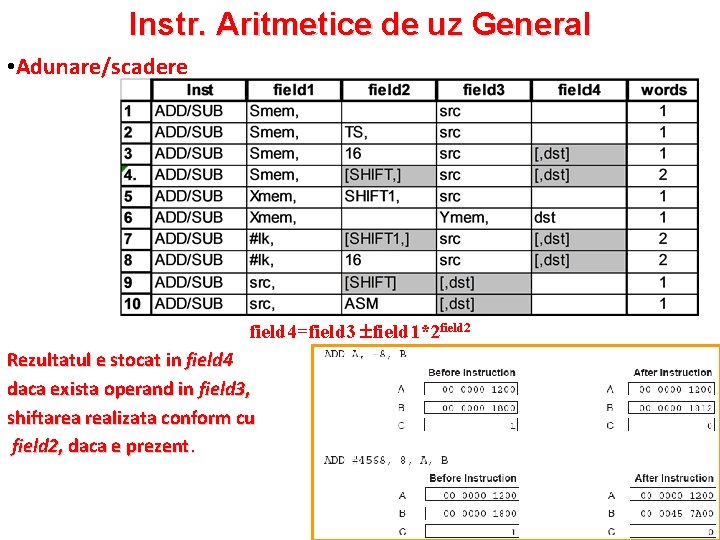

Campul de deplasare • Multe instructiuni folosesc deplasari ptr. un operand. • Acesta este specificat in campul operand si poate fi : – Imediat daca e specificat de cuvintele cheie: -16 SHIFT 15 0 SHIFT 1 15 – Registru indirect: -16 ASM 15 (Accumulator Shift Mode field of ST 1) -16 TS 31 (TS are the 6 LSBs of T register) 28

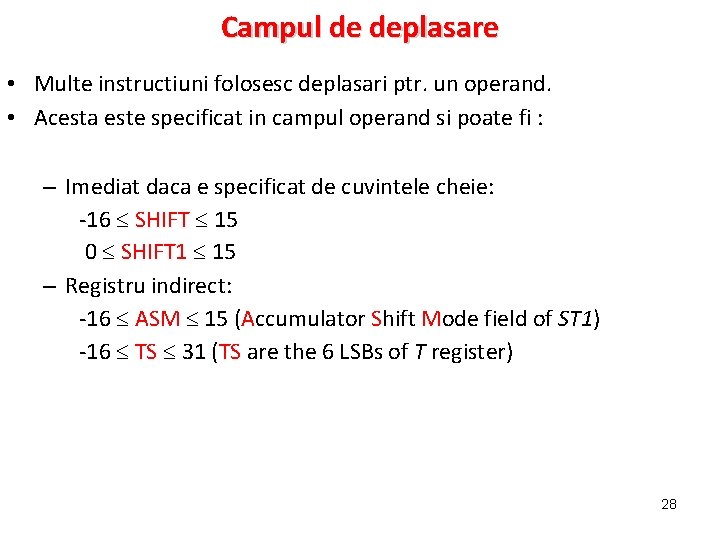

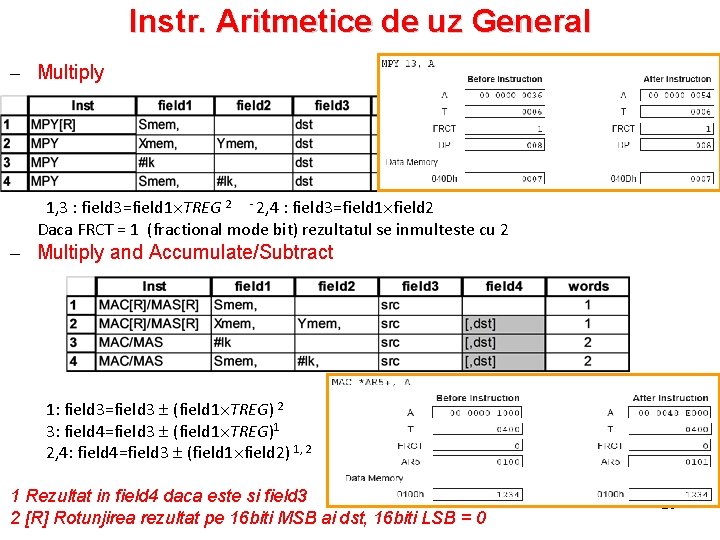

Instr. Aritmetice de uz General – Multiply 1, 3 : field 3=field 1 TREG 2 - 2, 4 : field 3=field 1 field 2 Daca FRCT = 1 (fractional mode bit) rezultatul se inmulteste cu 2 – Multiply and Accumulate/Subtract 1: field 3=field 3 (field 1 TREG) 2 3: field 4=field 3 (field 1 TREG)1 2, 4: field 4=field 3 (field 1 field 2) 1, 2 1 Rezultat in field 4 daca este si field 3 2 [R] Rotunjirea rezultat pe 16 biti MSB ai dst, 16 biti LSB = 0 29

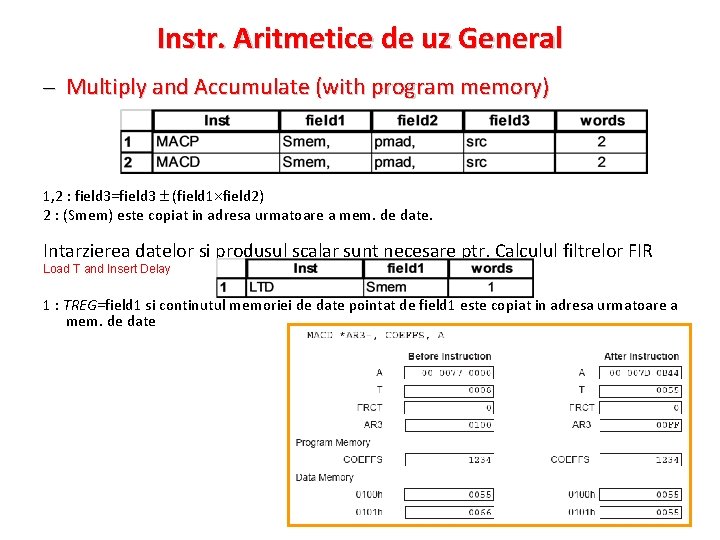

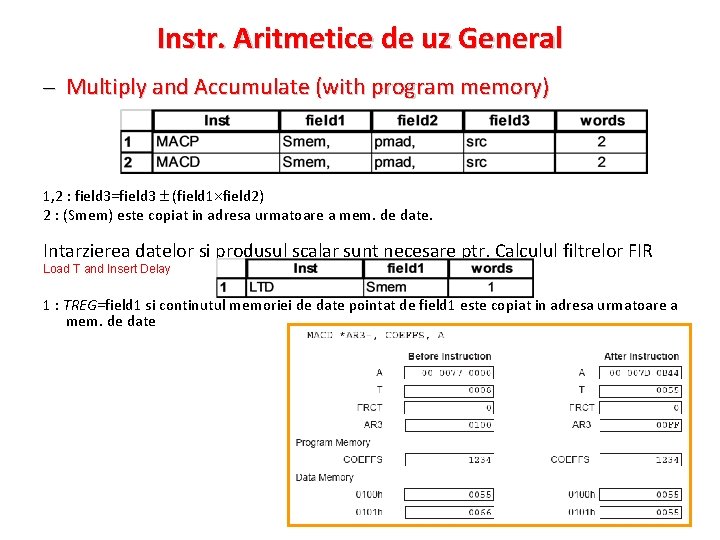

Instr. Aritmetice de uz General – Multiply and Accumulate (with program memory) 1, 2 : field 3=field 3 (field 1 field 2) 2 : (Smem) este copiat in adresa urmatoare a mem. de date. Intarzierea datelor si produsul scalar sunt necesare ptr. Calculul filtrelor FIR Load T and Insert Delay 1 : TREG=field 1 si continutul memoriei de date pointat de field 1 este copiat in adresa urmatoare a mem. de date 30

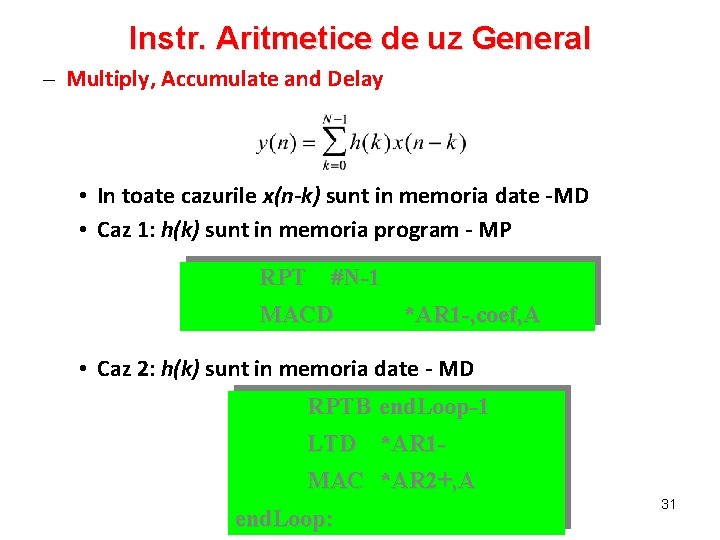

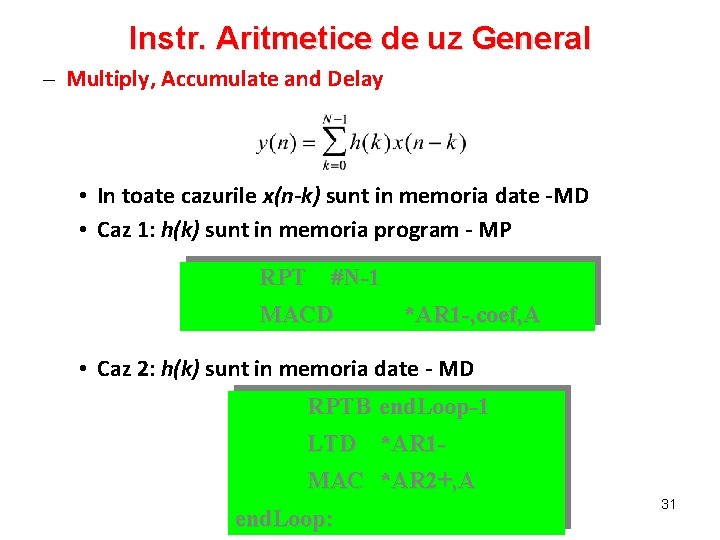

Instr. Aritmetice de uz General – Multiply, Accumulate and Delay • In toate cazurile x(n-k) sunt in memoria date -MD • Caz 1: h(k) sunt in memoria program - MP RPT #N-1 MACD *AR 1 -, coef, A • Caz 2: h(k) sunt in memoria date - MD RPTB end. Loop-1 LTD *AR 1 MAC *AR 2+, A end. Loop: 31

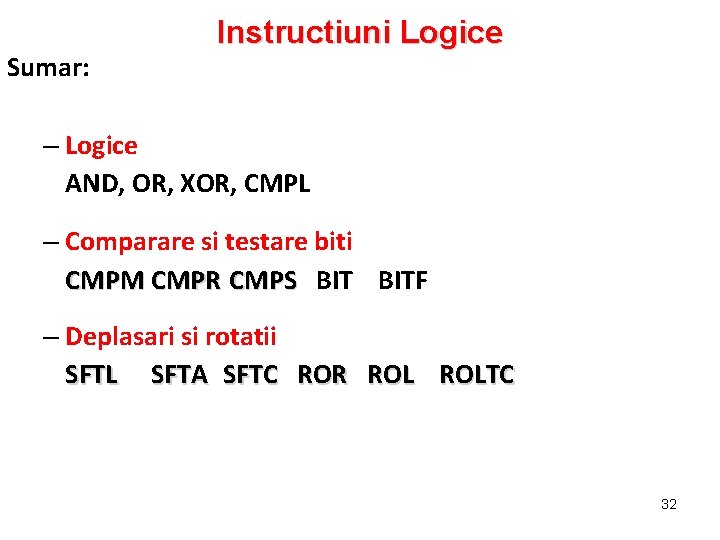

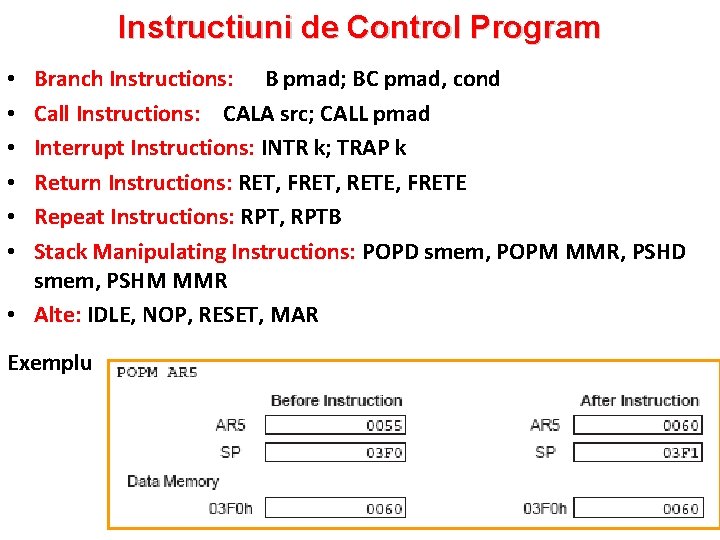

Sumar: Instructiuni Logice – Logice AND, OR, XOR, CMPL – Comparare si testare biti CMPM CMPR CMPS BITF – Deplasari si rotatii SFTL SFTA SFTC ROR ROLTC 32

![Instructiuni Logice Operatii Logice cu acumulatorul field 4field 3 field Instructiuni Logice • Operatii Logice cu acumulatorul field 4=field 3 [ + ] field](https://slidetodoc.com/presentation_image_h2/8b0dd8da7a5aa5a5c0b749fd8bc193ea/image-33.jpg)

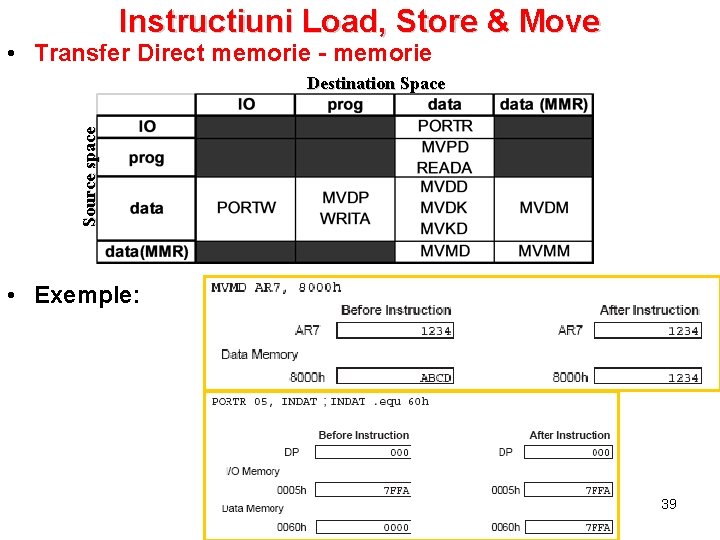

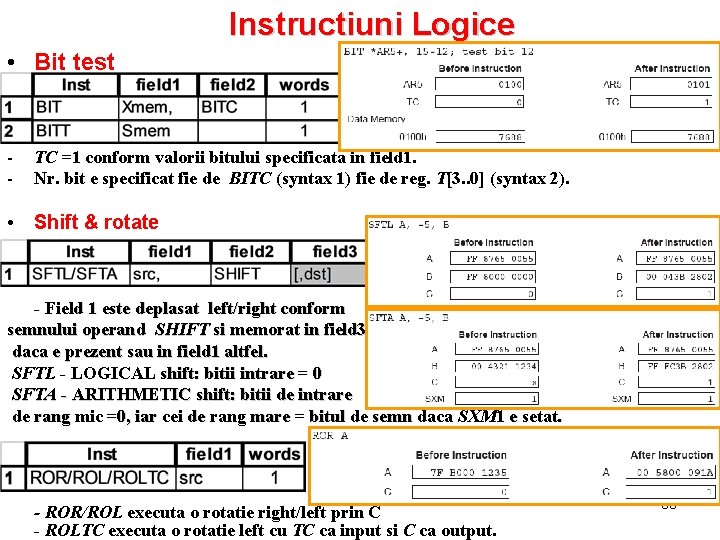

Instructiuni Logice • Operatii Logice cu acumulatorul field 4=field 3 [ + ] field 1*2 field 2, Rezultat stocat in field 4 daca este si field 3 bit complement • Operatii Logice cu memoria field 2=field 1 [ + ] field 2 CMPL A, B 33

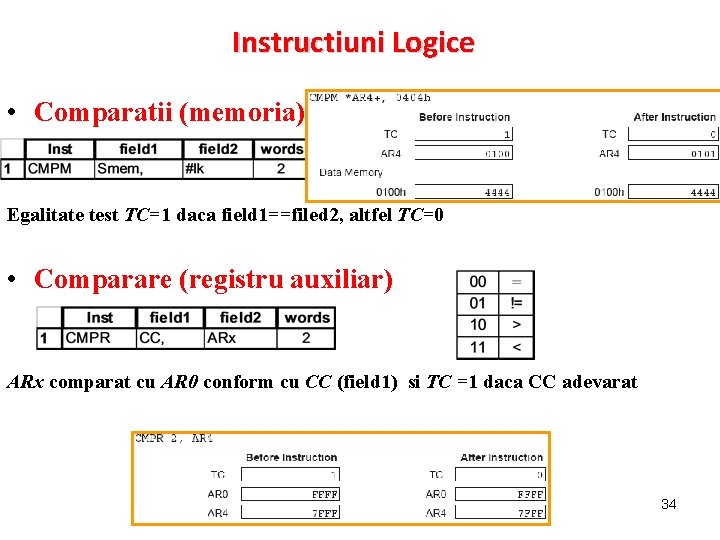

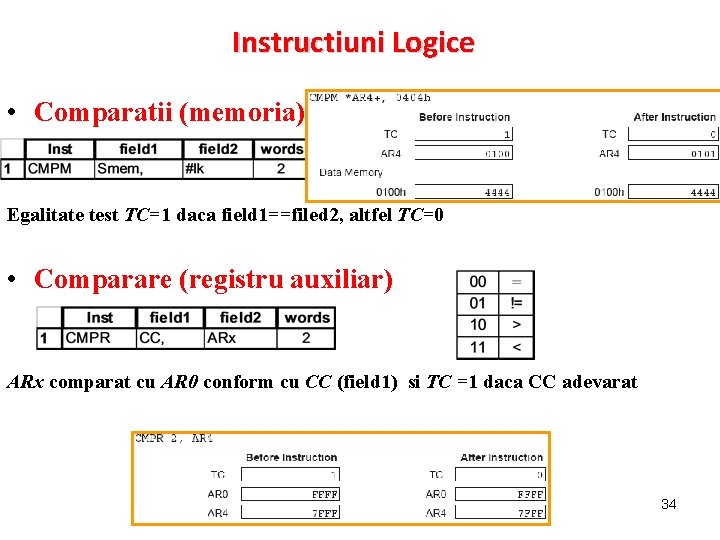

Instructiuni Logice • Comparatii (memoria) Egalitate test TC=1 daca field 1==filed 2, altfel TC=0 • Comparare (registru auxiliar) ARx comparat cu AR 0 conform cu CC (field 1) si TC =1 daca CC adevarat 34

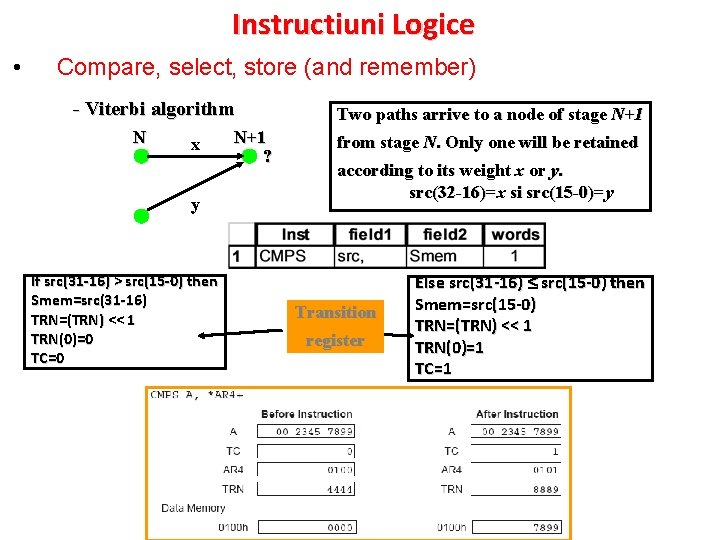

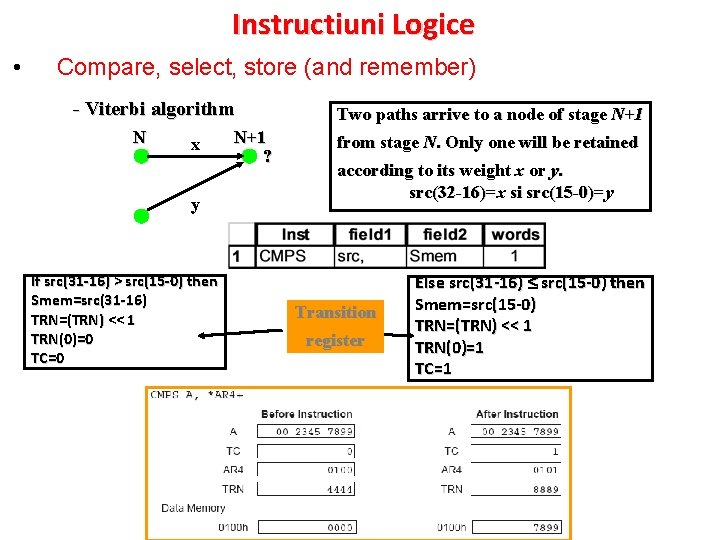

Instructiuni Logice • Compare, select, store (and remember) - Viterbi algorithm N x y If src(31 -16) > src(15 -0) then Smem=src(31 -16) TRN=(TRN) << 1 TRN(0)=0 TC=0 N+1 ? Two paths arrive to a node of stage N+1 from stage N. Only one will be retained according to its weight x or y. src(32 -16)=x si src(15 -0)=y Transition register Else src(31 -16) src(15 -0) then Smem=src(15 -0) TRN=(TRN) << 1 TRN(0)=1 TC=1

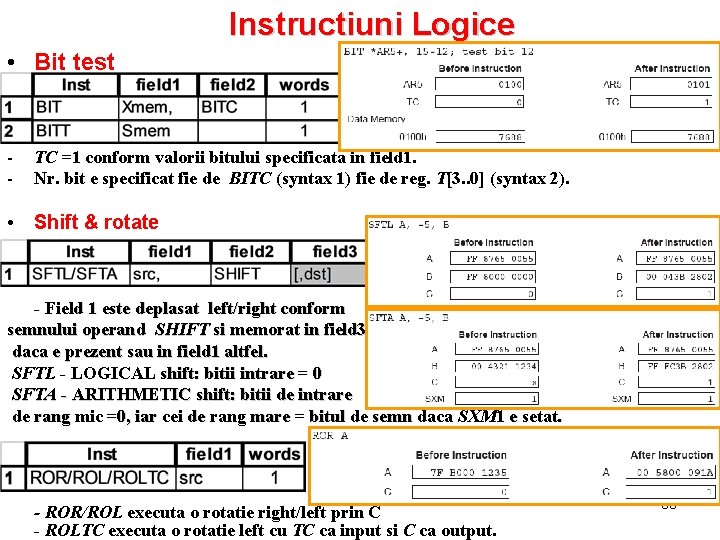

Instructiuni Logice • Bit test - TC =1 conform valorii bitului specificata in field 1. Nr. bit e specificat fie de BITC (syntax 1) fie de reg. T[3. . 0] (syntax 2). • Shift & rotate - Field 1 este deplasat left/right conform semnului operand SHIFT si memorat in field 3 daca e prezent sau in field 1 altfel. SFTL - LOGICAL shift: bitii intrare = 0 SFTA - ARITHMETIC shift: bitii de intrare de rang mic =0, iar cei de rang mare = bitul de semn daca SXM 1 e setat. - ROR/ROL executa o rotatie right/left prin C - ROLTC executa o rotatie left cu TC ca input si C ca output. 36

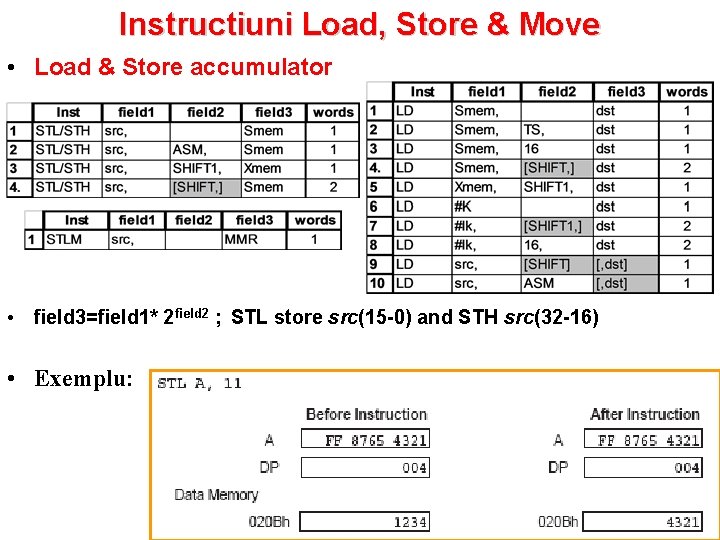

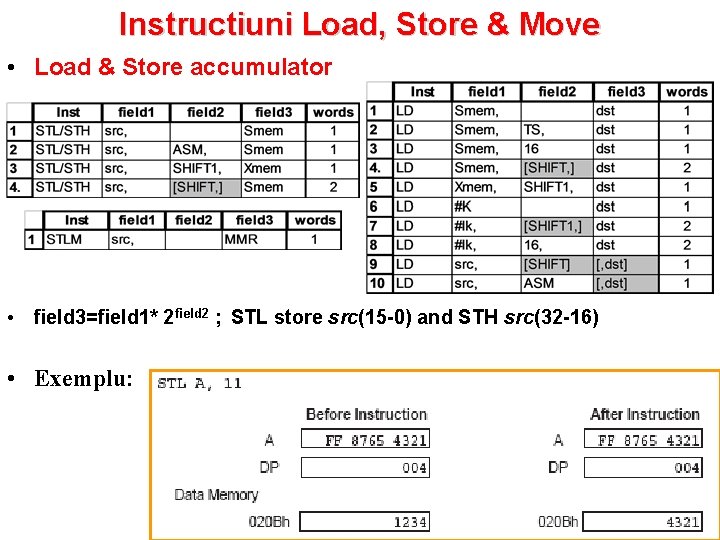

Instructiuni Load, Store & Move • Load & Store accumulator • field 3=field 1* 2 field 2 ; STL store src(15 -0) and STH src(32 -16) • Exemplu: 37

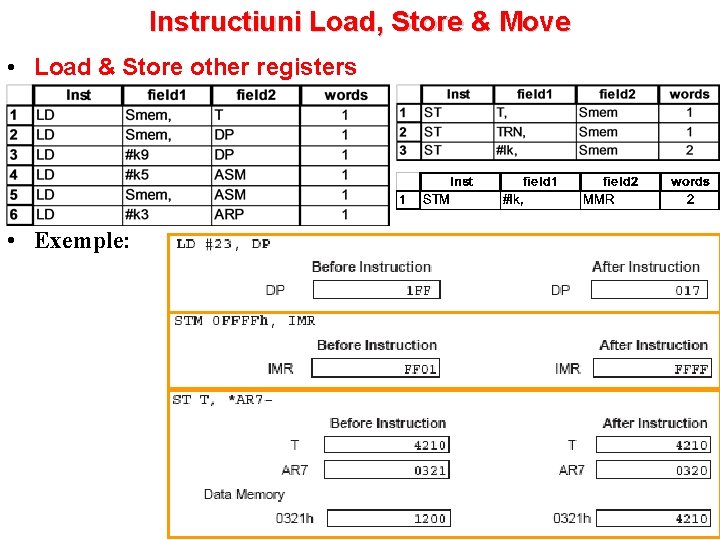

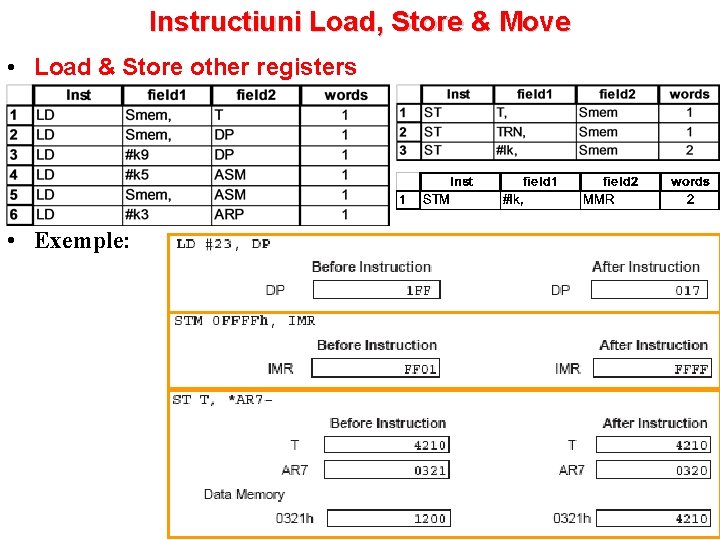

Instructiuni Load, Store & Move • Load & Store other registers • Exemple: 38

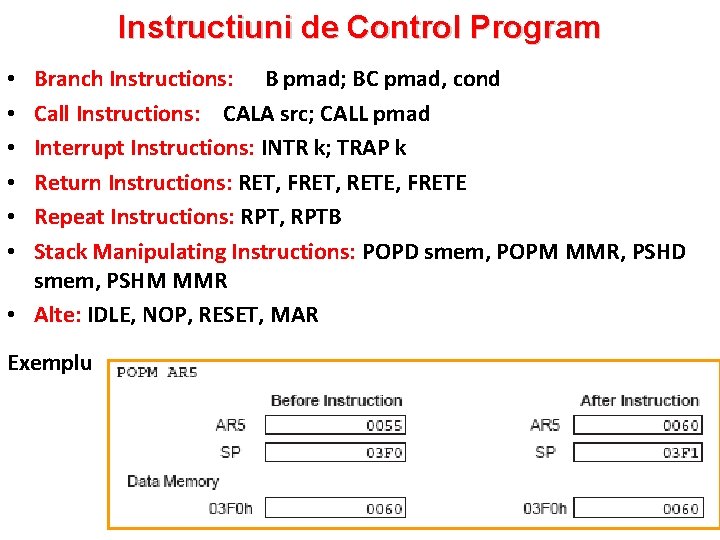

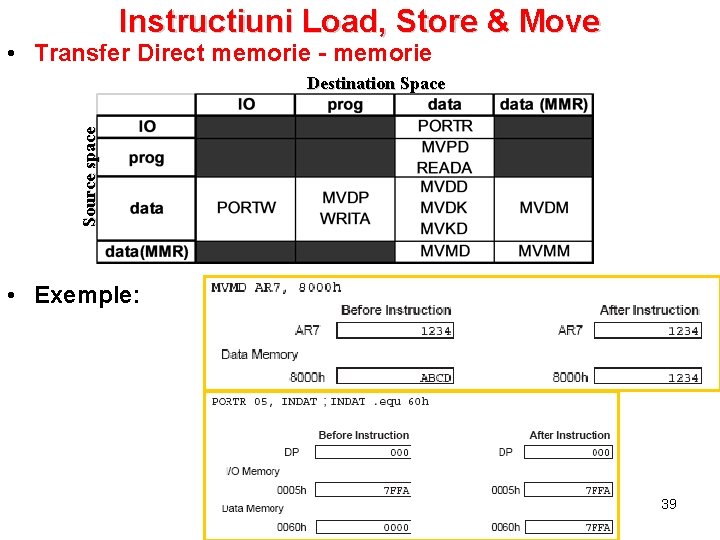

Instructiuni Load, Store & Move • Transfer Direct memorie - memorie Source space Destination Space • Exemple: 39

Instructiuni de Control Program Branch Instructions: B pmad; BC pmad, cond Call Instructions: CALA src; CALL pmad Interrupt Instructions: INTR k; TRAP k Return Instructions: RET, FRET, RETE, FRETE Repeat Instructions: RPT, RPTB Stack Manipulating Instructions: POPD smem, POPM MMR, PSHD smem, PSHM MMR • Alte: IDLE, NOP, RESET, MAR • • • Exemplu 40

Courtesy/Thanks to: Texas Instruments 41

Exercise on Addressing Modes of C 54 x Given: Address/Data (HEX) CPL=0 CMPT=0 DP=0 (60) = 20 h (61) = 120 h (62) = DP=4 (200) = 100 h (201) = 60 h (202) = 40 h DP=6 (300) = 100 h (301) = 30 h (302) = 60 h (362 h)=320 h