Coupling Aware Routing Ryan Kastner Elaheh Bozorgzadeh and

Coupling Aware Routing Ryan Kastner, Elaheh Bozorgzadeh and Majid Sarrafzadeh Department of Electrical and Computer Engineering Northwestern University ASIC/SOC, September 2000 1 Ryan Kastner

Outline l Coupling l l l Coupling-Free Routing l l l Definition Uses Algorithms for Coupling-Free Routing l l Definition Effects Greedy Forcing Results Conclusion ASIC/SOC, September 2000 2 Ryan Kastner

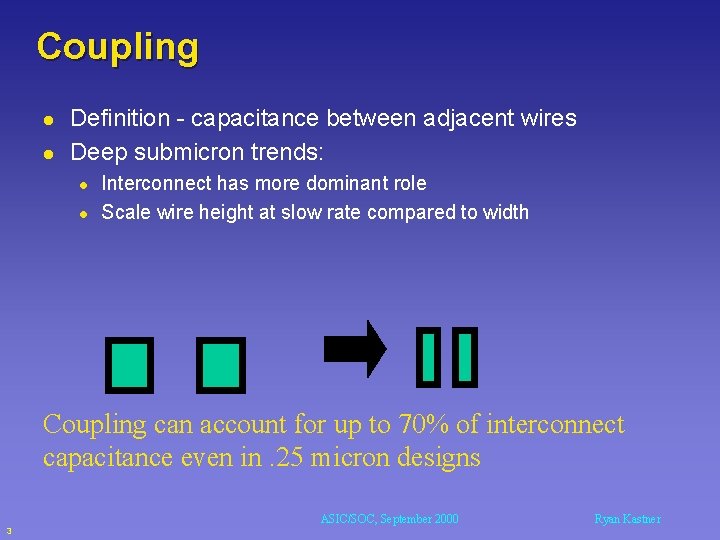

Coupling l l Definition - capacitance between adjacent wires Deep submicron trends: l l Interconnect has more dominant role Scale wire height at slow rate compared to width Coupling can account for up to 70% of interconnect capacitance even in. 25 micron designs ASIC/SOC, September 2000 3 Ryan Kastner

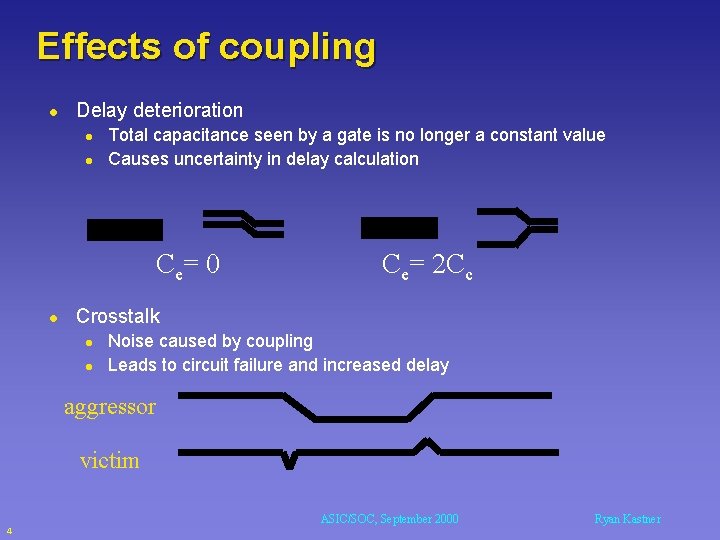

Effects of coupling l Delay deterioration l l Total capacitance seen by a gate is no longer a constant value Causes uncertainty in delay calculation C e= 0 l Ce= 2 Cc Crosstalk l l Noise caused by coupling Leads to circuit failure and increased delay aggressor victim ASIC/SOC, September 2000 4 Ryan Kastner

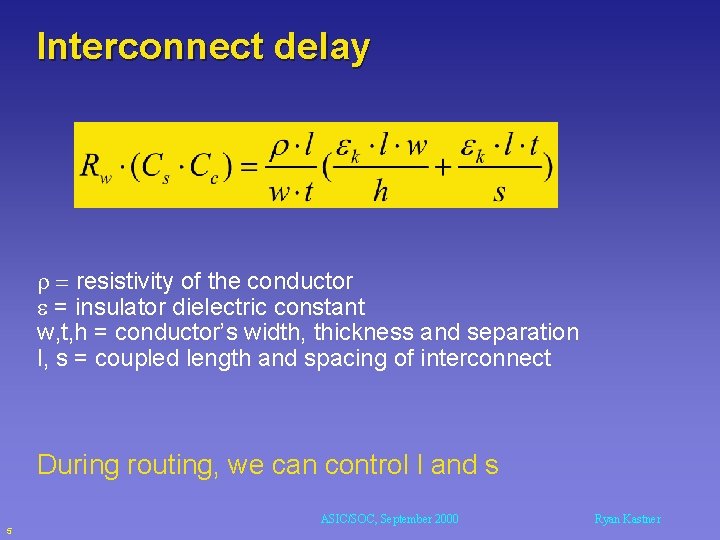

Interconnect delay r = resistivity of the conductor e = insulator dielectric constant w, t, h = conductor’s width, thickness and separation l, s = coupled length and spacing of interconnect During routing, we can control l and s ASIC/SOC, September 2000 5 Ryan Kastner

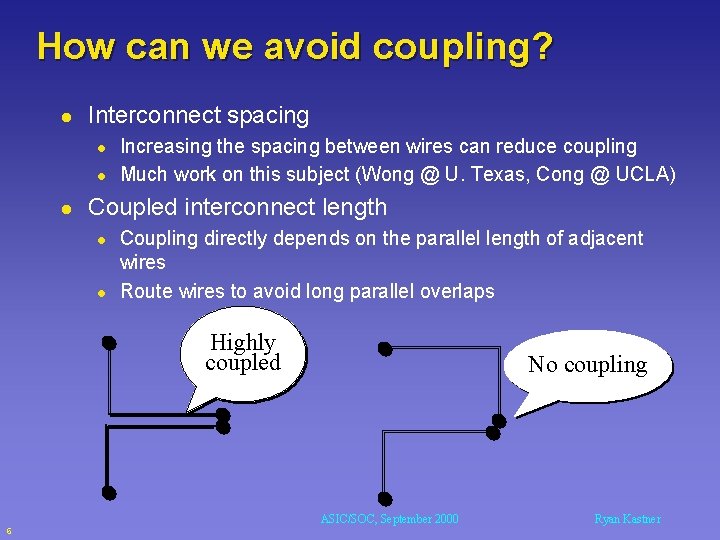

How can we avoid coupling? l Interconnect spacing l l l Increasing the spacing between wires can reduce coupling Much work on this subject (Wong @ U. Texas, Cong @ UCLA) Coupled interconnect length l l Coupling directly depends on the parallel length of adjacent wires Route wires to avoid long parallel overlaps Highly coupled No coupling ASIC/SOC, September 2000 6 Ryan Kastner

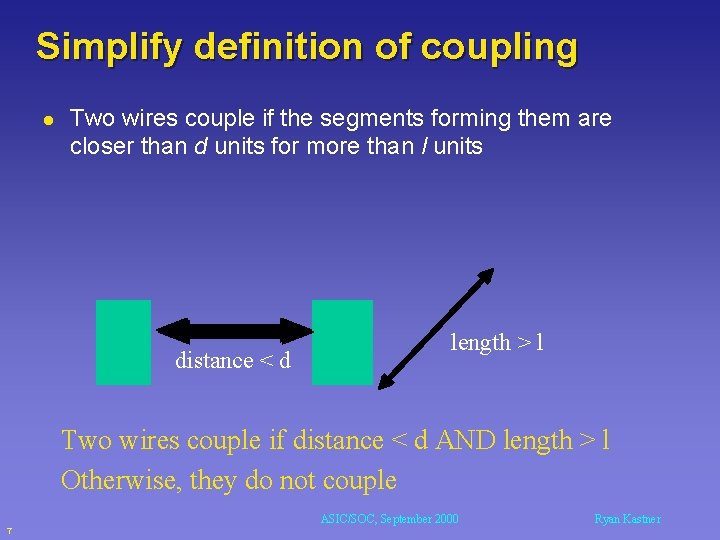

Simplify definition of coupling l Two wires couple if the segments forming them are closer than d units for more than l units distance < d length > l Two wires couple if distance < d AND length > l Otherwise, they do not couple ASIC/SOC, September 2000 7 Ryan Kastner

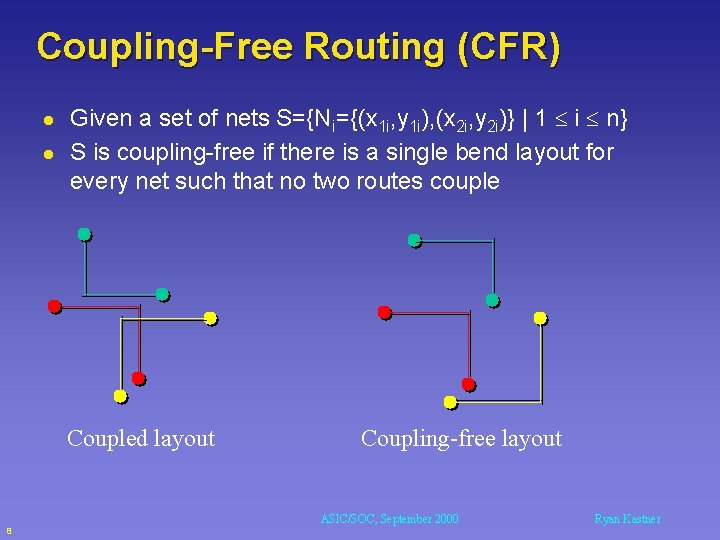

Coupling-Free Routing (CFR) l l Given a set of nets S={Ni={(x 1 i, y 1 i), (x 2 i, y 2 i)} | 1 i n} S is coupling-free if there is a single bend layout for every net such that no two routes couple Coupled layout Coupling-free layout ASIC/SOC, September 2000 8 Ryan Kastner

Usefulness of CFR l Minimum interconnect delay l l Increases predictability of routes l l l Single bend routing insures minimum wirelength Introduces only one via Coupling between nets is minimized Allows accurate prediction of wirelength, congestion, etc Predictable Routing, ICCAD 2000 Speeds up single net routing process ASIC/SOC, September 2000 9 Ryan Kastner

Usefulness of CFR-Detailed Routing l l As fabrication technology progresses, routing layers become more plentiful Reserving layers for critical nets is common l l Power, ground and clock are already routed on preferred layers Use preferred layers for critical nets l l l Layer can be used for timing critical nets Critical nets have little “slack” - need minimum delay CFR insures that nets have minimum delay l l l minimum wirelength minimum number of vias minimum coupling ASIC/SOC, September 2000 10 Ryan Kastner

Usefulness of CFR-Single Layer l Single layer routing is a important problem for routing l l l Area routers often use single layer routing for each layer Printed Circuit Board (PCB) use single layer algorithms Best known academic single layer router (developed by Lin and Ro) uses two step process l l Find a maximum planar set of one-bend nets Use rubberband equivalent to route remaining nets CFR can be easily be incorporated into in first step to produce a planar set of nets with minimum coupling ASIC/SOC, September 2000 11 Ryan Kastner

Usefulness of CFR-Global routing l Coupling at global routing is hard to determine l l l Routes are not exact, makes it difficult to know adjacency relations of nets Detailed router will often make local changes Global routing allows global changes, it is next to impossible to make global changes at the detailed stage A coupling-free global layout will produce a coupling-free detailed layout ASIC/SOC, September 2000 12 Ryan Kastner

MAX-CFL Definition l l Given a set of two-terminal nets S and a positive integer K |S|. Is there a single bend routing for at least K nets such that no two routings couple? Additional routing constraints can easily be added l l Routed nets must be planar Routed nets must be routed on two layers MAX-CFL for planar layouts is NP-Complete General MAX-CFL NP-Complete? ASIC/SOC, September 2000 13 Ryan Kastner

Algorithms l We developed two algorithms l l l Greedy Forcing Algorithms try to maximize number of nets routed and/or criticality of routed nets ASIC/SOC, September 2000 14 Ryan Kastner

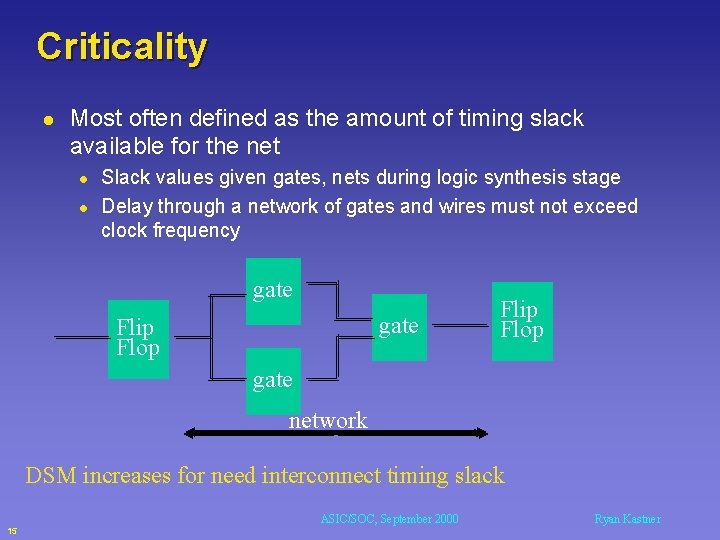

Criticality l Most often defined as the amount of timing slack available for the net l l Slack values given gates, nets during logic synthesis stage Delay through a network of gates and wires must not exceed clock frequency gate Flip Flop gate network DSM increases for need interconnect timing slack ASIC/SOC, September 2000 15 Ryan Kastner

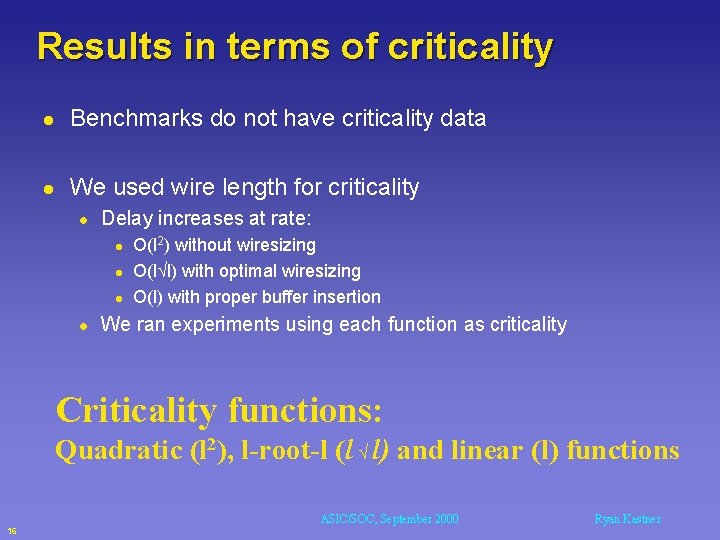

Results in terms of criticality l Benchmarks do not have criticality data l We used wire length for criticality l Delay increases at rate: l l O(l 2) without wiresizing O(l l) with optimal wiresizing O(l) with proper buffer insertion We ran experiments using each function as criticality Criticality functions: Quadratic (l 2), l-root-l (l l) and linear (l) functions ASIC/SOC, September 2000 16 Ryan Kastner

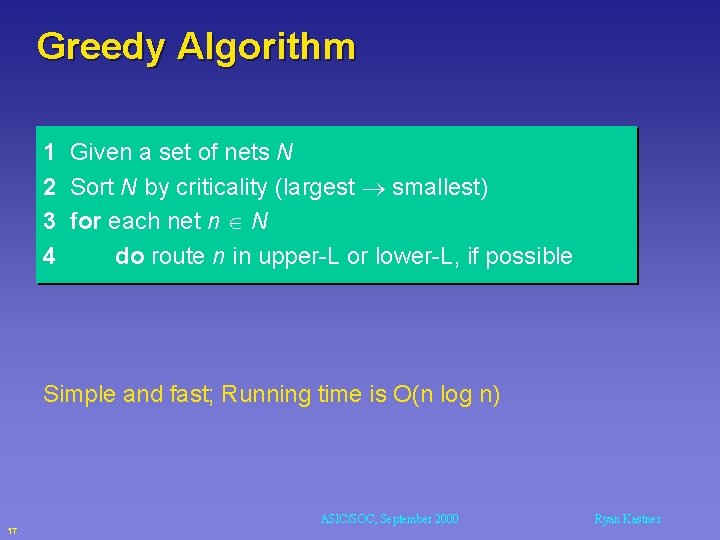

Greedy Algorithm 1 Given a set of nets N 2 Sort N by criticality (largest smallest) 3 for each net n N 4 do route n in upper-L or lower-L, if possible Simple and fast; Running time is O(n log n) ASIC/SOC, September 2000 17 Ryan Kastner

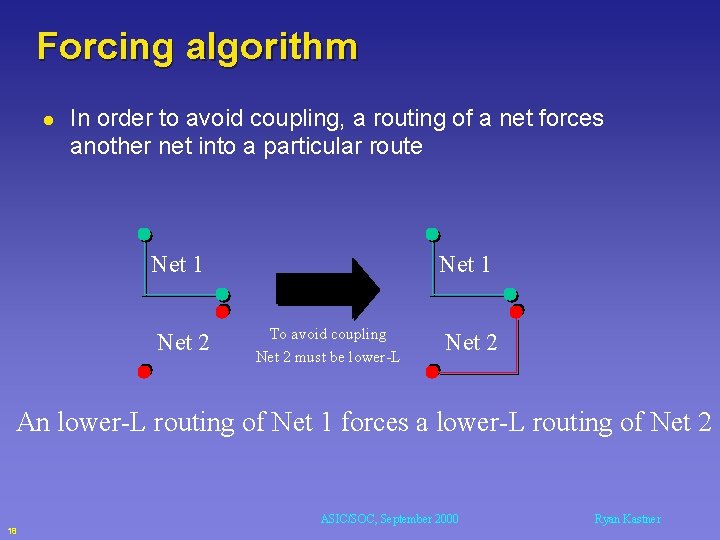

Forcing algorithm l In order to avoid coupling, a routing of a net forces another net into a particular route Net 1 Net 2 Net 1 To avoid coupling Net 2 must be lower-L Net 2 An lower-L routing of Net 1 forces a lower-L routing of Net 2 ASIC/SOC, September 2000 18 Ryan Kastner

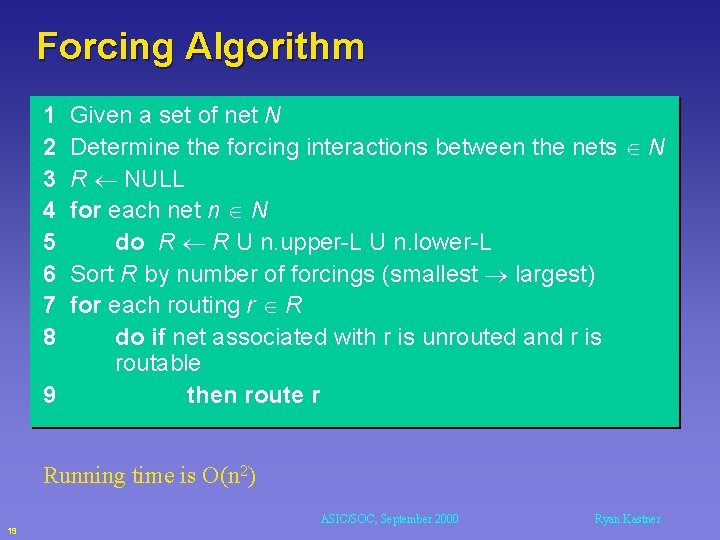

Forcing Algorithm 1 2 3 4 5 6 7 8 Given a set of net N Determine the forcing interactions between the nets N R NULL for each net n N do R R U n. upper-L U n. lower-L Sort R by number of forcings (smallest largest) for each routing r R do if net associated with r is unrouted and r is routable 9 then route r Running time is O(n 2) ASIC/SOC, September 2000 19 Ryan Kastner

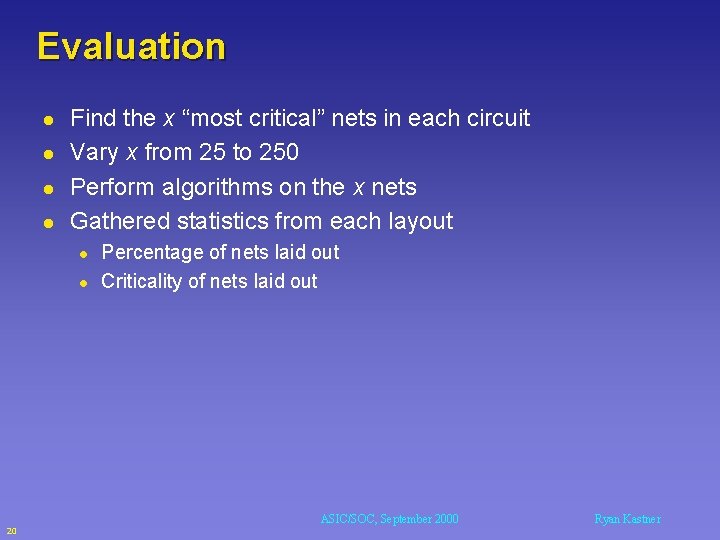

Evaluation l l Find the x “most critical” nets in each circuit Vary x from 25 to 250 Perform algorithms on the x nets Gathered statistics from each layout l l Percentage of nets laid out Criticality of nets laid out ASIC/SOC, September 2000 20 Ryan Kastner

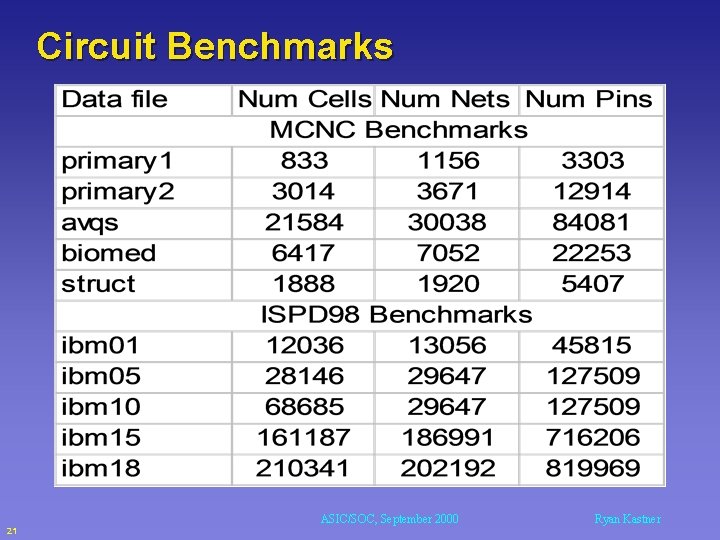

Circuit Benchmarks ASIC/SOC, September 2000 21 Ryan Kastner

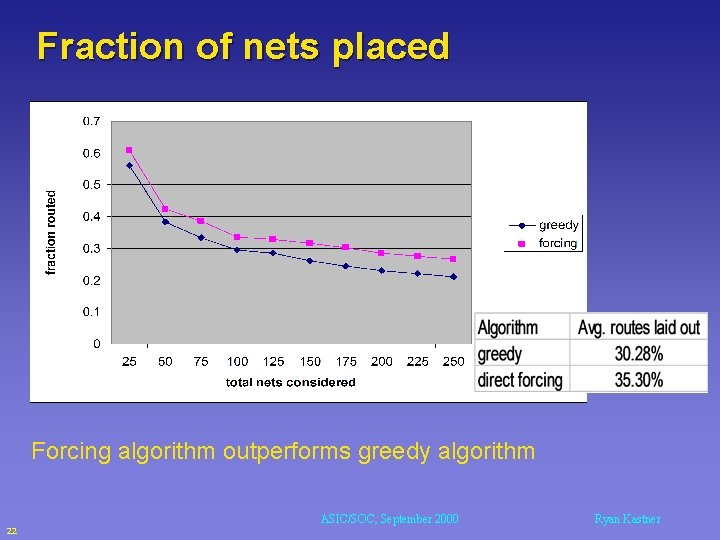

Fraction of nets placed Forcing algorithm outperforms greedy algorithm ASIC/SOC, September 2000 22 Ryan Kastner

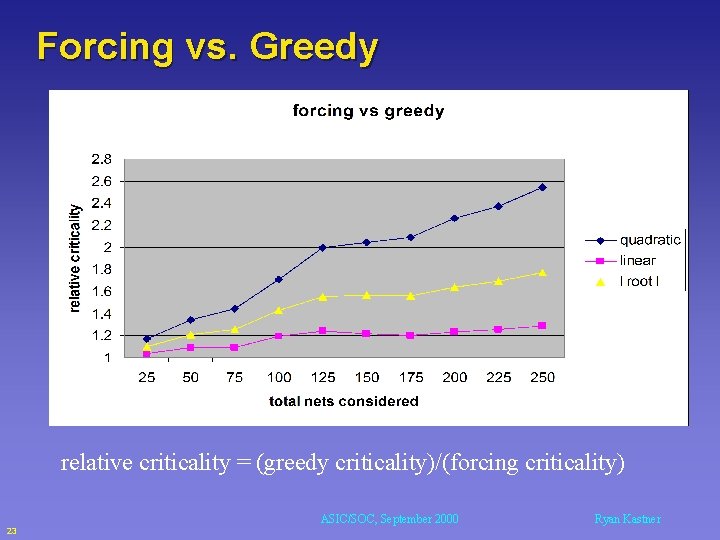

Forcing vs. Greedy relative criticality = (greedy criticality)/(forcing criticality) ASIC/SOC, September 2000 23 Ryan Kastner

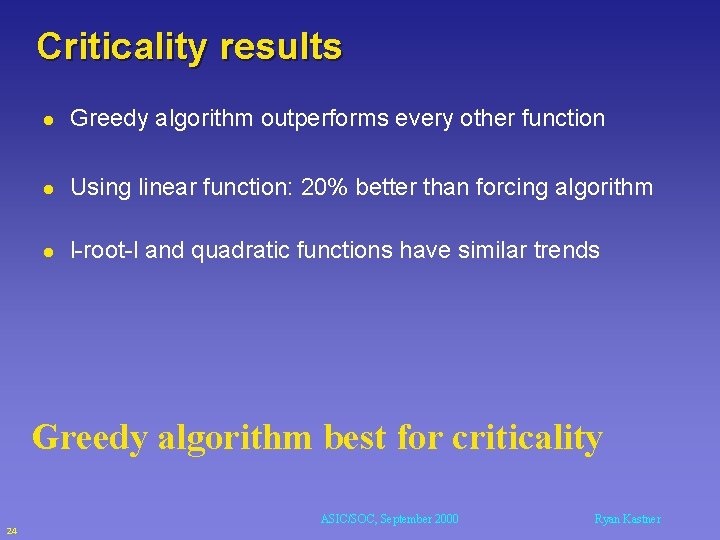

Criticality results l Greedy algorithm outperforms every other function l Using linear function: 20% better than forcing algorithm l l-root-l and quadratic functions have similar trends Greedy algorithm best for criticality ASIC/SOC, September 2000 24 Ryan Kastner

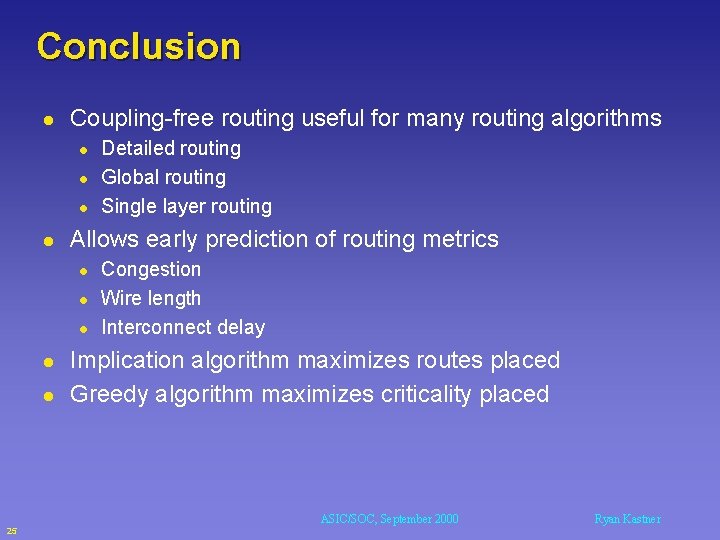

Conclusion l Coupling-free routing useful for many routing algorithms l l Allows early prediction of routing metrics l l l Detailed routing Global routing Single layer routing Congestion Wire length Interconnect delay Implication algorithm maximizes routes placed Greedy algorithm maximizes criticality placed ASIC/SOC, September 2000 25 Ryan Kastner

- Slides: 25