Counters Discussion D 5 3 Example 33 Counters

- Slides: 23

Counters Discussion D 5. 3 Example 33

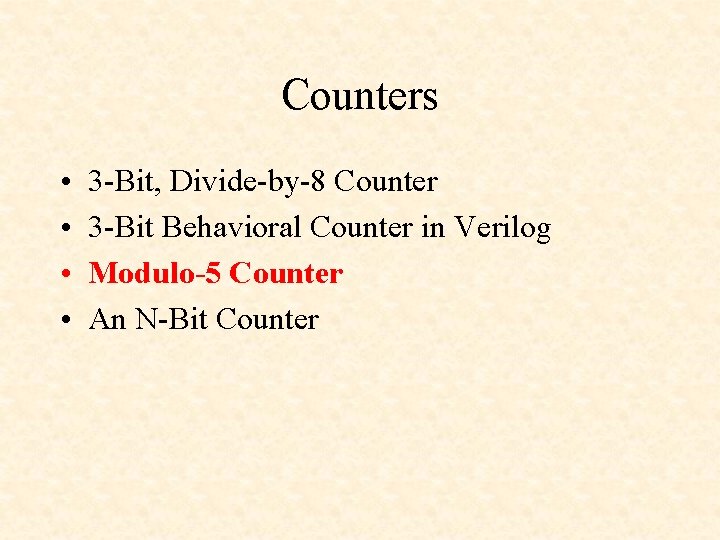

Counters • • 3 -Bit, Divide-by-8 Counter 3 -Bit Behavioral Counter in Verilog Modulo-5 Counter An N-Bit Counter

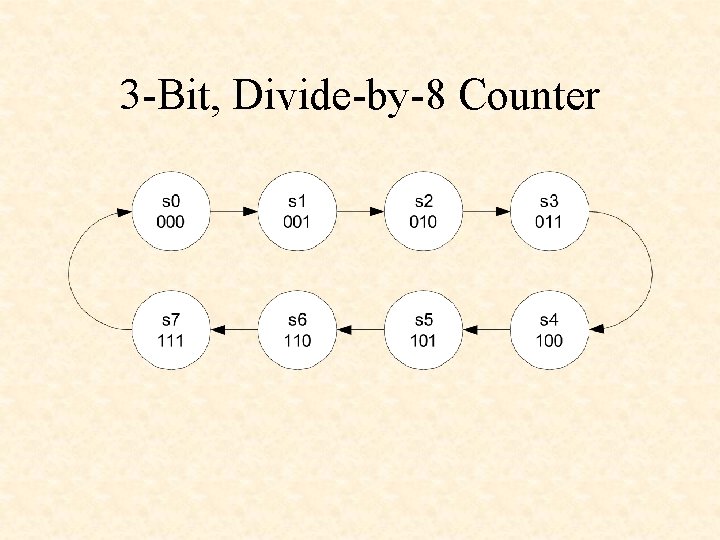

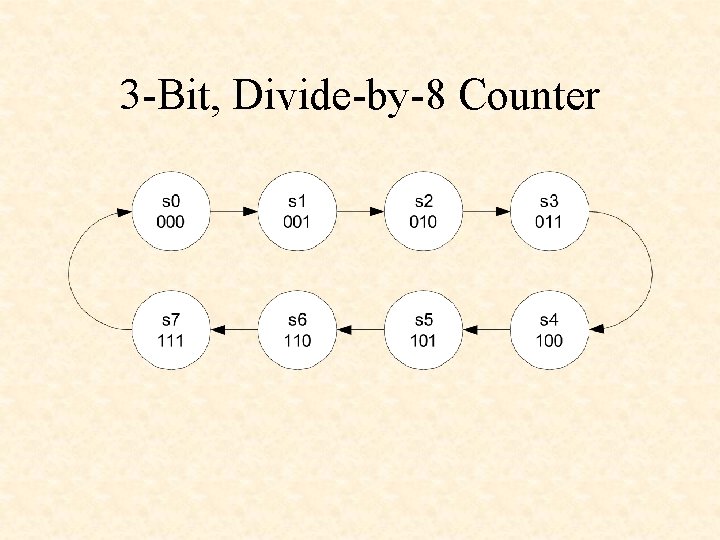

3 -Bit, Divide-by-8 Counter

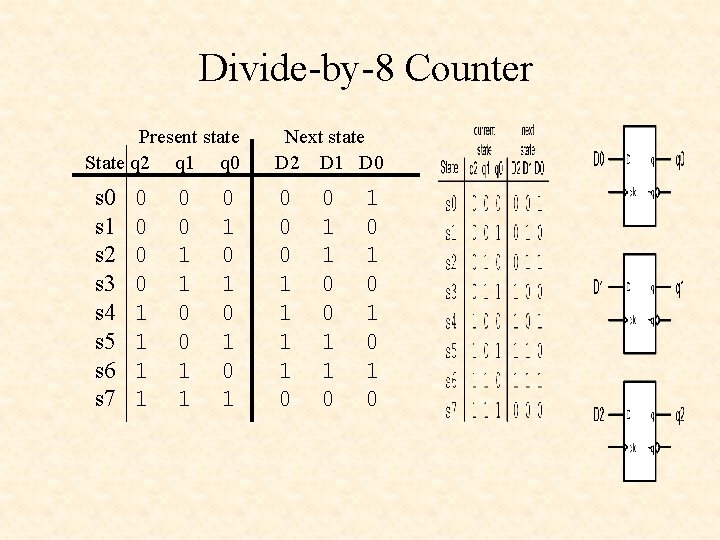

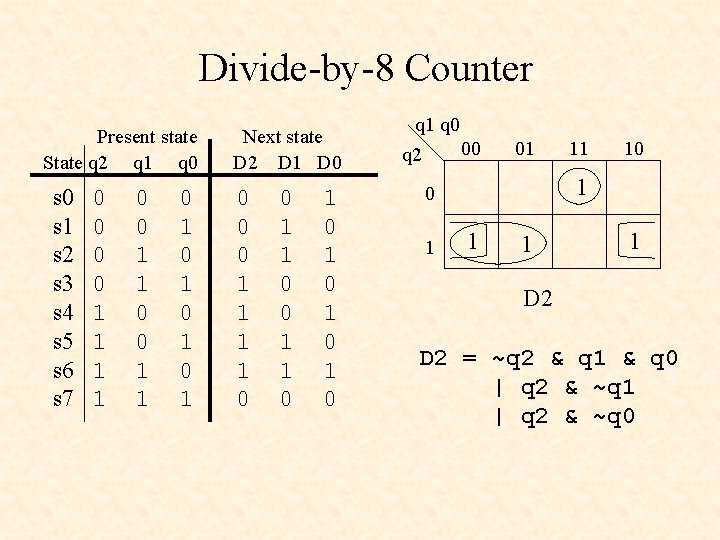

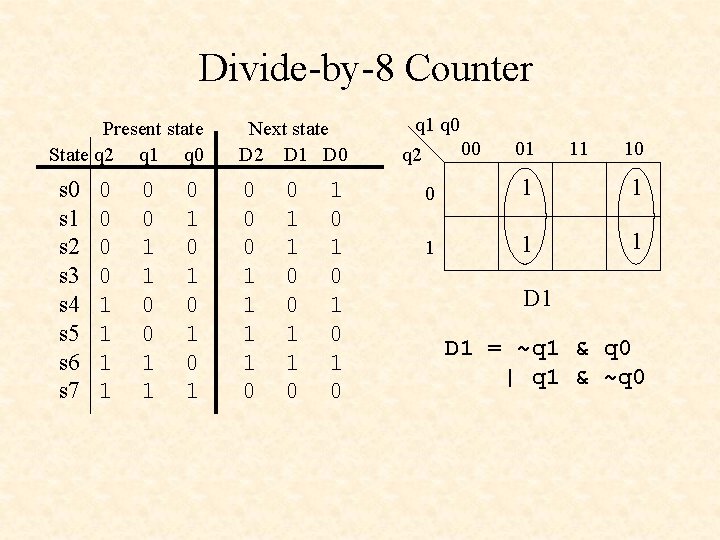

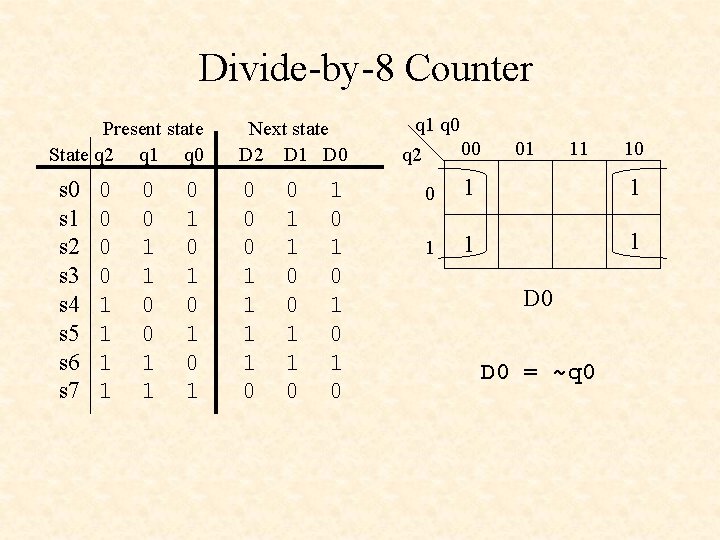

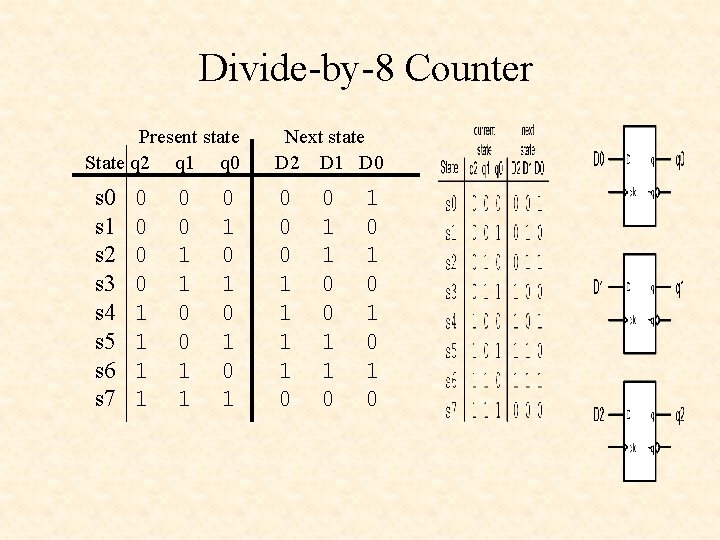

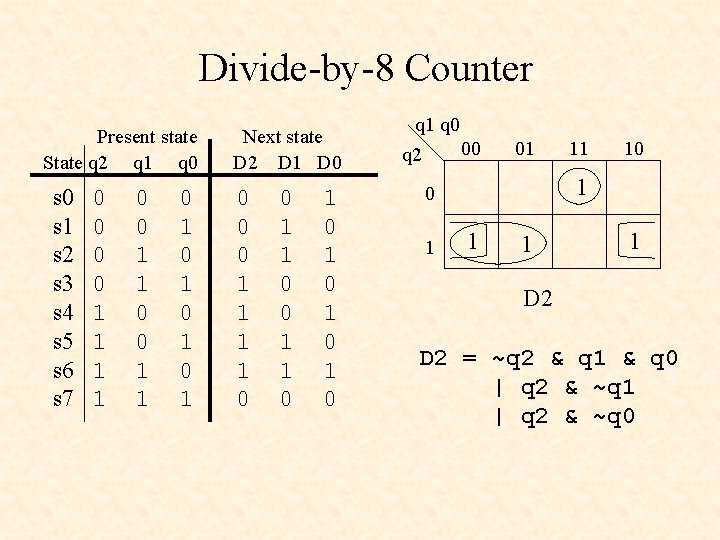

Divide-by-8 Counter Present state State q 2 q 1 q 0 s 1 s 2 s 3 s 4 s 5 s 6 s 7 0 0 1 1 0 1 0 1 Next state D 2 D 1 D 0 0 1 1 0 1 0 1 0

Divide-by-8 Counter Present state State q 2 q 1 q 0 s 1 s 2 s 3 s 4 s 5 s 6 s 7 0 0 1 1 0 1 0 1 Next state D 2 D 1 D 0 0 1 1 0 1 0 1 0 q 1 q 0 00 q 2 01 10 1 11 1 D 2 = ~q 2 & q 1 & q 0 | q 2 & ~q 1 | q 2 & ~q 0

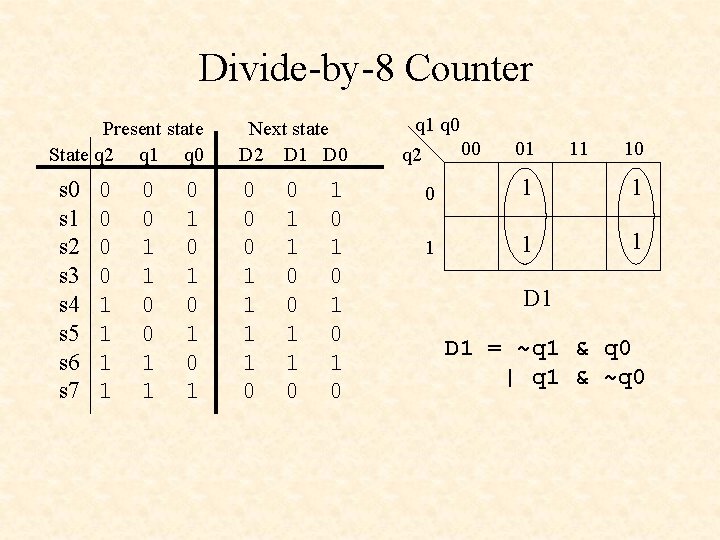

Divide-by-8 Counter Present state State q 2 q 1 q 0 s 1 s 2 s 3 s 4 s 5 s 6 s 7 0 0 1 1 0 1 0 1 Next state D 2 D 1 D 0 0 1 1 0 1 0 1 0 q 1 q 0 00 q 2 01 11 10 0 1 1 1 D 1 = ~q 1 & q 0 | q 1 & ~q 0

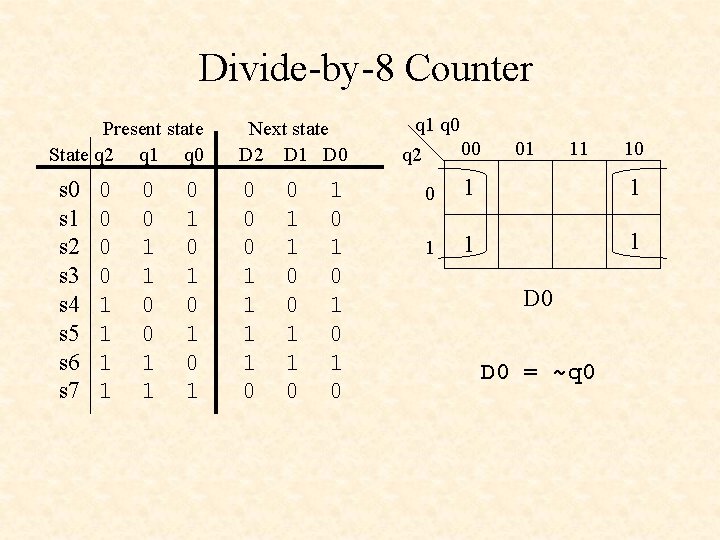

Divide-by-8 Counter Present state State q 2 q 1 q 0 s 1 s 2 s 3 s 4 s 5 s 6 s 7 0 0 1 1 0 1 0 1 Next state D 2 D 1 D 0 0 1 1 0 1 0 1 0 q 1 q 0 00 q 2 01 11 10 0 1 1 1 D 0 = ~q 0

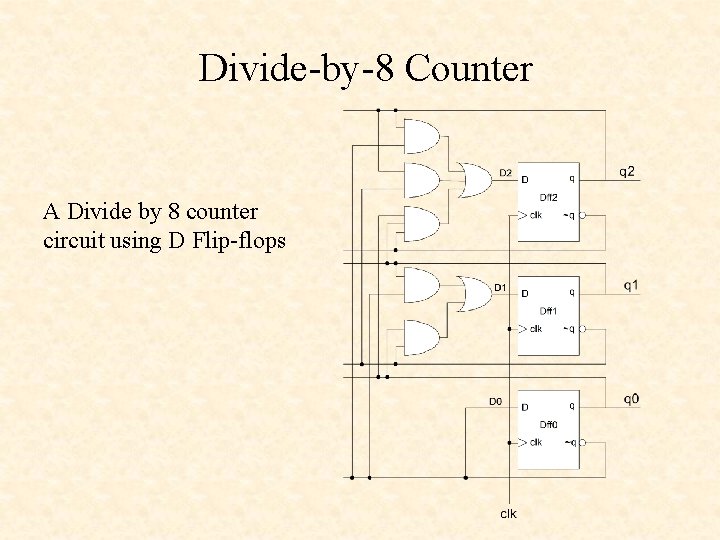

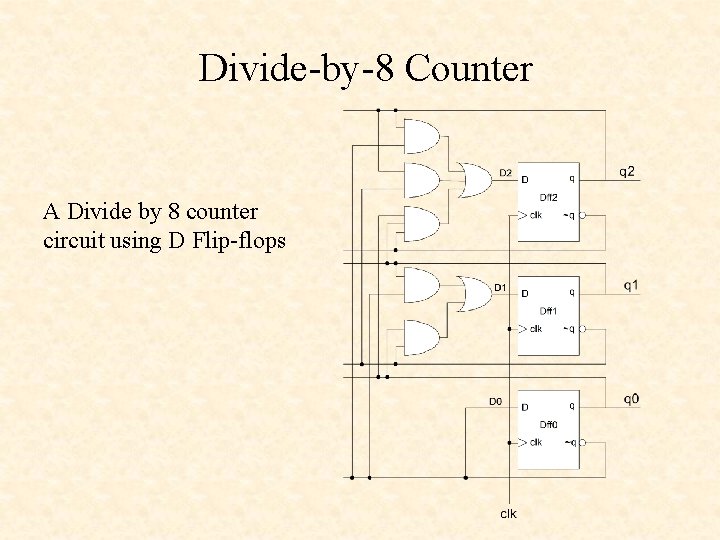

Divide-by-8 Counter A Divide by 8 counter circuit using D Flip-flops

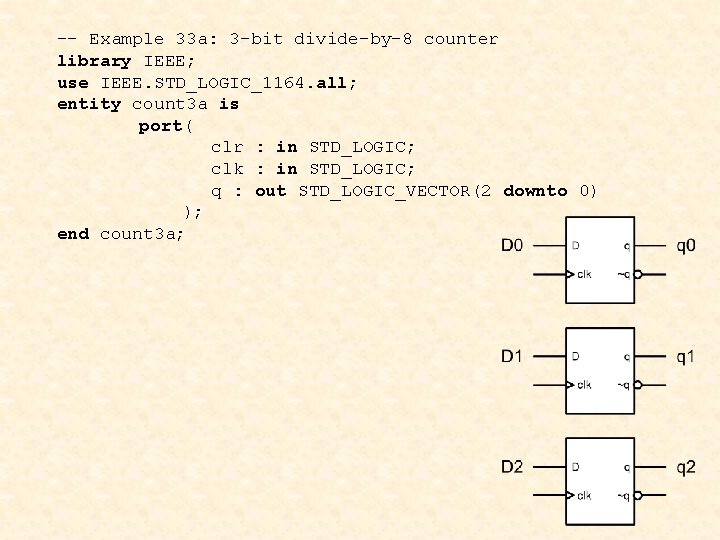

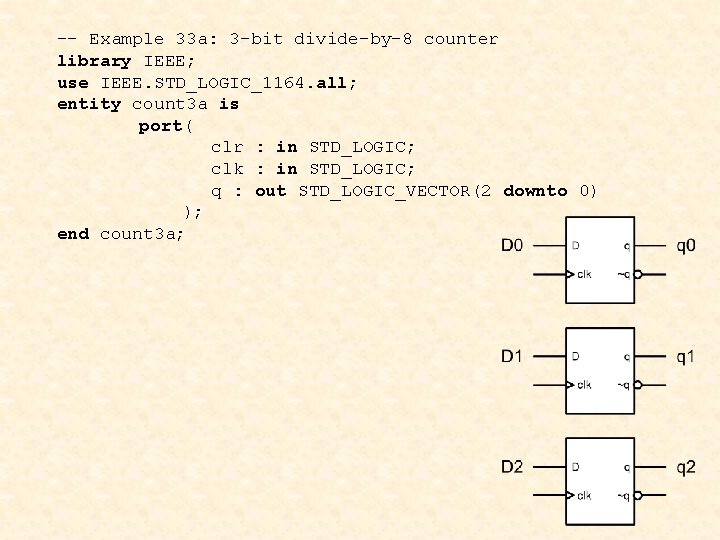

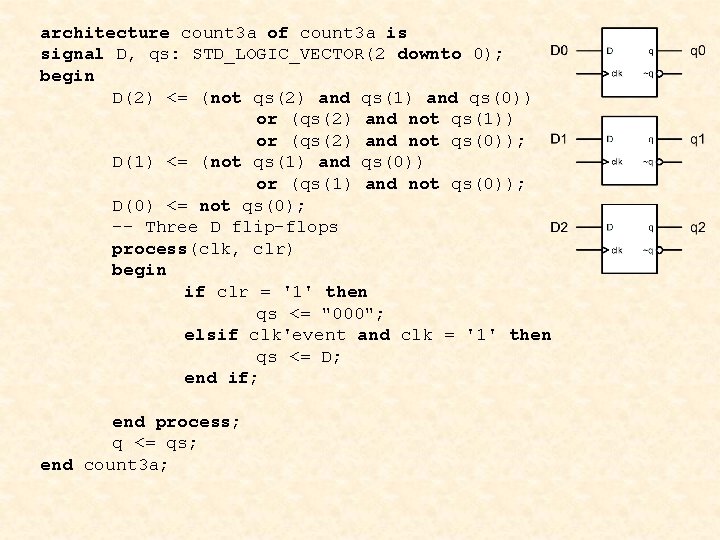

-- Example 33 a: 3 -bit divide-by-8 counter library IEEE; use IEEE. STD_LOGIC_1164. all; entity count 3 a is port( clr : in STD_LOGIC; clk : in STD_LOGIC; q : out STD_LOGIC_VECTOR(2 downto 0) ); end count 3 a;

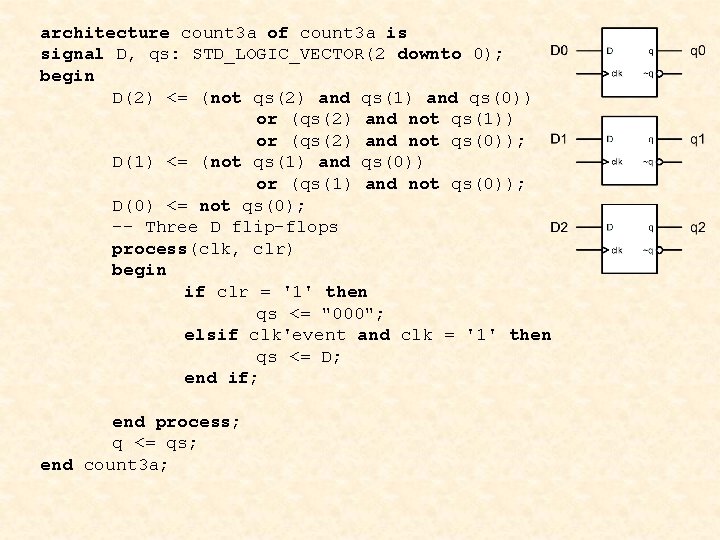

architecture count 3 a of count 3 a is signal D, qs: STD_LOGIC_VECTOR(2 downto 0); begin D(2) <= (not qs(2) and qs(1) and qs(0)) or (qs(2) and not qs(1)) or (qs(2) and not qs(0)); D(1) <= (not qs(1) and qs(0)) or (qs(1) and not qs(0)); D(0) <= not qs(0); -- Three D flip-flops process(clk, clr) begin if clr = '1' then qs <= "000"; elsif clk'event and clk = '1' then qs <= D; end if; end process; q <= qs; end count 3 a;

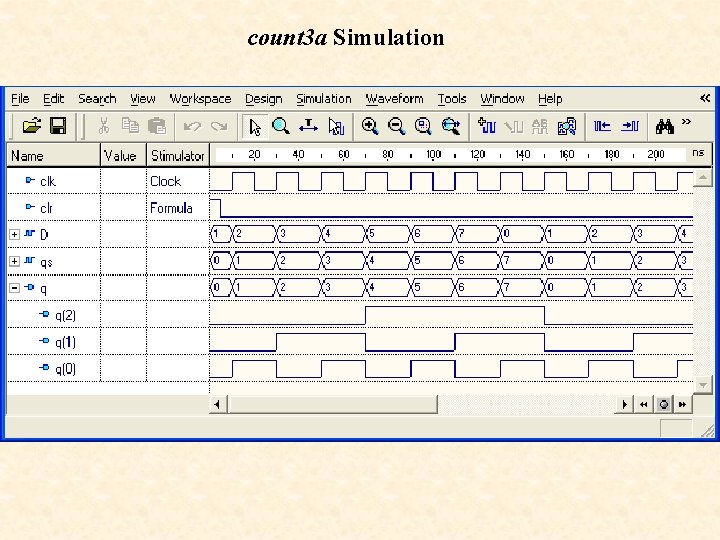

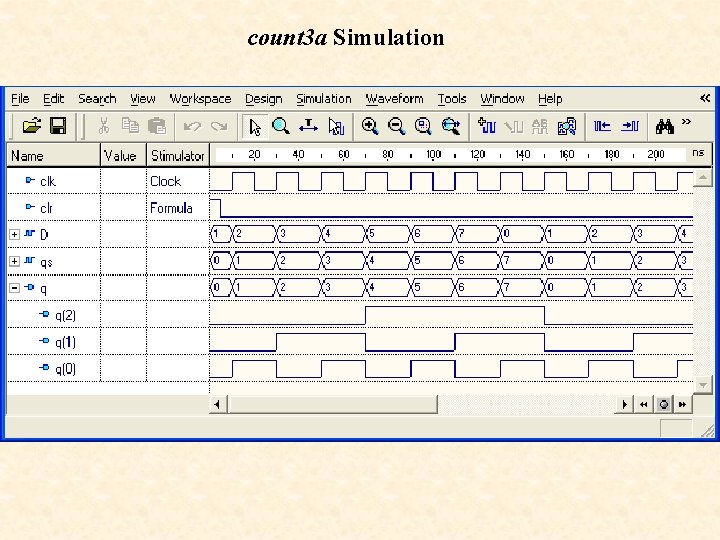

count 3 a Simulation

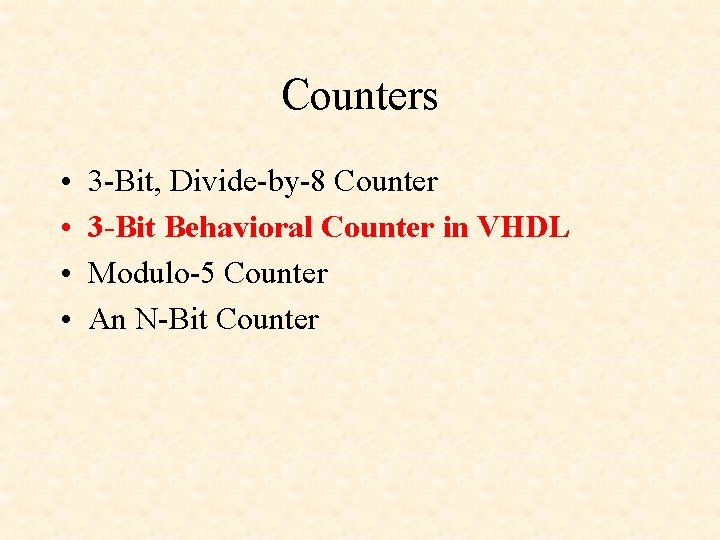

Counters • • 3 -Bit, Divide-by-8 Counter 3 -Bit Behavioral Counter in VHDL Modulo-5 Counter An N-Bit Counter

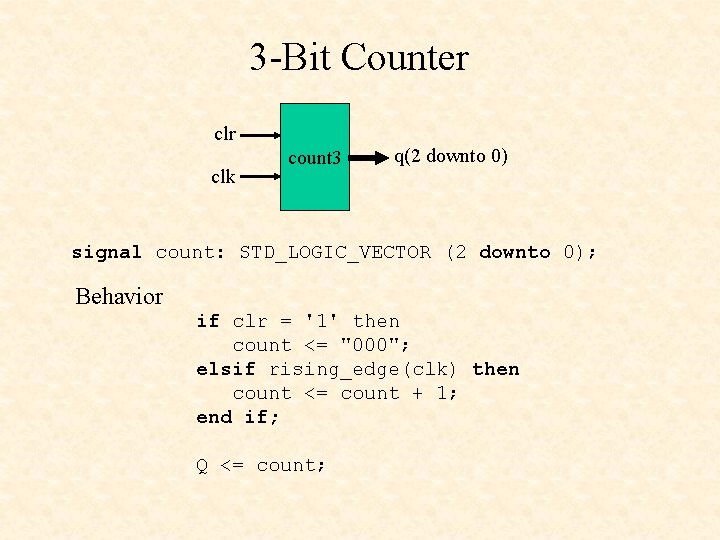

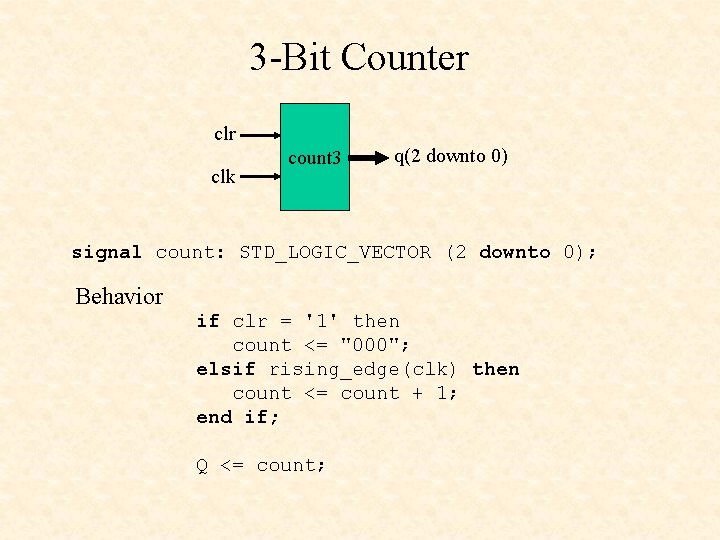

3 -Bit Counter clk count 3 q(2 downto 0) signal count: STD_LOGIC_VECTOR (2 downto 0); Behavior if clr = '1' then count <= "000"; elsif rising_edge(clk) then count <= count + 1; end if; Q <= count;

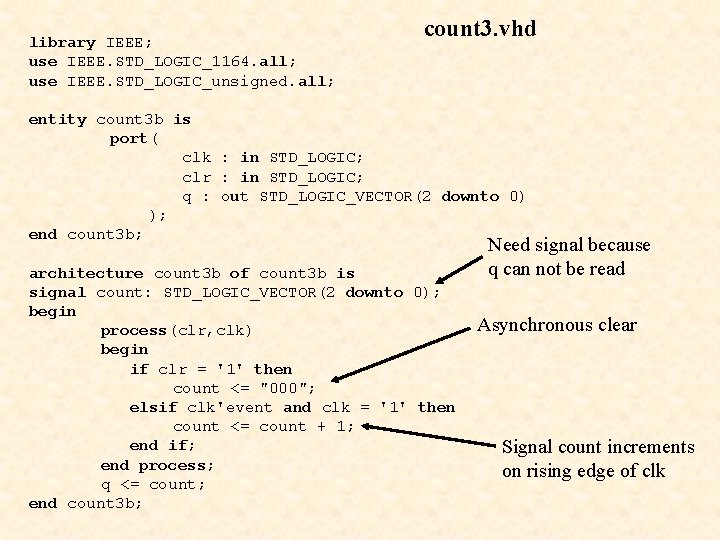

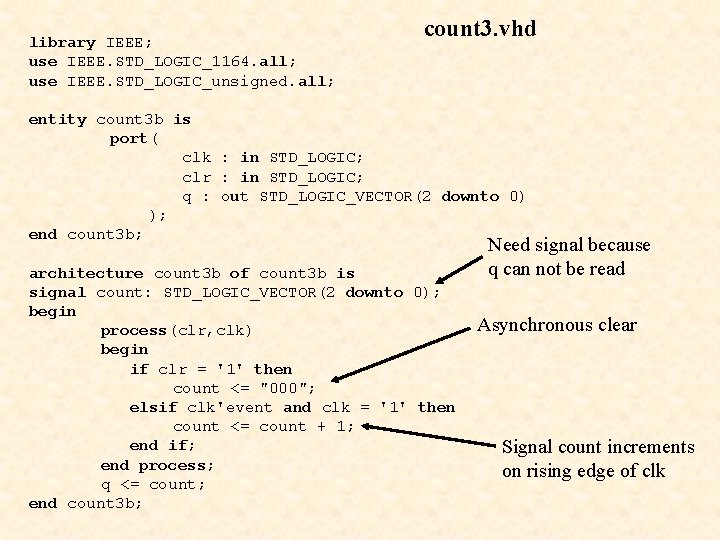

library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. STD_LOGIC_unsigned. all; count 3. vhd entity count 3 b is port( clk : in STD_LOGIC; clr : in STD_LOGIC; q : out STD_LOGIC_VECTOR(2 downto 0) ); end count 3 b; architecture count 3 b of count 3 b is signal count: STD_LOGIC_VECTOR(2 downto 0); begin process(clr, clk) begin if clr = '1' then count <= "000"; elsif clk'event and clk = '1' then count <= count + 1; end if; end process; q <= count; end count 3 b; Need signal because q can not be read Asynchronous clear Signal count increments on rising edge of clk

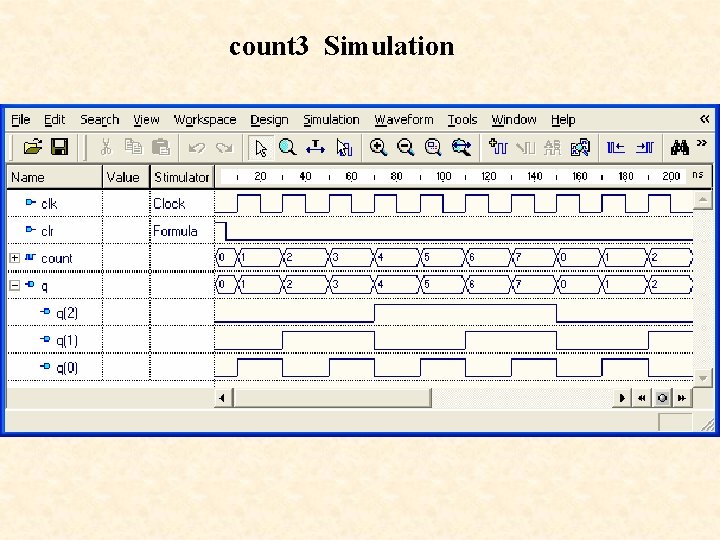

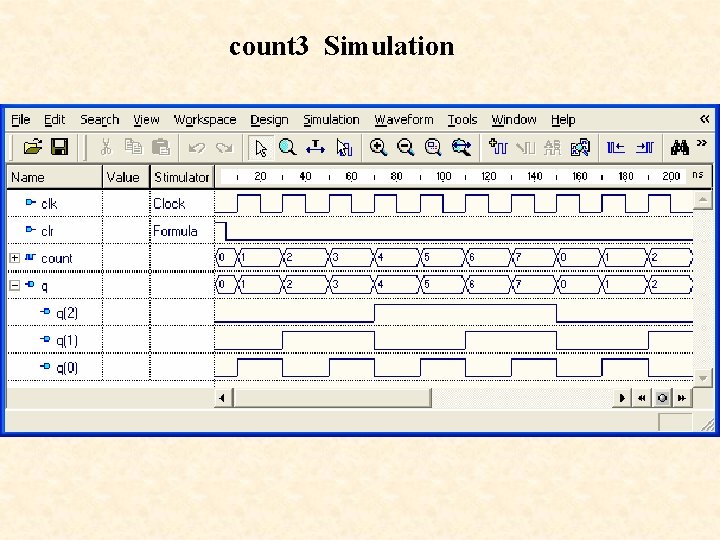

count 3 Simulation

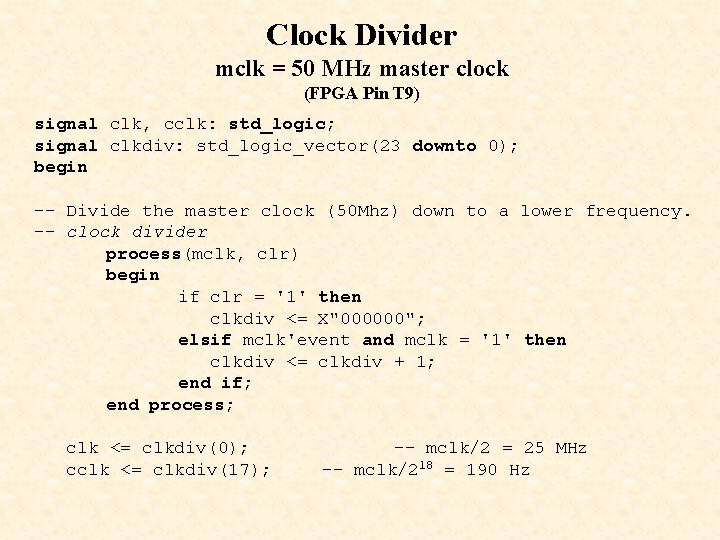

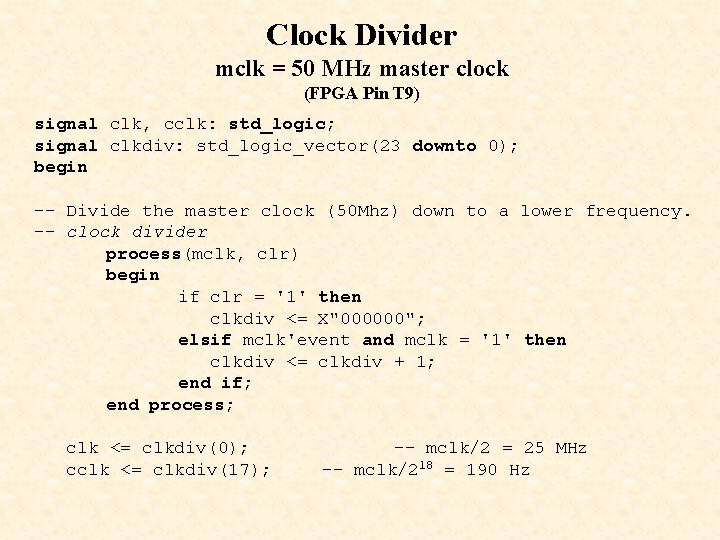

Clock Divider mclk = 50 MHz master clock (FPGA Pin T 9) signal clk, cclk: std_logic; signal clkdiv: std_logic_vector(23 downto 0); begin -- Divide the master clock (50 Mhz) down to a lower frequency. -- clock divider process(mclk, clr) begin if clr = '1' then clkdiv <= X"000000"; elsif mclk'event and mclk = '1' then clkdiv <= clkdiv + 1; end if; end process; clk <= clkdiv(0); cclk <= clkdiv(17); -- mclk/2 = 25 MHz -- mclk/218 = 190 Hz

Counters • • 3 -Bit, Divide-by-8 Counter 3 -Bit Behavioral Counter in Verilog Modulo-5 Counter An N-Bit Counter

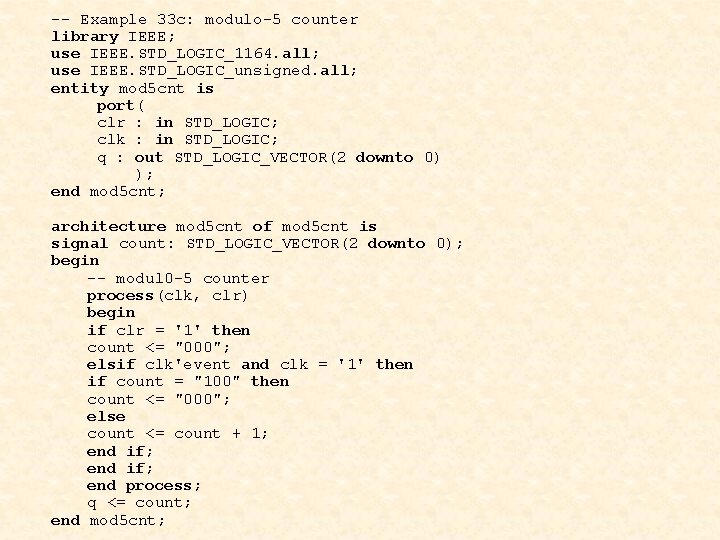

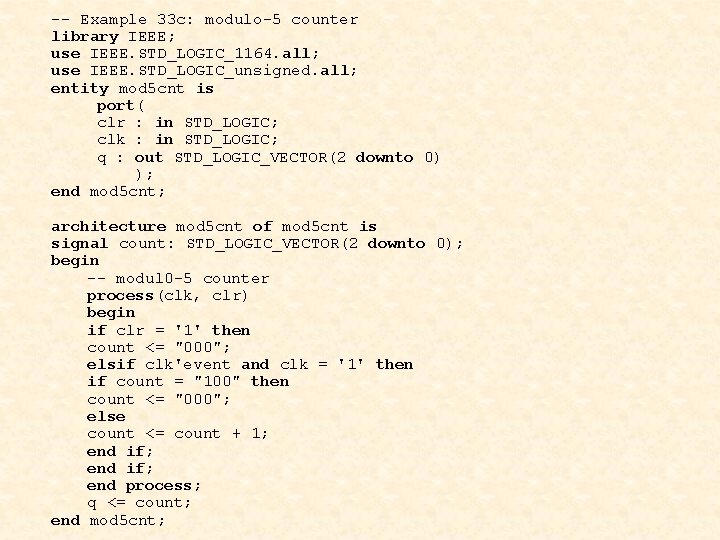

-- Example 33 c: modulo-5 counter library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. STD_LOGIC_unsigned. all; entity mod 5 cnt is port( clr : in STD_LOGIC; clk : in STD_LOGIC; q : out STD_LOGIC_VECTOR(2 downto 0) ); end mod 5 cnt; architecture mod 5 cnt of mod 5 cnt is signal count: STD_LOGIC_VECTOR(2 downto 0); begin -- modul 0 -5 counter process(clk, clr) begin if clr = '1' then count <= "000"; elsif clk'event and clk = '1' then if count = "100" then count <= "000"; else count <= count + 1; end if; end process; q <= count; end mod 5 cnt;

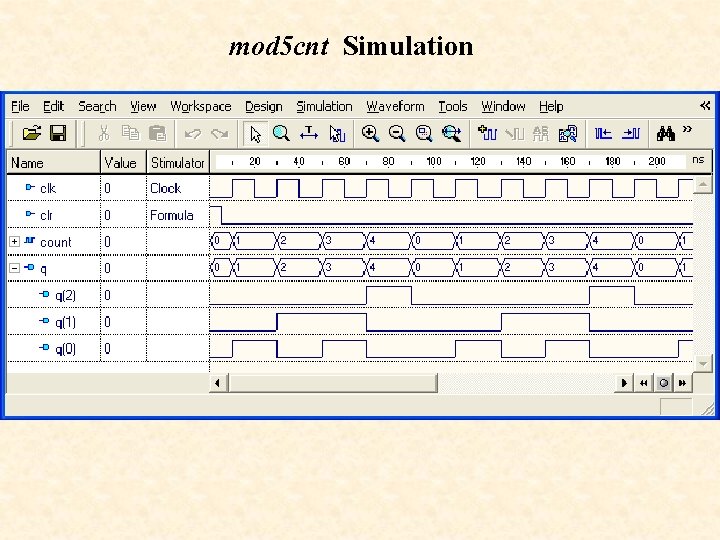

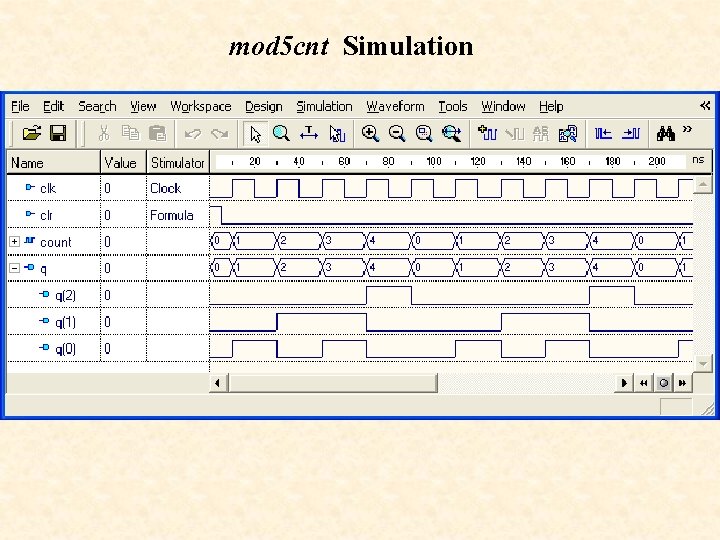

mod 5 cnt Simulation

Counters • • 3 -Bit, Divide-by-8 Counter 3 -Bit Behavioral Counter in Verilog Modulo-5 Counter An N-Bit Counter

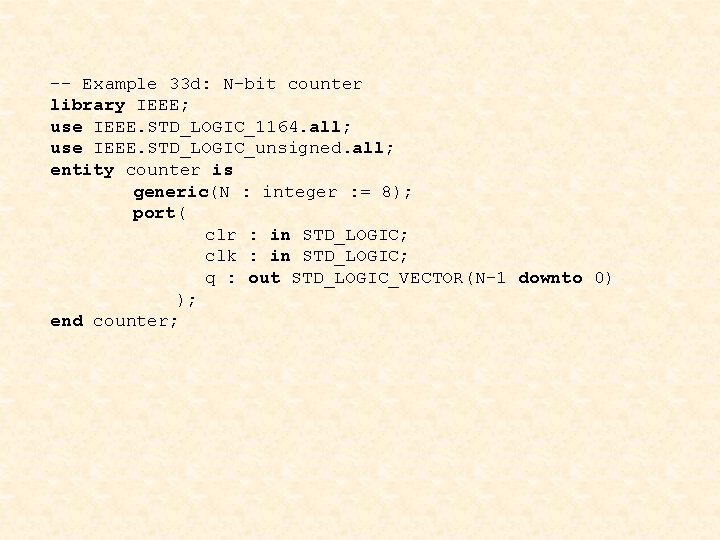

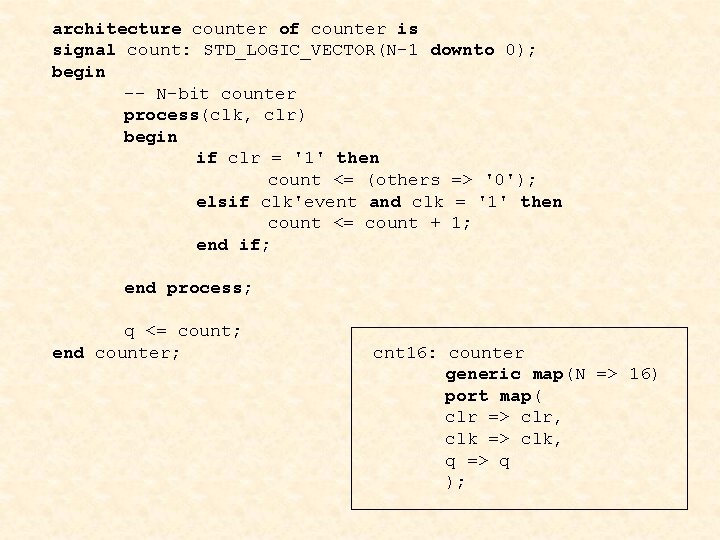

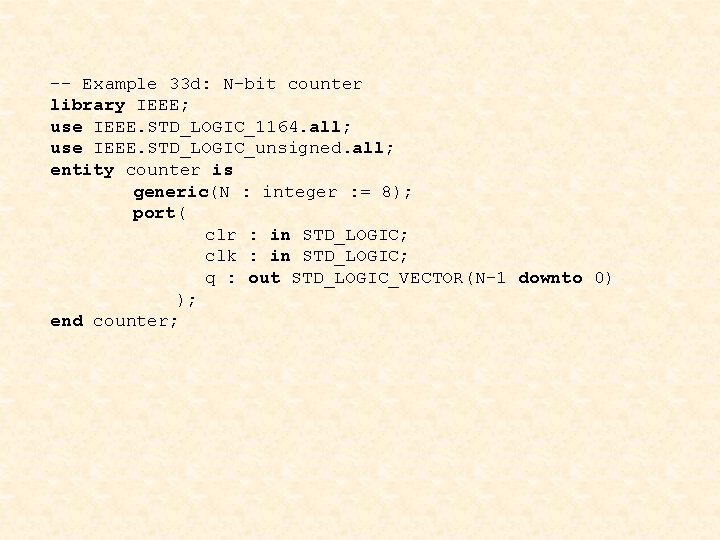

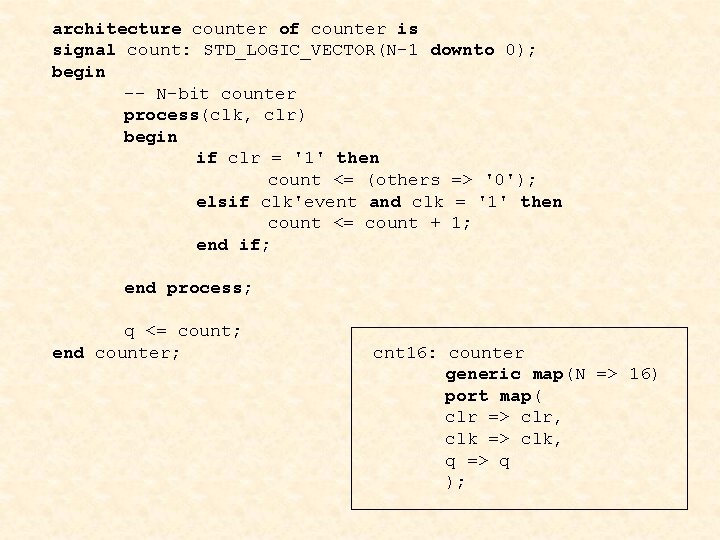

-- Example 33 d: N-bit counter library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. STD_LOGIC_unsigned. all; entity counter is generic(N : integer : = 8); port( clr : in STD_LOGIC; clk : in STD_LOGIC; q : out STD_LOGIC_VECTOR(N-1 downto 0) ); end counter;

architecture counter of counter is signal count: STD_LOGIC_VECTOR(N-1 downto 0); begin -- N-bit counter process(clk, clr) begin if clr = '1' then count <= (others => '0'); elsif clk'event and clk = '1' then count <= count + 1; end if; end process; q <= count; end counter; cnt 16: counter generic map(N => 16) port map( clr => clr, clk => clk, q => q );

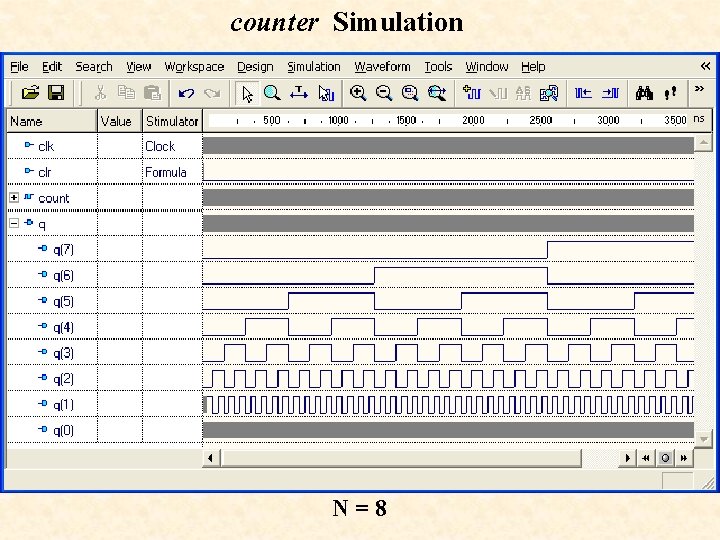

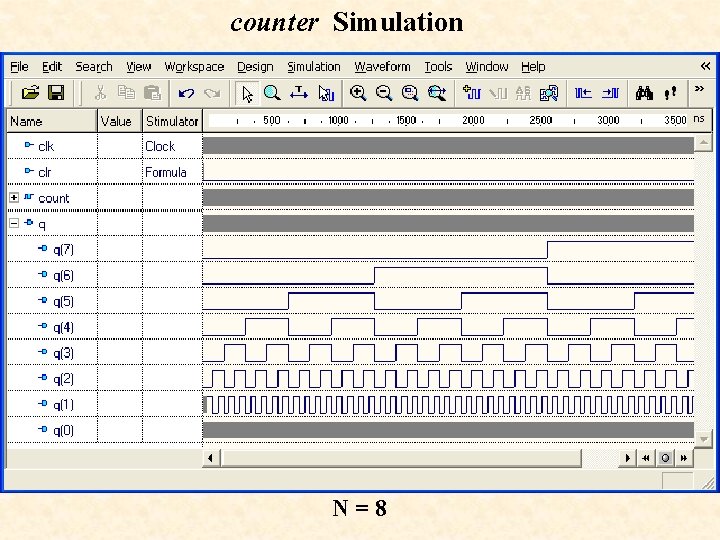

counter Simulation N=8