Counter Circuits and Applications Group 6 Overview Analysis

- Slides: 22

Counter Circuits and Applications Group 6 彭柏源 袁鋒 陳康本

Overview Analysis of Sequential Circuits. Ripple Counters. Design of Divide-by-N Counters. Ripple Counter ICs. Applications. System Design Applications. Seven-Segment LED Display Decoders. Synchronous Counters. Synchronous Up/Down-Counter ICs. Applications.

Analysis of Sequential Circuits Using Timing Diagrams to analyze.

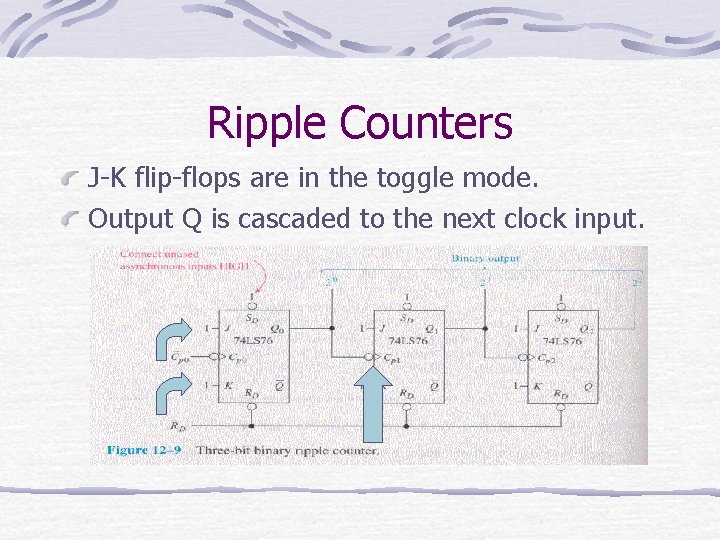

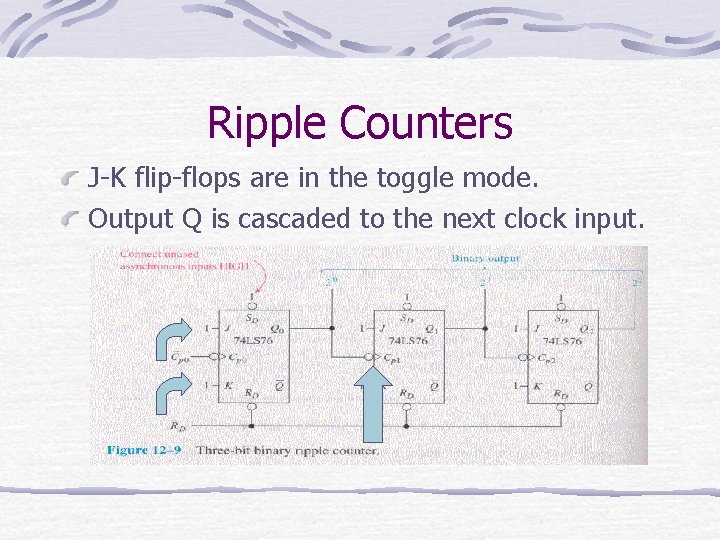

Ripple Counters J-K flip-flops are in the toggle mode. Output Q is cascaded to the next clock input.

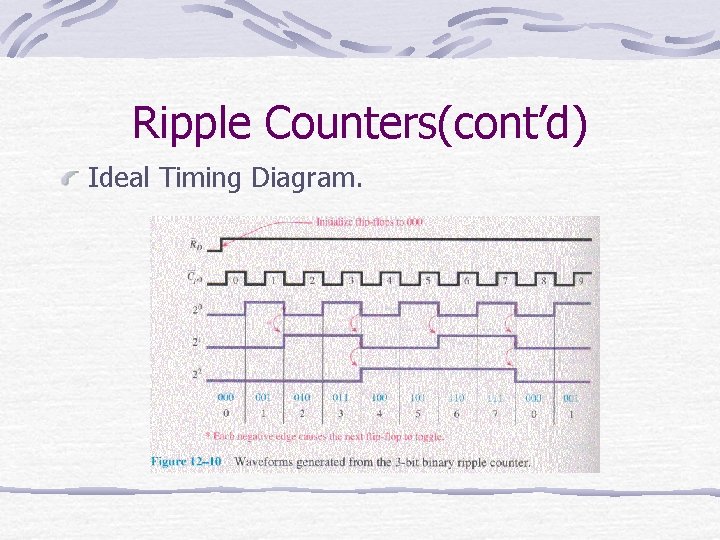

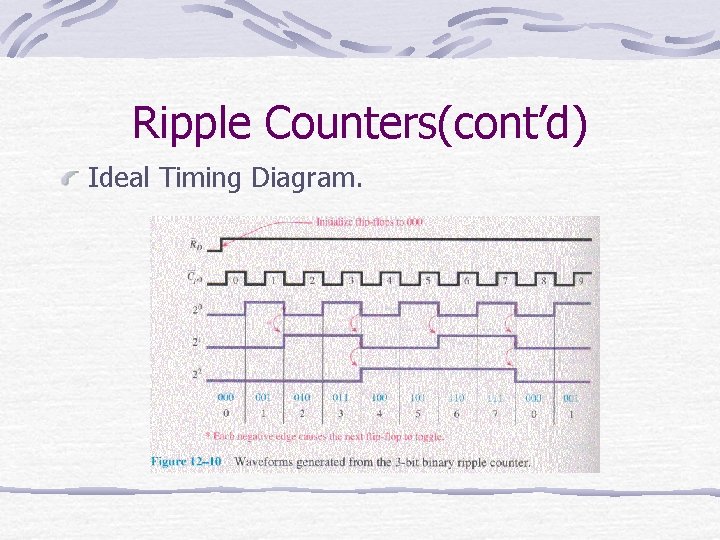

Ripple Counters(cont’d) Ideal Timing Diagram.

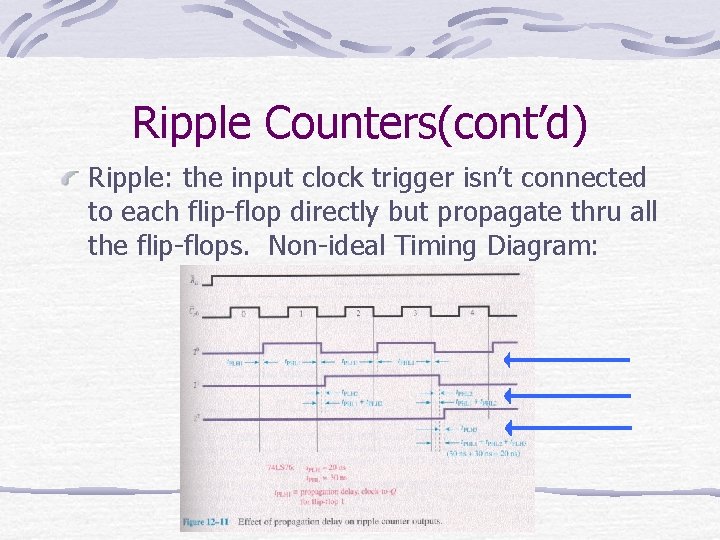

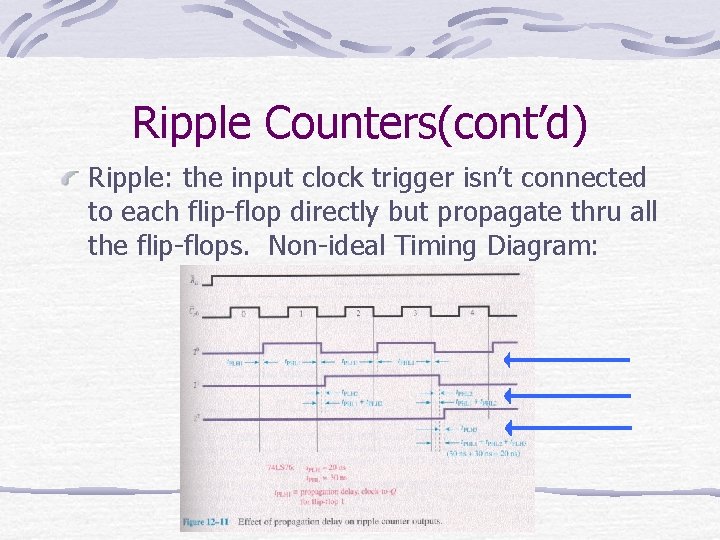

Ripple Counters(cont’d) Ripple: the input clock trigger isn’t connected to each flip-flop directly but propagate thru all the flip-flops. Non-ideal Timing Diagram:

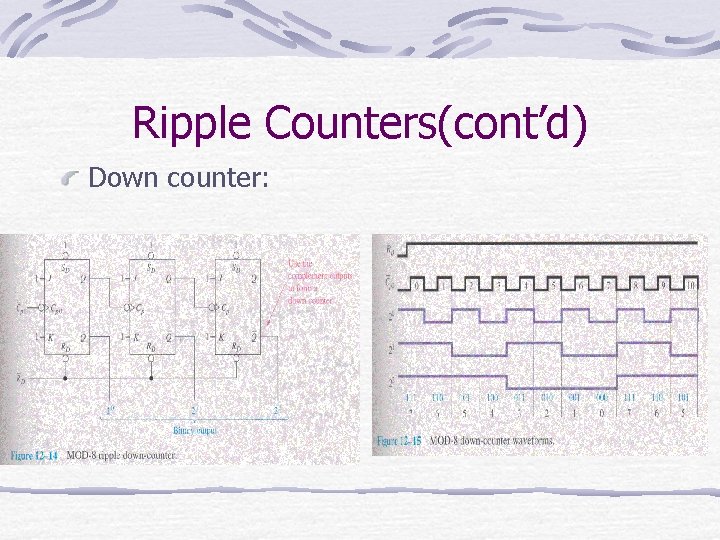

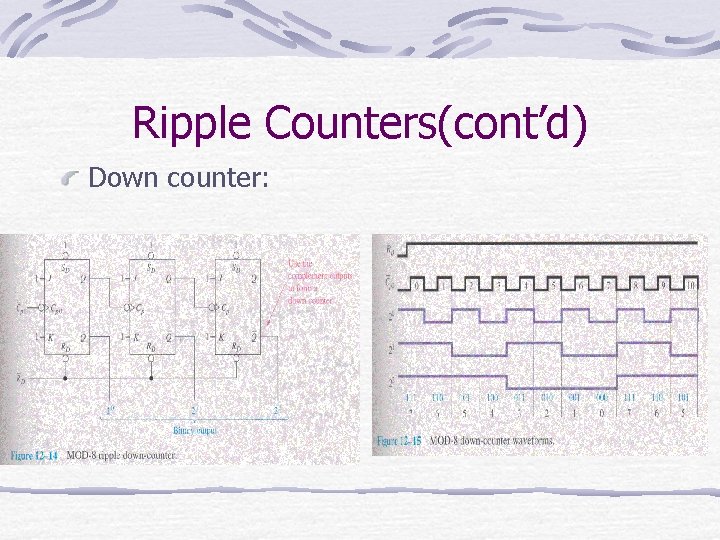

Ripple Counters(cont’d) Down counter:

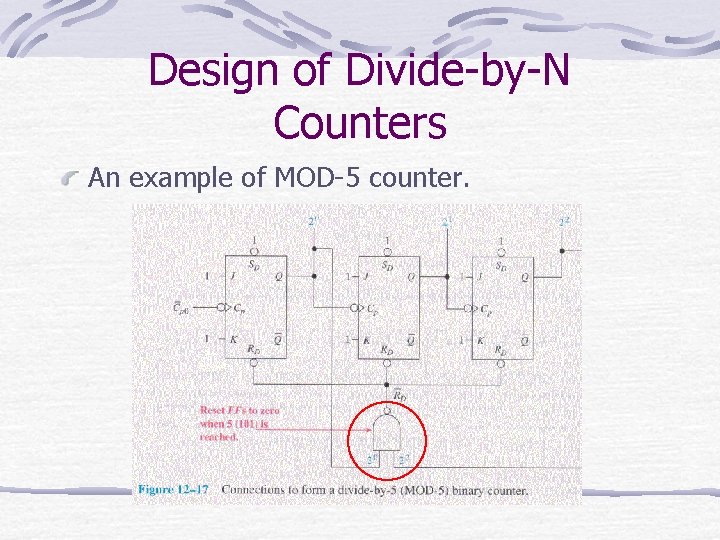

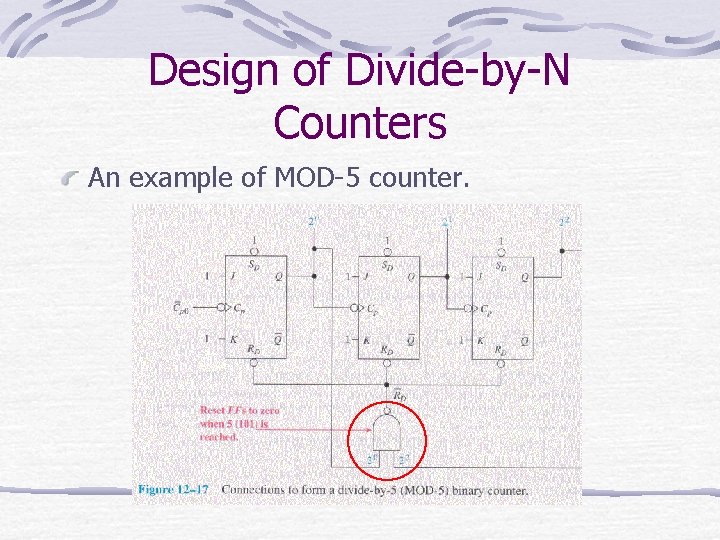

Design of Divide-by-N Counters An example of MOD-5 counter.

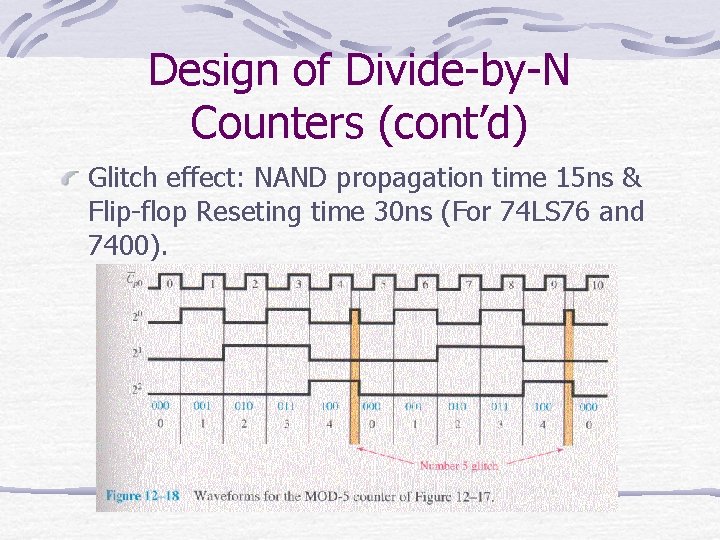

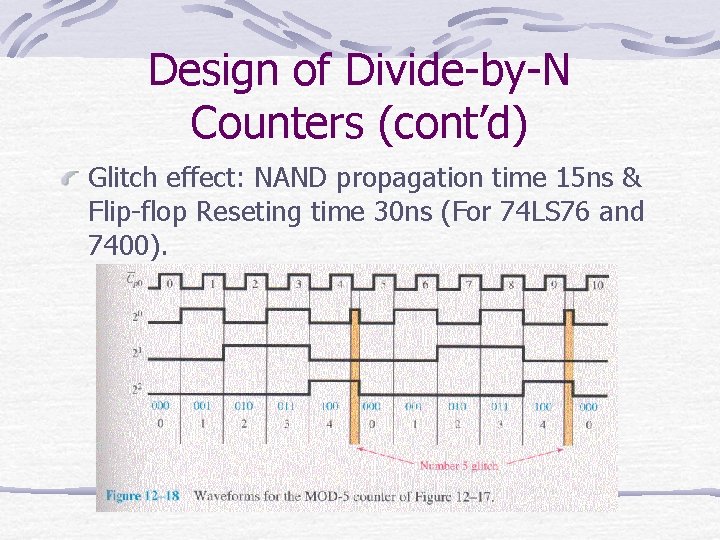

Design of Divide-by-N Counters (cont’d) Glitch effect: NAND propagation time 15 ns & Flip-flop Reseting time 30 ns (For 74 LS 76 and 7400).

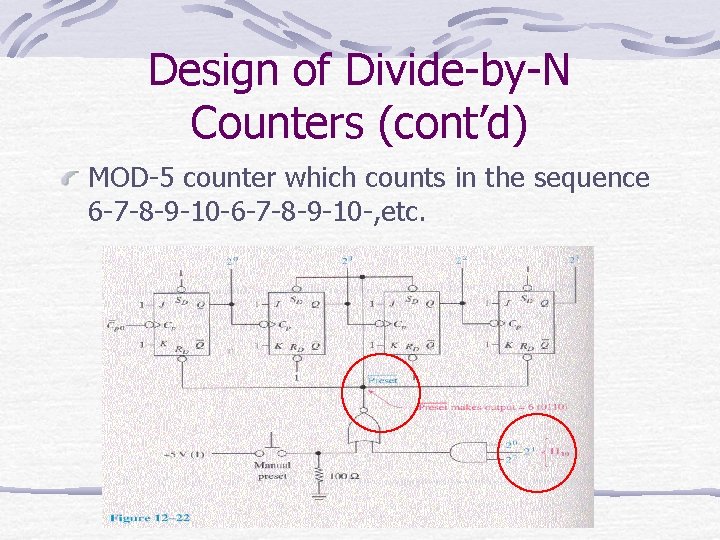

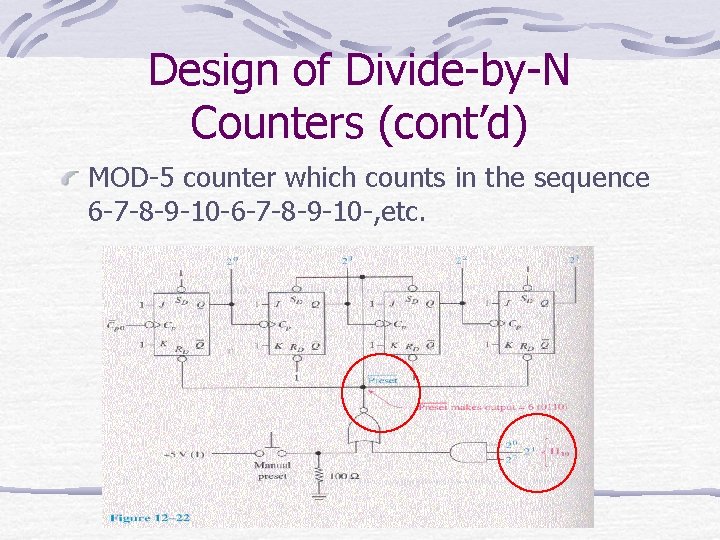

Design of Divide-by-N Counters (cont’d) MOD-5 counter which counts in the sequence 6 -7 -8 -9 -10 -, etc.

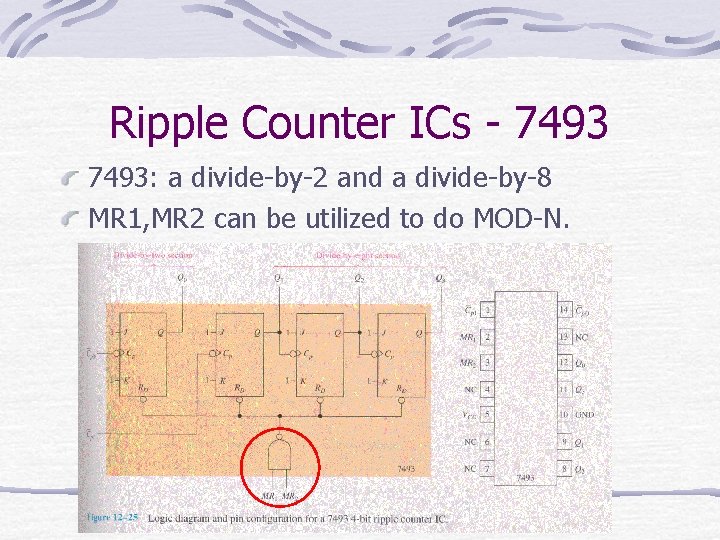

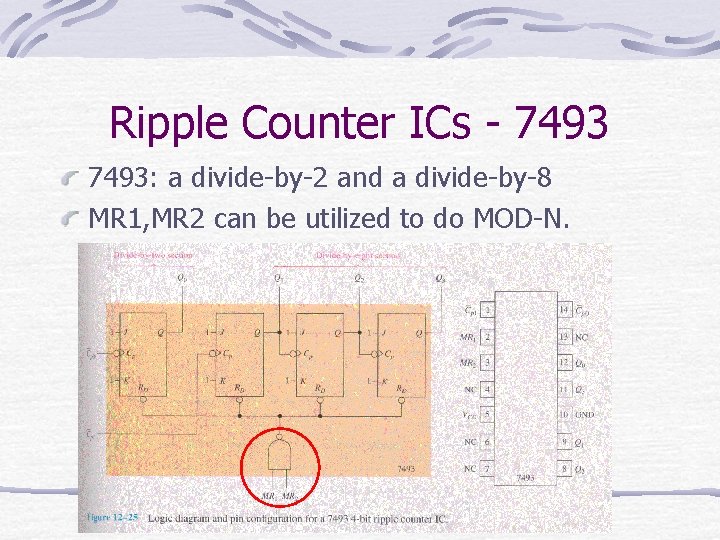

Ripple Counter ICs - 7493: a divide-by-2 and a divide-by-8 MR 1, MR 2 can be utilized to do MOD-N.

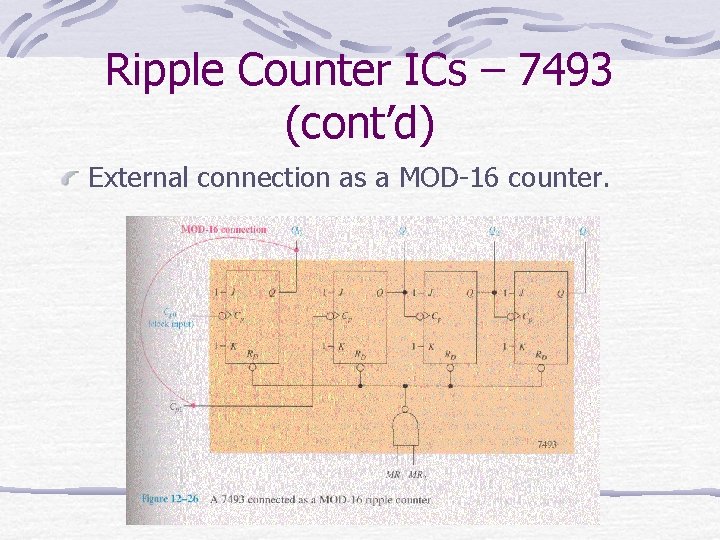

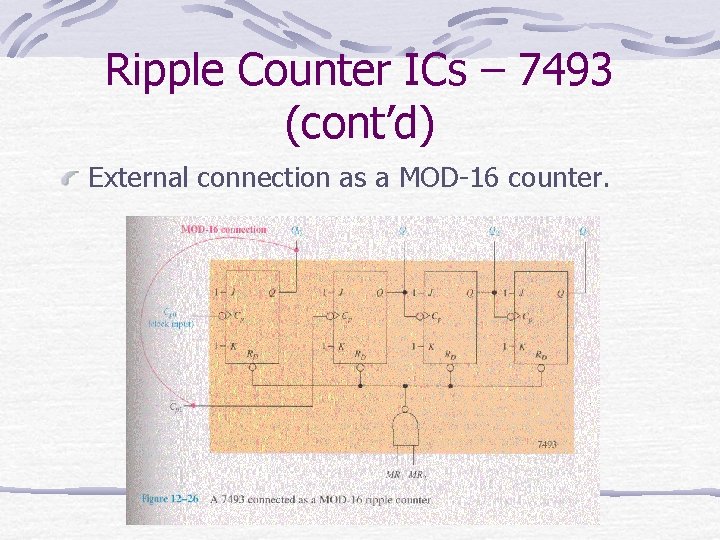

Ripple Counter ICs – 7493 (cont’d) External connection as a MOD-16 counter.

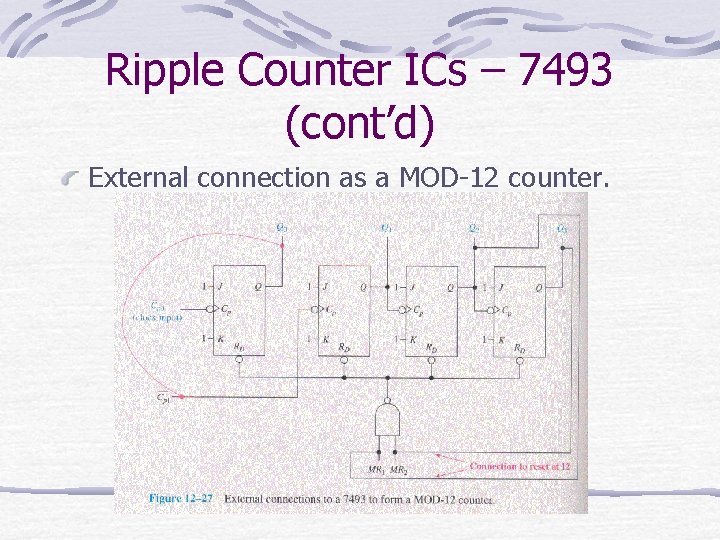

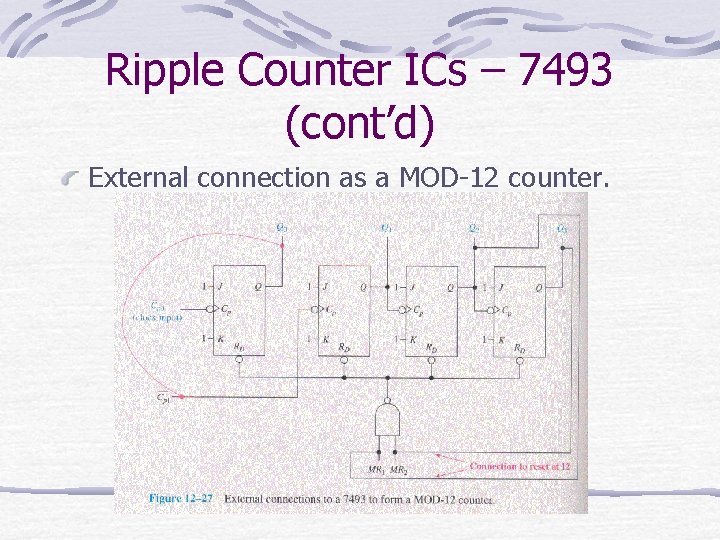

Ripple Counter ICs – 7493 (cont’d) External connection as a MOD-12 counter.

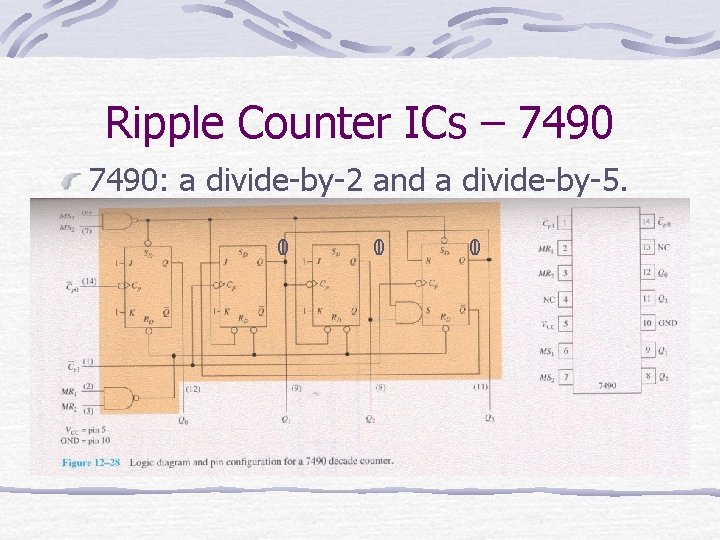

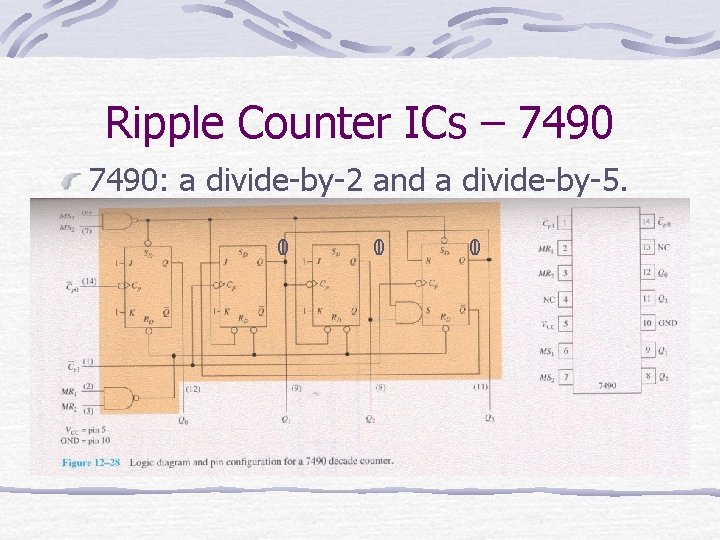

Ripple Counter ICs – 7490: a divide-by-2 and a divide-by-5. 01 01 01

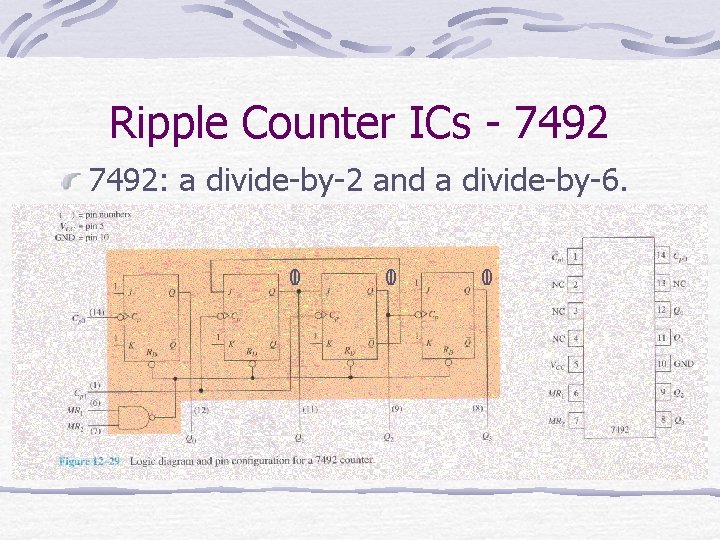

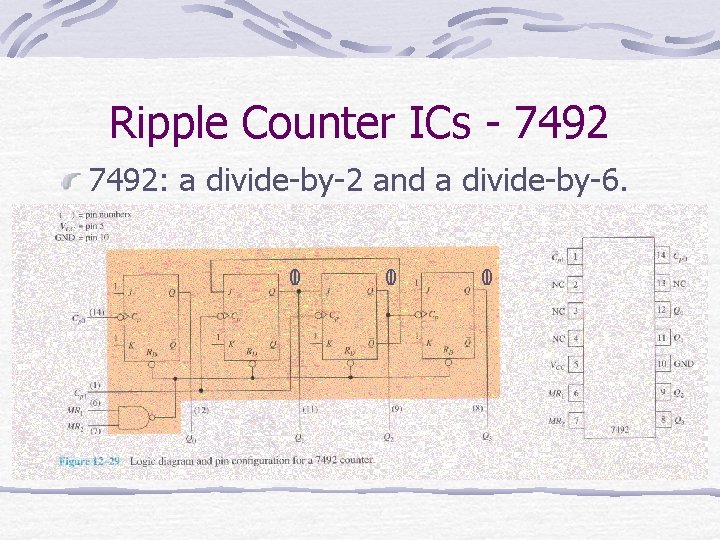

Ripple Counter ICs - 7492: a divide-by-2 and a divide-by-6. 01 10 10

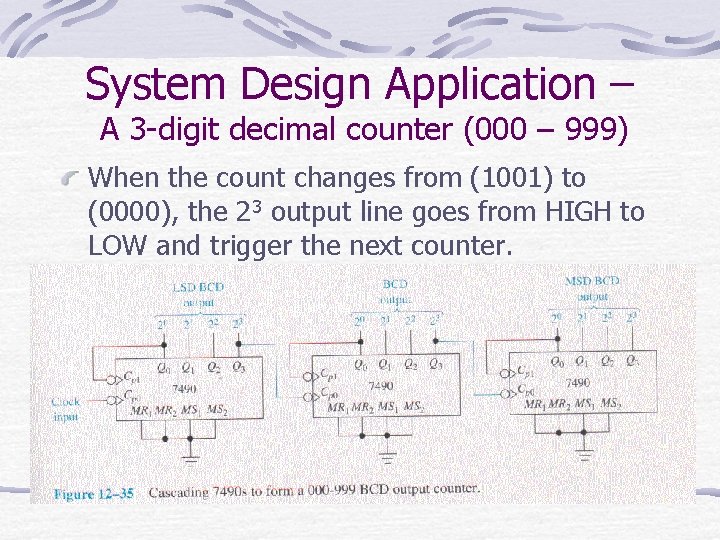

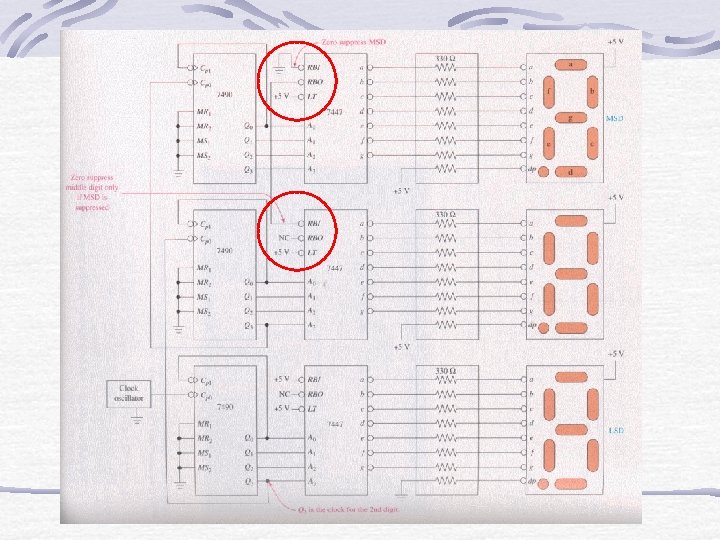

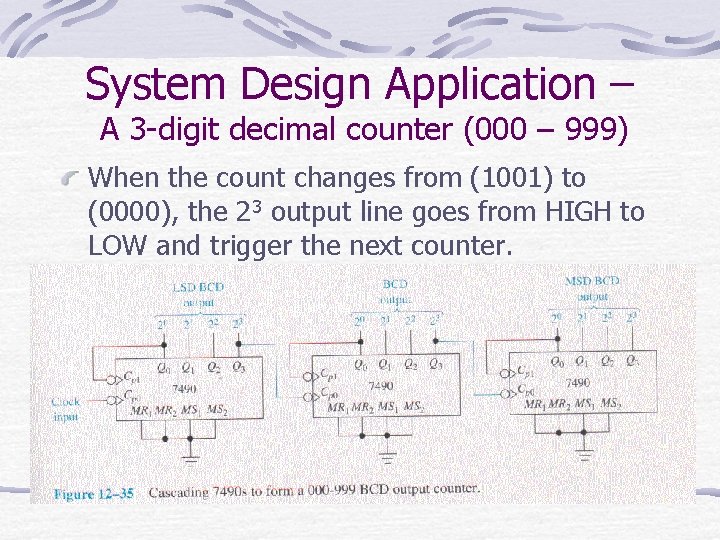

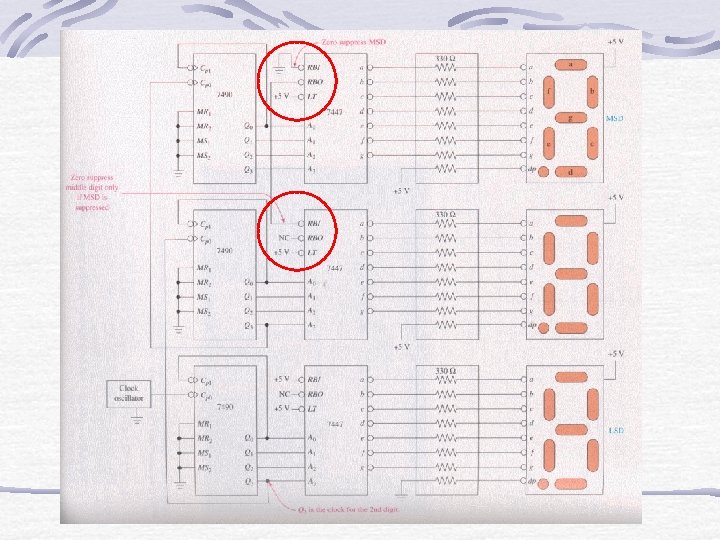

System Design Application – A 3 -digit decimal counter (000 – 999) When the count changes from (1001) to (0000), the 23 output line goes from HIGH to LOW and trigger the next counter.

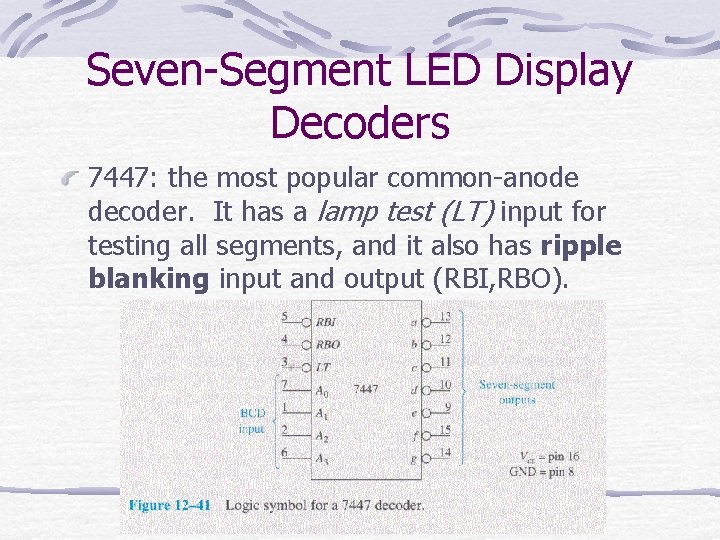

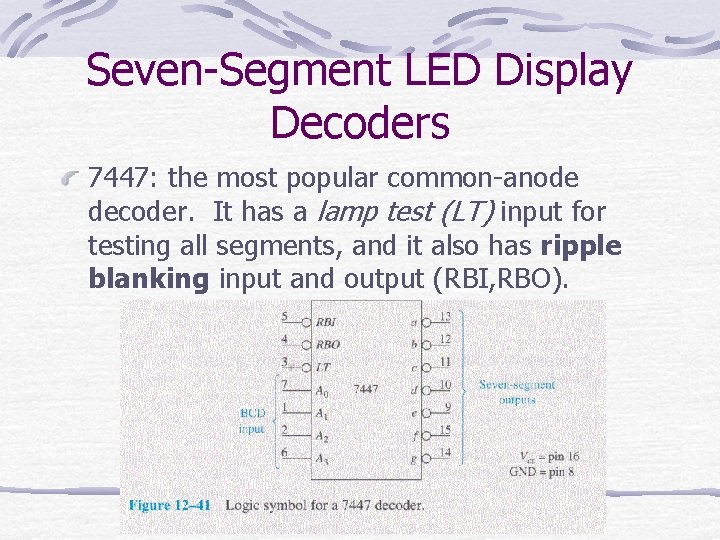

Seven-Segment LED Display Decoders 7447: the most popular common-anode decoder. It has a lamp test (LT) input for testing all segments, and it also has ripple blanking input and output (RBI, RBO).

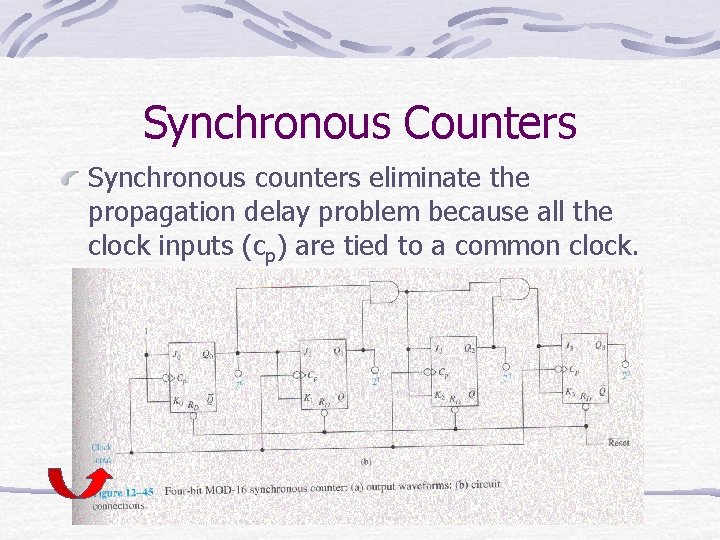

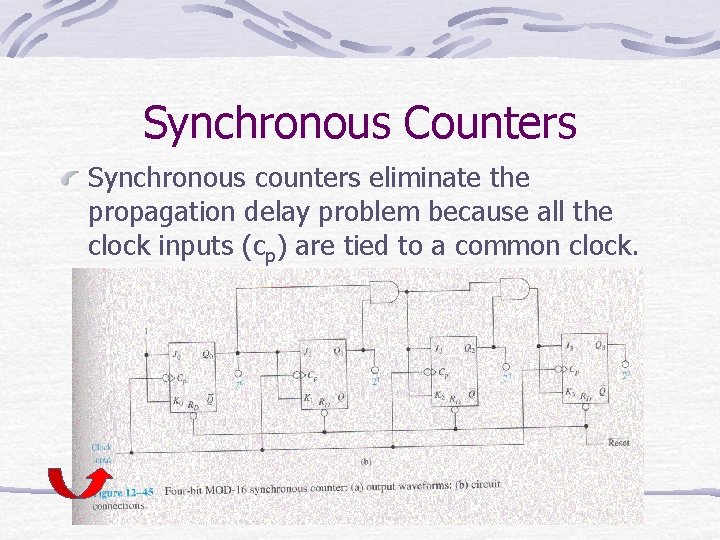

Synchronous Counters Synchronous counters eliminate the propagation delay problem because all the clock inputs (cp) are tied to a common clock.

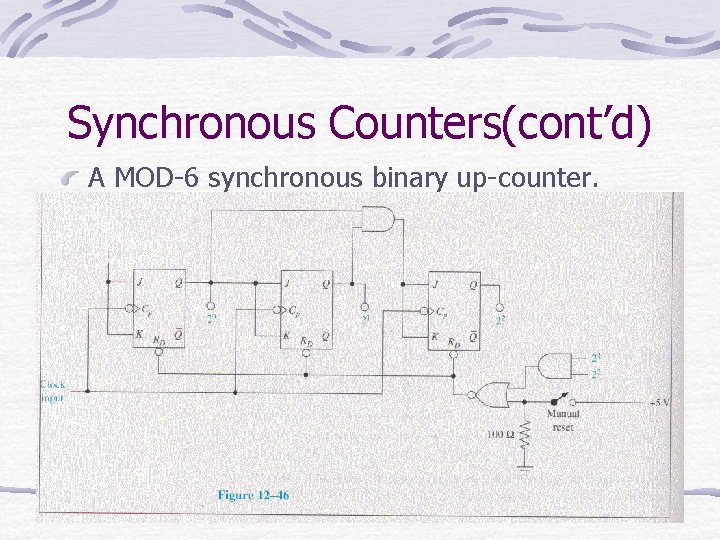

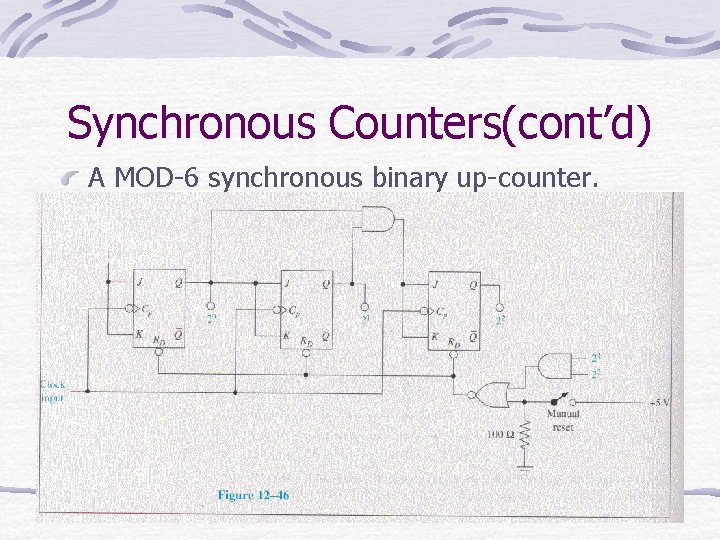

Synchronous Counters(cont’d) A MOD-6 synchronous binary up-counter.

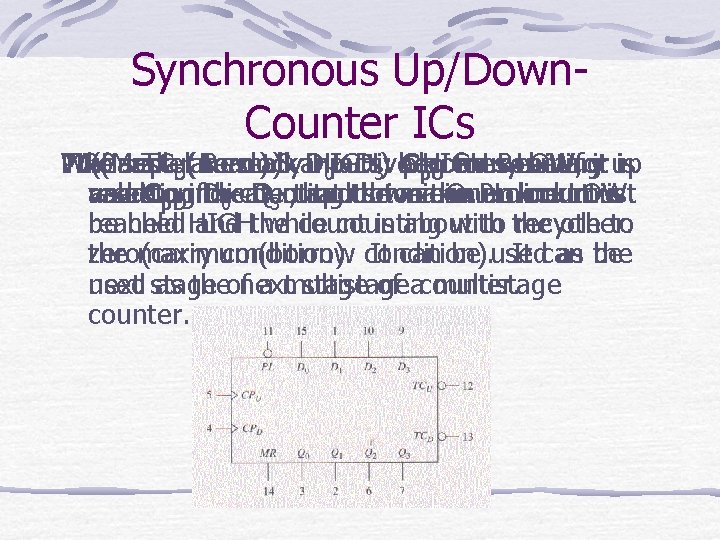

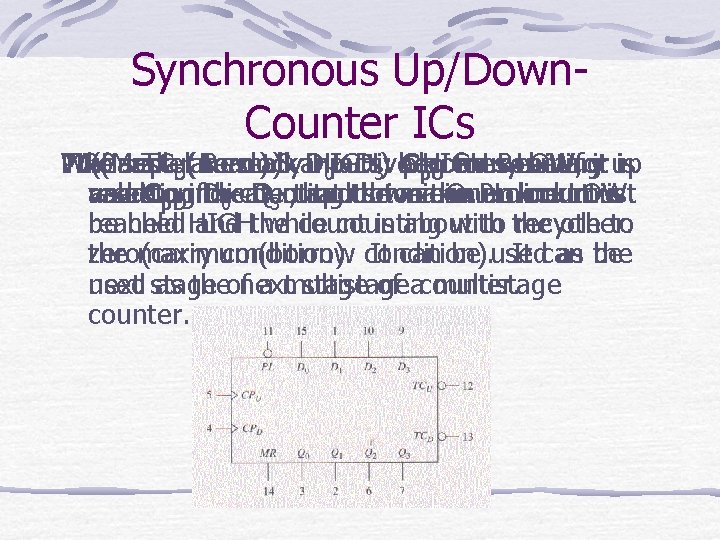

Synchronous Up/Down. Counter ICs PL(Parallel Two When separate TCDU(normally Load) clock & an D inputs: HIGH) C place any counting LOW, binary it up is MR(Master Reset): active-HIGH Reset for 0~D 3: becomes p. U for value and used Cto onindicate for D counting , that andthe down. drive maximum the One PLclock line count LOW. must isis resetting the Q 3 outputs tominimum zero. p. D 0~D be held HIGH reached and the while counting is about with to the recycle other. to zero(carry the maximum(borrow condition). It can be used It can as the be next stage used as theofnext a multistage of acounter. multistage counter.

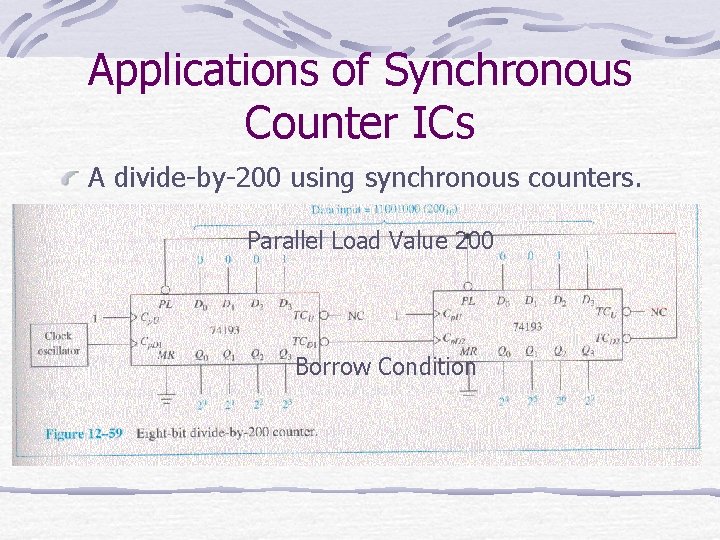

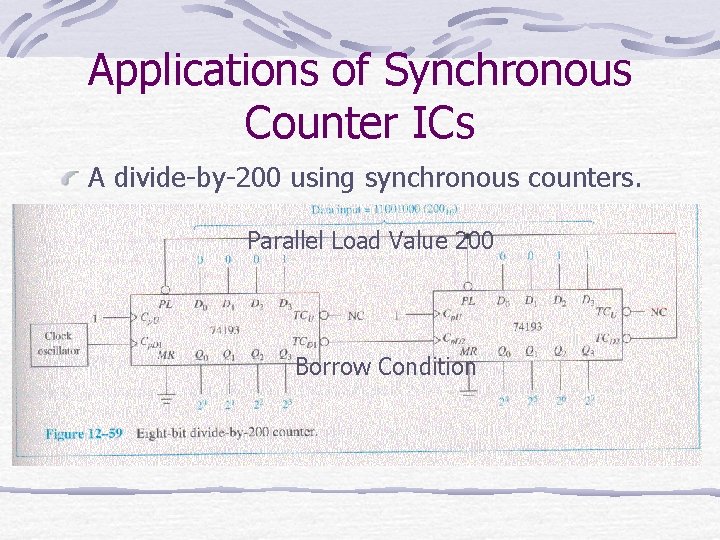

Applications of Synchronous Counter ICs A divide-by-200 using synchronous counters. Parallel Load Value 200 Borrow Condition