COTS for ondetector timing distribution Status report and

COTS for on-detector timing distribution. Status report and preliminary tests. A. Aloisio, R. Giordano University of Naples ‘Federico II’ and INFN aloisio@na. infn. it rgiordano@na. infn. it

Overview n n n n Ser. Des in the ETD framework COTS for the FCTS Testing the NSC DS 92 LV 18 Info from the foundry: layout, process, … Preparing for the rad tests Work in progress Conclusions Super. B Workshop - SLAC, Oct. 09 2

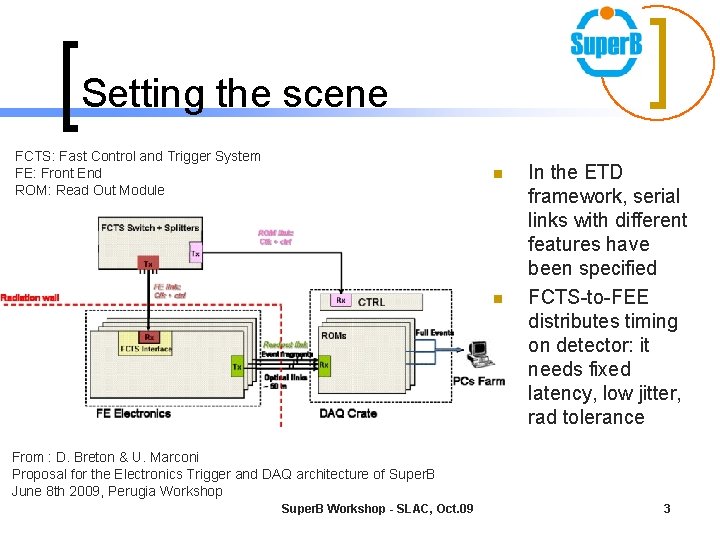

Setting the scene FCTS: Fast Control and Trigger System FE: Front End ROM: Read Out Module n n In the ETD framework, serial links with different features have been specified FCTS-to-FEE distributes timing on detector: it needs fixed latency, low jitter, rad tolerance From : D. Breton & U. Marconi Proposal for the Electronics Trigger and DAQ architecture of Super. B June 8 th 2009, Perugia Workshop Super. B Workshop - SLAC, Oct. 09 3

Why COTS ? n n Ser. Des embedded in SRAM FPGAs very likely can not be used Off-the-shelf components could be selected and qualified for rad-tolerance Glue-logic could go in anti-fuse FPGAs Alternatives: custom design, SLHC GBT project, …

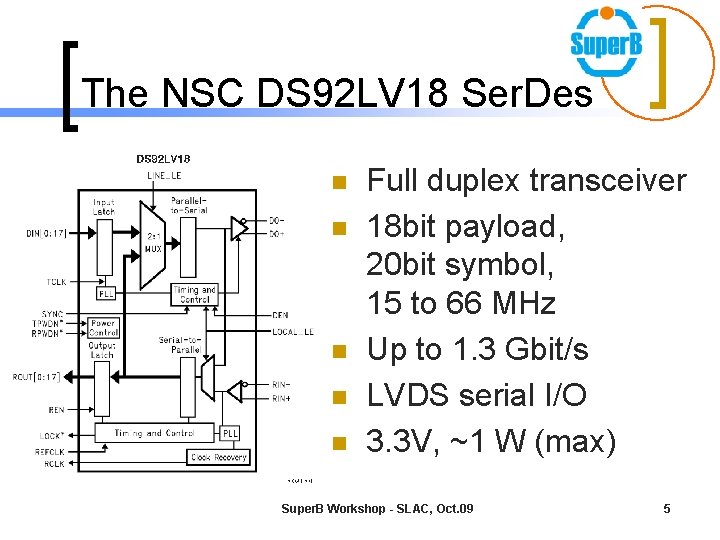

The NSC DS 92 LV 18 Ser. Des n n n Full duplex transceiver 18 bit payload, 20 bit symbol, 15 to 66 MHz Up to 1. 3 Gbit/s LVDS serial I/O 3. 3 V, ~1 W (max) Super. B Workshop - SLAC, Oct. 09 5

DS 92 LV 18 Plus/Minus n Plus n n n Simple protocol -> fixed latency 20 bit simbol, compatible with FPGA embedded transceivers Tolerant TX vs. RX clock frequency scheme 0. 25 um CMOS process already qualified (not the part) Cheap (<10€) Minus n n 1 Gbit/s range Encoding required externally

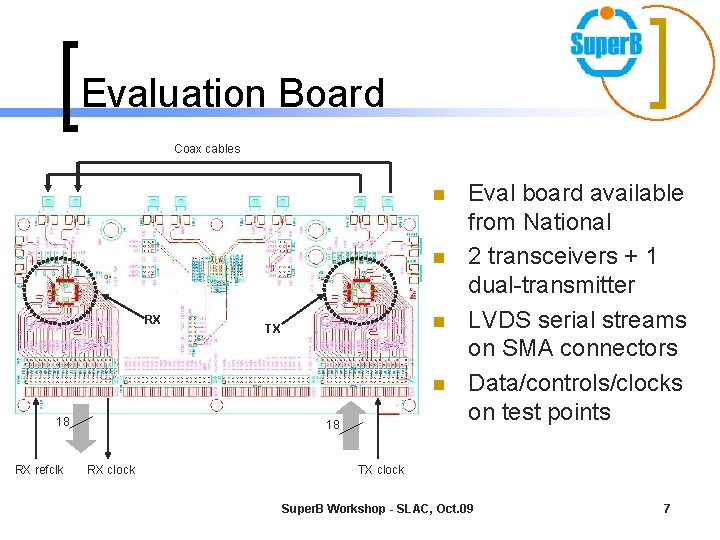

Evaluation Board Coax cables n n RX n TX n 18 RX refclk 18 RX clock Eval board available from National 2 transceivers + 1 dual-transmitter LVDS serial streams on SMA connectors Data/controls/clocks on test points TX clock Super. B Workshop - SLAC, Oct. 09 7

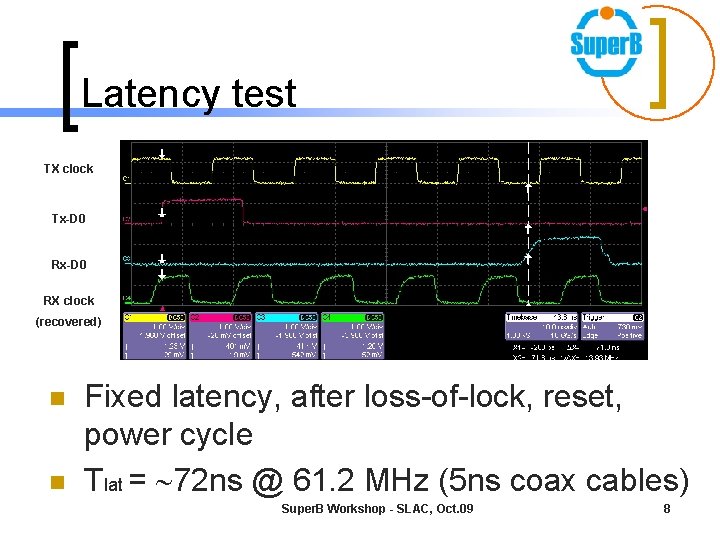

Latency test TX clock Tx-D 0 RX clock (recovered) n n Fixed latency, after loss-of-lock, reset, power cycle Tlat = 72 ns @ 61. 2 MHz (5 ns coax cables) Super. B Workshop - SLAC, Oct. 09 8

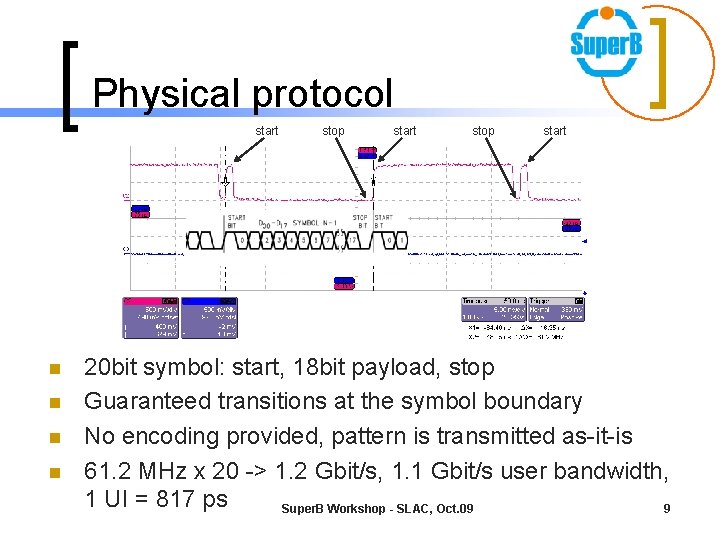

Physical protocol start n n stop start 20 bit symbol: start, 18 bit payload, stop Guaranteed transitions at the symbol boundary No encoding provided, pattern is transmitted as-it-is 61. 2 MHz x 20 -> 1. 2 Gbit/s, 1. 1 Gbit/s user bandwidth, 1 UI = 817 ps Super. B Workshop - SLAC, Oct. 09 9

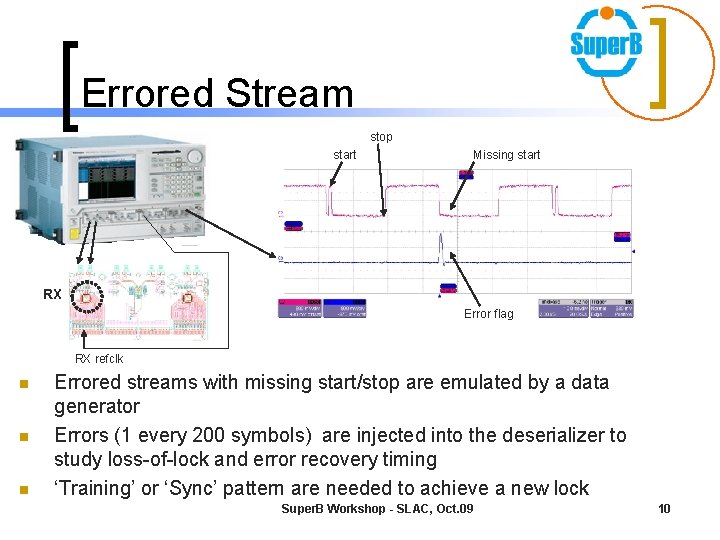

Errored Stream stop start Missing start RX Error flag RX refclk n n n Errored streams with missing start/stop are emulated by a data generator Errors (1 every 200 symbols) are injected into the deserializer to study loss-of-lock and error recovery timing ‘Training’ or ‘Sync’ pattern are needed to achieve a new lock Super. B Workshop - SLAC, Oct. 09 10

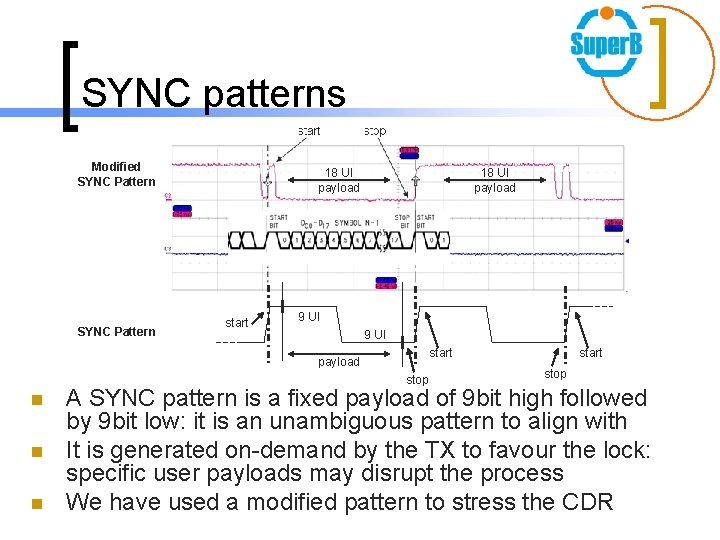

SYNC patterns Modified SYNC Pattern 18 UI payload start 18 UI payload 9 UI start payload stop n n n start stop A SYNC pattern is a fixed payload of 9 bit high followed by 9 bit low: it is an unambiguous pattern to align with It is generated on-demand by the TX to favour the lock: specific user payloads may disrupt the process We have used a modified pattern to stress the CDR

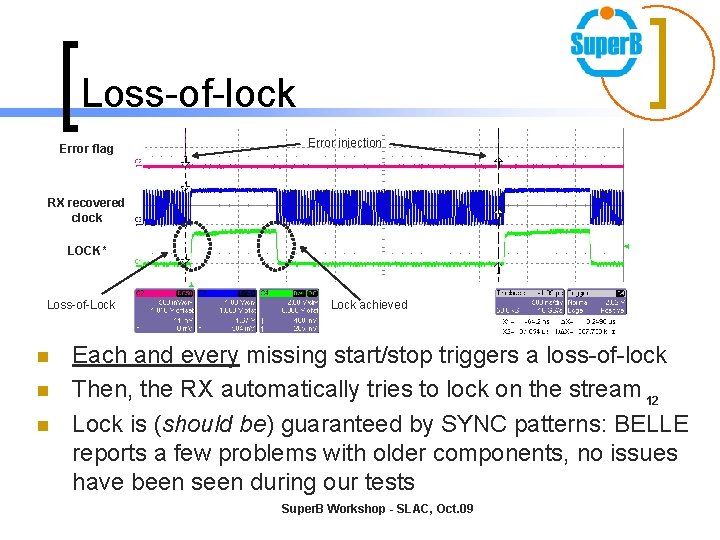

Loss-of-lock Error flag Error injection RX recovered clock LOCK* Loss-of-Lock n n n Lock achieved Each and every missing start/stop triggers a loss-of-lock Then, the RX automatically tries to lock on the stream 12 Lock is (should be) guaranteed by SYNC patterns: BELLE reports a few problems with older components, no issues have been seen during our tests Super. B Workshop - SLAC, Oct. 09

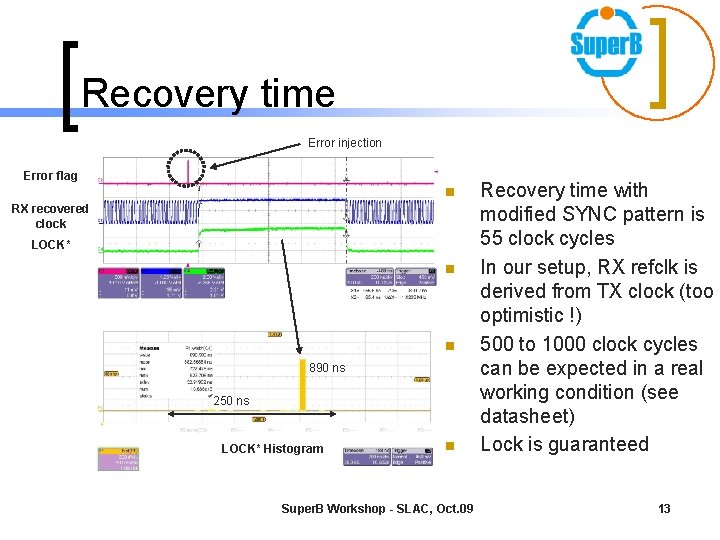

Recovery time Error injection Error flag n RX recovered clock LOCK* n n 890 ns 250 ns LOCK* Histogram n Super. B Workshop - SLAC, Oct. 09 Recovery time with modified SYNC pattern is 55 clock cycles In our setup, RX refclk is derived from TX clock (too optimistic !) 500 to 1000 clock cycles can be expected in a real working condition (see datasheet) Lock is guaranteed 13

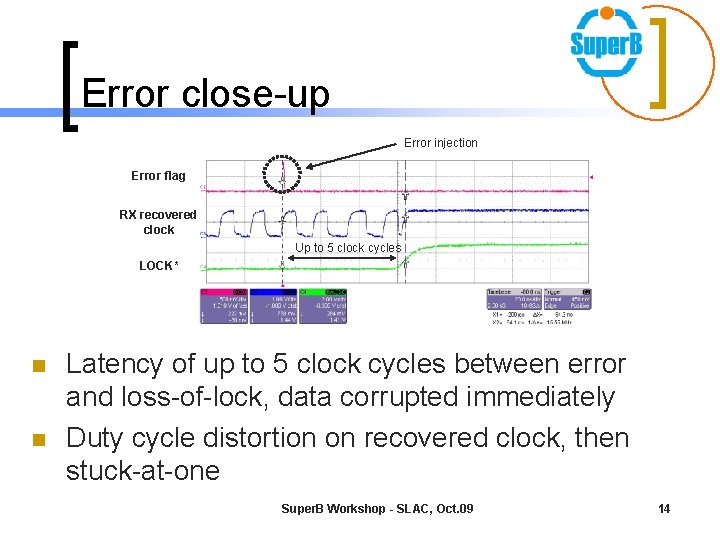

Error close-up Error injection Error flag RX recovered clock Up to 5 clock cycles LOCK* n n Latency of up to 5 clock cycles between error and loss-of-lock, data corrupted immediately Duty cycle distortion on recovered clock, then stuck-at-one Super. B Workshop - SLAC, Oct. 09 14

Process info n n CMOS 8 process, 250 nm same as DS 92 LV 1023, qualified by ATLAS, CMS No SEU/SEL performed up to now on DS 92 LV 18 (National, ESA, CERN, …) TID test passed up to 100 k. Rad (National) Super. B Workshop - SLAC, Oct. 09 15

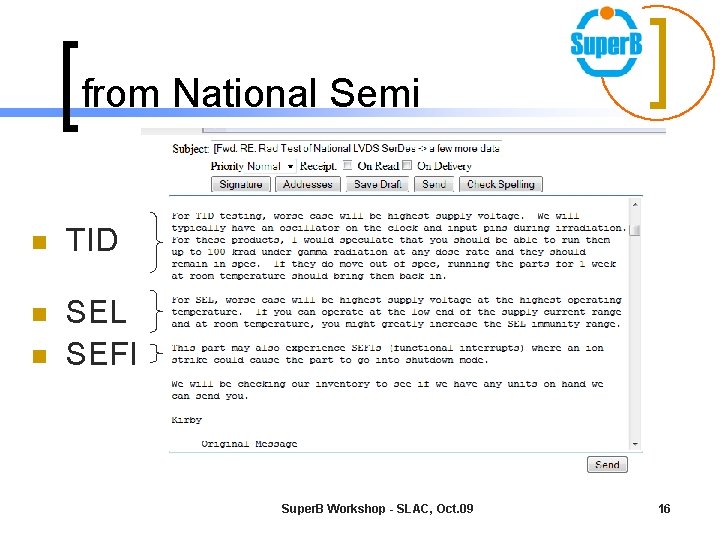

from National Semi n TID n SEL SEFI n Super. B Workshop - SLAC, Oct. 09 16

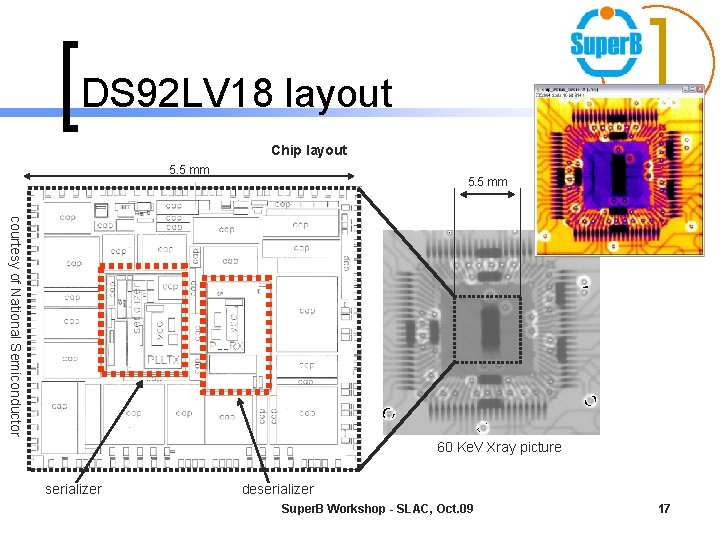

DS 92 LV 18 layout Chip layout 5. 5 mm courtesy of National Semiconductor 60 Ke. V Xray picture serializer deserializer Super. B Workshop - SLAC, Oct. 09 17

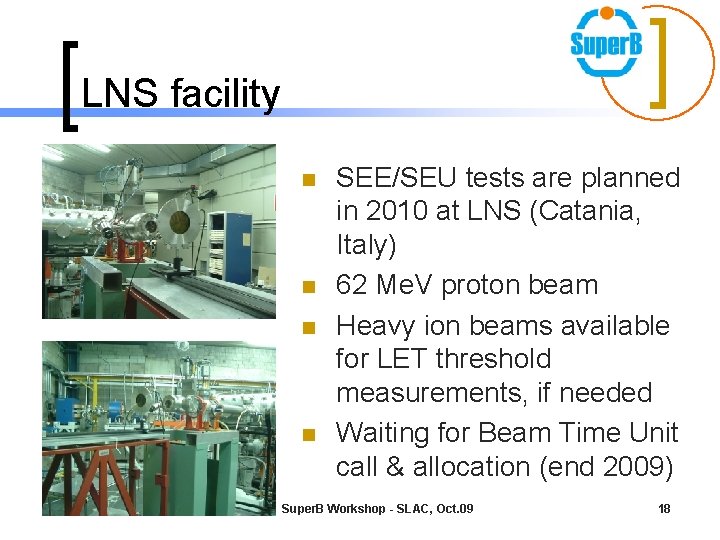

LNS facility n n SEE/SEU tests are planned in 2010 at LNS (Catania, Italy) 62 Me. V proton beam Heavy ion beams available for LET threshold measurements, if needed Waiting for Beam Time Unit call & allocation (end 2009) Super. B Workshop - SLAC, Oct. 09 18

Work in progress n DS 92 LV 18 n n Recovered clock jitter analysis Payload encoding scheme FPGA protocol emulation for hybrid links Rad Tests Super. B Workshop - SLAC, Oct. 09 19

Conclusions n n n DS 92 LV 18 is a candidate for on-detector FCTS implementation It shows fixed latency and it could also be considered for FEE-to-ROM links, depending upon the total bandwidth required Encoding/scrambling to be done externally for DC balance, possibly Error Detection/Correction in the payload Process already validated by ATLAS, CMS , not the part. Rad test at LNS in 2010, with 62 Me. V proton beam Super. B Workshop - SLAC, Oct. 09 20

Acknowledgement n n We wish to thank Kirby Kruckmeyer, Radiation Effects Engineering Manager, Hi-Rel Operations (National Semiconductor) for his suggestions and precious support We are also grateful to Giacomo Cuttone and his team at LNS for the support in preparing the rad test setup; to Paolo Russo and Giovanni Mettivier (Univ. of Naples and INFN) for the Xray analysis of the DS 92 LV 18

- Slides: 21