COTS Based High Performance Radar and EW Development

COTS Based High Performance Radar and EW Development Platform HPEC September 2011 Mikael Taveniku, XCube Gunnar Hillerstrom, Swedish Defence Research Agency 1/7/2022 XCube 2011 Page 1

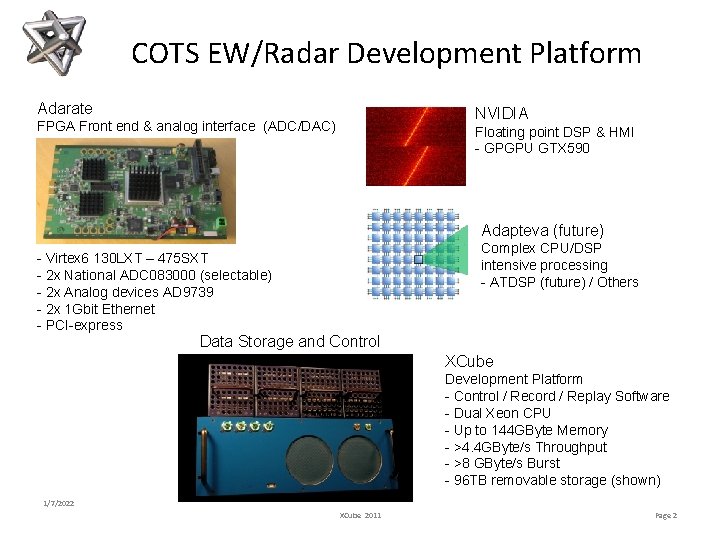

COTS EW/Radar Development Platform Adarate NVIDIA FPGA Front end & analog interface (ADC/DAC) Floating point DSP & HMI - GPGPU GTX 590 Adapteva (future) Complex CPU/DSP intensive processing - ATDSP (future) / Others - Virtex 6 130 LXT – 475 SXT - 2 x National ADC 083000 (selectable) - 2 x Analog devices AD 9739 - 2 x 1 Gbit Ethernet - PCI-express Data Storage and Control XCube Development Platform - Control / Record / Replay Software - Dual Xeon CPU - Up to 144 GByte Memory - >4. 4 GByte/s Throughput - >8 GByte/s Burst - 96 TB removable storage (shown) 1/7/2022 XCube 2011 Page 2

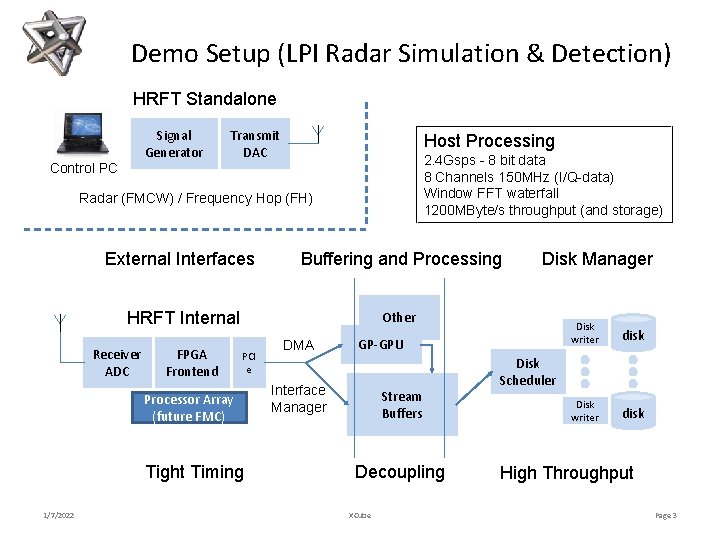

Demo Setup (LPI Radar Simulation & Detection) HRFT Standalone Signal Generator Control PC Transmit DAC Host Processing 2. 4 Gsps - 8 bit data 8 Channels 150 MHz (I/Q-data) Window FFT waterfall 1200 MByte/s throughput (and storage) Radar (FMCW) / Frequency Hop (FH) External Interfaces Buffering and Processing HRFT Internal Other Receiver ADC FPGA Frontend PCI e Processor Array (future FMC) Tight Timing 1/7/2022 DMA Disk Manager GP-GPU Interface Manager Stream Buffers Decoupling XCube Disk writer disk Disk Scheduler High Throughput Page 3

- Slides: 3