COSC 121 Computer Systems LC 3 IO Intro

- Slides: 33

COSC 121: Computer Systems: LC 3 I/O (Intro) Jeremy Bolton, Ph. D Assistant Teaching Professor Constructed using materials: - Patt and Patel Introduction to Computing Systems (2 nd) - Patterson and Hennessy Computer Organization and Design (4 th) **A special thanks to Rich Squier and Walid Najjar

Notes • Read PP. 8 – PP. 9 • Complete HW #4 • Project #1 Posted (in parts) – Supplemental files

Outline • Programming in Overview of – I/O in LC 3 • Keyboard • Monitor – Polling vs Interrupts – Operating System Intro

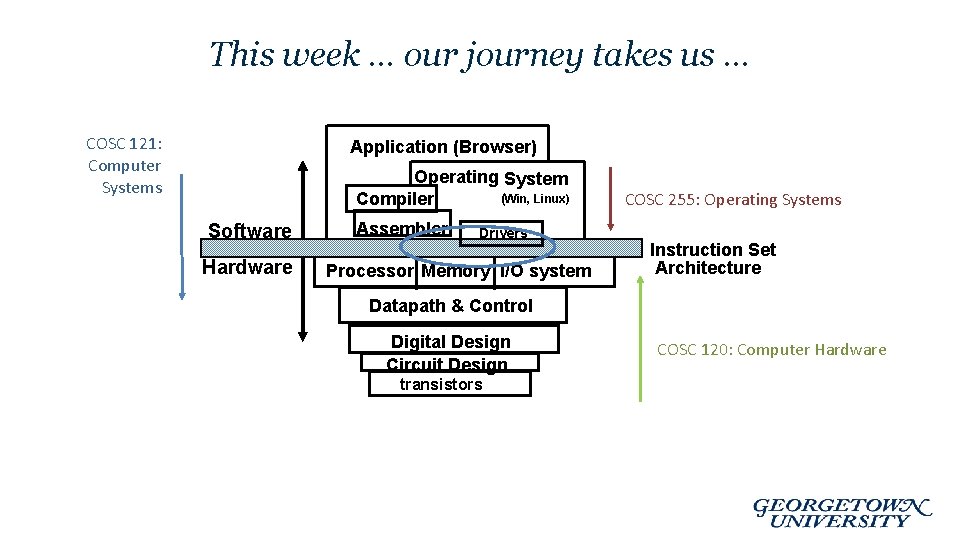

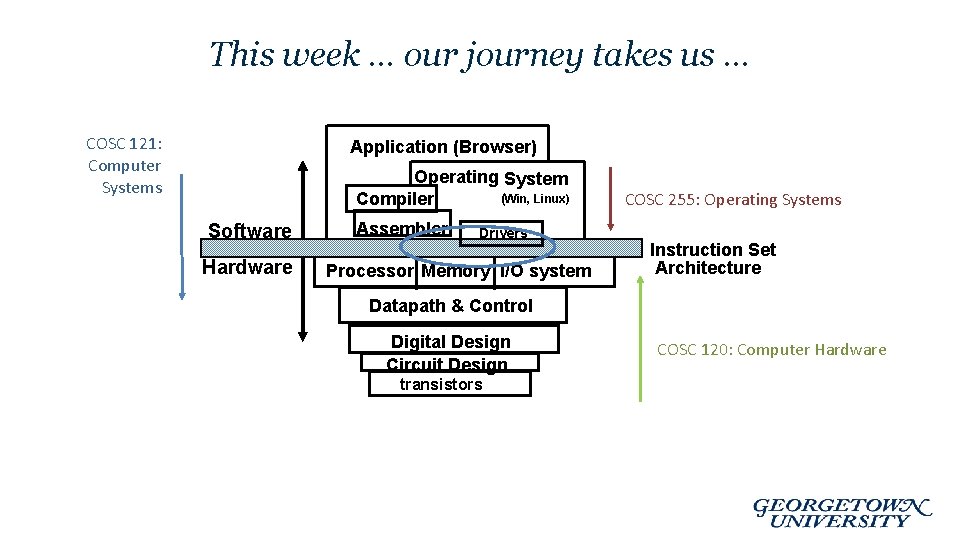

This week … our journey takes us … COSC 121: Computer Systems Application (Browser) Operating System (Win, Linux) Compiler Software Hardware Assembler Drivers Processor Memory I/O system COSC 255: Operating Systems Instruction Set Architecture Datapath & Control Digital Design Circuit Design transistors COSC 120: Computer Hardware

PP. 8 I/O

I/O: Connecting to Outside World • So far, we’ve learned how to: – compute with values in registers – load data from memory to registers – store data from registers to memory • But where does data in memory come from? • And how does data get out of the system so that humans can use it? 8 -6

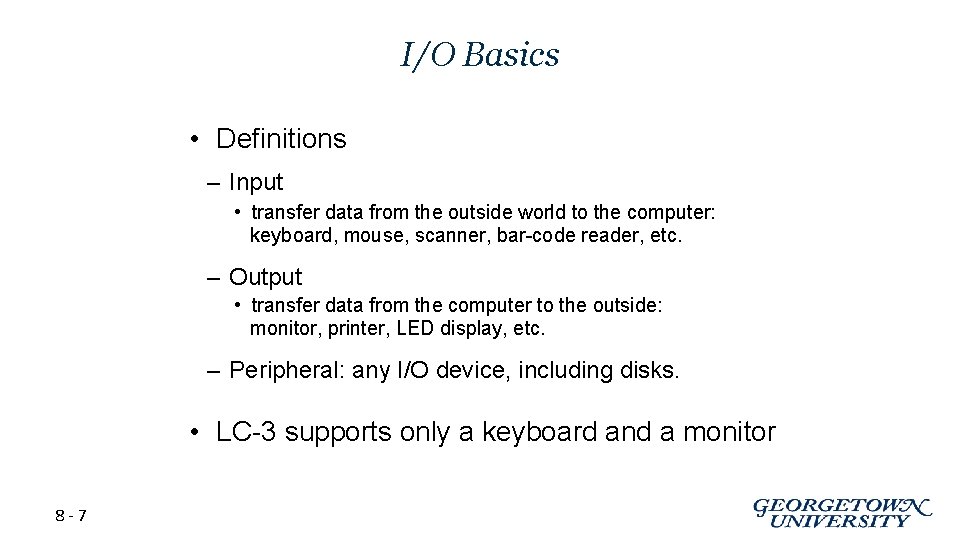

I/O Basics • Definitions – Input • transfer data from the outside world to the computer: keyboard, mouse, scanner, bar-code reader, etc. – Output • transfer data from the computer to the outside: monitor, printer, LED display, etc. – Peripheral: any I/O device, including disks. • LC-3 supports only a keyboard and a monitor 8 -7

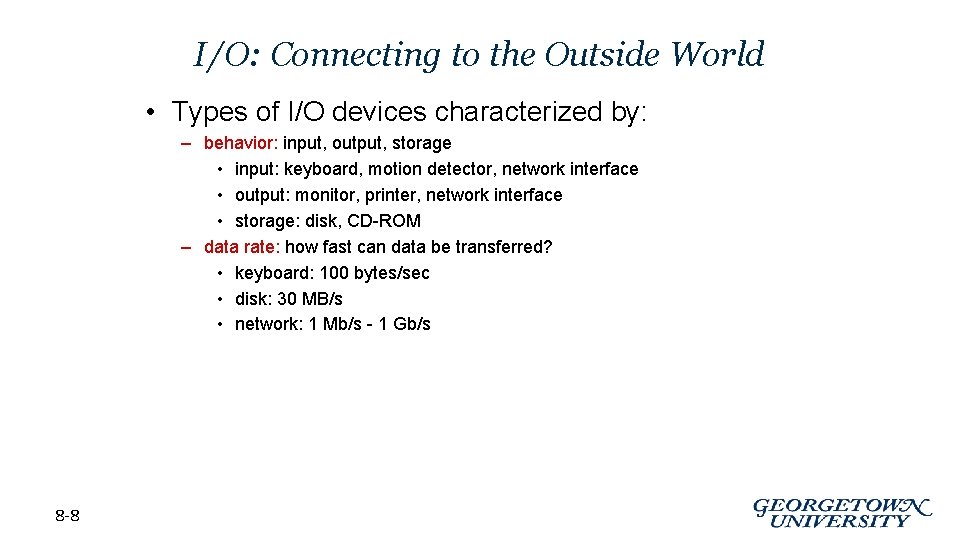

I/O: Connecting to the Outside World • Types of I/O devices characterized by: – behavior: input, output, storage • input: keyboard, motion detector, network interface • output: monitor, printer, network interface • storage: disk, CD-ROM – data rate: how fast can data be transferred? • keyboard: 100 bytes/sec • disk: 30 MB/s • network: 1 Mb/s - 1 Gb/s 8 -8

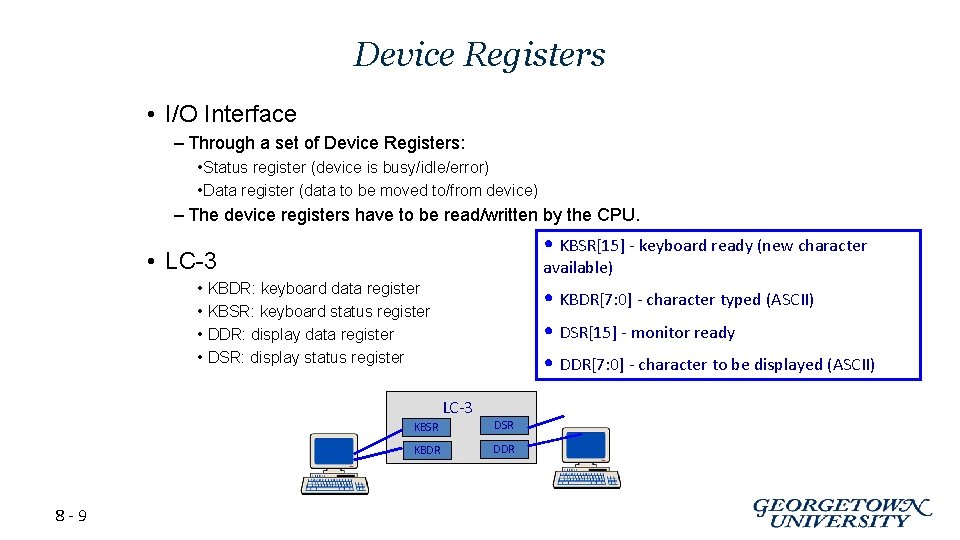

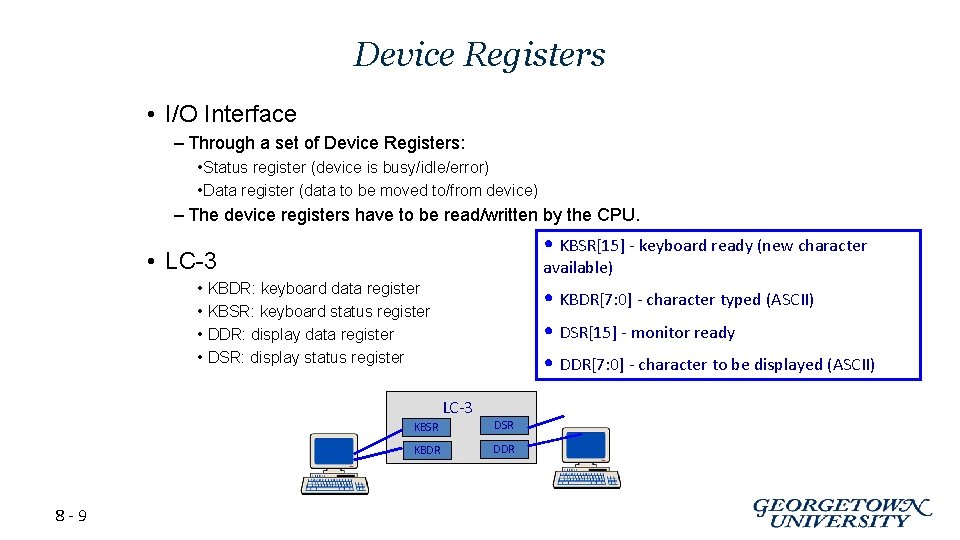

Device Registers • I/O Interface – Through a set of Device Registers: • Status register (device is busy/idle/error) • Data register (data to be moved to/from device) – The device registers have to be read/written by the CPU. • KBSR[15] - keyboard ready (new character • LC-3 available) • KBDR: keyboard data register • KBSR: keyboard status register • DDR: display data register • DSR: display status register • KBDR[7: 0] - character typed (ASCII) • DSR[15] - monitor ready • DDR[7: 0] - character to be displayed (ASCII) LC-3 8 -9 KBSR DSR KBDR DDR

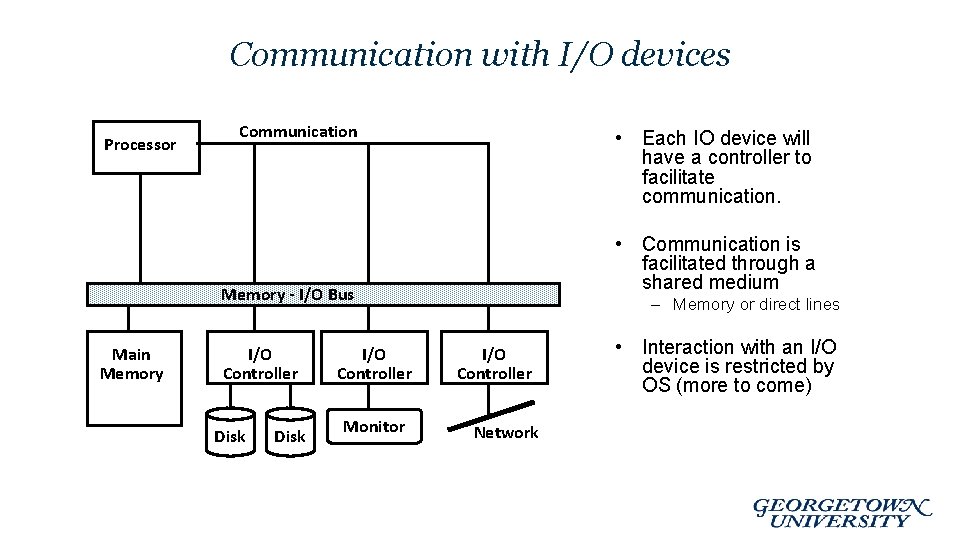

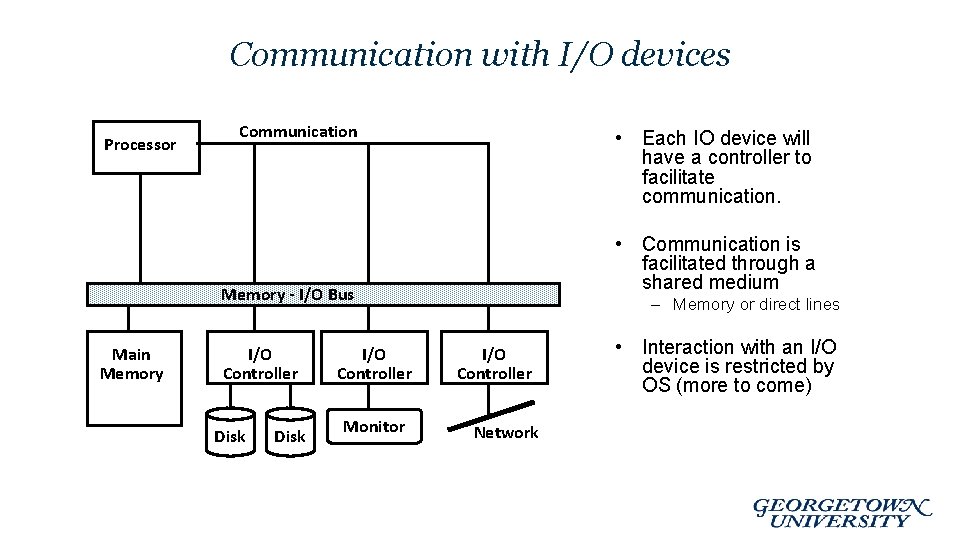

Communication with I/O devices Processor Communication • Each IO device will have a controller to facilitate communication. • Communication is facilitated through a shared medium Memory - I/O Bus Main Memory I/O Controller Disk I/O Controller Monitor – Memory or direct lines I/O Controller Network • Interaction with an I/O device is restricted by OS (more to come)

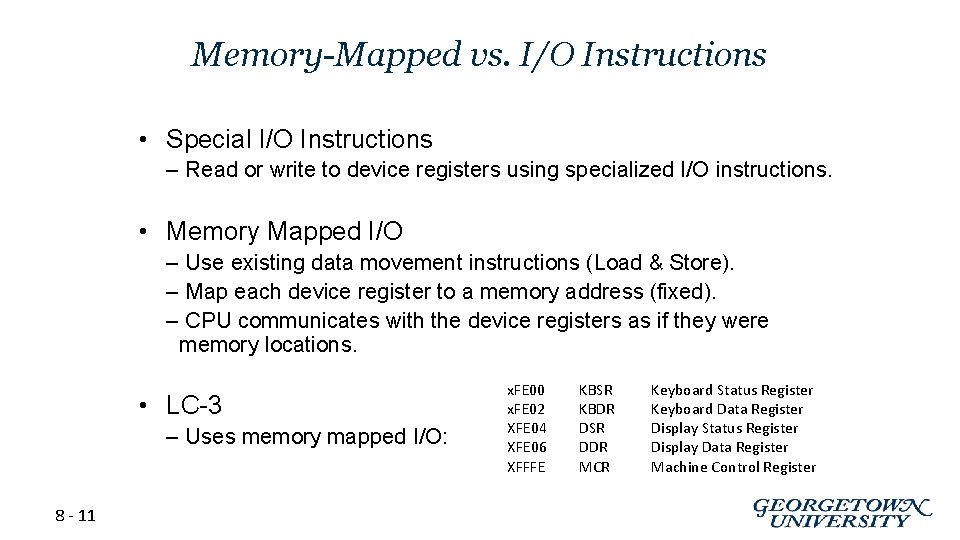

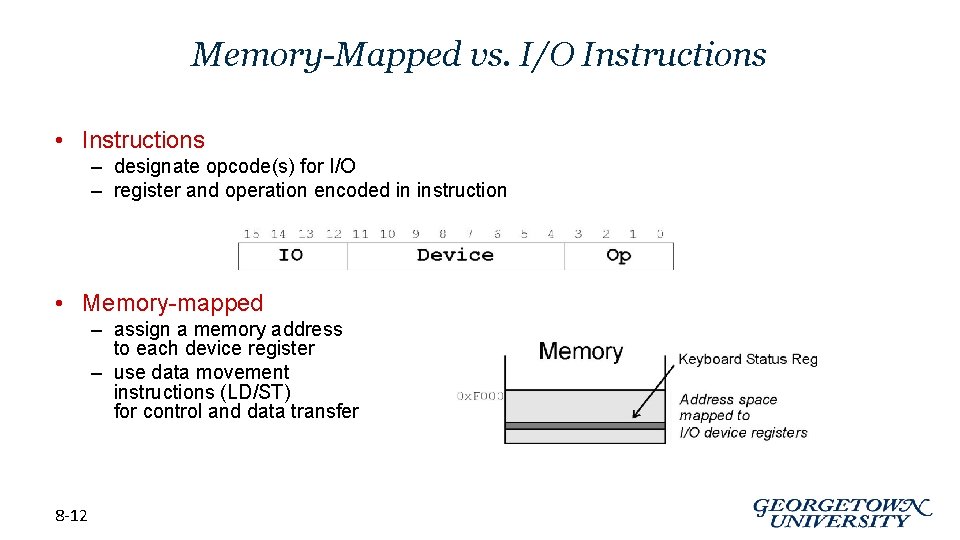

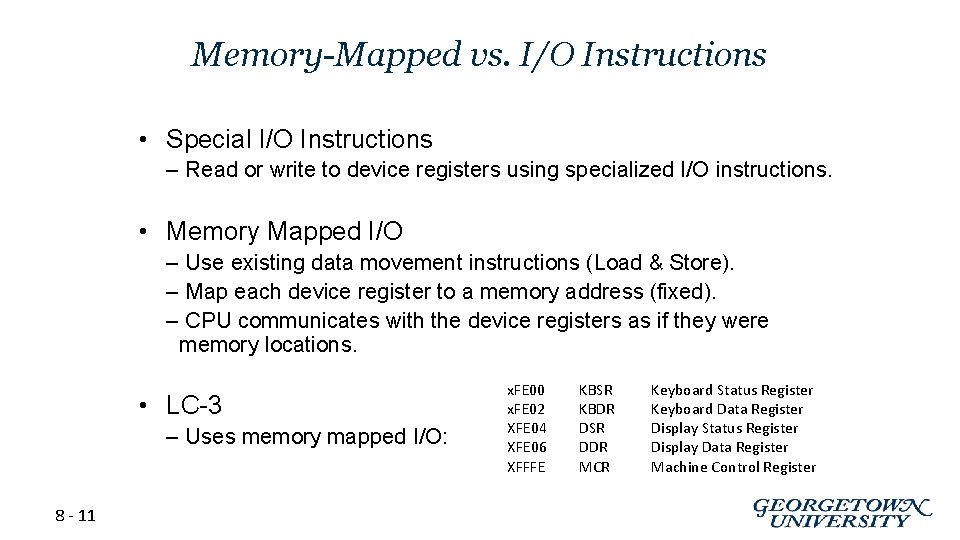

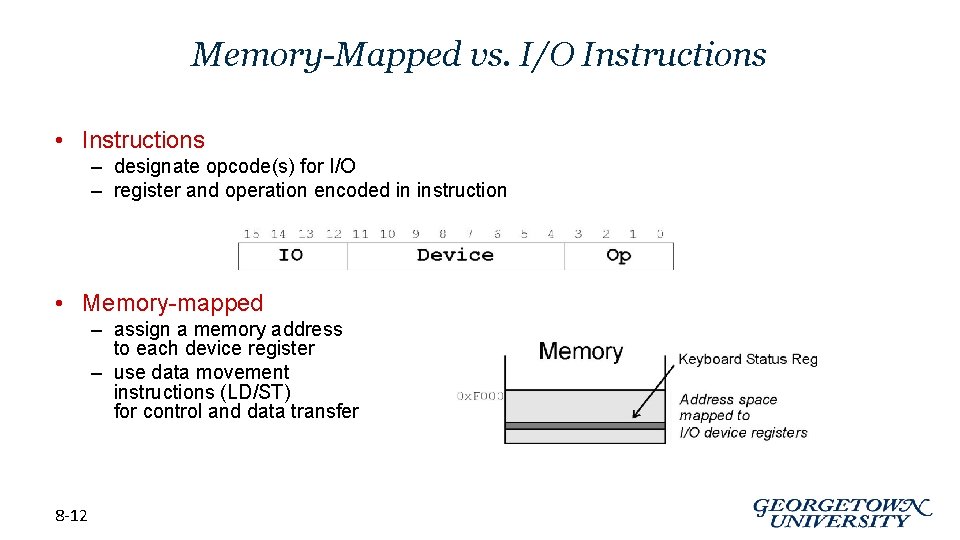

Memory-Mapped vs. I/O Instructions • Special I/O Instructions – Read or write to device registers using specialized I/O instructions. • Memory Mapped I/O – Use existing data movement instructions (Load & Store). – Map each device register to a memory address (fixed). – CPU communicates with the device registers as if they were memory locations. • LC-3 – Uses memory mapped I/O: 8 - 11 x. FE 00 x. FE 02 XFE 04 XFE 06 XFFFE KBSR KBDR DSR DDR MCR Keyboard Status Register Keyboard Data Register Display Status Register Display Data Register Machine Control Register

Memory-Mapped vs. I/O Instructions • Instructions – designate opcode(s) for I/O – register and operation encoded in instruction • Memory-mapped – assign a memory address to each device register – use data movement instructions (LD/ST) for control and data transfer 8 -12

Synchronizing CPU and I/O • Problem – Speed mismatch between CPU and I/O: • CPU runs at up to ~ 2 GHz, while all I/O is much slower. – Example : Keyboard input is both slow, and irregular. – We need a protocol to keep CPU & KBD synchronized. • Two possible solutions: – Polling (handshake synchronization) – Interrupt-driven I/O 8 - 13

Transfer Timing • I/O events generally happen much slower than CPU cycles. • Synchronous – data supplied at a fixed, predictable rate – CPU reads/writes every X cycles • Asynchronous – data rate less predictable – CPU must synchronize with device, so that it doesn’t miss data or write too quickly 8 -14

Transfer Control • Who determines when the next data transfer occurs? • Polling – CPU keeps checking status register until new data arrives OR device ready for next data – “Are we there yet? ” • Interrupts – Device sends a special signal to CPU when new data arrives OR device ready for next data – CPU can be performing other tasks instead of polling device. – “Wake me when we get there. ” 8 -15

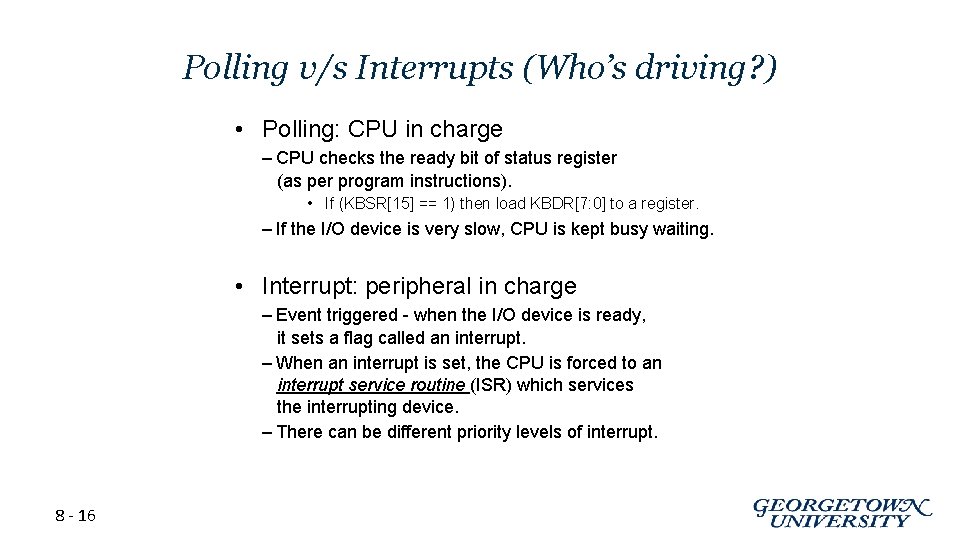

Polling v/s Interrupts (Who’s driving? ) • Polling: CPU in charge – CPU checks the ready bit of status register (as per program instructions). • If (KBSR[15] == 1) then load KBDR[7: 0] to a register. – If the I/O device is very slow, CPU is kept busy waiting. • Interrupt: peripheral in charge – Event triggered - when the I/O device is ready, it sets a flag called an interrupt. – When an interrupt is set, the CPU is forced to an interrupt service routine (ISR) which services the interrupting device. – There can be different priority levels of interrupt. 8 - 16

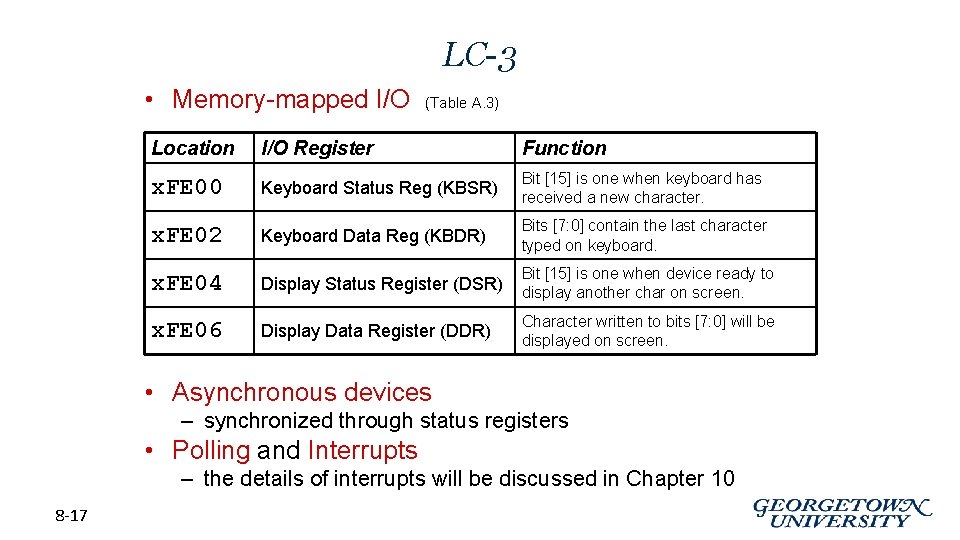

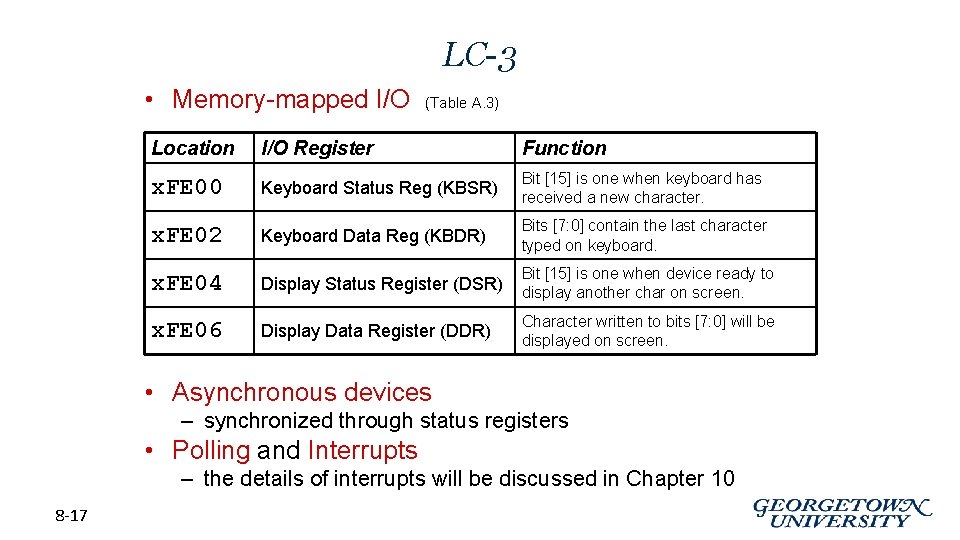

LC-3 • Memory-mapped I/O (Table A. 3) Location I/O Register Function x. FE 00 Keyboard Status Reg (KBSR) Bit [15] is one when keyboard has received a new character. x. FE 02 Keyboard Data Reg (KBDR) Bits [7: 0] contain the last character typed on keyboard. x. FE 04 Display Status Register (DSR) Bit [15] is one when device ready to display another char on screen. x. FE 06 Display Data Register (DDR) Character written to bits [7: 0] will be displayed on screen. • Asynchronous devices – synchronized through status registers • Polling and Interrupts – the details of interrupts will be discussed in Chapter 10 8 -17

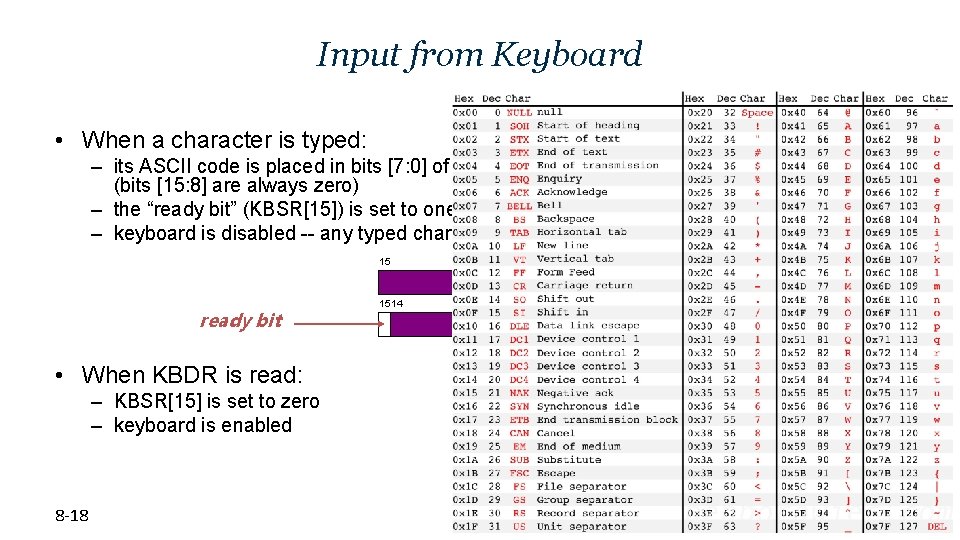

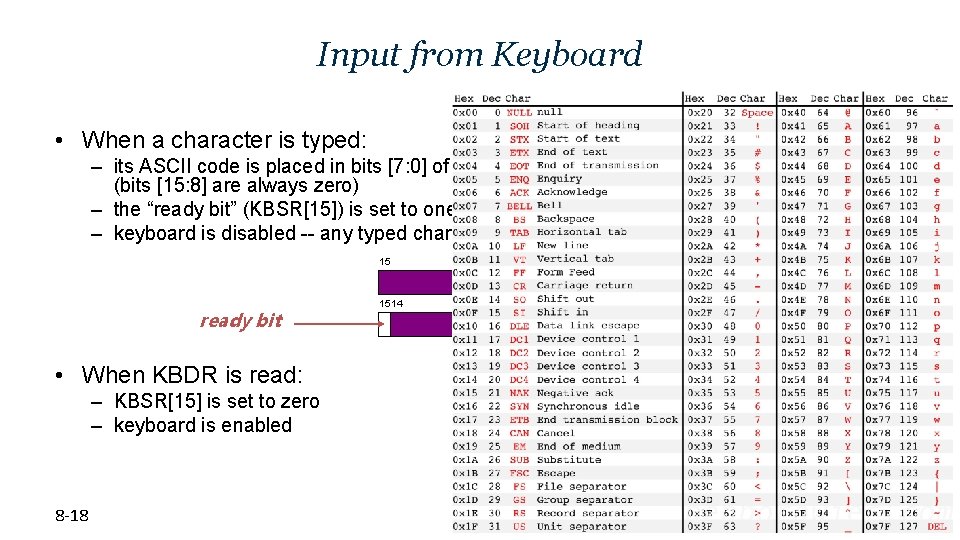

Input from Keyboard • When a character is typed: – its ASCII code is placed in bits [7: 0] of KBDR (bits [15: 8] are always zero) – the “ready bit” (KBSR[15]) is set to one – keyboard is disabled -- any typed characters will be ignored** keyboard data 15 8 7 0 KBDR ready bit • When KBDR is read: – KBSR[15] is set to zero – keyboard is enabled 8 -18 1514 0 KBSR

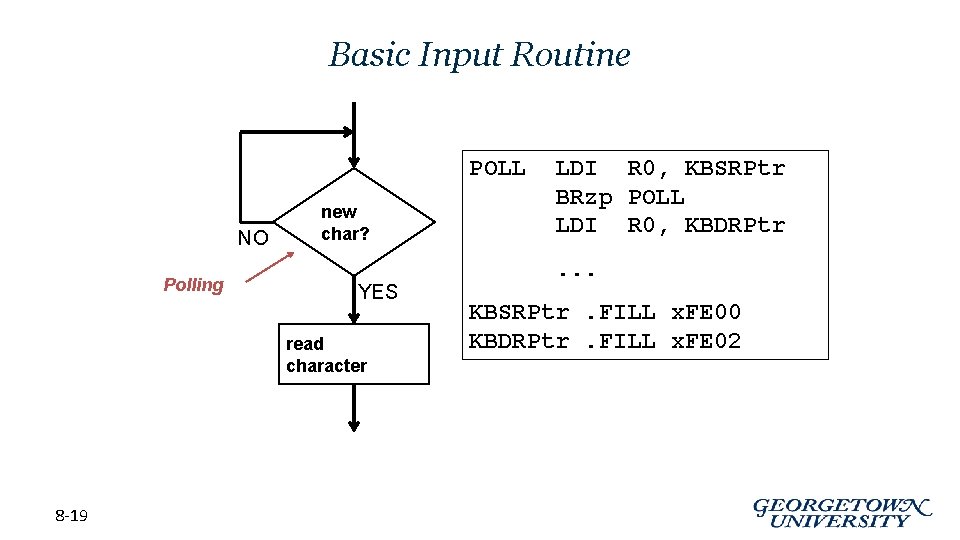

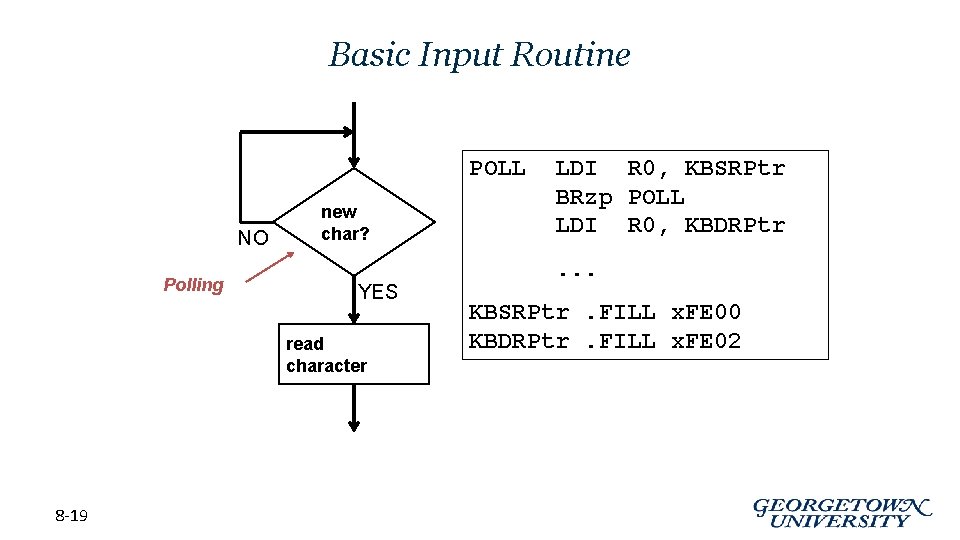

Basic Input Routine POLL NO Polling new char? YES read character 8 -19 LDI R 0, KBSRPtr BRzp POLL LDI R 0, KBDRPtr. . . KBSRPtr. FILL x. FE 00 KBDRPtr. FILL x. FE 02

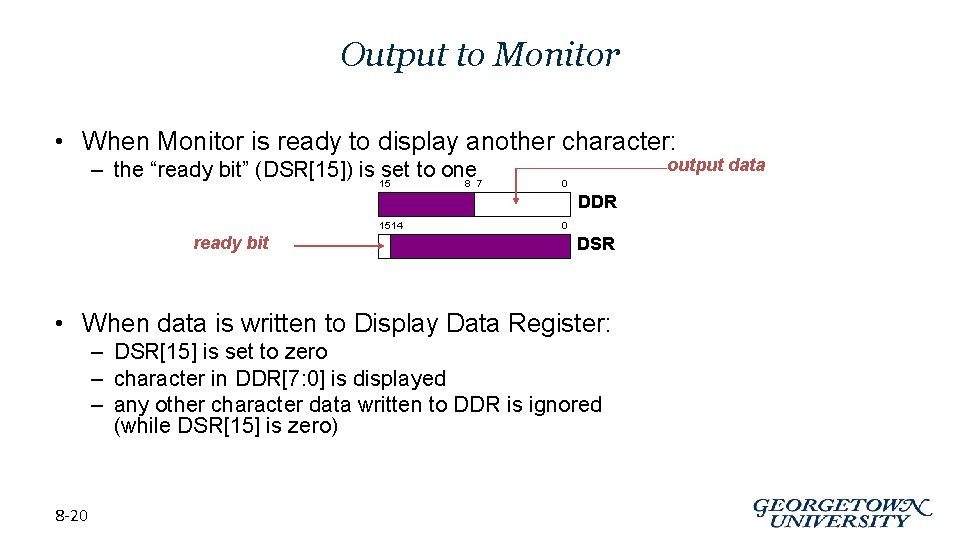

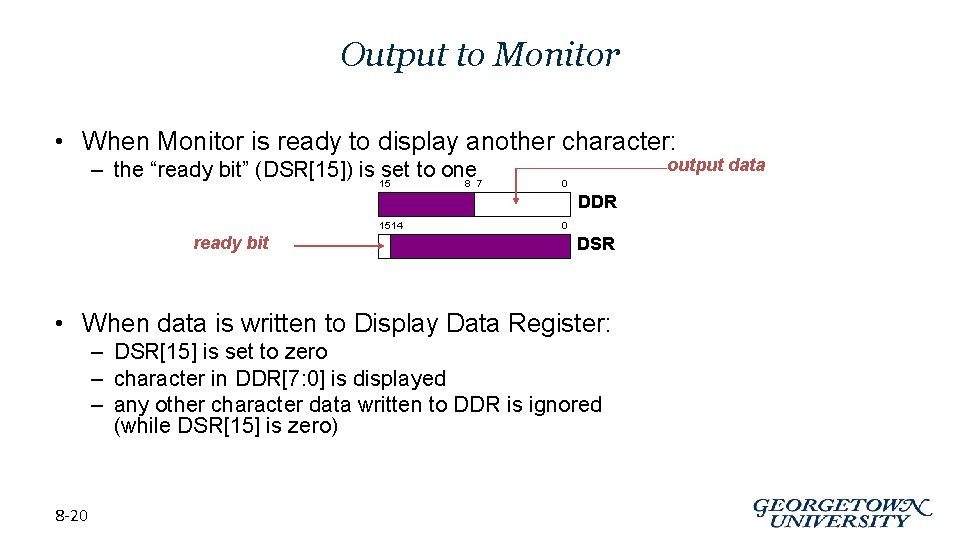

Output to Monitor • When Monitor is ready to display another character: – the “ready bit” (DSR[15]) is 15 set to one 8 7 output data 0 DDR 1514 ready bit 0 DSR • When data is written to Display Data Register: – DSR[15] is set to zero – character in DDR[7: 0] is displayed – any other character data written to DDR is ignored (while DSR[15] is zero) 8 -20

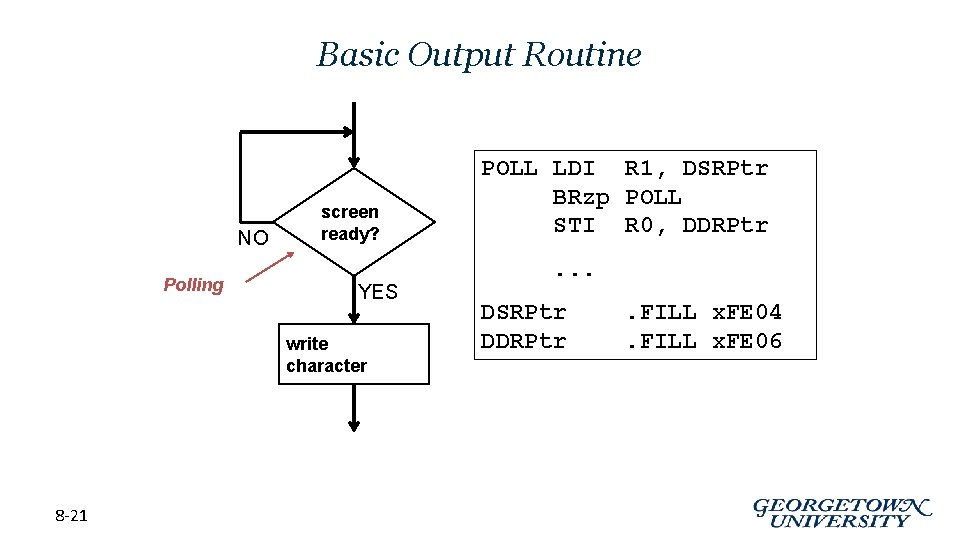

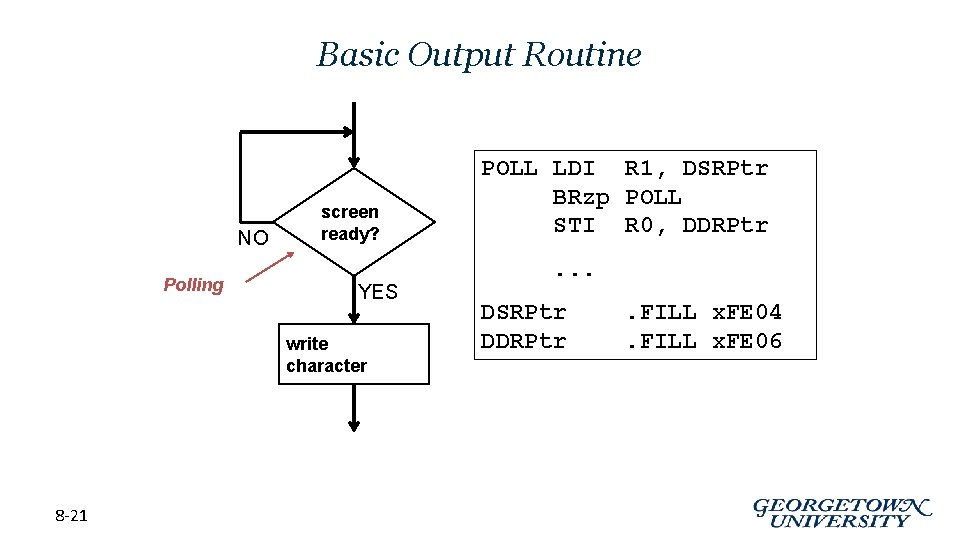

Basic Output Routine NO Polling screen ready? YES write character 8 -21 POLL LDI R 1, DSRPtr BRzp POLL STI R 0, DDRPtr. . . DSRPtr DDRPtr . FILL x. FE 04. FILL x. FE 06

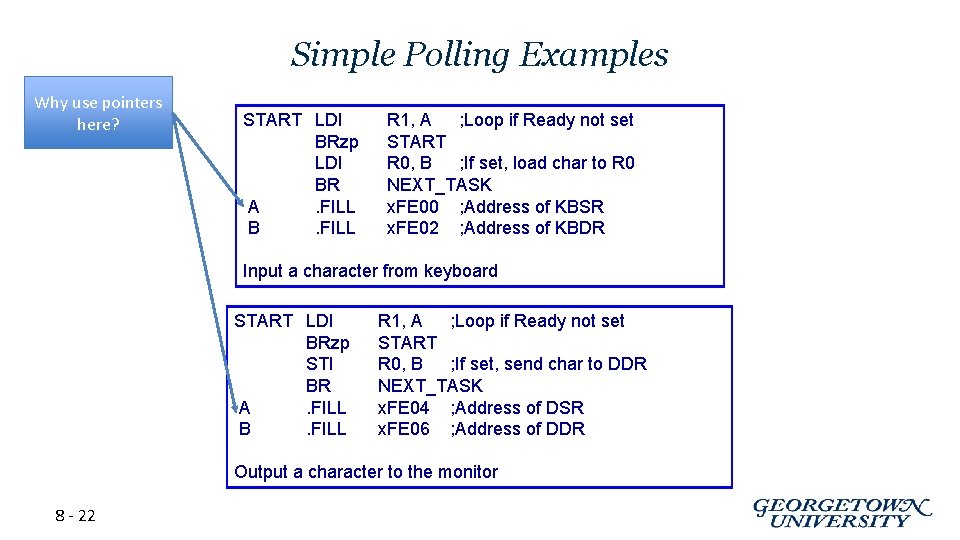

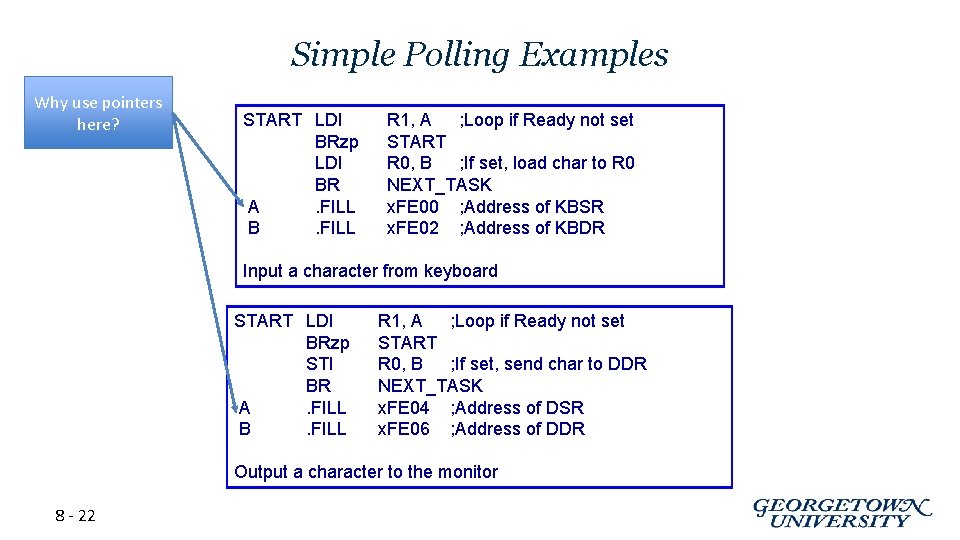

Simple Polling Examples Why use pointers here? START LDI BRzp LDI BR A. FILL B. FILL R 1, A ; Loop if Ready not set START R 0, B ; If set, load char to R 0 NEXT_TASK x. FE 00 ; Address of KBSR x. FE 02 ; Address of KBDR Input a character from keyboard START LDI BRzp STI BR A. FILL B. FILL R 1, A ; Loop if Ready not set START R 0, B ; If set, send char to DDR NEXT_TASK x. FE 04 ; Address of DSR x. FE 06 ; Address of DDR Output a character to the monitor 8 - 22

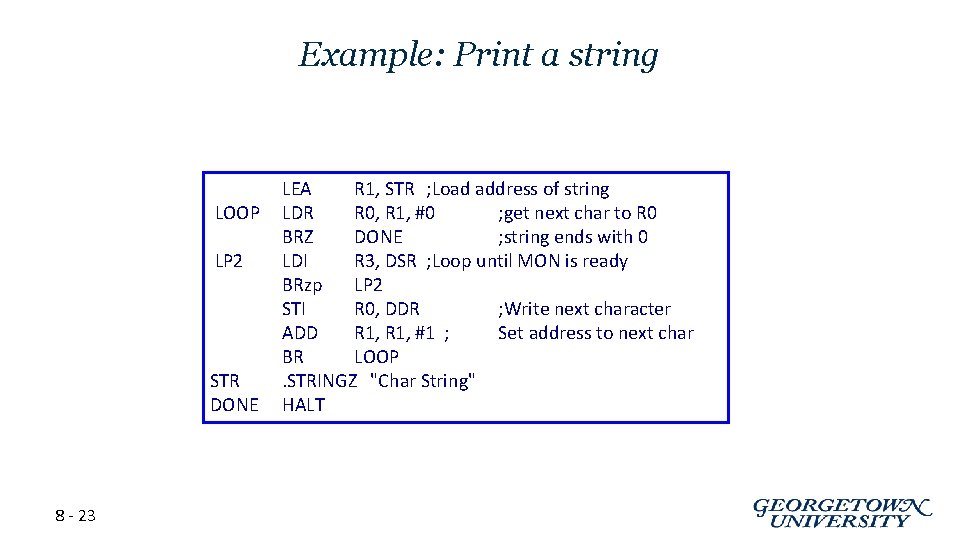

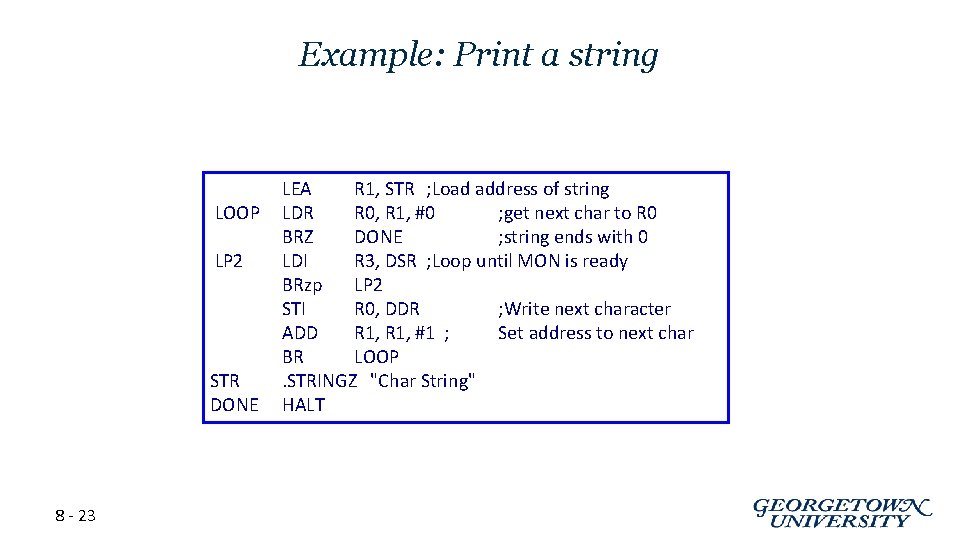

Example: Print a string LOOP LP 2 STR DONE 8 - 23 LEA R 1, STR ; Load address of string LDR R 0, R 1, #0 ; get next char to R 0 BRZ DONE ; string ends with 0 LDI R 3, DSR ; Loop until MON is ready BRzp LP 2 STI R 0, DDR ; Write next character ADD R 1, #1 ; Set address to next char BR LOOP. STRINGZ "Char String" HALT

Interrupt-driven I/O • Generating the interrupt signal – The I/O device must want to request service. – The device must have the right to request service, – This request must be more urgent than the processor’s current task. • Handling the interrupt signal – We will wait untile we understand stacks before getting to this. 8 - 24

Interrupt-Driven I/O • External device can: (1) Force currently executing program to stop; (2) Have the processor satisfy the device’s needs; and (3) Resume the stopped program as if nothing happened. • Why? – Polling consumes a lot of cycles, especially for rare events – these cycles can be used for more computation. – Example: Process previous input while collecting current input. (See Example 8. 1 in text. ) 8 -25

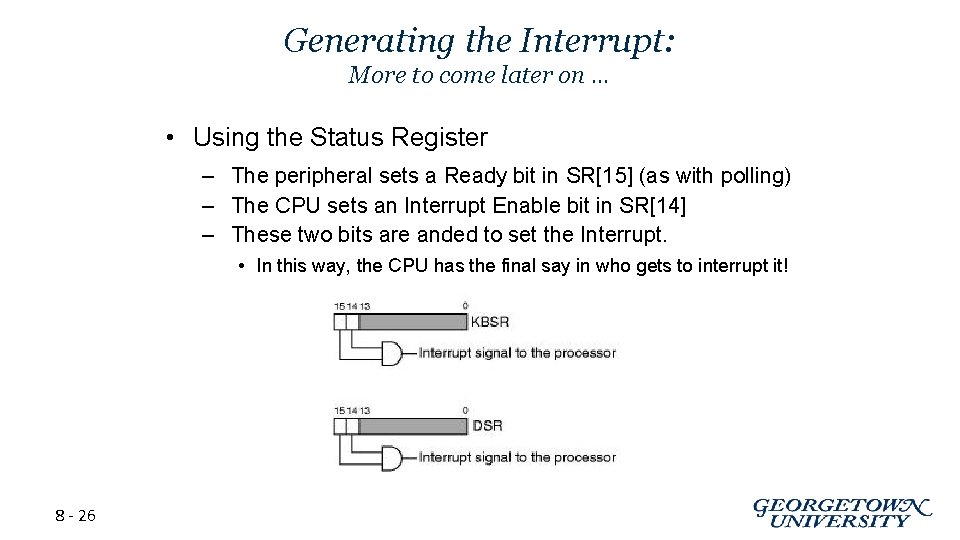

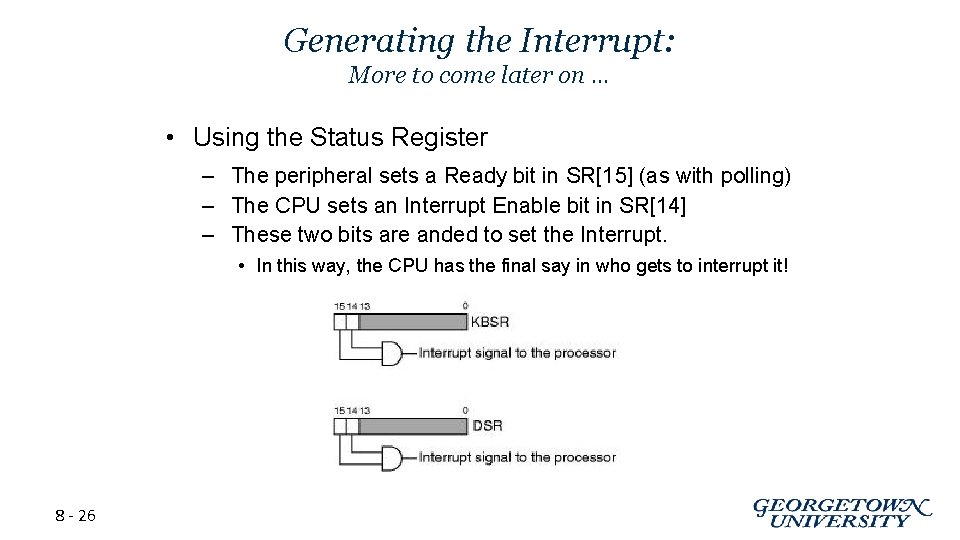

Generating the Interrupt: More to come later on … • Using the Status Register – The peripheral sets a Ready bit in SR[15] (as with polling) – The CPU sets an Interrupt Enable bit in SR[14] – These two bits are anded to set the Interrupt. • In this way, the CPU has the final say in who gets to interrupt it! 8 - 26

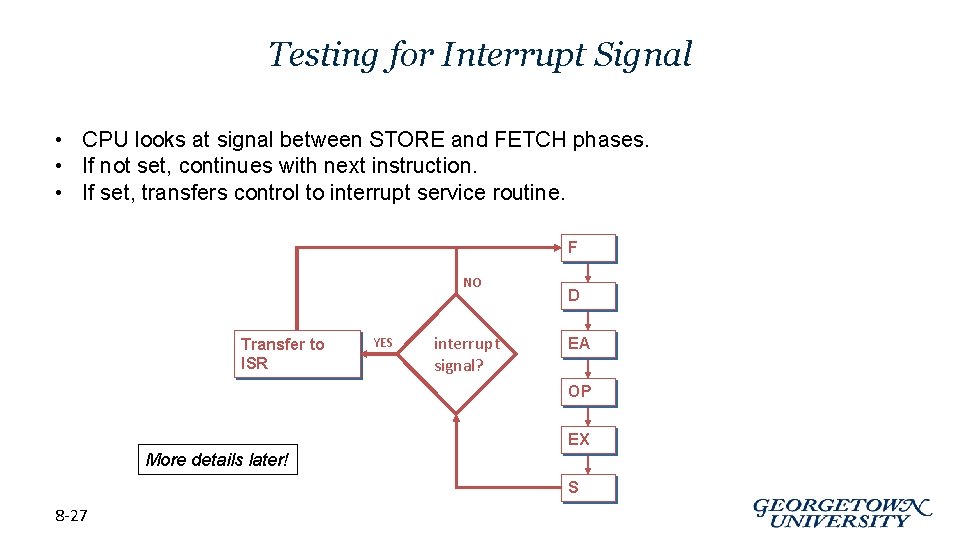

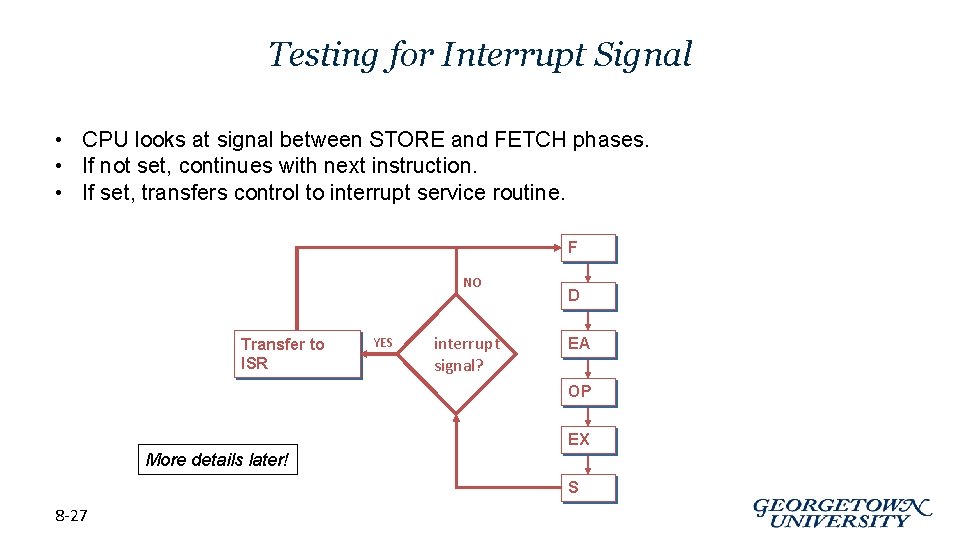

Testing for Interrupt Signal • CPU looks at signal between STORE and FETCH phases. • If not set, continues with next instruction. • If set, transfers control to interrupt service routine. F NO Transfer to ISR YES interrupt signal? D EA OP EX More details later! S 8 -27

Appendix: Jeremy Bolton, Ph. D Assistant Teaching Professor Constructed using materials: - Patt and Patel Introduction to Computing Systems (2 nd) - Patterson and Hennessy Computer Organization and Design (4 th) **A special thanks to Rich Squier and Walid Najjar

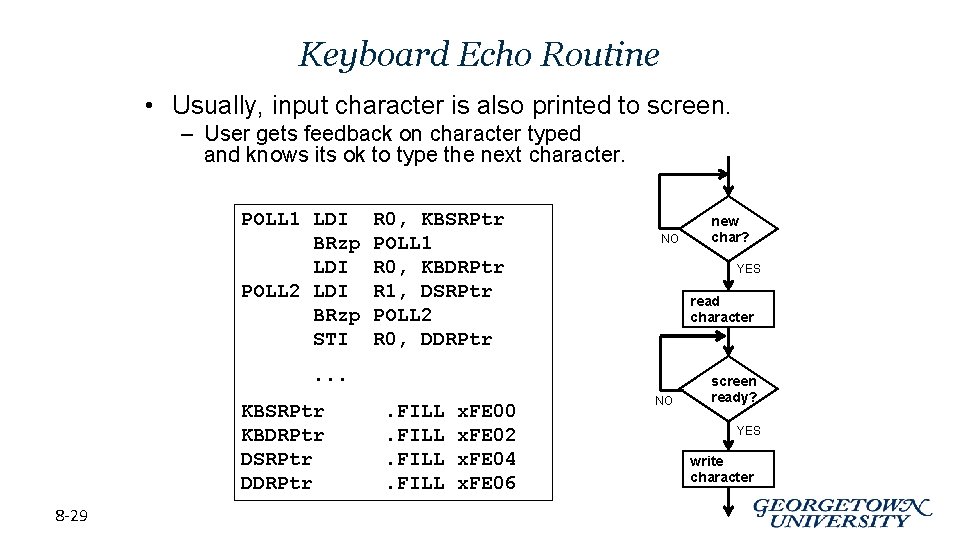

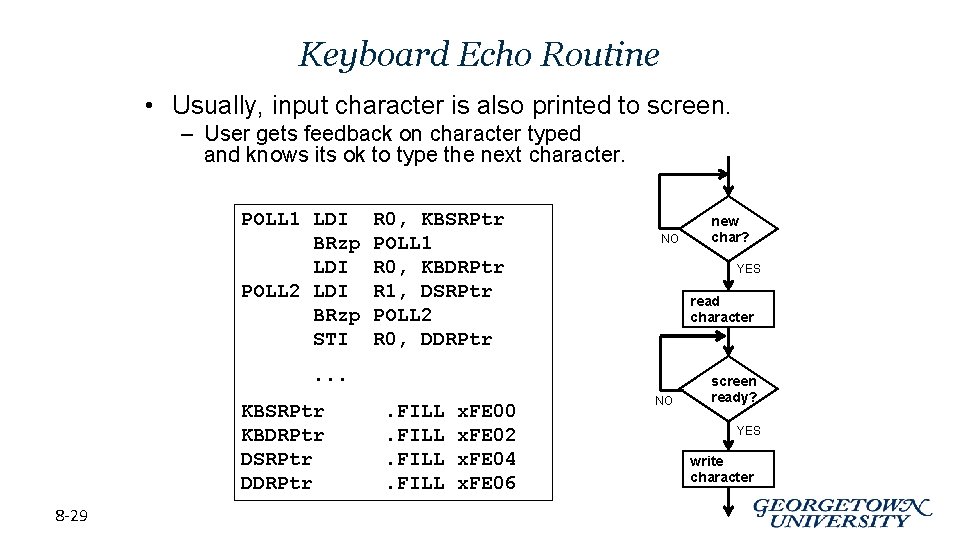

Keyboard Echo Routine • Usually, input character is also printed to screen. – User gets feedback on character typed and knows its ok to type the next character. POLL 1 LDI BRzp LDI POLL 2 LDI BRzp STI R 0, KBSRPtr POLL 1 R 0, KBDRPtr R 1, DSRPtr POLL 2 R 0, DDRPtr NO YES read character . . . KBSRPtr KBDRPtr DSRPtr DDRPtr 8 -29 . FILL x. FE 00 x. FE 02 x. FE 04 x. FE 06 new char? NO screen ready? YES write character

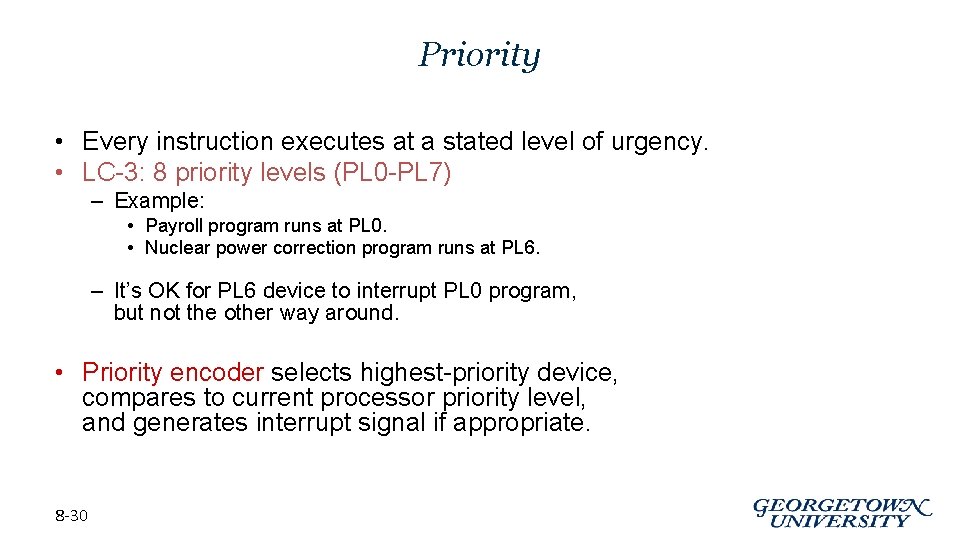

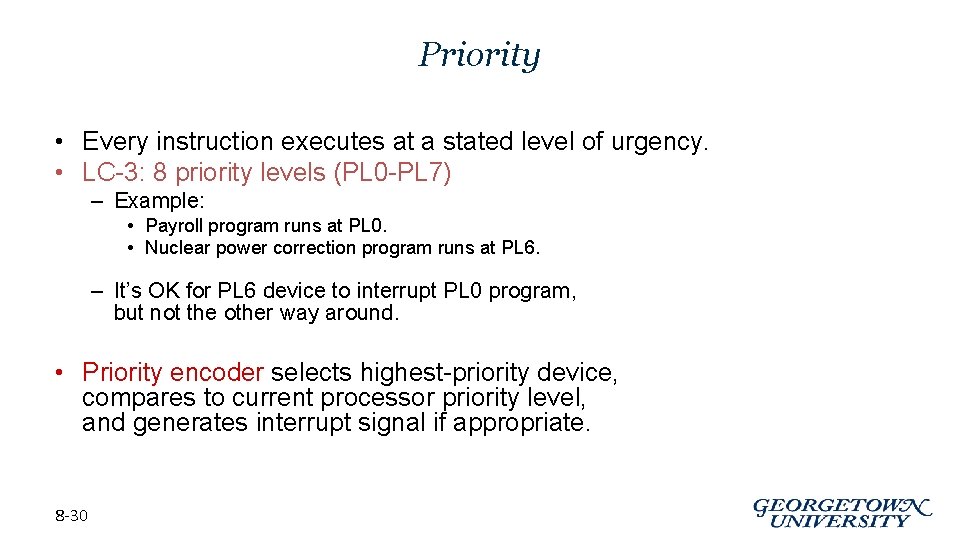

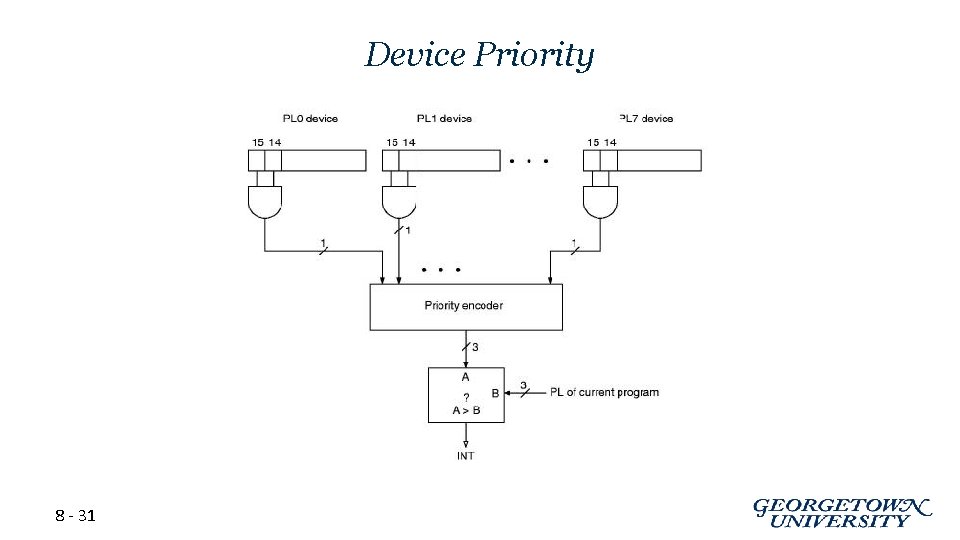

Priority • Every instruction executes at a stated level of urgency. • LC-3: 8 priority levels (PL 0 -PL 7) – Example: • Payroll program runs at PL 0. • Nuclear power correction program runs at PL 6. – It’s OK for PL 6 device to interrupt PL 0 program, but not the other way around. • Priority encoder selects highest-priority device, compares to current processor priority level, and generates interrupt signal if appropriate. 8 -30

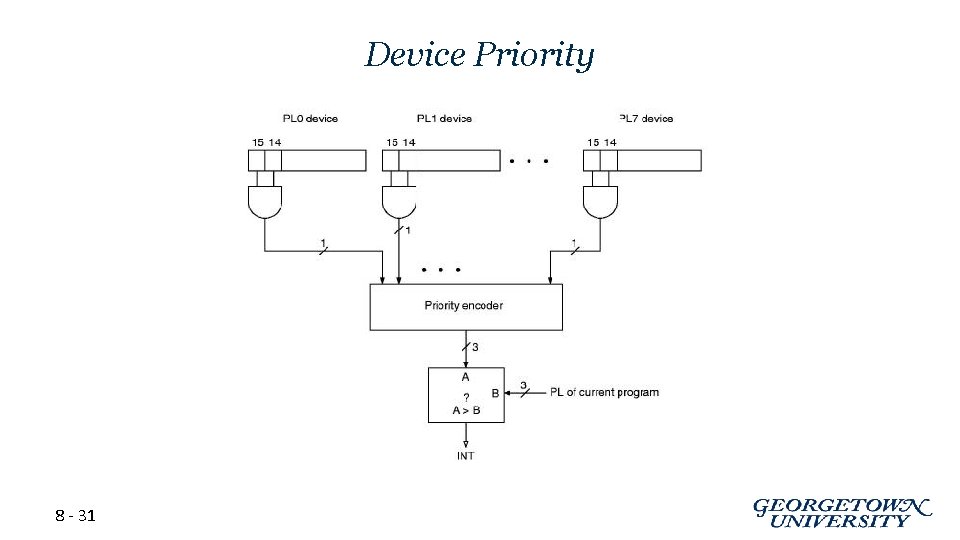

Device Priority 8 - 31

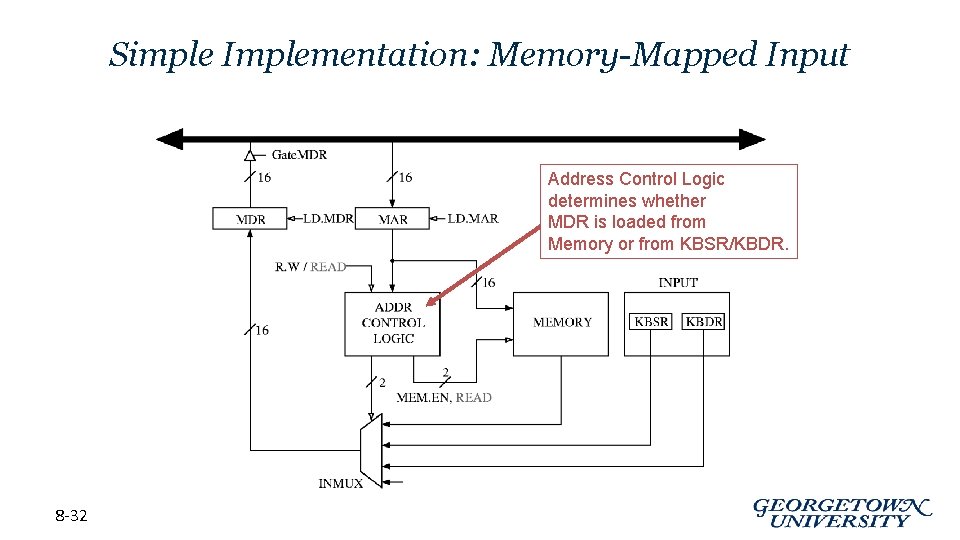

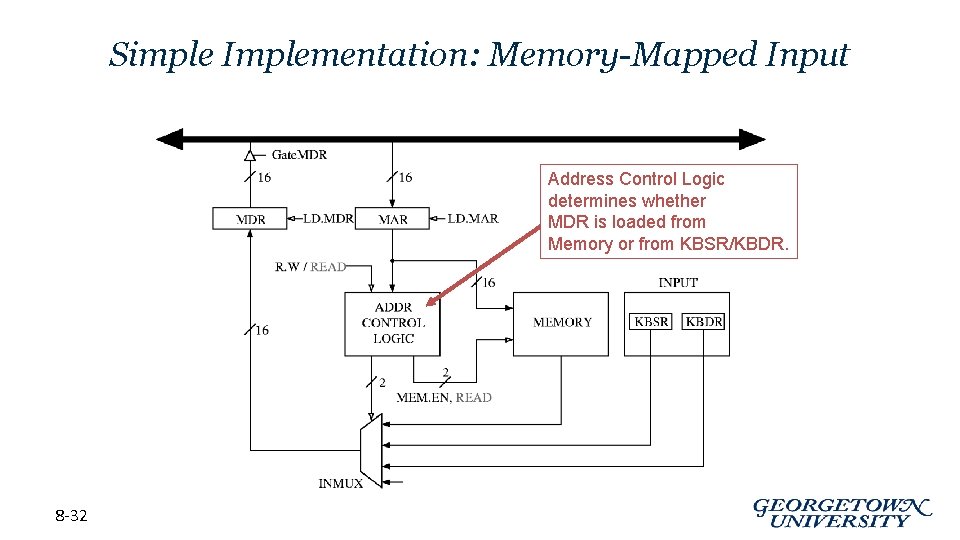

Simple Implementation: Memory-Mapped Input Address Control Logic determines whether MDR is loaded from Memory or from KBSR/KBDR. 8 -32

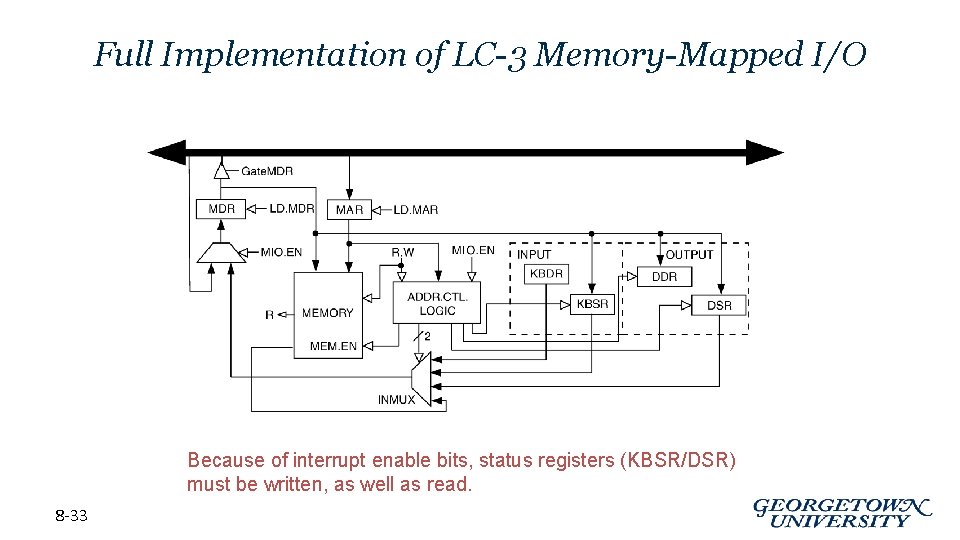

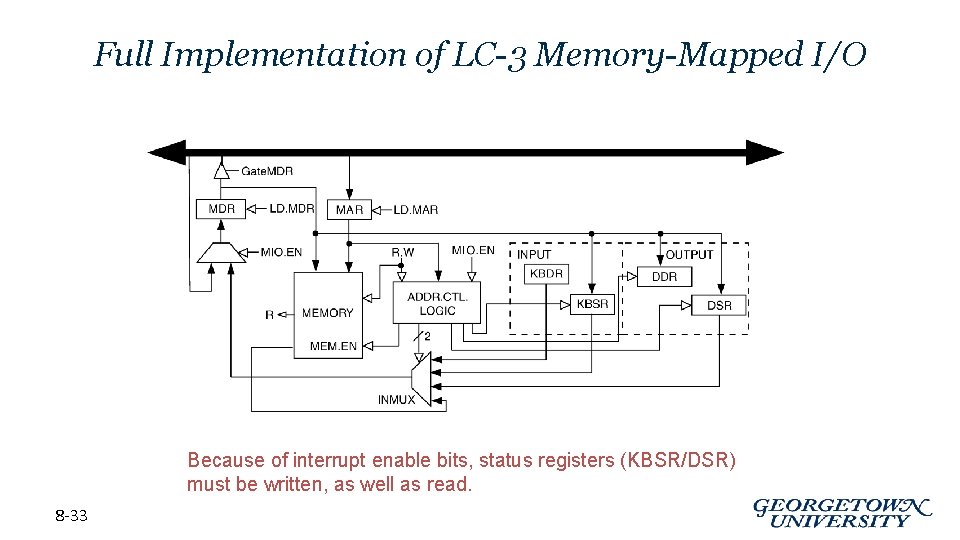

Full Implementation of LC-3 Memory-Mapped I/O Because of interrupt enable bits, status registers (KBSR/DSR) must be written, as well as read. 8 -33