COSC 121 Computer Systems Exceptions and Interrupts Jeremy

- Slides: 48

COSC 121: Computer Systems. Exceptions and Interrupts Jeremy Bolton, Ph. D Assistant Teaching Professor Constructed using materials: - Patt and Patel Introduction to Computing Systems (2 nd) - Patterson and Hennessy Computer Organization and Design (4 th) **A special thanks to Eric Roberts and Mary Jane Irwin

Notes • Read PH. 4. 9 and PH. 6

Outline • Interrupts • Exceptions

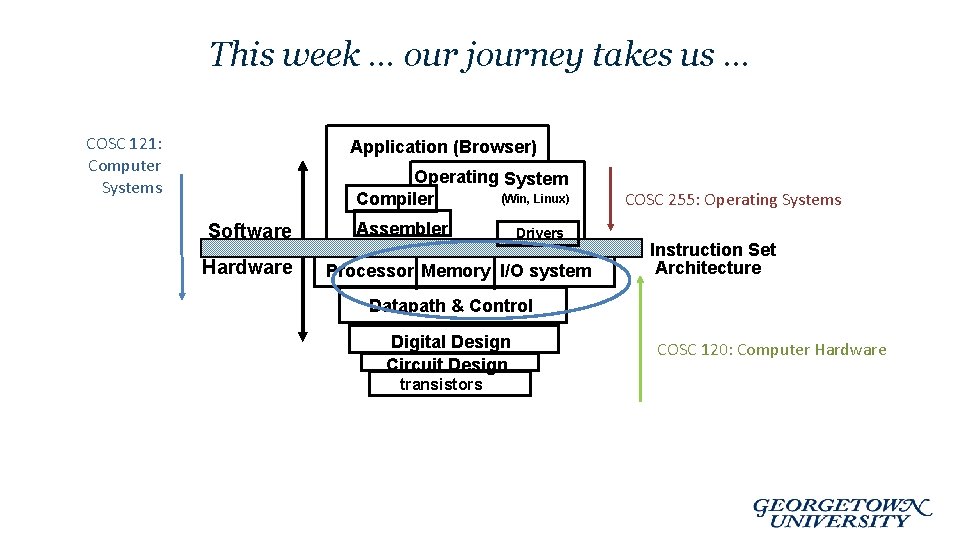

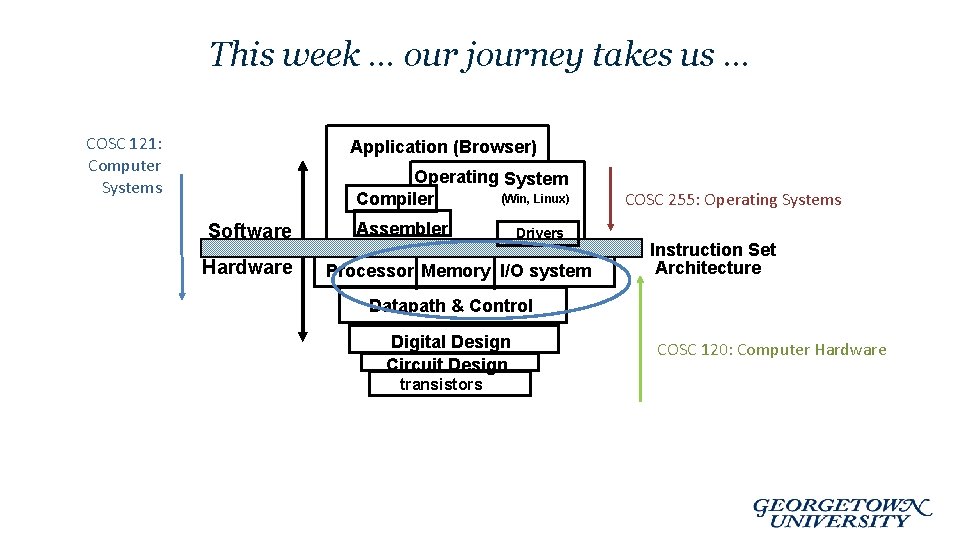

This week … our journey takes us … COSC 121: Computer Systems Application (Browser) Operating System (Win, Linux) Compiler Software Hardware Assembler Drivers Processor Memory I/O system COSC 255: Operating Systems Instruction Set Architecture Datapath & Control Digital Design Circuit Design transistors COSC 120: Computer Hardware

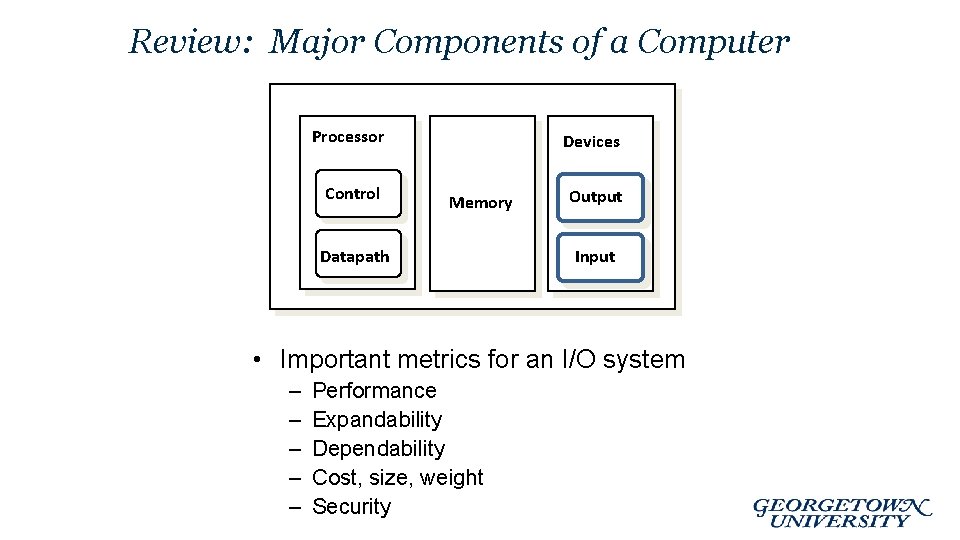

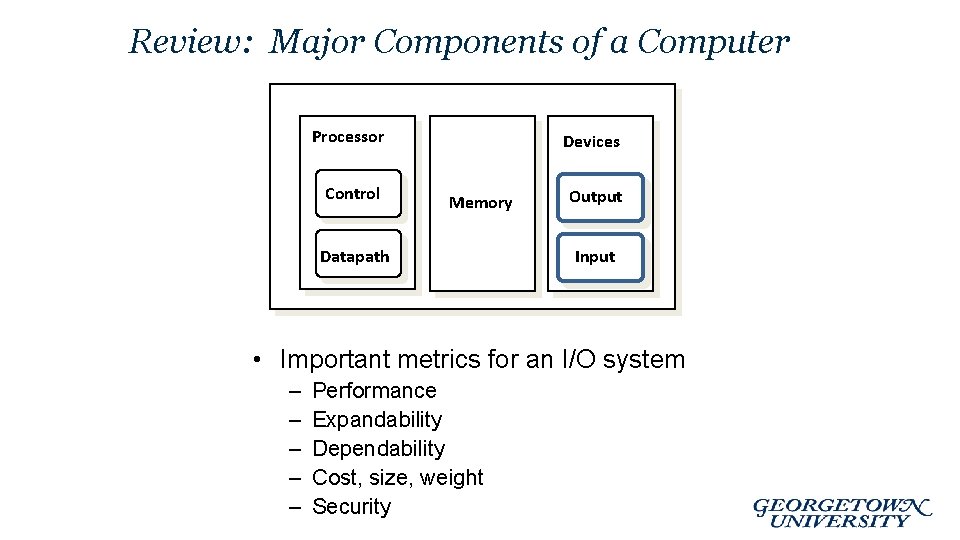

Review: Major Components of a Computer Processor Control Devices Memory Datapath Output Input • Important metrics for an I/O system – – – Performance Expandability Dependability Cost, size, weight Security

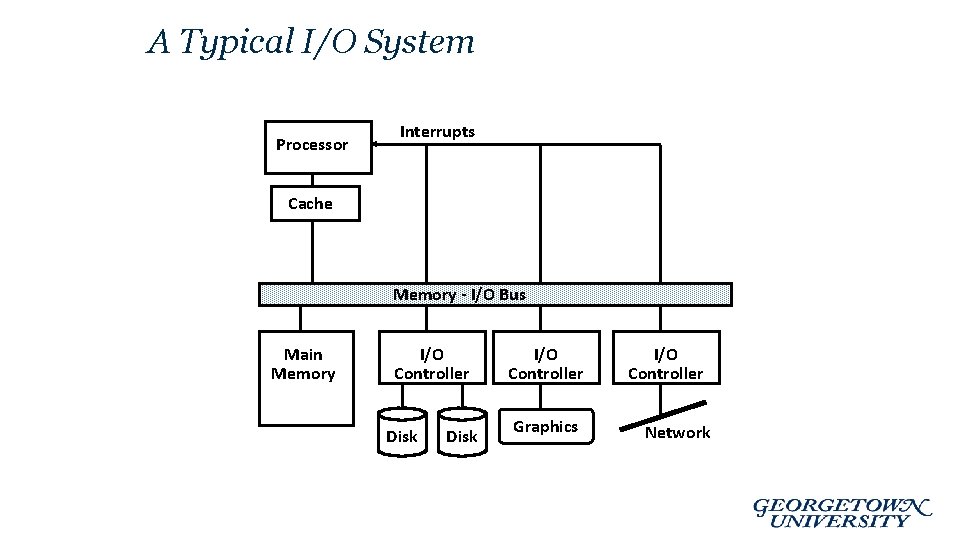

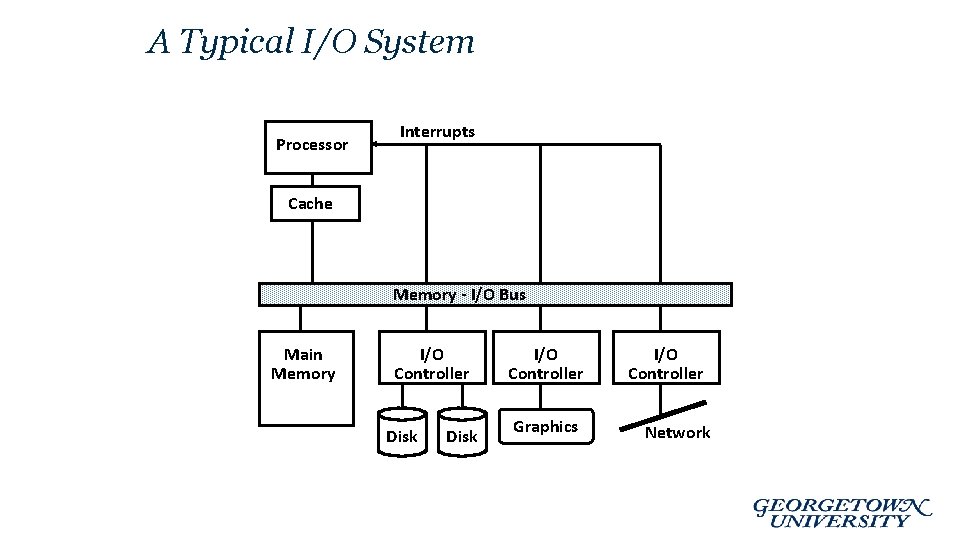

A Typical I/O System Processor Interrupts Cache Memory - I/O Bus Main Memory I/O Controller Disk I/O Controller Graphics I/O Controller Network

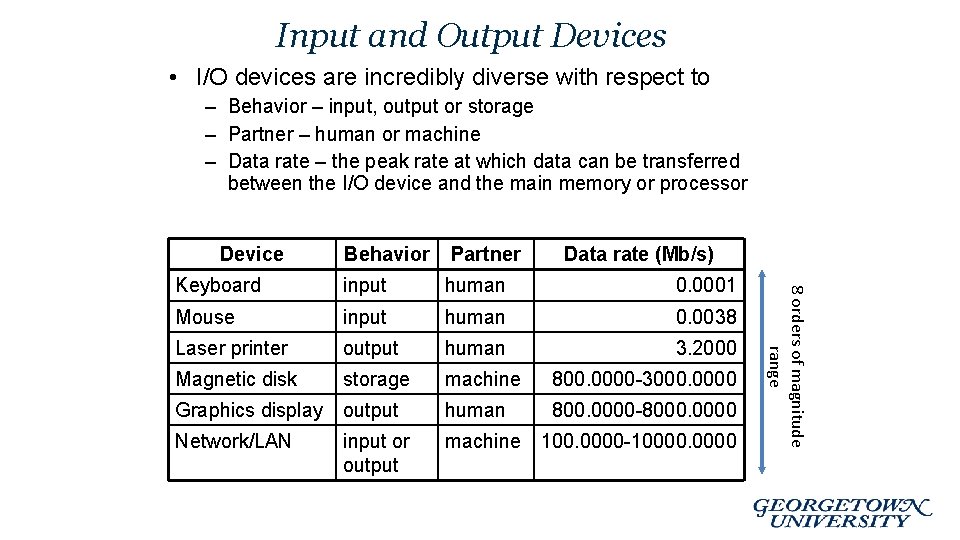

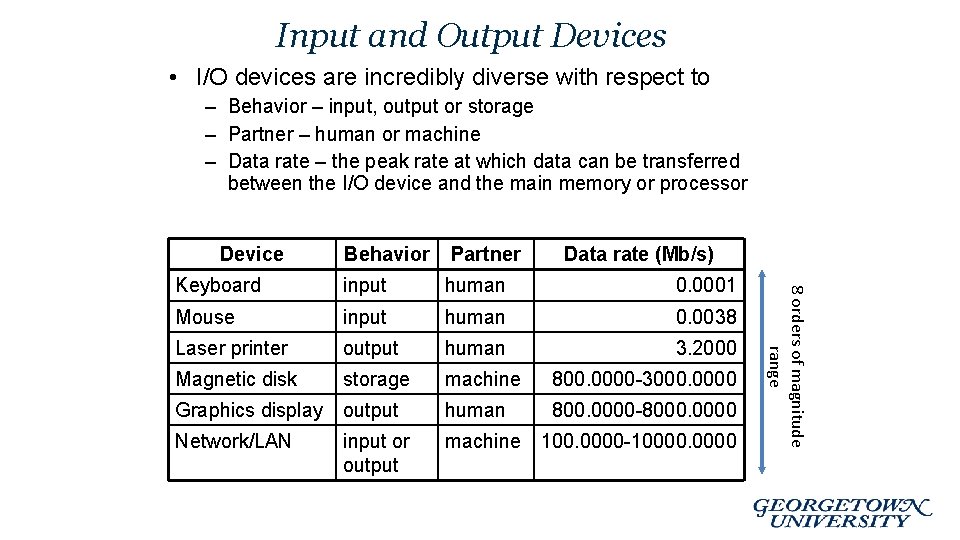

Input and Output Devices • I/O devices are incredibly diverse with respect to – Behavior – input, output or storage – Partner – human or machine – Data rate – the peak rate at which data can be transferred between the I/O device and the main memory or processor Device Partner Data rate (Mb/s) Keyboard input human 0. 0001 Mouse input human 0. 0038 Laser printer output human 3. 2000 Magnetic disk storage machine 800. 0000 -3000. 0000 Graphics display output human 800. 0000 -8000. 0000 Network/LAN input or output machine 100. 0000 -10000 8 orders of magnitude range Behavior

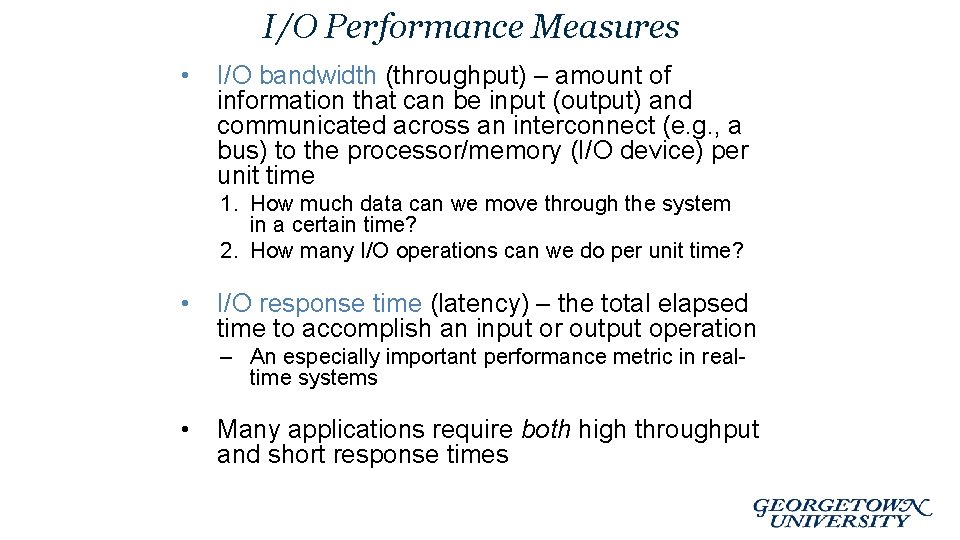

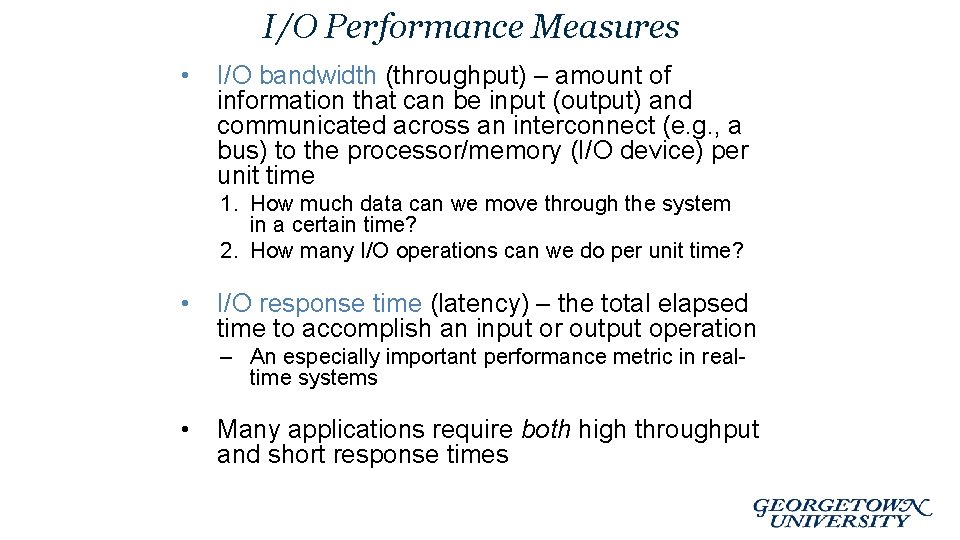

I/O Performance Measures • I/O bandwidth (throughput) – amount of information that can be input (output) and communicated across an interconnect (e. g. , a bus) to the processor/memory (I/O device) per unit time 1. How much data can we move through the system in a certain time? 2. How many I/O operations can we do per unit time? • I/O response time (latency) – the total elapsed time to accomplish an input or output operation – An especially important performance metric in realtime systems • Many applications require both high throughput and short response times

I/O System Interconnect Issues • A bus is a shared communication link (a single set of wires used to connect multiple subsystems) that needs to support a range of devices with widely varying latencies and data transfer rates – Advantages • Versatile – new devices can be added easily and can be moved between computer systems that use the same bus standard • Low cost – a single set of wires is shared in multiple ways – Disadvantages • Creates a communication bottleneck – bus bandwidth limits the maximum I/O throughput • The maximum bus speed is largely limited by – The length of the bus – The number of devices on the bus

Types of Buses • Processor-memory bus (“Front Side Bus”, proprietary) – Short and high speed – Matched to the memory system to maximize the memoryprocessor bandwidth – Optimized for cache block transfers • I/O bus (industry standard, e. g. , SCSI, USB, Firewire) – Usually is lengthy and slower – Needs to accommodate a wide range of I/O devices – Use either the processor-memory bus or a backplane bus to connect to memory • Backplane bus (industry standard, e. g. , PCIexpress) – Used as an intermediary bus connecting I/O busses to the processor-memory bus

I/O Transactions • An I/O transaction is a sequence of operations over the interconnect that includes a request and may include a response either of which may carry data. A transaction is initiated by a single request and may take many individual bus operations. An I/O transaction typically includes two parts 1. Sending the address 2. Receiving or sending the data • Bus transactions are defined by what they do to memory output input – A read transaction reads data from memory (to either the processor or an I/O device) – A write transaction writes data to the memory (from either the processor or an I/O device)

Synchronous and Asynchronous Buses • Synchronous bus (e. g. , processor-memory buses) – Includes a clock in the control lines and has a fixed protocol for communication that is relative to the clock – Advantage: involves very little logic and can run very fast – Disadvantages: • Every device communicating on the bus must use same clock rate • To avoid clock skew, they cannot be long if they are fast • Asynchronous bus (e. g. , I/O buses) – It is not clocked, so requires a handshaking protocol and additional control lines (Read. Req, Ack, Data. Rdy) – Advantages: • Can accommodate a wide range of devices and device speeds • Can be lengthened without worrying about clock skew or synchronization problems – Disadvantage: slow(er)

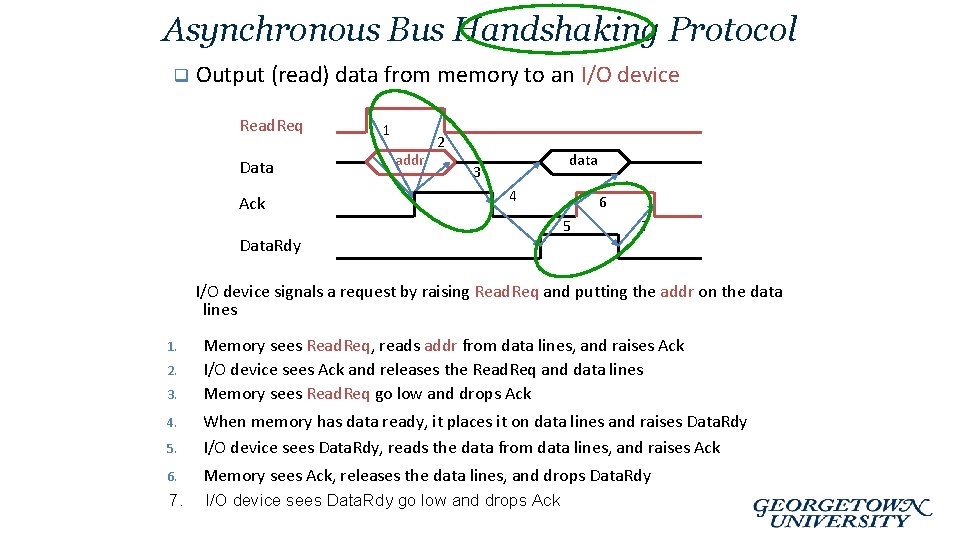

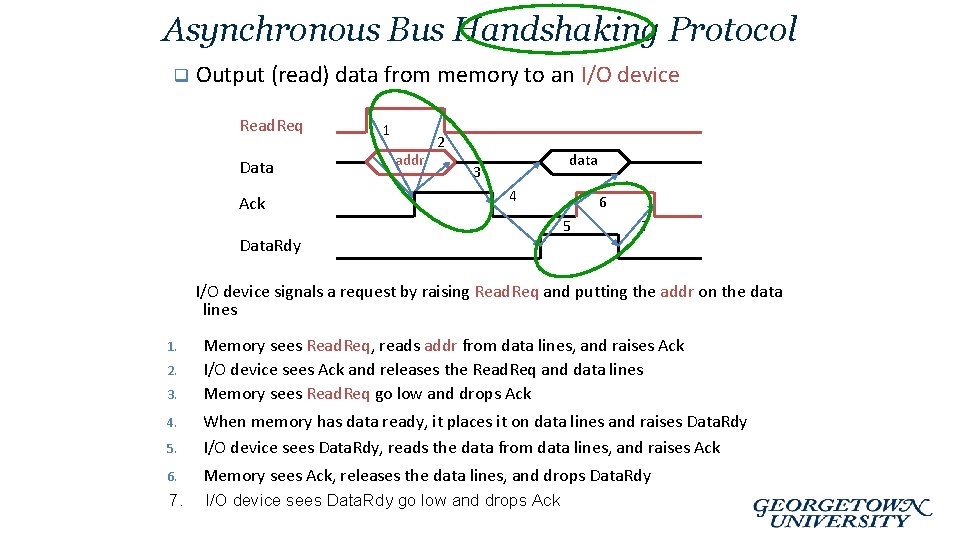

Asynchronous Bus Handshaking Protocol q Output (read) data from memory to an I/O device Read. Req Data Ack 1 addr 2 data 3 4 Data. Rdy 6 5 7 I/O device signals a request by raising Read. Req and putting the addr on the data lines 1. 2. 3. Memory sees Read. Req, reads addr from data lines, and raises Ack I/O device sees Ack and releases the Read. Req and data lines Memory sees Read. Req go low and drops Ack 5. When memory has data ready, it places it on data lines and raises Data. Rdy I/O device sees Data. Rdy, reads the data from data lines, and raises Ack 6. Memory sees Ack, releases the data lines, and drops Data. Rdy 7. I/O device sees Data. Rdy go low and drops Ack 4.

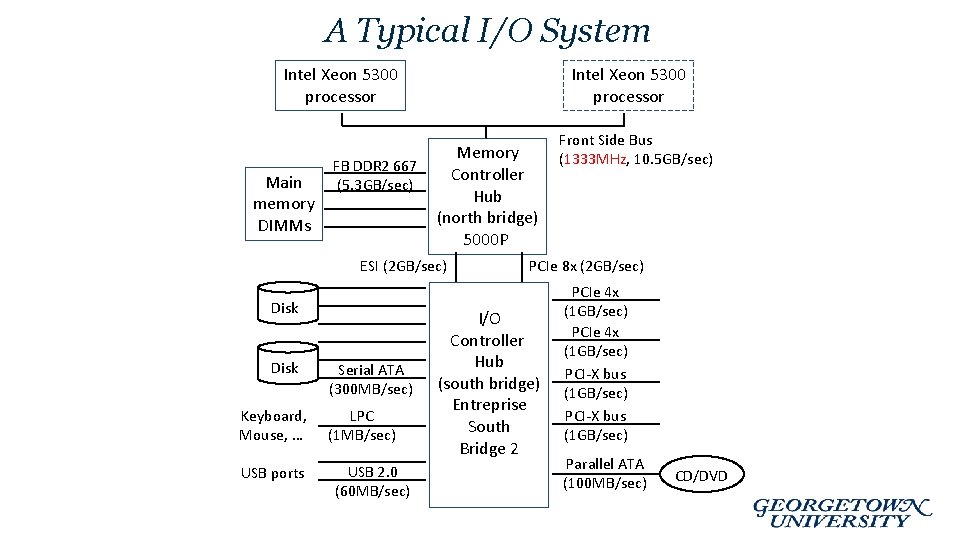

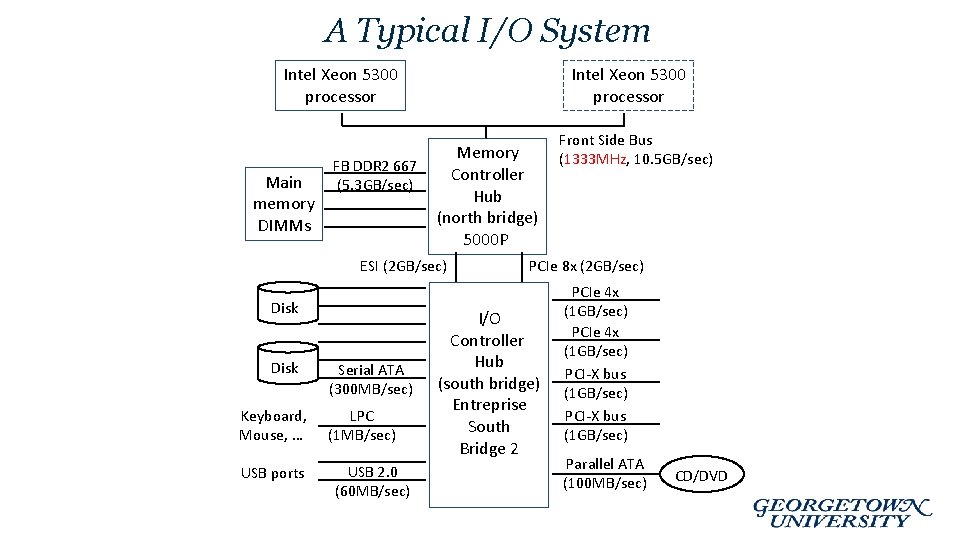

A Typical I/O System Intel Xeon 5300 processor Main memory DIMMs FB DDR 2 667 (5. 3 GB/sec) Intel Xeon 5300 processor Memory Controller Hub (north bridge) 5000 P ESI (2 GB/sec) Disk Keyboard, Mouse, … USB ports Serial ATA (300 MB/sec) LPC (1 MB/sec) USB 2. 0 (60 MB/sec) Front Side Bus (1333 MHz, 10. 5 GB/sec) PCIe 8 x (2 GB/sec) I/O Controller Hub (south bridge) Entreprise South Bridge 2 PCIe 4 x (1 GB/sec) PCI-X bus (1 GB/sec) Parallel ATA (100 MB/sec) CD/DVD

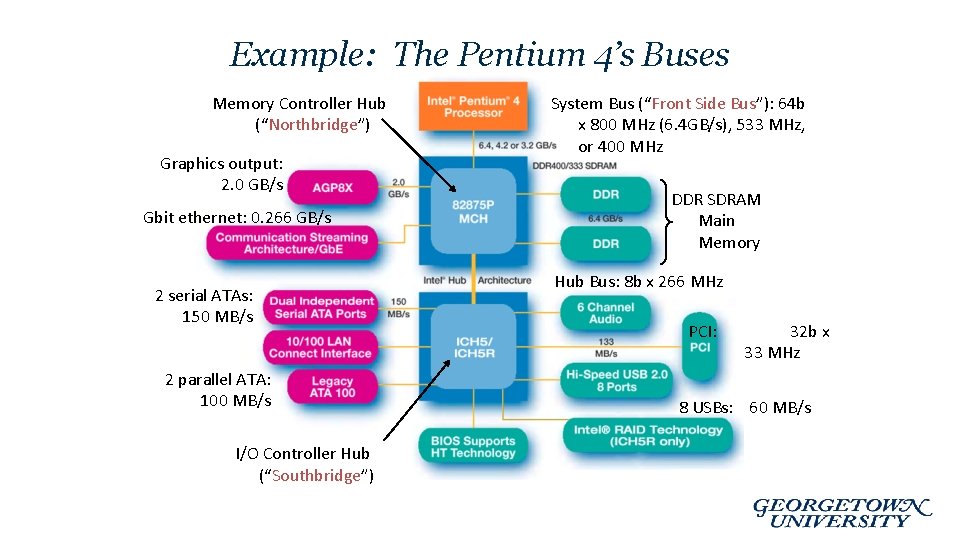

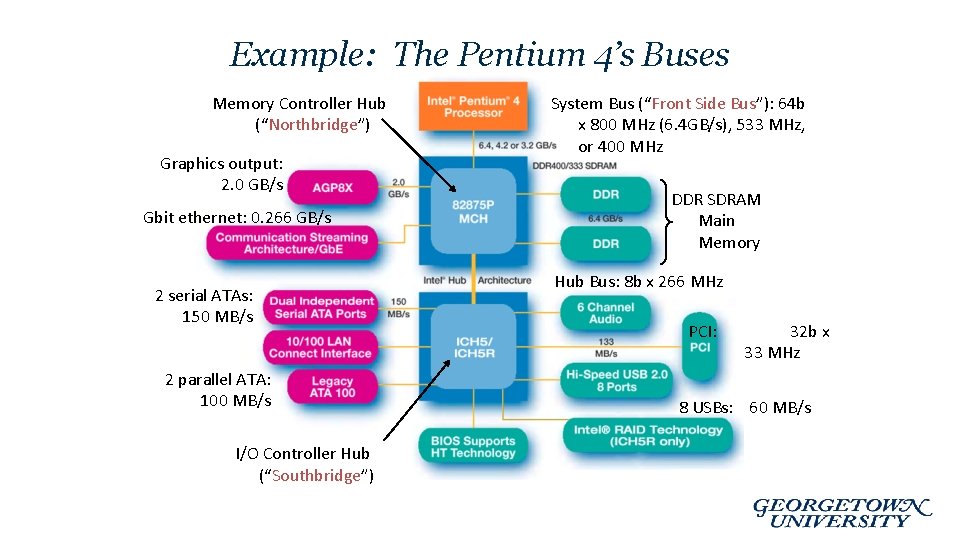

Example: The Pentium 4’s Buses Memory Controller Hub (“Northbridge”) Graphics output: 2. 0 GB/s Gbit ethernet: 0. 266 GB/s 2 serial ATAs: 150 MB/s 2 parallel ATA: 100 MB/s I/O Controller Hub (“Southbridge”) System Bus (“Front Side Bus”): 64 b x 800 MHz (6. 4 GB/s), 533 MHz, or 400 MHz DDR SDRAM Main Memory Hub Bus: 8 b x 266 MHz PCI: 32 b x 33 MHz 8 USBs: 60 MB/s

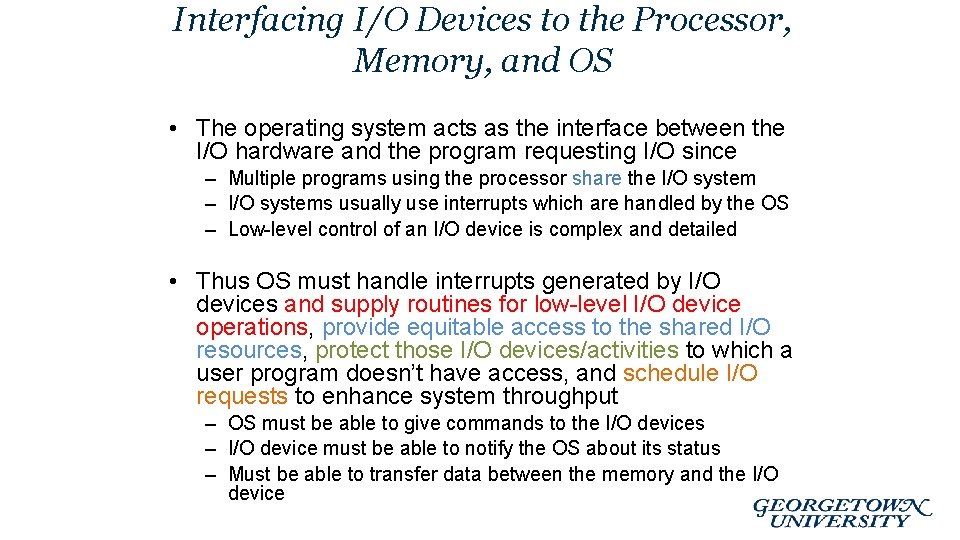

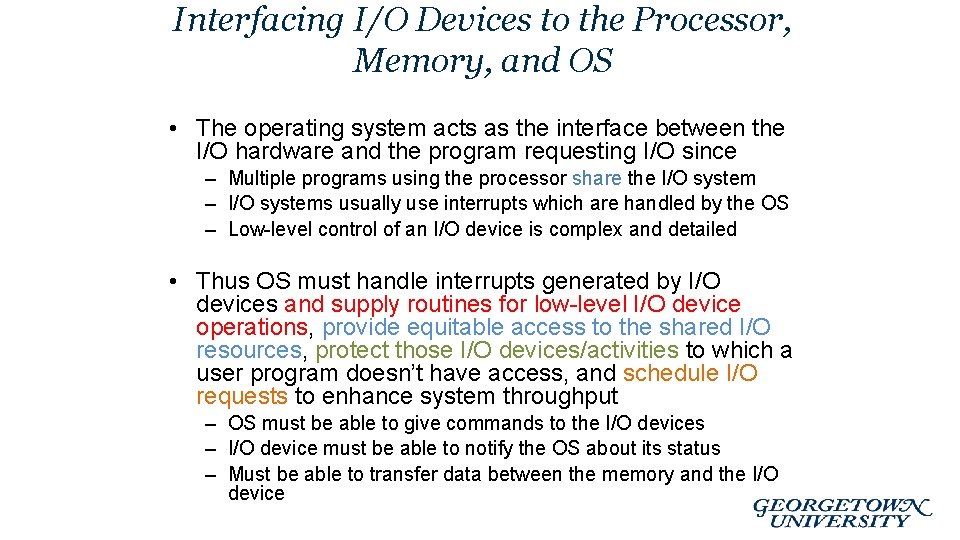

Interfacing I/O Devices to the Processor, Memory, and OS • The operating system acts as the interface between the I/O hardware and the program requesting I/O since – Multiple programs using the processor share the I/O system – I/O systems usually use interrupts which are handled by the OS – Low-level control of an I/O device is complex and detailed • Thus OS must handle interrupts generated by I/O devices and supply routines for low-level I/O device operations, provide equitable access to the shared I/O resources, protect those I/O devices/activities to which a user program doesn’t have access, and schedule I/O requests to enhance system throughput – OS must be able to give commands to the I/O devices – I/O device must be able to notify the OS about its status – Must be able to transfer data between the memory and the I/O device

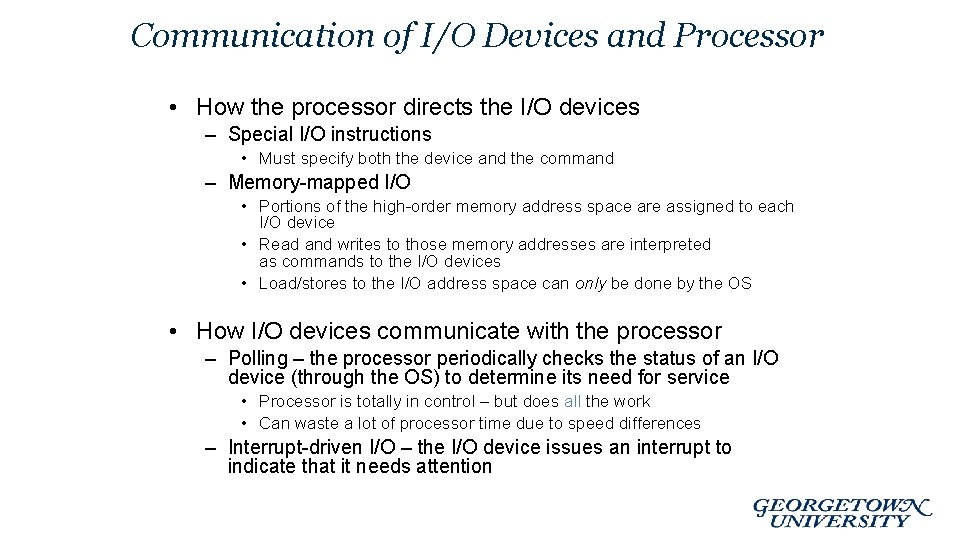

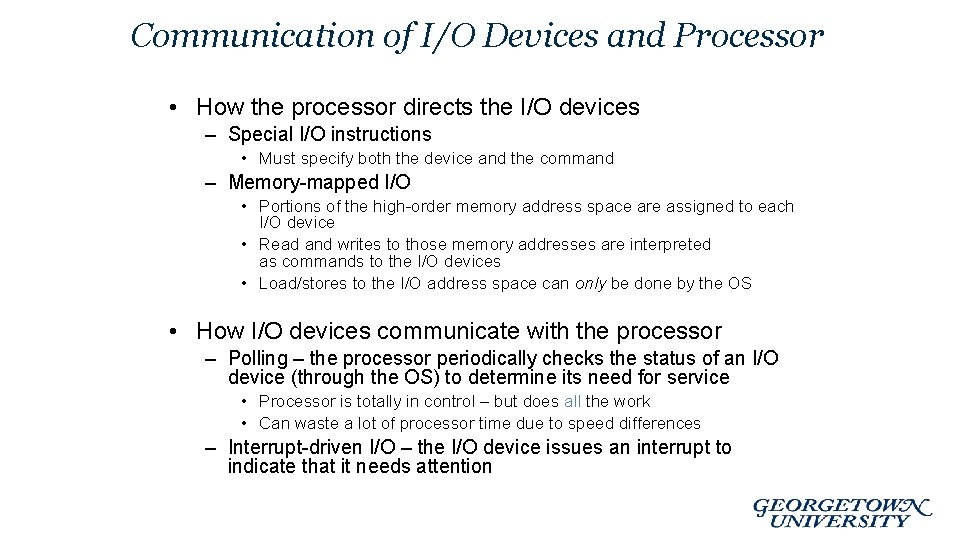

Communication of I/O Devices and Processor • How the processor directs the I/O devices – Special I/O instructions • Must specify both the device and the command – Memory-mapped I/O • Portions of the high-order memory address space are assigned to each I/O device • Read and writes to those memory addresses are interpreted as commands to the I/O devices • Load/stores to the I/O address space can only be done by the OS • How I/O devices communicate with the processor – Polling – the processor periodically checks the status of an I/O device (through the OS) to determine its need for service • Processor is totally in control – but does all the work • Can waste a lot of processor time due to speed differences – Interrupt-driven I/O – the I/O device issues an interrupt to indicate that it needs attention

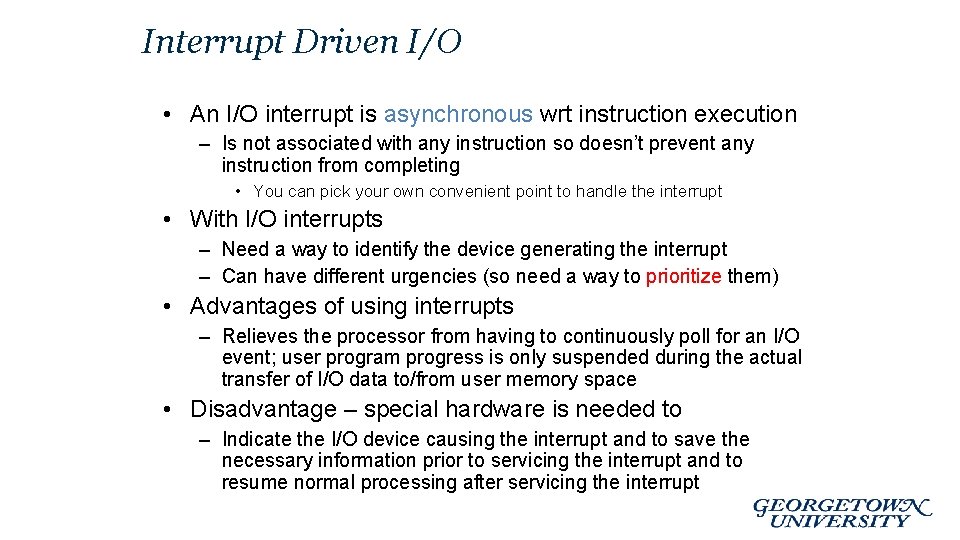

Interrupt Driven I/O • An I/O interrupt is asynchronous wrt instruction execution – Is not associated with any instruction so doesn’t prevent any instruction from completing • You can pick your own convenient point to handle the interrupt • With I/O interrupts – Need a way to identify the device generating the interrupt – Can have different urgencies (so need a way to prioritize them) • Advantages of using interrupts – Relieves the processor from having to continuously poll for an I/O event; user program progress is only suspended during the actual transfer of I/O data to/from user memory space • Disadvantage – special hardware is needed to – Indicate the I/O device causing the interrupt and to save the necessary information prior to servicing the interrupt and to resume normal processing after servicing the interrupt

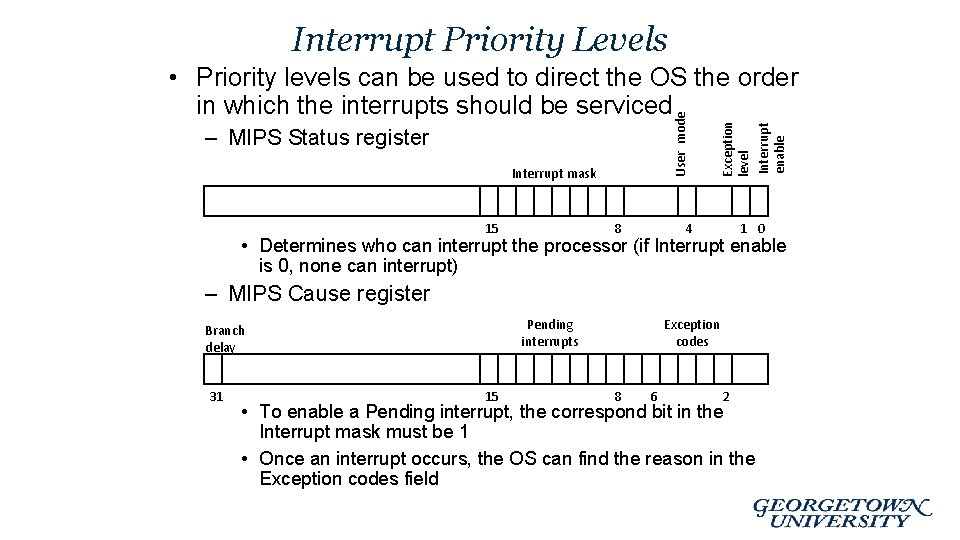

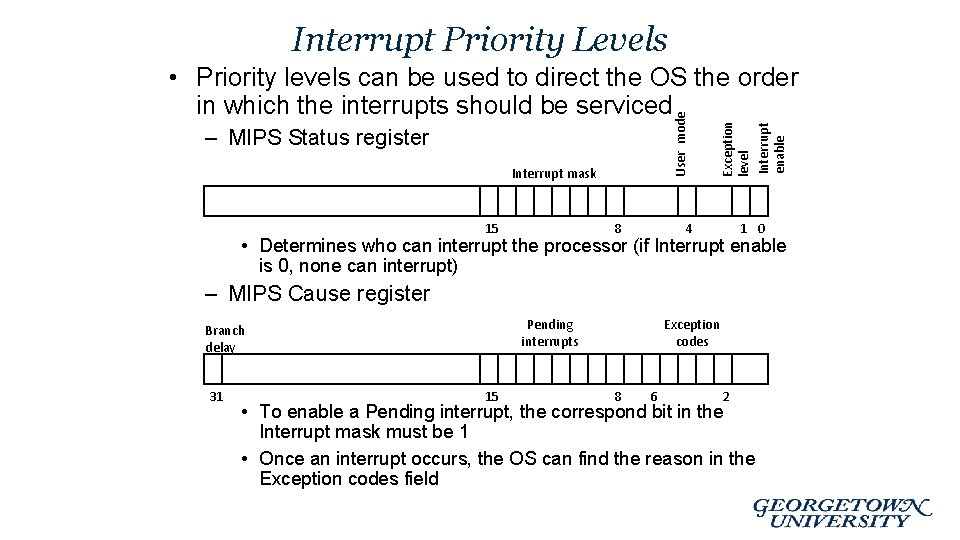

Interrupt Priority Levels – MIPS Status register Interrupt mask 15 8 Exception level Interrupt enable User mode • Priority levels can be used to direct the OS the order in which the interrupts should be serviced 4 1 0 • Determines who can interrupt the processor (if Interrupt enable is 0, none can interrupt) – MIPS Cause register Pending interrupts Branch delay 31 15 Exception codes 8 6 2 • To enable a Pending interrupt, the correspond bit in the Interrupt mask must be 1 • Once an interrupt occurs, the OS can find the reason in the Exception codes field

Interrupt Handling Steps 1. Logically AND the Pending interrupt field and the Interrupt mask field to see which enabled interrupts could be the culprit. Make copies of both Status and Cause registers. 2. Select the higher priority of these interrupts (leftmost is highest) 3. Save the Interrupt mask field 4. Change the Interrupt mask field to disable all interrupts of equal or lower priority 5. Save the processor state prior to “handling” the interrupt 1. See example with LC 3 later 6. Set the Interrupt enable bit (to allow higher-priority interrupts) 7. Call the appropriate interrupt handler routine 8. Before returning from interrupt, set the Interrupt enable bit back to 0 and restore the Interrupt mask field q Interrupt priority levels (IPLs) assigned by the OS to each process can be raised and lowered via changes to the Status’s Interrupt mask field

Direct Memory Access (DMA) • • For high-bandwidth devices (like disks) interrupt-driven I/O would consume a lot of processor cycles With DMA, the DMA controller has the ability to transfer large blocks of data directly to/from the memory without involving the processor 1. The processor initiates the DMA transfer by supplying the I/O device address, the operation to be performed, the memory address destination/source, the number of bytes to transfer 2. The DMA controller manages the entire transfer (possibly thousand of bytes in length), arbitrating for the bus 3. When the DMA transfer is complete, the DMA controller interrupts the processor to let it know that the transfer is complete • There may be multiple DMA devices in one system – Processor and DMA controllers contend for bus cycles and for memory

The DMA Stale Data Problem • In systems with caches, there can be two copies of a data item, one in the cache and one in the main memory – For a DMA input (from disk to memory) – the processor will be using stale data if that location is also in the cache – For a DMA output (from memory to disk) and a writeback cache – the I/O device will receive stale data if the data is in the cache and has not yet been written back to the memory • The coherency problem can be solved by 1. Routing all I/O activity through the cache – expensive and a large negative performance impact 2. Having the OS invalidate all the entries in the cache for an I/O input or force write-backs for an I/O output (called a cache flush) 3. Providing hardware to selectively invalidate cache entries – i. e. , need a snooping cache controller

I/O System Performance • Designing an I/O system to meet a set of bandwidth and/or latency constraints means 1. Finding the weakest link in the I/O system – the component that constrains the design – – The processor and memory system ? The underlying interconnection (i. e. , bus) ? The I/O controllers ? The I/O devices themselves ? 2. (Re)configuring the weakest link to meet the bandwidth and/or latency requirements 3. Determining requirements for the rest of the components and (re)configuring them to support this latency and/or bandwidth

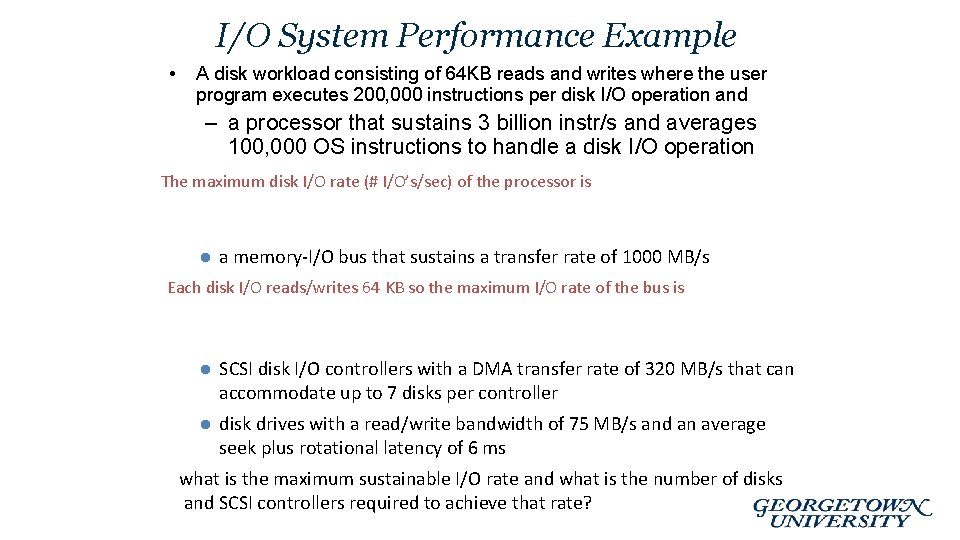

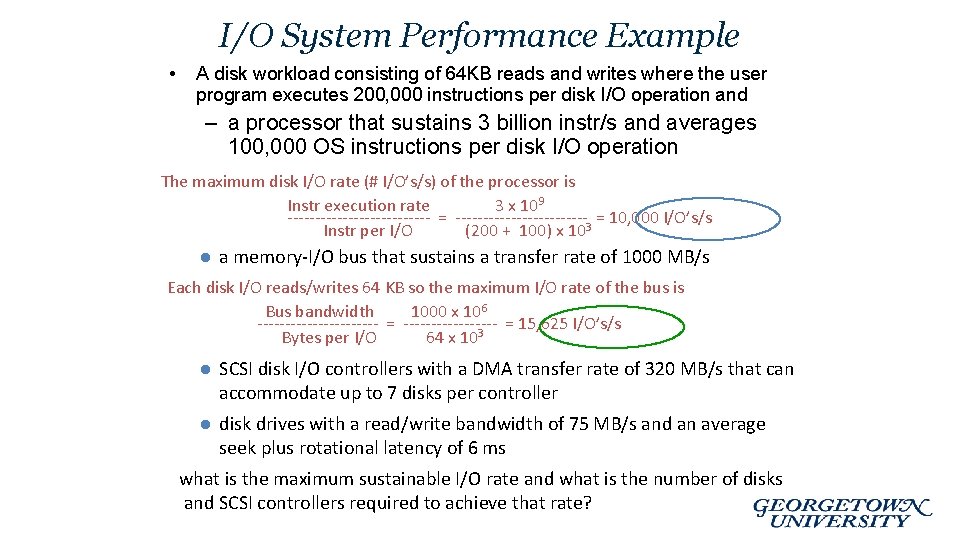

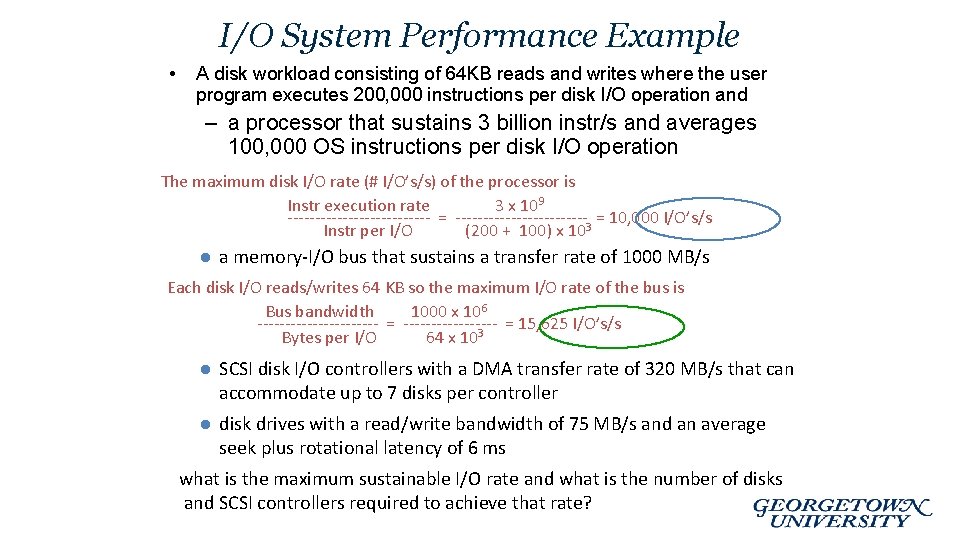

I/O System Performance Example • A disk workload consisting of 64 KB reads and writes where the user program executes 200, 000 instructions per disk I/O operation and – a processor that sustains 3 billion instr/s and averages 100, 000 OS instructions to handle a disk I/O operation The maximum disk I/O rate (# I/O’s/sec) of the processor is l a memory-I/O bus that sustains a transfer rate of 1000 MB/s Each disk I/O reads/writes 64 KB so the maximum I/O rate of the bus is l SCSI disk I/O controllers with a DMA transfer rate of 320 MB/s that can accommodate up to 7 disks per controller l disk drives with a read/write bandwidth of 75 MB/s and an average seek plus rotational latency of 6 ms what is the maximum sustainable I/O rate and what is the number of disks and SCSI controllers required to achieve that rate?

I/O System Performance Example • A disk workload consisting of 64 KB reads and writes where the user program executes 200, 000 instructions per disk I/O operation and – a processor that sustains 3 billion instr/s and averages 100, 000 OS instructions per disk I/O operation The maximum disk I/O rate (# I/O’s/s) of the processor is Instr execution rate 3 x 109 ------------- = ------------3 = 10, 000 I/O’s/s Instr per I/O (200 + 100) x 10 l a memory-I/O bus that sustains a transfer rate of 1000 MB/s Each disk I/O reads/writes 64 KB so the maximum I/O rate of the bus is Bus bandwidth 1000 x 106 ----------- = --------= 15, 625 I/O’s/s Bytes per I/O 64 x 103 l SCSI disk I/O controllers with a DMA transfer rate of 320 MB/s that can accommodate up to 7 disks per controller l disk drives with a read/write bandwidth of 75 MB/s and an average seek plus rotational latency of 6 ms what is the maximum sustainable I/O rate and what is the number of disks and SCSI controllers required to achieve that rate?

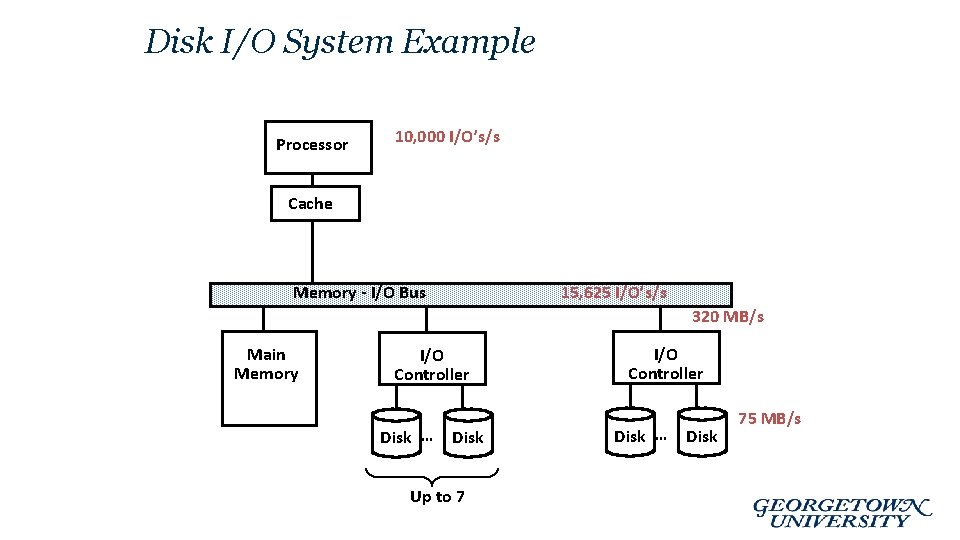

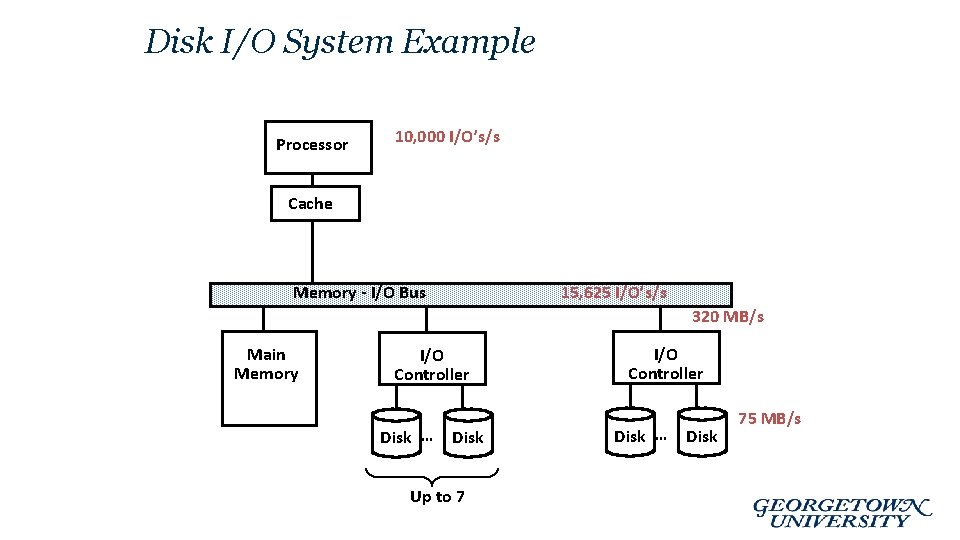

Disk I/O System Example Processor 10, 000 I/O’s/s Cache Memory - I/O Bus 15, 625 I/O’s/s 320 MB/s Main Memory I/O Controller Disk … Disk Up to 7 I/O Controller Disk … Disk 75 MB/s

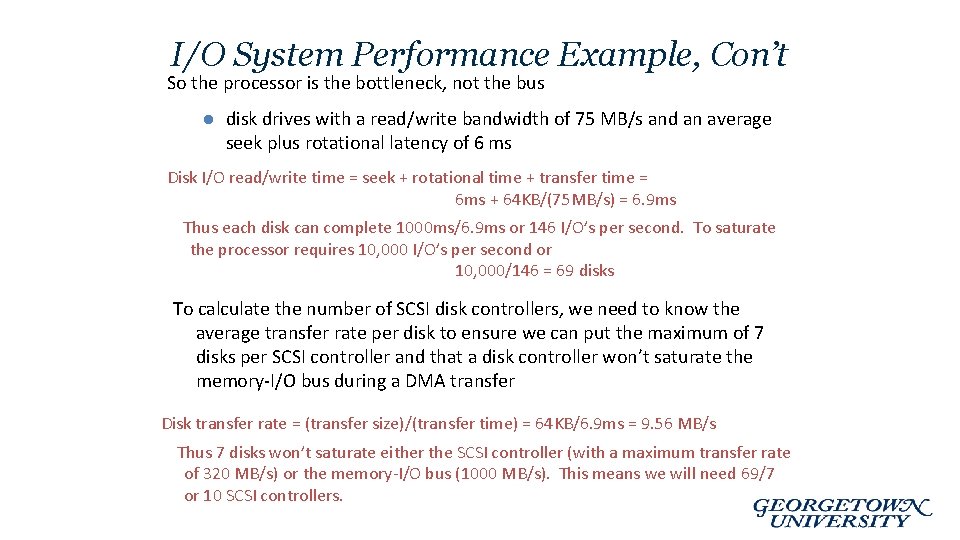

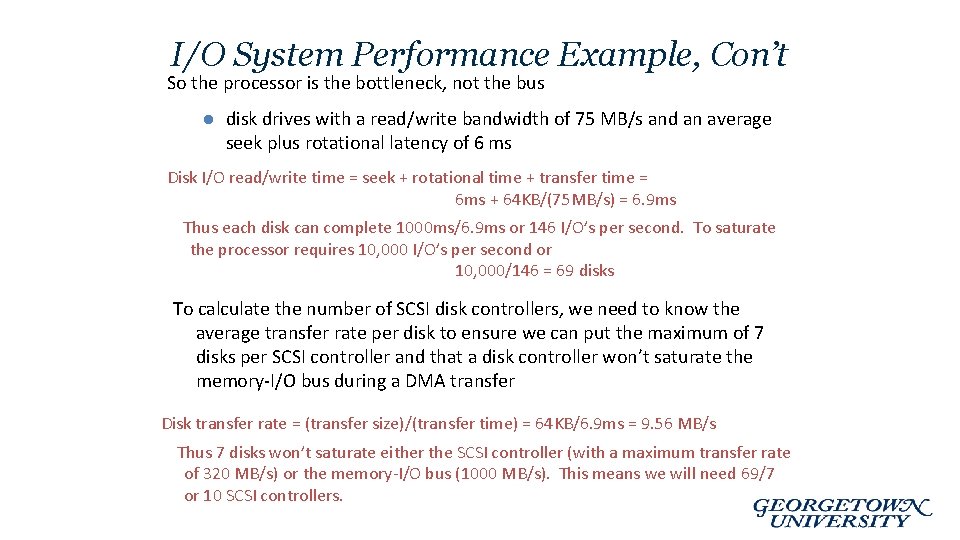

I/O System Performance Example, Con’t So the processor is the bottleneck, not the bus l disk drives with a read/write bandwidth of 75 MB/s and an average seek plus rotational latency of 6 ms Disk I/O read/write time = seek + rotational time + transfer time = 6 ms + 64 KB/(75 MB/s) = 6. 9 ms Thus each disk can complete 1000 ms/6. 9 ms or 146 I/O’s per second. To saturate the processor requires 10, 000 I/O’s per second or 10, 000/146 = 69 disks To calculate the number of SCSI disk controllers, we need to know the average transfer rate per disk to ensure we can put the maximum of 7 disks per SCSI controller and that a disk controller won’t saturate the memory-I/O bus during a DMA transfer Disk transfer rate = (transfer size)/(transfer time) = 64 KB/6. 9 ms = 9. 56 MB/s Thus 7 disks won’t saturate either the SCSI controller (with a maximum transfer rate of 320 MB/s) or the memory-I/O bus (1000 MB/s). This means we will need 69/7 or 10 SCSI controllers.

Exceptions: Example MIPS Jeremy Bolton, Ph. D Assistant Teaching Professor Constructed using materials: - Patt and Patel Introduction to Computing Systems (2 nd) - Patterson and Hennessy Computer Organization and Design (4 th) **A special thanks to Eric Roberts and Mary Jane Irwin

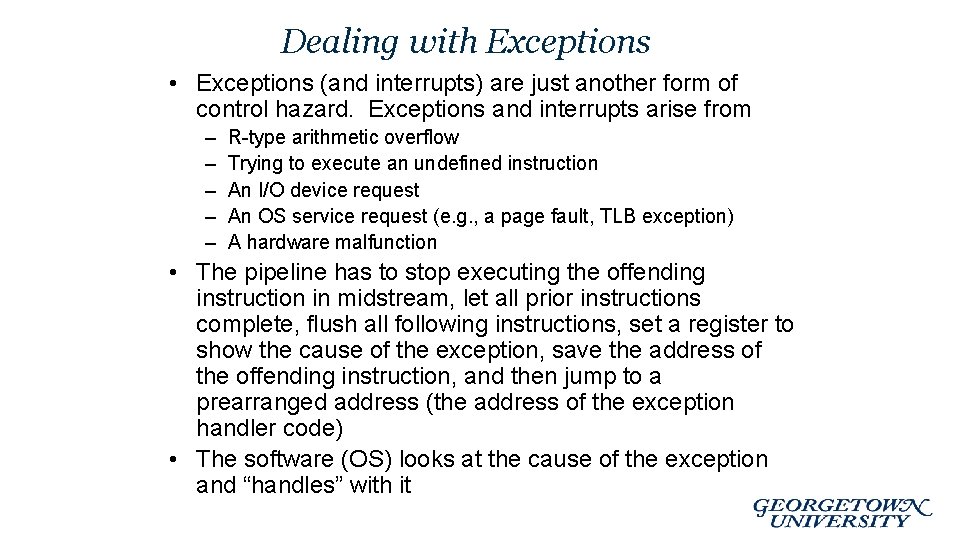

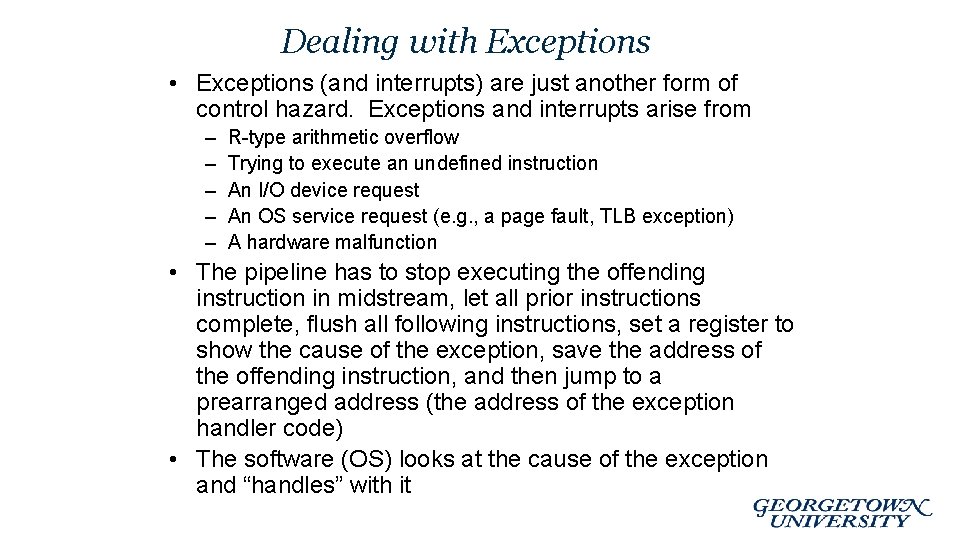

Dealing with Exceptions • Exceptions (and interrupts) are just another form of control hazard. Exceptions and interrupts arise from – – – R-type arithmetic overflow Trying to execute an undefined instruction An I/O device request An OS service request (e. g. , a page fault, TLB exception) A hardware malfunction • The pipeline has to stop executing the offending instruction in midstream, let all prior instructions complete, flush all following instructions, set a register to show the cause of the exception, save the address of the offending instruction, and then jump to a prearranged address (the address of the exception handler code) • The software (OS) looks at the cause of the exception and “handles” with it

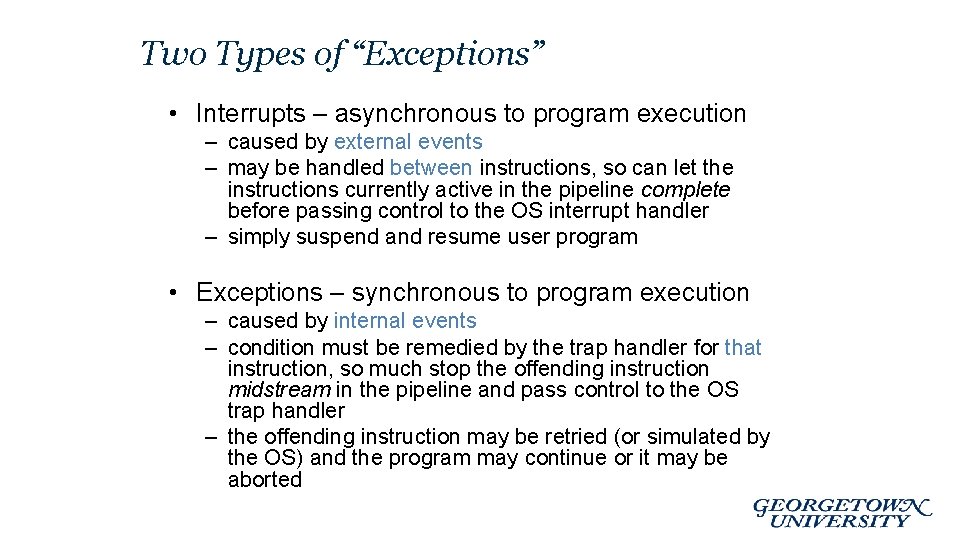

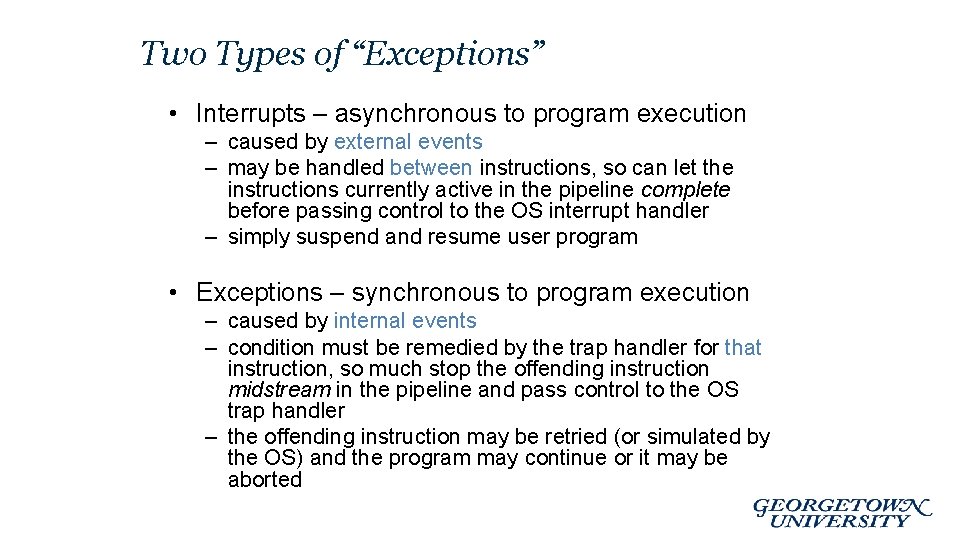

Two Types of “Exceptions” • Interrupts – asynchronous to program execution – caused by external events – may be handled between instructions, so can let the instructions currently active in the pipeline complete before passing control to the OS interrupt handler – simply suspend and resume user program • Exceptions – synchronous to program execution – caused by internal events – condition must be remedied by the trap handler for that instruction, so much stop the offending instruction midstream in the pipeline and pass control to the OS trap handler – the offending instruction may be retried (or simulated by the OS) and the program may continue or it may be aborted

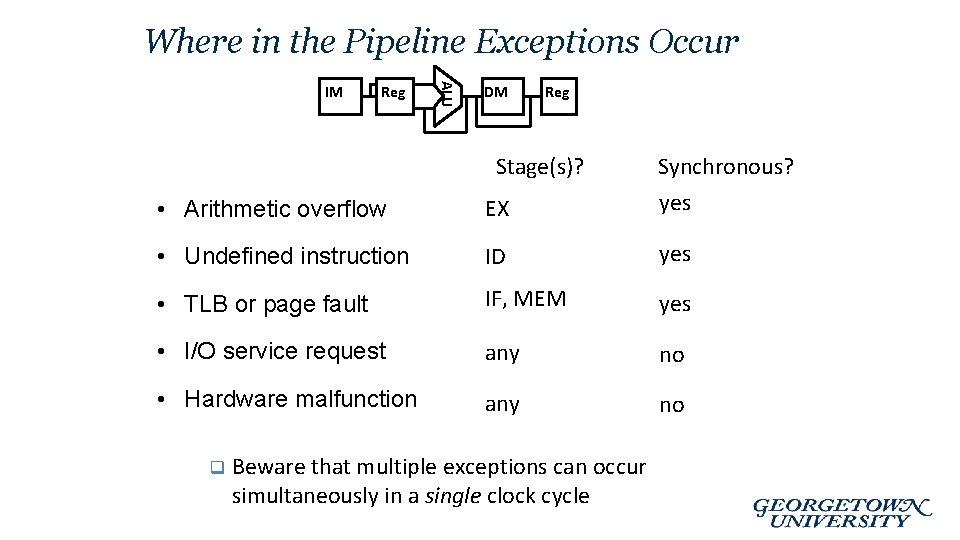

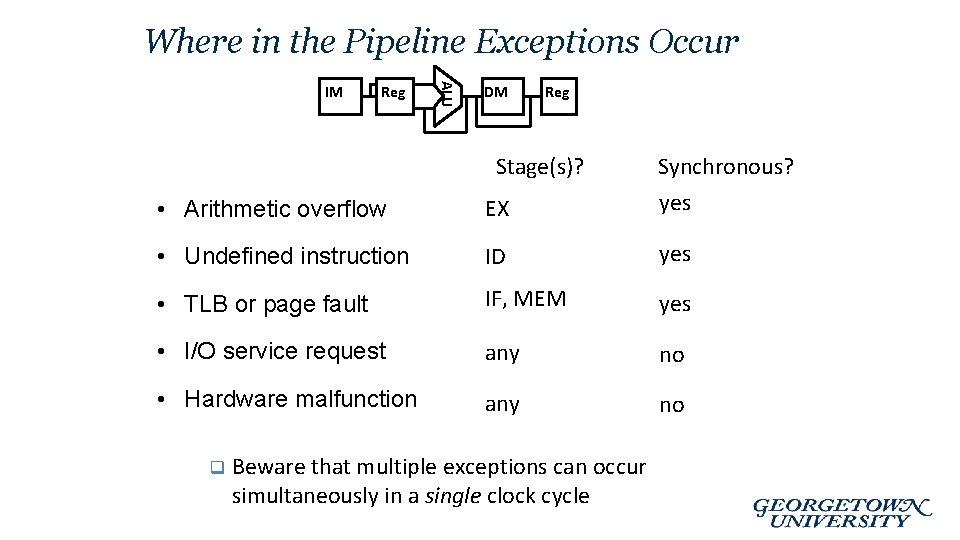

Where in the Pipeline Exceptions Occur Reg ALU IM DM Reg Stage(s)? Synchronous? • Arithmetic overflow EX yes • Undefined instruction ID yes • TLB or page fault IF, MEM yes • I/O service request any no • Hardware malfunction any no q Beware that multiple exceptions can occur simultaneously in a single clock cycle

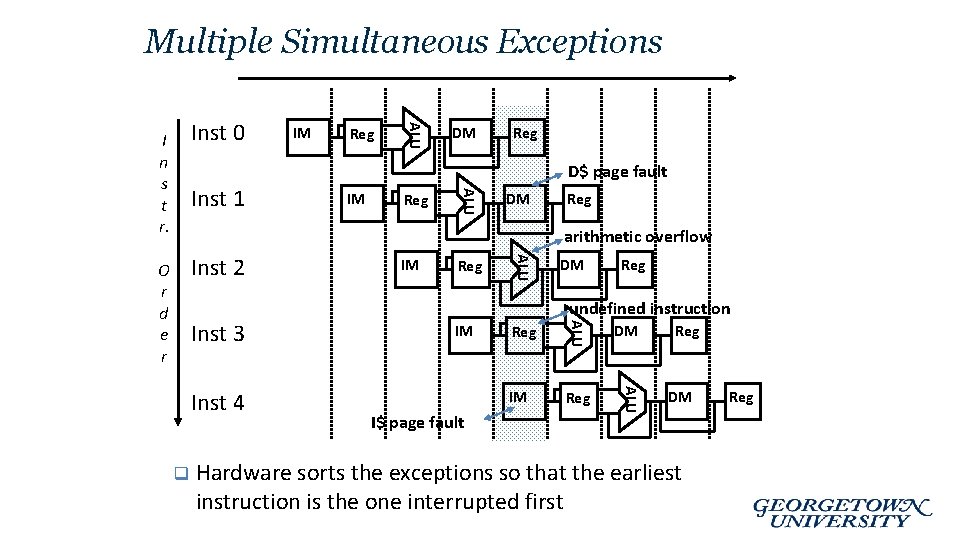

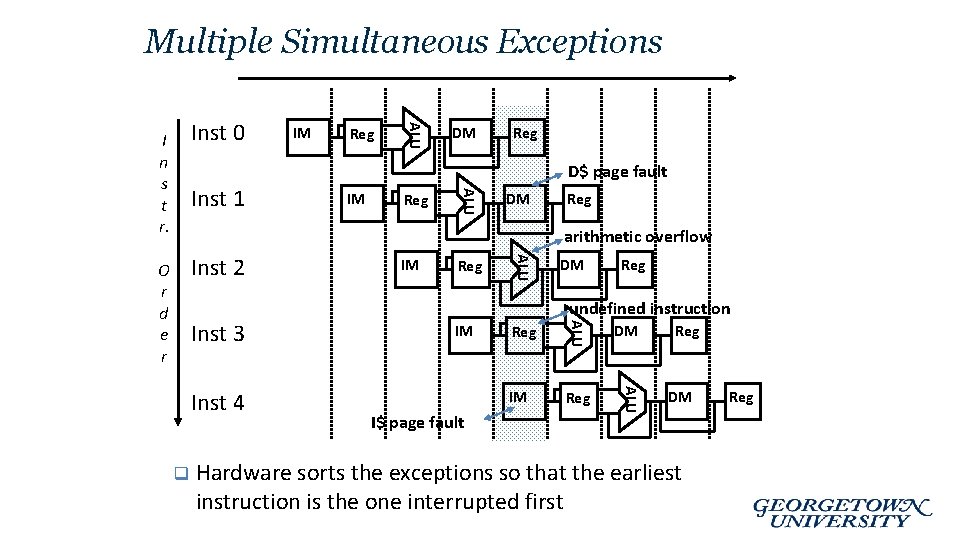

Multiple Simultaneous Exceptions IM Reg ALU Inst 0 I n s t r. DM Reg D$ page fault IM Reg ALU Inst 1 DM Reg arithmetic overflow q DM Reg undefined instruction IM I$ page fault Reg DM IM Reg ALU Inst 4 Reg ALU Inst 3 IM ALU Inst 2 O r d e r Reg DM Hardware sorts the exceptions so that the earliest instruction is the one interrupted first Reg

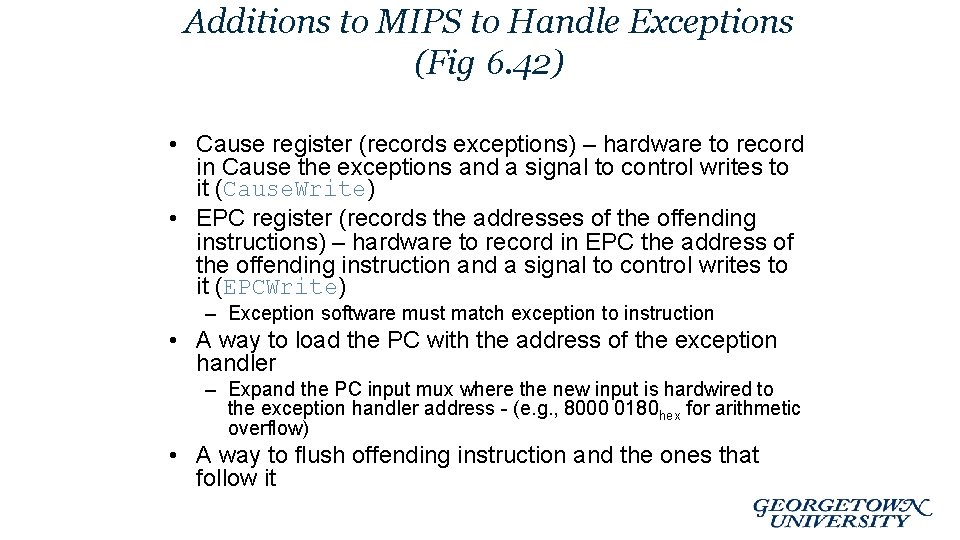

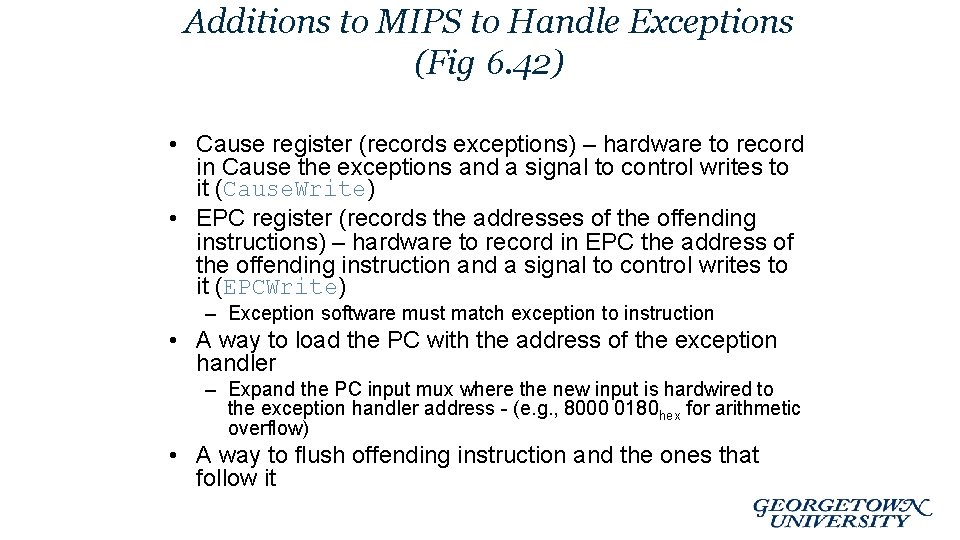

Additions to MIPS to Handle Exceptions (Fig 6. 42) • Cause register (records exceptions) – hardware to record in Cause the exceptions and a signal to control writes to it (Cause. Write) • EPC register (records the addresses of the offending instructions) – hardware to record in EPC the address of the offending instruction and a signal to control writes to it (EPCWrite) – Exception software must match exception to instruction • A way to load the PC with the address of the exception handler – Expand the PC input mux where the new input is hardwired to the exception handler address - (e. g. , 8000 0180 hex for arithmetic overflow) • A way to flush offending instruction and the ones that follow it

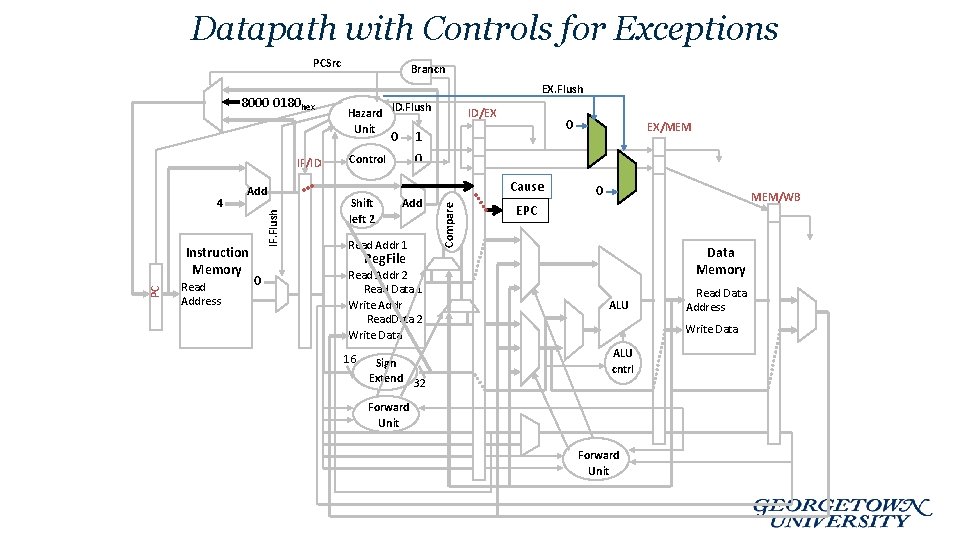

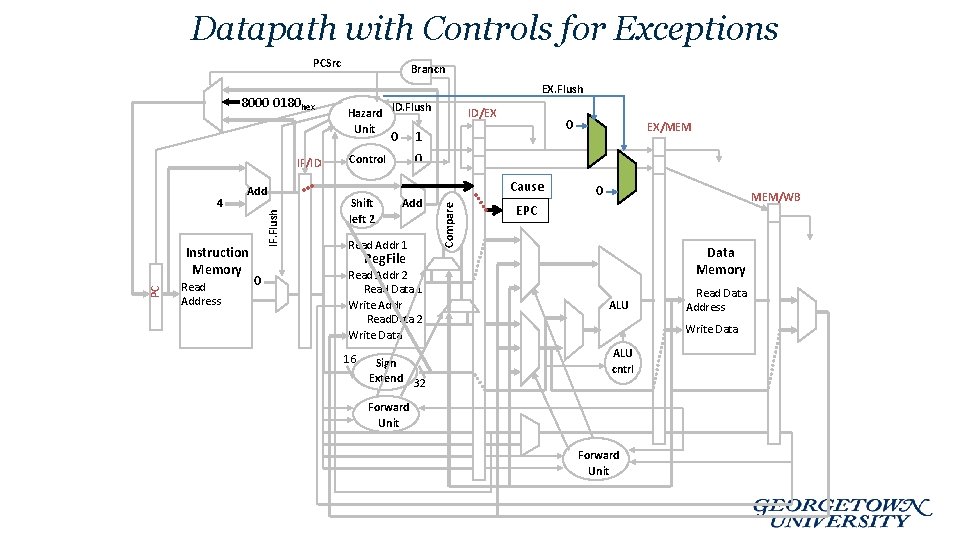

Datapath with Controls for Exceptions PCSrc EX. Flush Hazard ID. Flush Unit 0 IF/ID PC Instruction Memory Read Address IF. Flush 4 Add ID/EX 0 1 Cause Shift left 2 EX/MEM 0 Control Add Read Addr 1 Compare 8000 0180 hex Branch 0 MEM/WB EPC Data Memory Reg. File 0 Read Addr 2 Read Data 1 Write Addr Read. Data 2 Write Data 16 Sign Extend 32 ALU Read Data Address Write Data ALU cntrl Forward Unit

Exceptions: Example LC 3 Jeremy Bolton, Ph. D Assistant Teaching Professor Constructed using materials: - Patt and Patel Introduction to Computing Systems (2 nd) - Patterson and Hennessy Computer Organization and Design (4 th) **A special thanks to Eric Roberts and Mary Jane Irwin

Interrupt-Driven I/O • Interrupts. 1. External device signals need to be serviced. 2. Processor saves state and starts service routine. 3. When finished, processor restores state and resumes program. Interrupt is an unscripted subroutine call, triggered by an external event. • How doe we save the current state of computation so the interrupt can be resolved? 10 -39

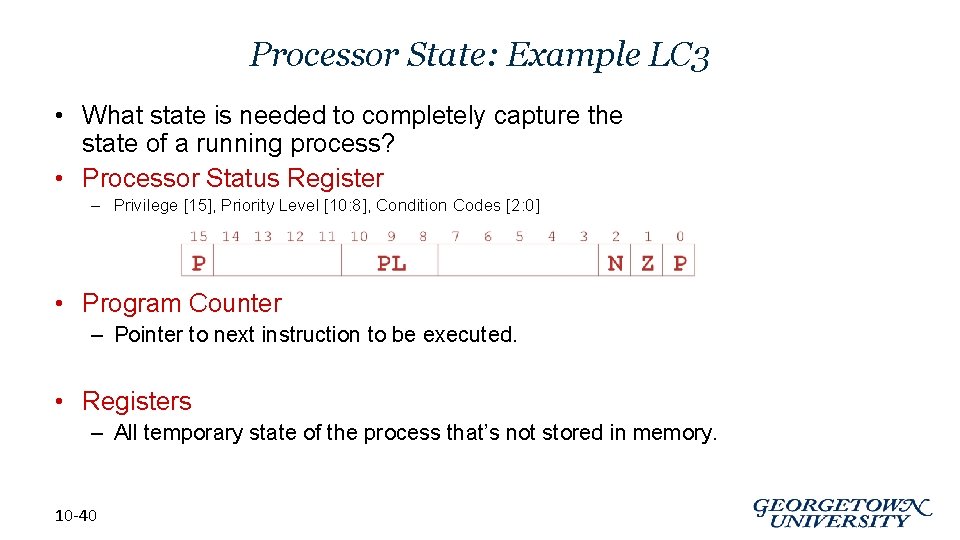

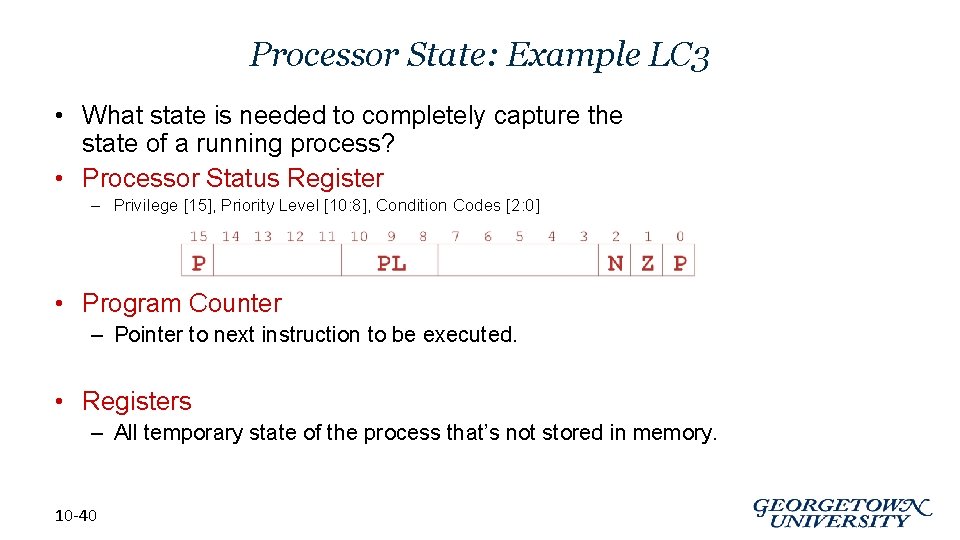

Processor State: Example LC 3 • What state is needed to completely capture the state of a running process? • Processor Status Register – Privilege [15], Priority Level [10: 8], Condition Codes [2: 0] • Program Counter – Pointer to next instruction to be executed. • Registers – All temporary state of the process that’s not stored in memory. 10 -40

Where to Save Processor State? • Can’t use registers. – Programmer doesn’t know when interrupt might occur, so she can’t prepare by saving critical registers. – When resuming, need to restore state exactly as it was. • Memory allocated by service routine? – Must save state before invoking routine, so we wouldn’t know where. – Also, interrupts may be nested – that is, an interrupt service routine might also get interrupted! • Use a stack! 10 -41 – Location of stack “hard-wired”. – Push state to save, pop to restore.

Supervisor Stack • A special region of memory used as the stack for interrupt service routines. – Initial Supervisor Stack Pointer (SSP) stored in Saved. SSP. – Another register for storing User Stack Pointer (USP): Saved. USP. • Want to use R 6 as stack pointer. – So that our PUSH/POP routines still work. • When switching from User mode to Supervisor mode (as result of interrupt), save R 6 to Saved. USP. 10 -42

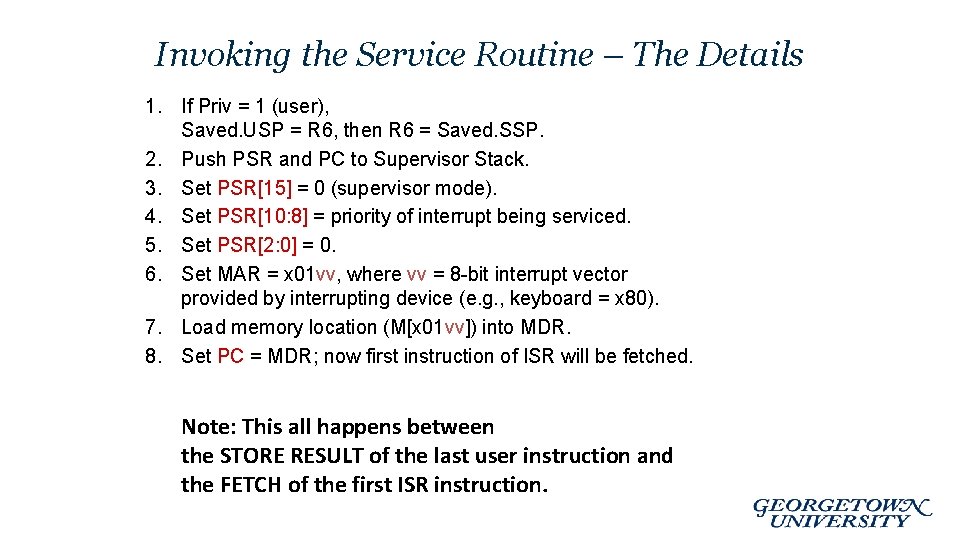

Invoking the Service Routine – The Details 1. If Priv = 1 (user), Saved. USP = R 6, then R 6 = Saved. SSP. 2. Push PSR and PC to Supervisor Stack. 3. Set PSR[15] = 0 (supervisor mode). 4. Set PSR[10: 8] = priority of interrupt being serviced. 5. Set PSR[2: 0] = 0. 6. Set MAR = x 01 vv, where vv = 8 -bit interrupt vector provided by interrupting device (e. g. , keyboard = x 80). 7. Load memory location (M[x 01 vv]) into MDR. 8. Set PC = MDR; now first instruction of ISR will be fetched. Note: This all happens between the STORE RESULT of the last user instruction and the FETCH of the first ISR instruction.

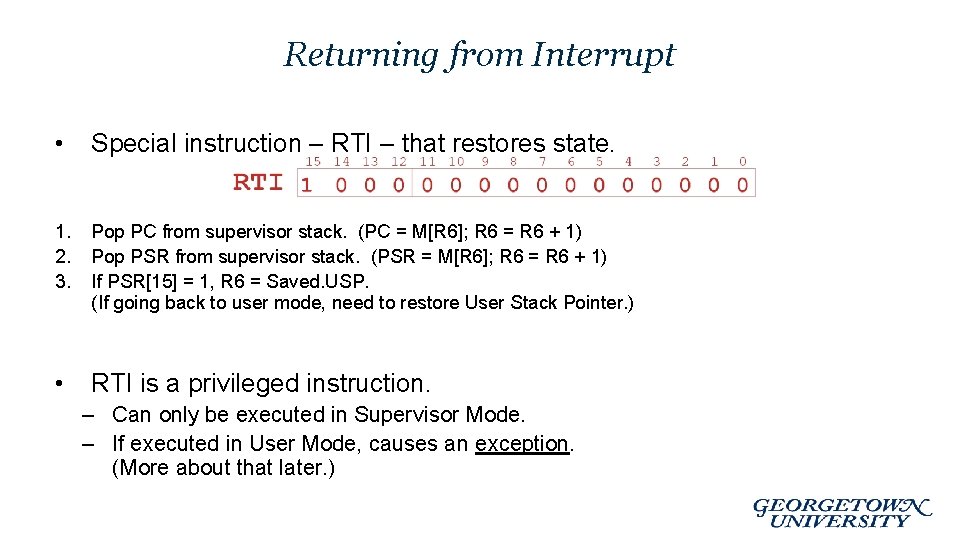

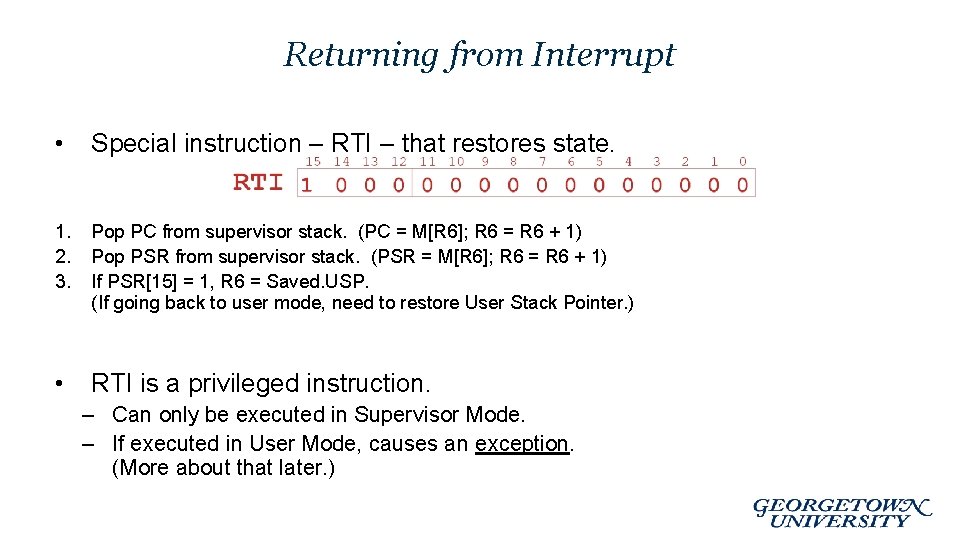

Returning from Interrupt • Special instruction – RTI – that restores state. 1. 2. 3. Pop PC from supervisor stack. (PC = M[R 6]; R 6 = R 6 + 1) Pop PSR from supervisor stack. (PSR = M[R 6]; R 6 = R 6 + 1) If PSR[15] = 1, R 6 = Saved. USP. (If going back to user mode, need to restore User Stack Pointer. ) • RTI is a privileged instruction. – Can only be executed in Supervisor Mode. – If executed in User Mode, causes an exception. (More about that later. )

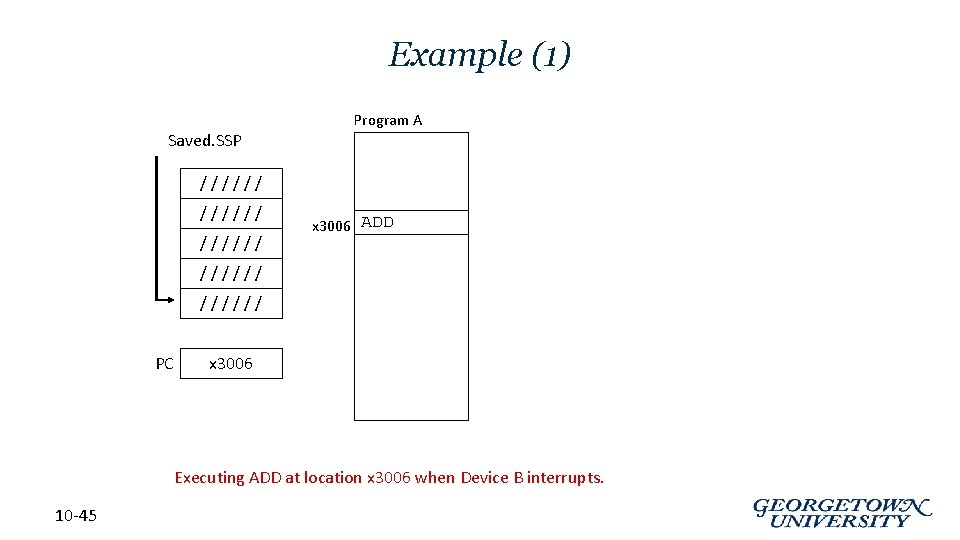

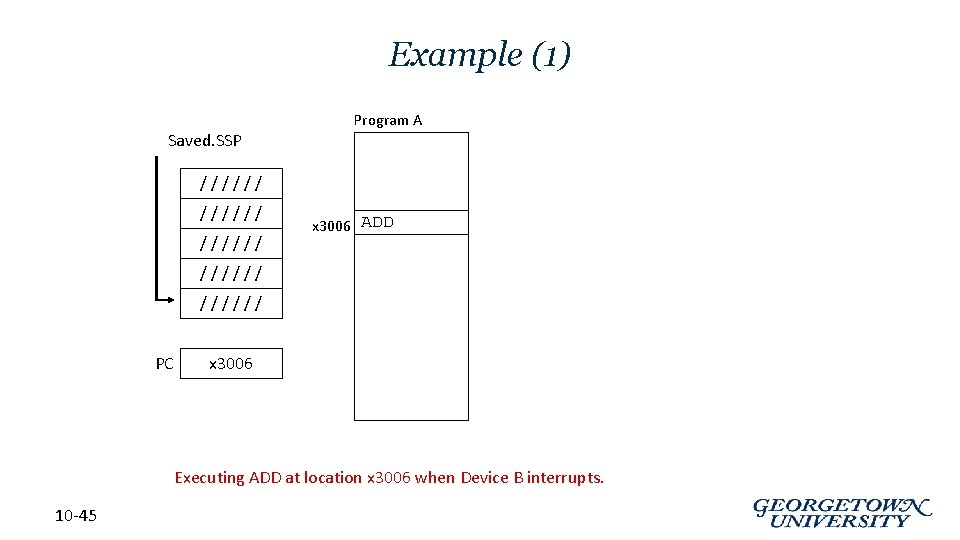

Example (1) Saved. SSP Program A ////// x 3006 ADD ////// PC x 3006 Executing ADD at location x 3006 when Device B interrupts. 10 -45

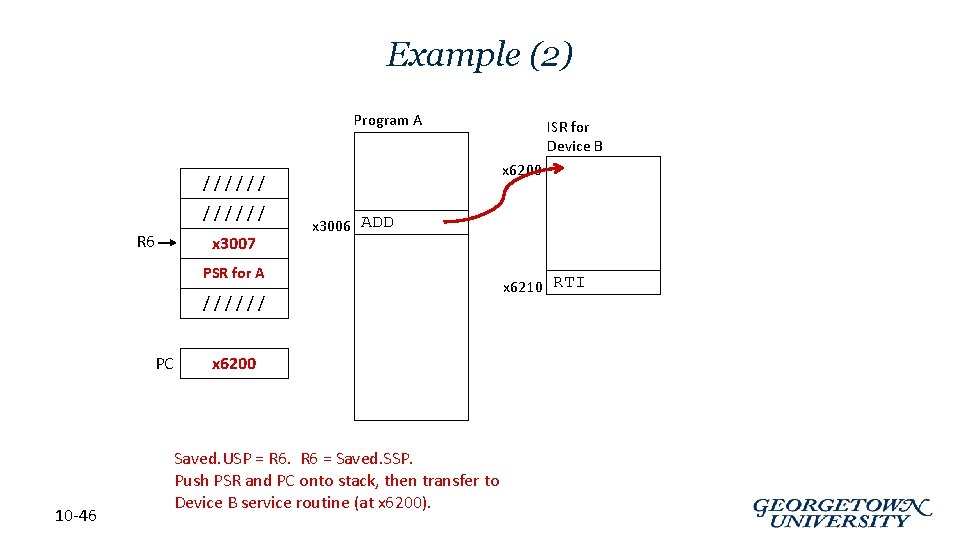

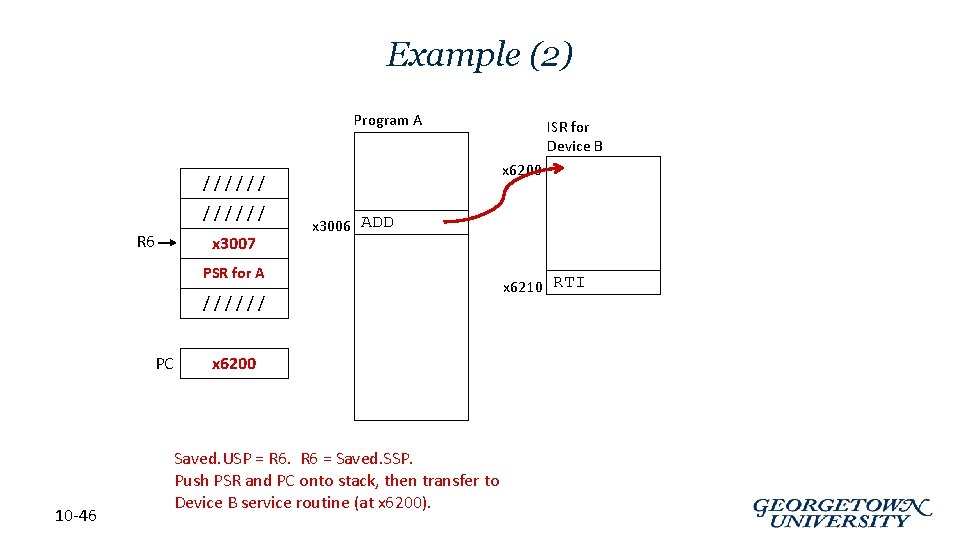

Example (2) Program A x 6200 ////// R 6 x 3007 x 3006 ADD PSR for A ////// PC 10 -46 ISR for Device B x 6200 Saved. USP = R 6 = Saved. SSP. Push PSR and PC onto stack, then transfer to Device B service routine (at x 6200). x 6210 RTI

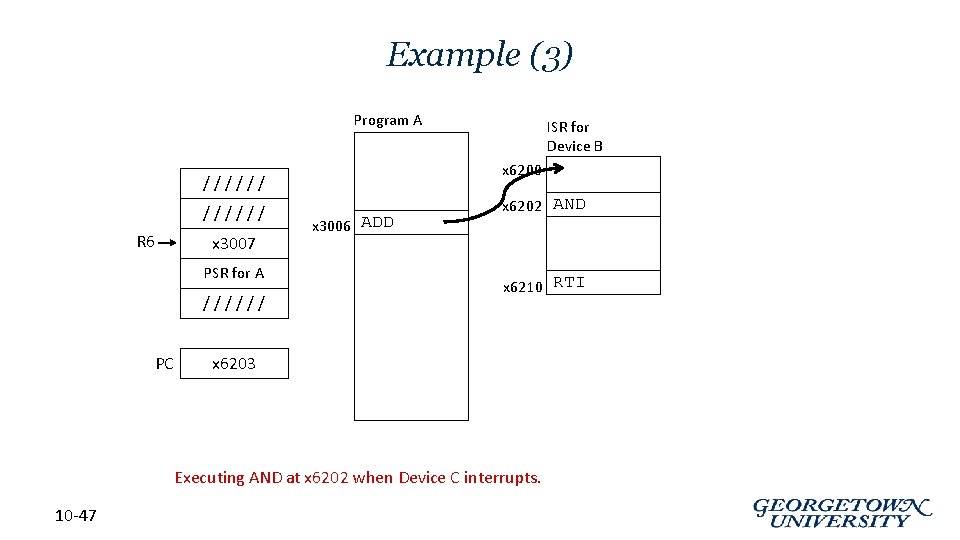

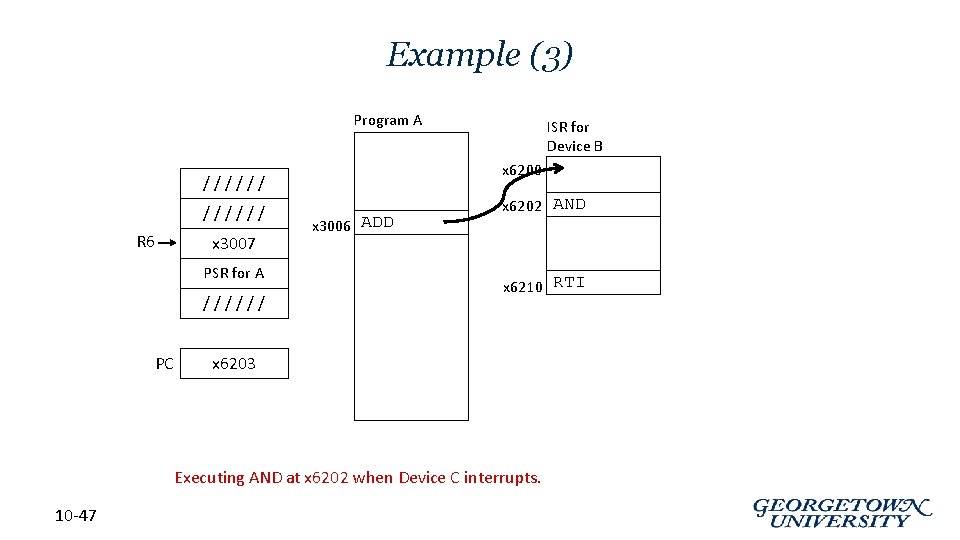

Example (3) Program A x 6200 ////// R 6 x 3007 PSR for A ////// PC ISR for Device B x 3006 ADD x 6202 AND x 6210 RTI x 6203 Executing AND at x 6202 when Device C interrupts. 10 -47

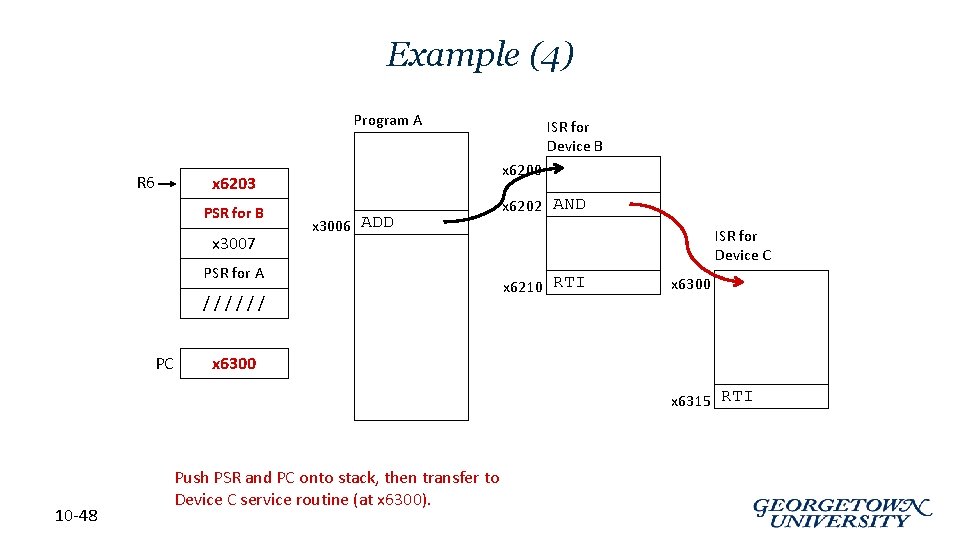

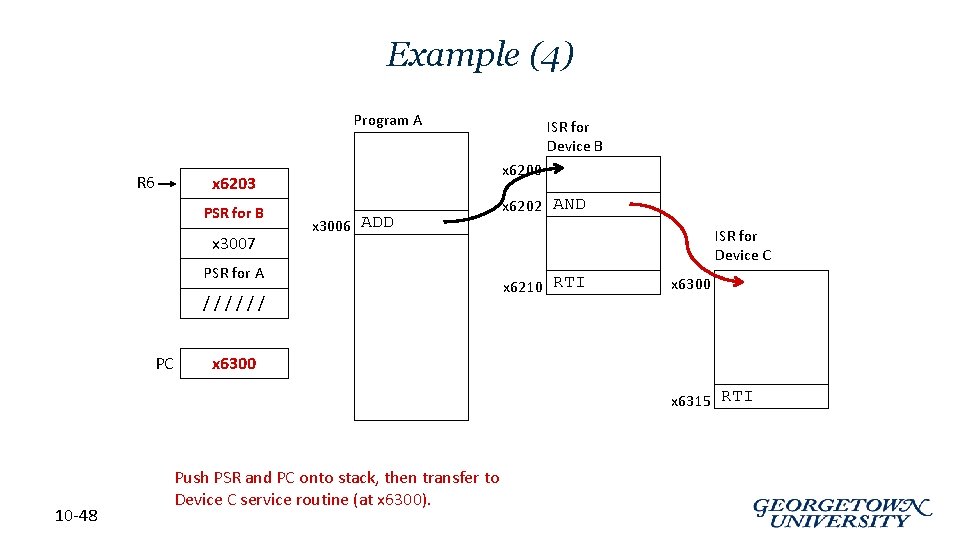

Example (4) Program A R 6 x 6200 x 6203 PSR for B x 3007 x 3006 ADD PSR for A ////// PC ISR for Device B x 6202 AND ISR for Device C x 6210 RTI x 6300 x 6315 RTI 10 -48 Push PSR and PC onto stack, then transfer to Device C service routine (at x 6300).

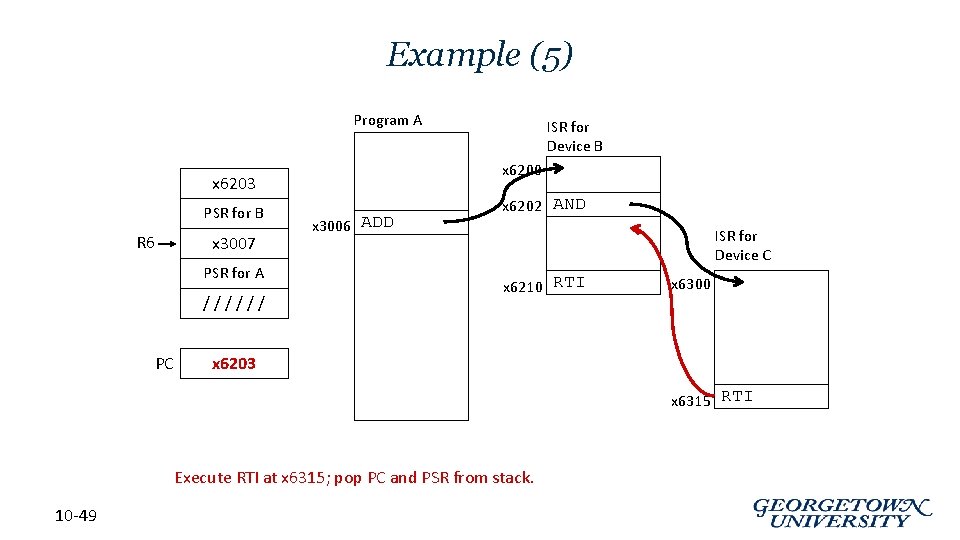

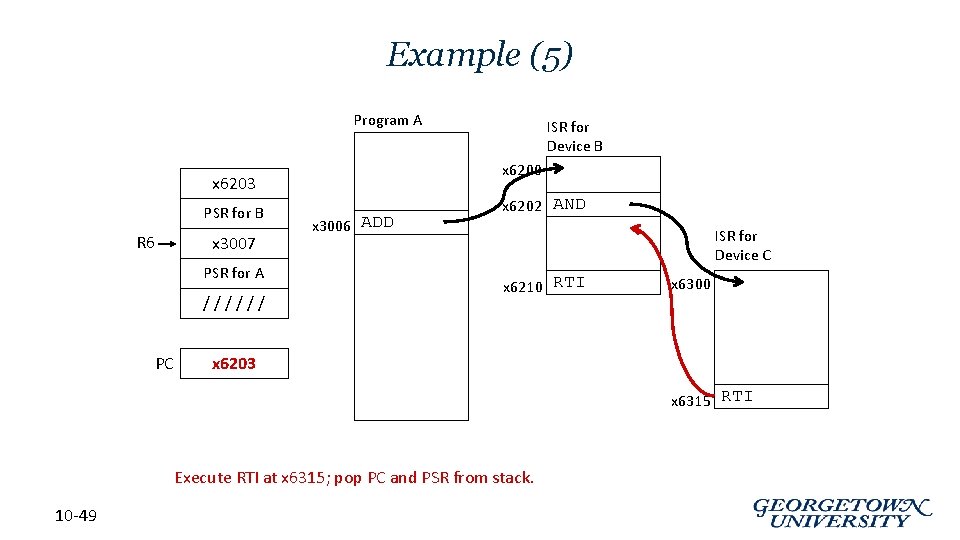

Example (5) Program A x 6200 x 6203 PSR for B R 6 x 3007 PSR for A ////// PC ISR for Device B x 3006 ADD x 6202 AND ISR for Device C x 6210 RTI x 6300 x 6203 x 6315 RTI Execute RTI at x 6315; pop PC and PSR from stack. 10 -49

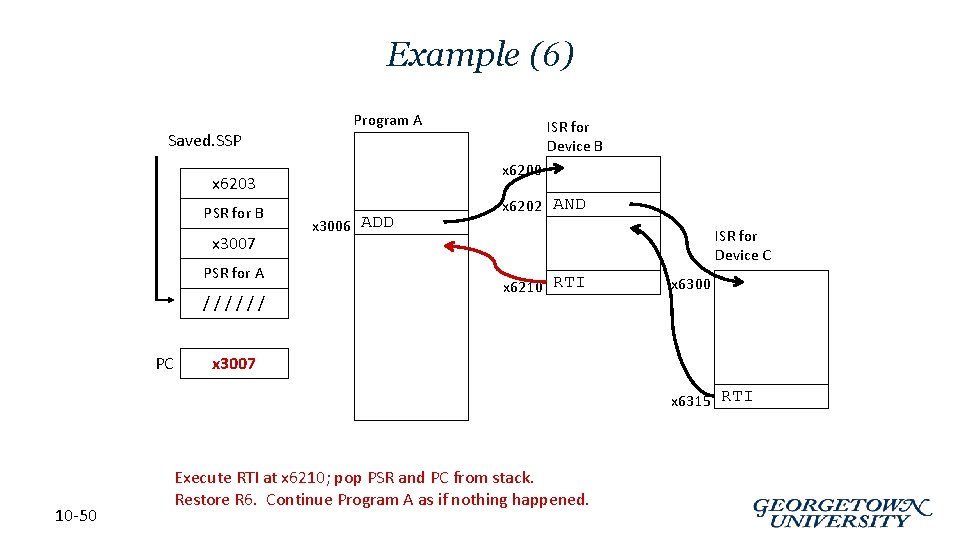

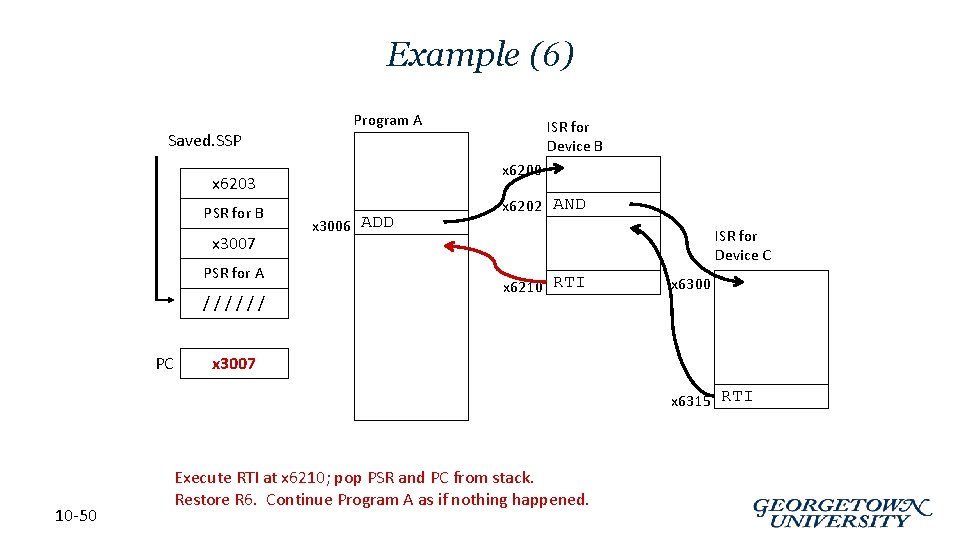

Example (6) Saved. SSP Program A x 6200 x 6203 PSR for B x 3007 PSR for A ////// PC ISR for Device B x 3006 ADD x 6202 AND ISR for Device C x 6210 RTI x 6300 x 3007 x 6315 RTI 10 -50 Execute RTI at x 6210; pop PSR and PC from stack. Restore R 6. Continue Program A as if nothing happened.

Exception: Internal Interrupt • When something unexpected happens inside the processor, it may cause an exception. • Examples: – – Privileged operation (e. g. , RTI in user mode) Executing an illegal opcode Divide by zero Accessing an illegal address (e. g. , protected system memory) • Handled just like an interrupt – Vector is determined internally by type of exception – Priority is the same as running program 10 -51