CORSO DI SIMULAZIONE ELETTRONICA Studenti Riccardo Arduini Andrea

- Slides: 29

CORSO DI SIMULAZIONE ELETTRONICA Studenti: Riccardo Arduini, Andrea Crea, Marco Dina, Francesco Fondi, Flavio Giorgianni, Giorgio Grilli, Matteo Lanni, Matteo Mancini, Noemi Marinelli, Daniele Pecchia, Gianluca Prosperi, Michele Ricci, Adriano Rita, Alessio Staffoli, Luca Tagnani, Roberto Testa, Alessio Volpini, Tutors: G. Corradi, M. Bazzi, D. Tagnani

Stage 2006 Obiettivi • Corso di Simulazione elettronica • Esercitazioni tramite il simulatore Pspice • Simulazione di filtri (integratori e derivatori), circuiti risonanti, diodi e circuiti di polarizzazione dei transistor. • Analisi termica di vari circuiti elettronici. • Progetto di un buffer in classe a b • Progetto di un pcb

Definire un circuito elettrico • Si possono creare modelli tramite il modellatore di SPICE • È possibile creare nuovi modelli di componenti tramite opportuni linguaggi “verilog” oppure il più diffuso “VHDL” • Disposti i componenti elettronici, devono essere collegati tra di loro come se fosse un circuito elettrico fisico • Si devono collegare le alimentazioni e le sorgenti di segnale • È obbligatorio connettere sempre una massa di riferimento alla quale si riferiscono tutti i generatori di tensione e di segnale • Ovviamente le modalità di connessione e di inserimento dati dipendono dal tipo di versione di SPICE

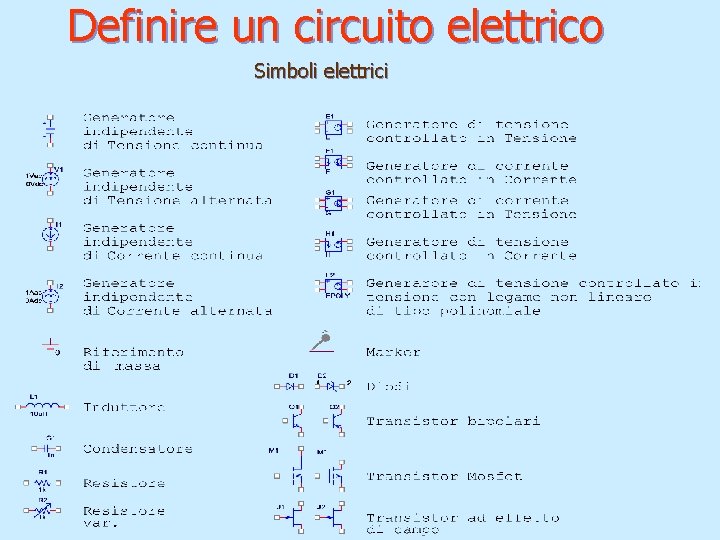

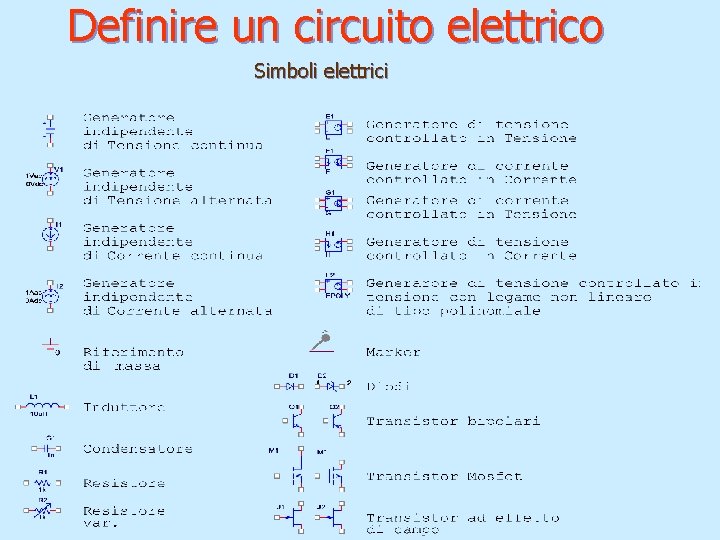

Definire un circuito elettrico Simboli elettrici

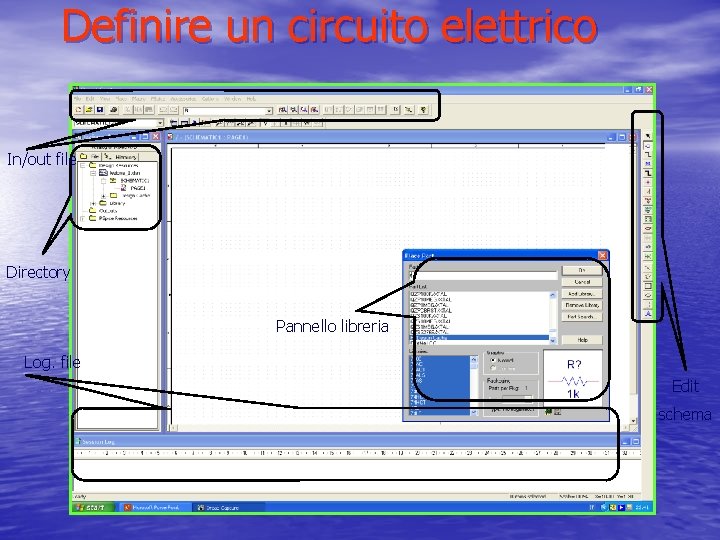

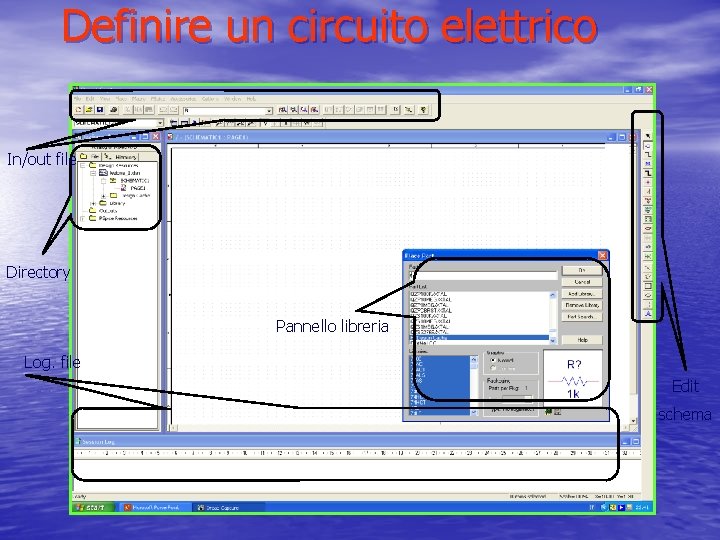

Definire un circuito elettrico In/out file Directory Pannello libreria Log. file Edit schema

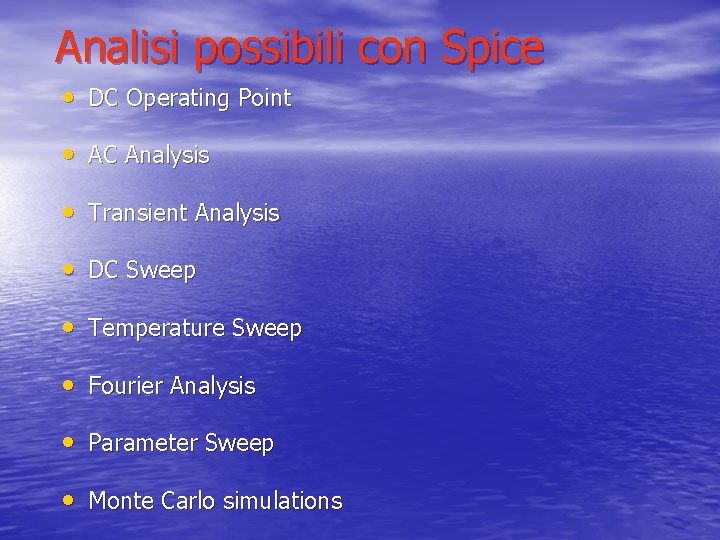

Analisi possibili con Spice • DC Operating Point • AC Analysis • Transient Analysis • DC Sweep • Temperature Sweep • Fourier Analysis • Parameter Sweep • Monte Carlo simulations

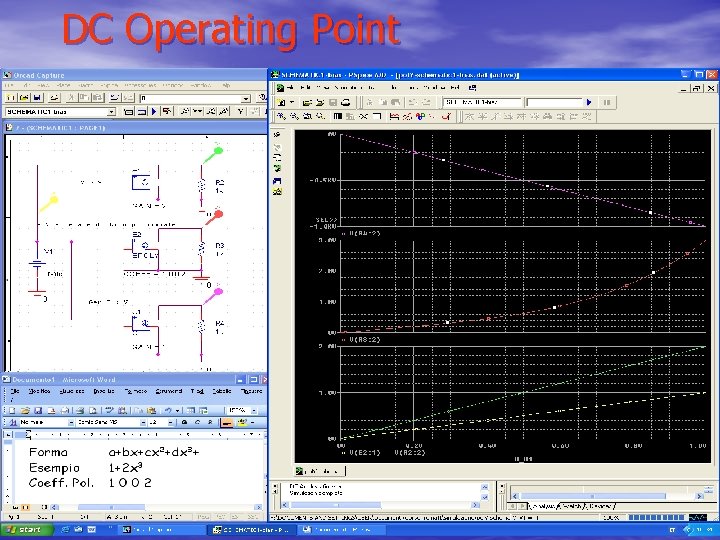

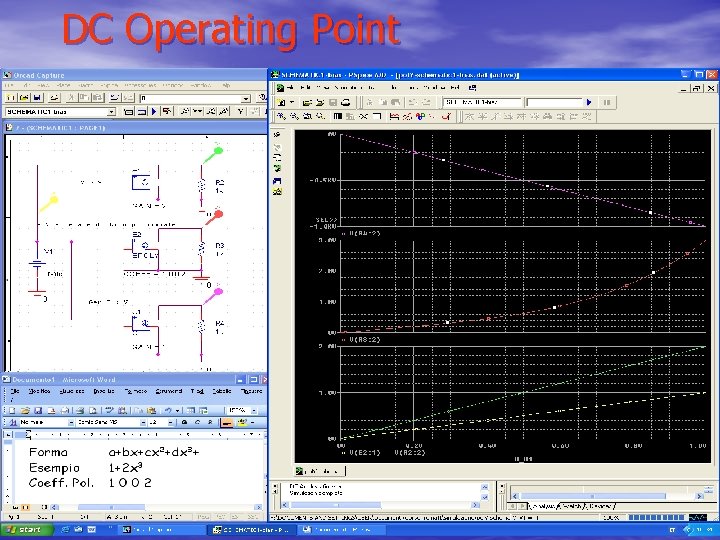

DC Operating Point

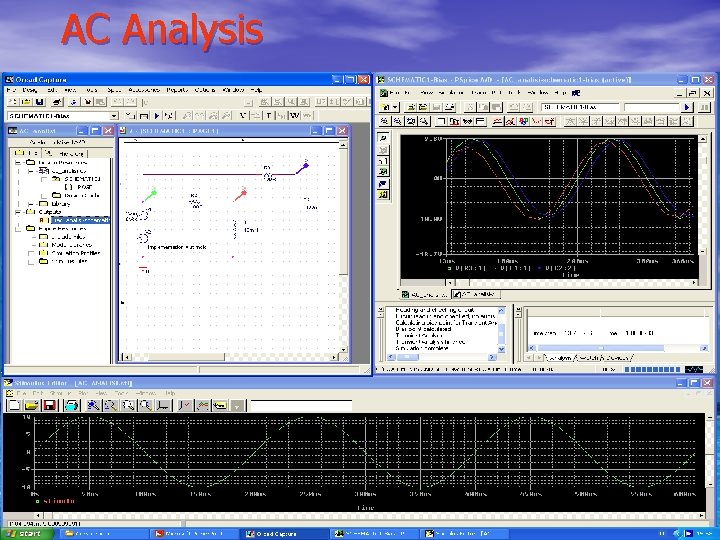

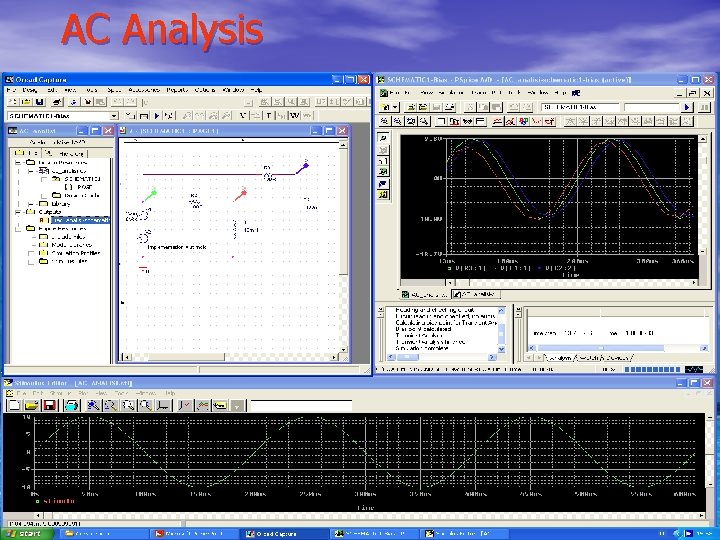

AC Analysis

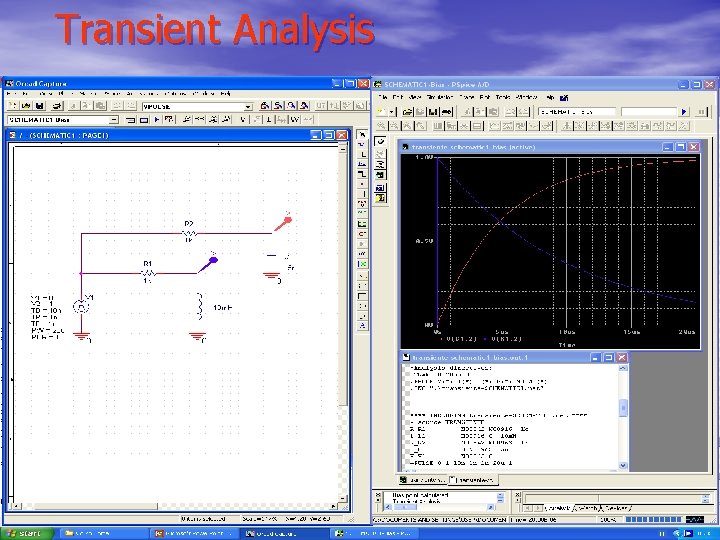

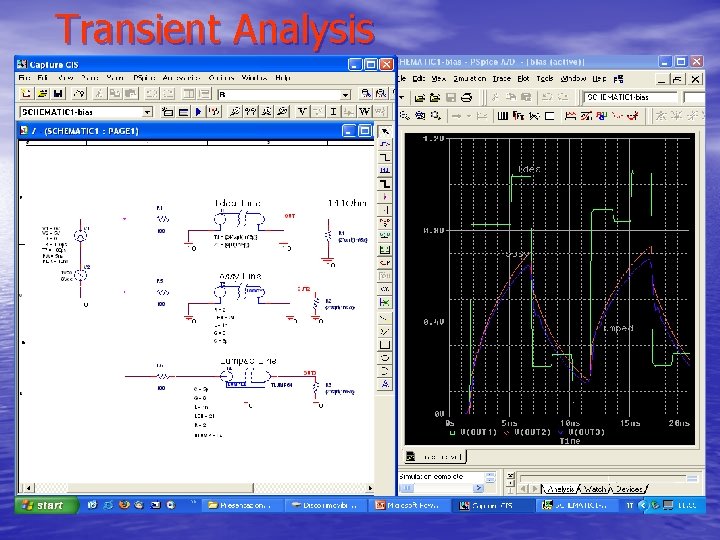

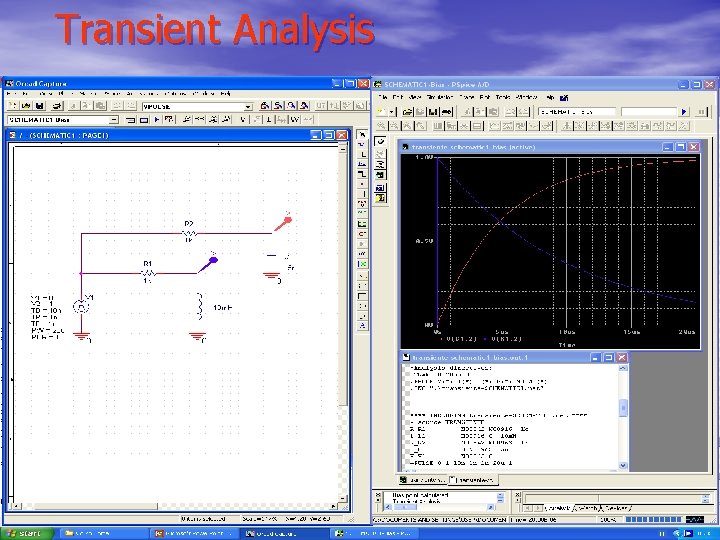

Transient Analysis

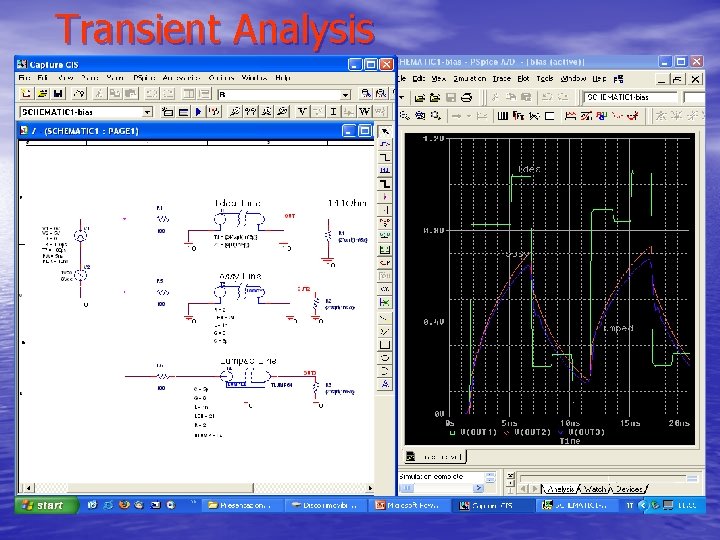

Transient Analysis

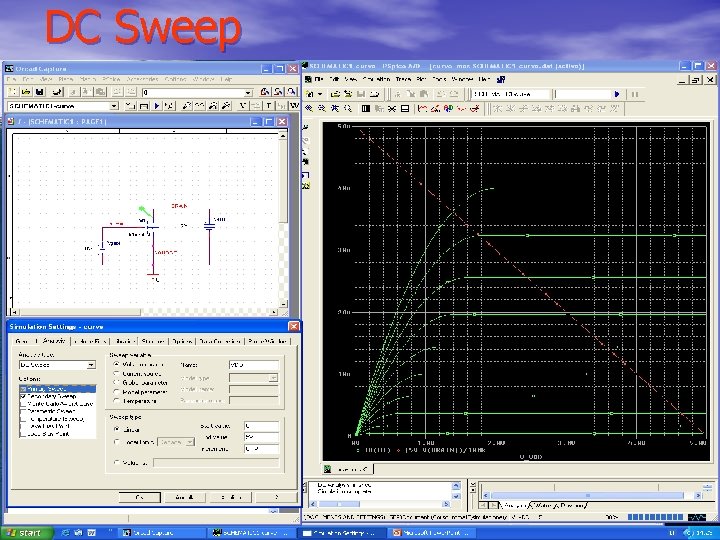

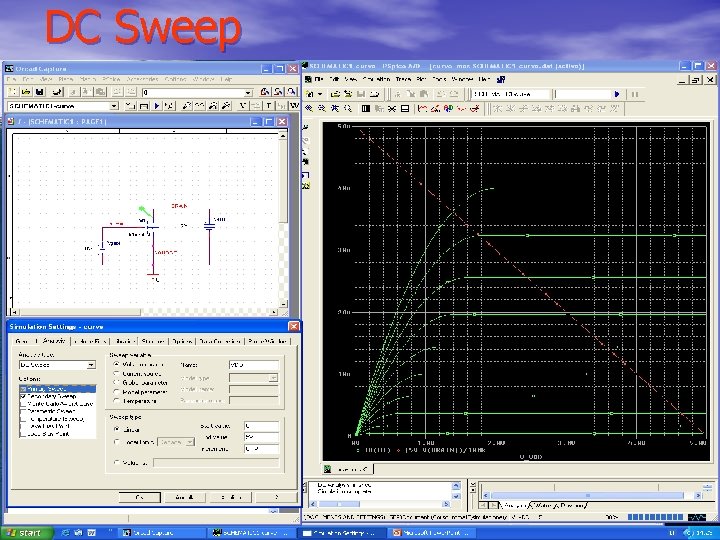

DC Sweep

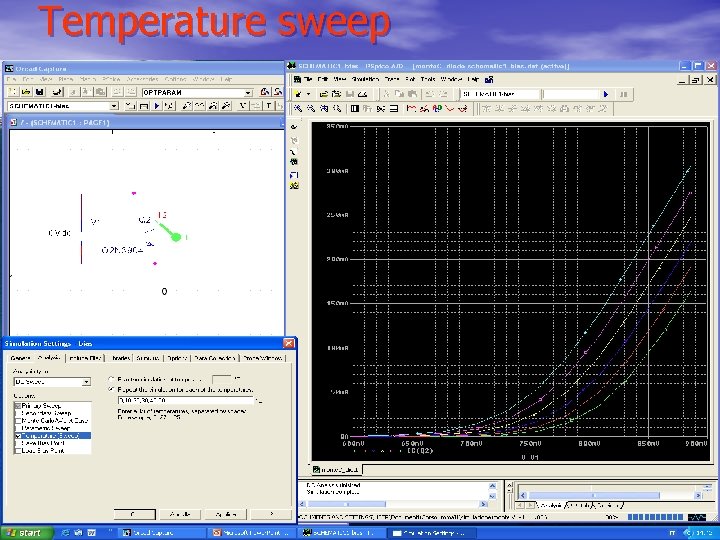

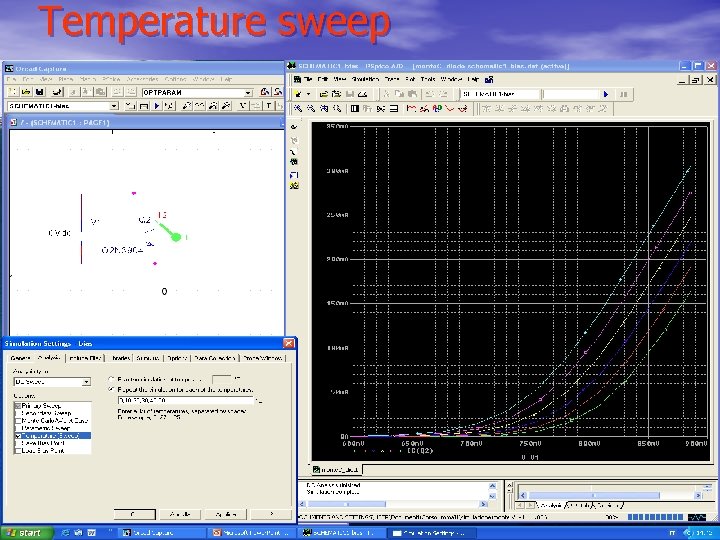

Temperature sweep

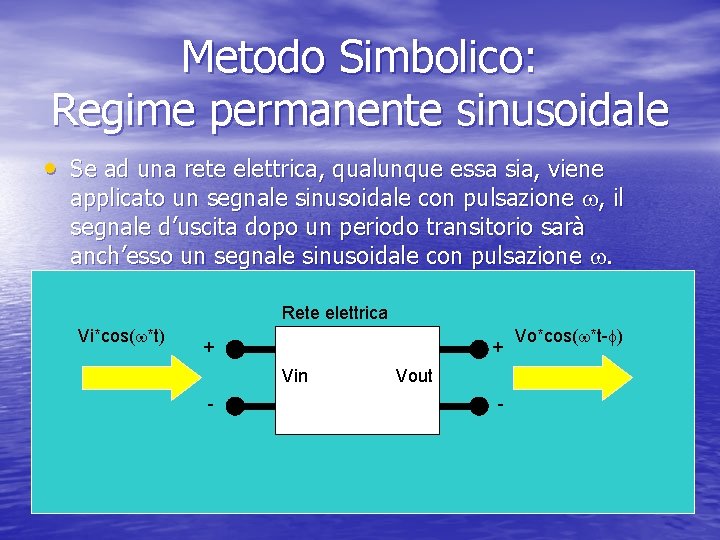

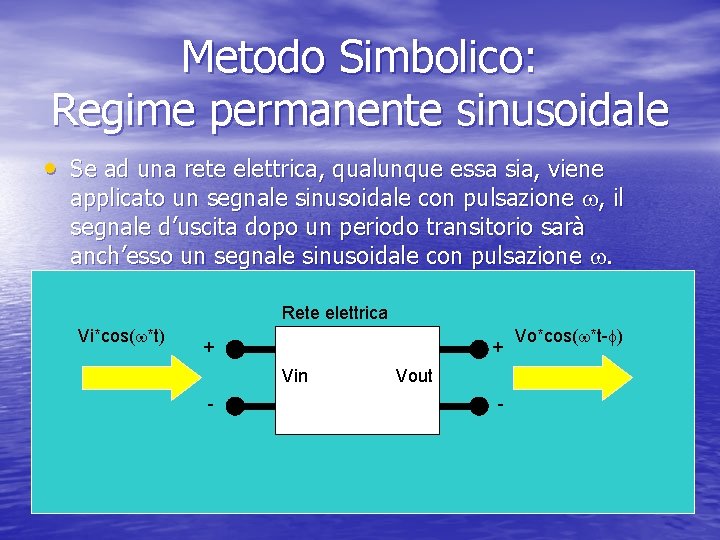

Metodo Simbolico: Regime permanente sinusoidale • Se ad una rete elettrica, qualunque essa sia, viene applicato un segnale sinusoidale con pulsazione w, il segnale d’uscita dopo un periodo transitorio sarà anch’esso un segnale sinusoidale con pulsazione w. Rete elettrica Vi*cos(w*t) + + Vin - Vout - Vo*cos(w*t-f)

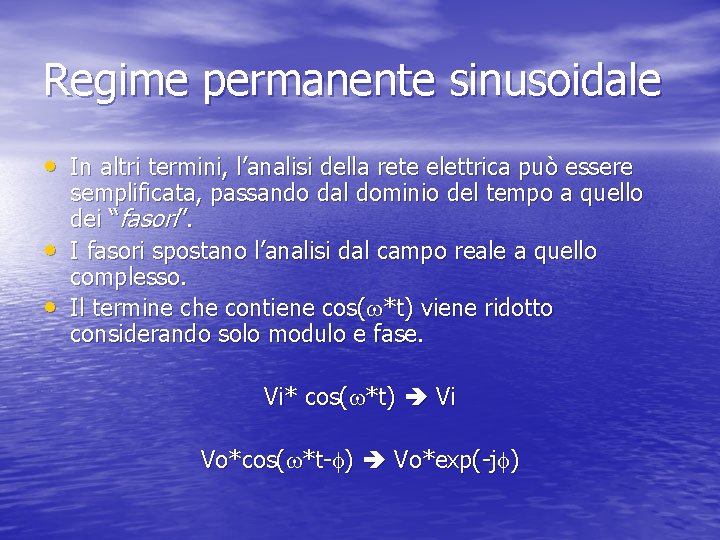

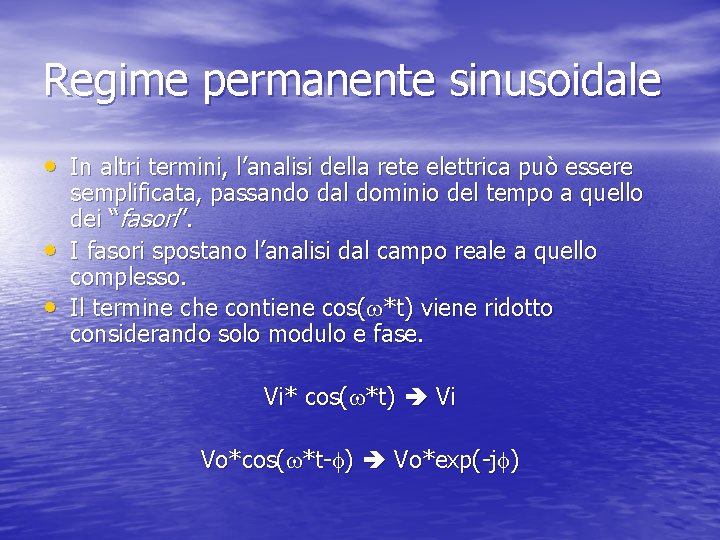

Regime permanente sinusoidale • In altri termini, l’analisi della rete elettrica può essere • • semplificata, passando dal dominio del tempo a quello dei “fasori”. I fasori spostano l’analisi dal campo reale a quello complesso. Il termine che contiene cos(w*t) viene ridotto considerando solo modulo e fase. Vi* cos(w*t) Vi Vo*cos(w*t-f) Vo*exp(-jf)

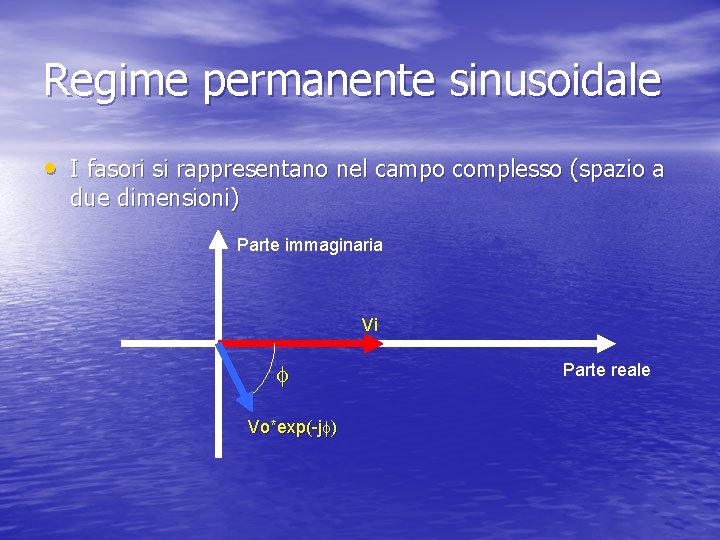

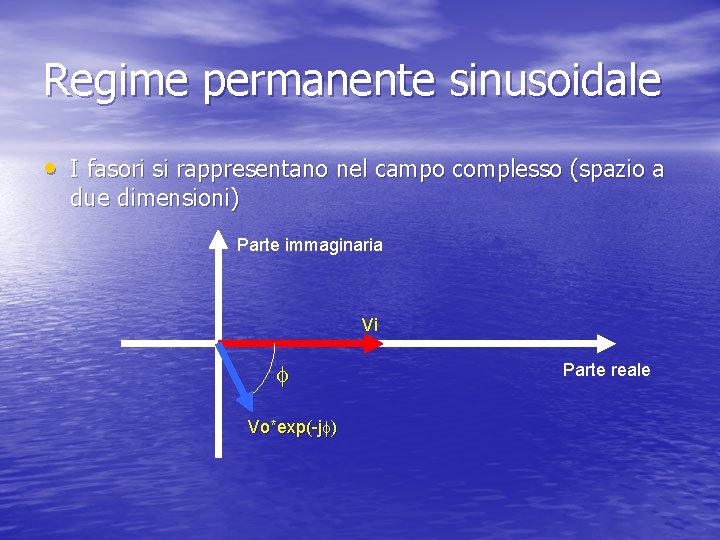

Regime permanente sinusoidale • I fasori si rappresentano nel campo complesso (spazio a due dimensioni) Parte immaginaria Vi f Vo*exp(-jf) Parte reale

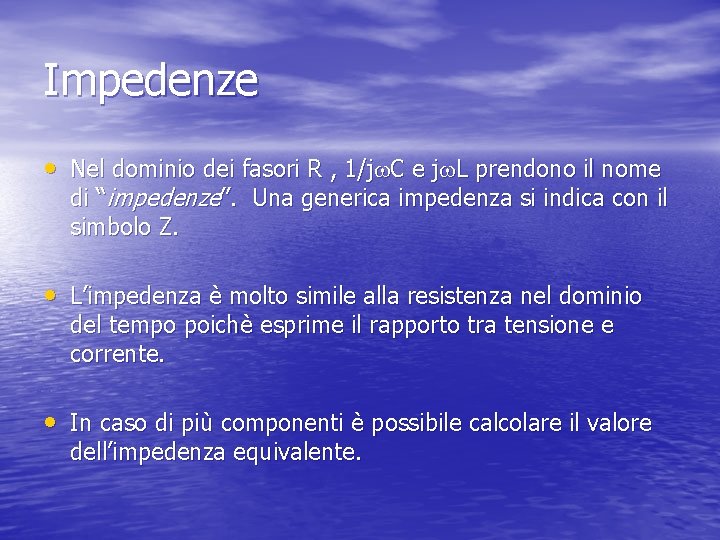

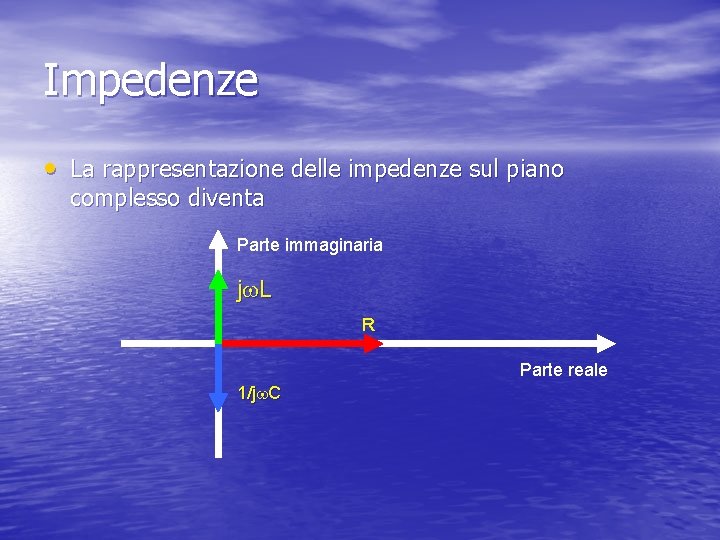

Impedenze • Nel dominio dei fasori R , 1/jw. C e jw. L prendono il nome di “impedenze”. Una generica impedenza si indica con il simbolo Z. • L’impedenza è molto simile alla resistenza nel dominio del tempo poichè esprime il rapporto tra tensione e corrente. • In caso di più componenti è possibile calcolare il valore dell’impedenza equivalente.

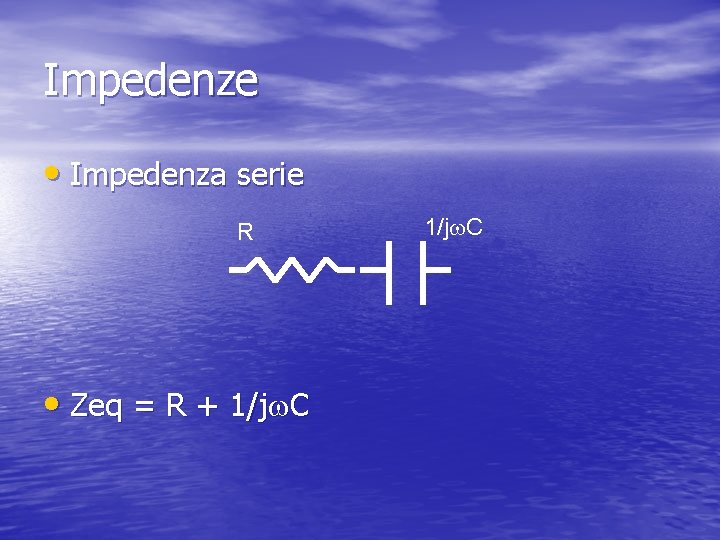

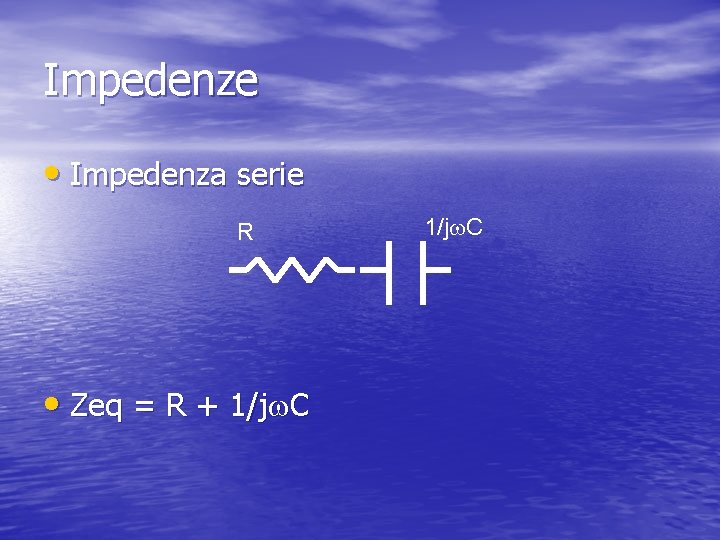

Impedenze • Impedenza serie R • Zeq = R + 1/jw. C

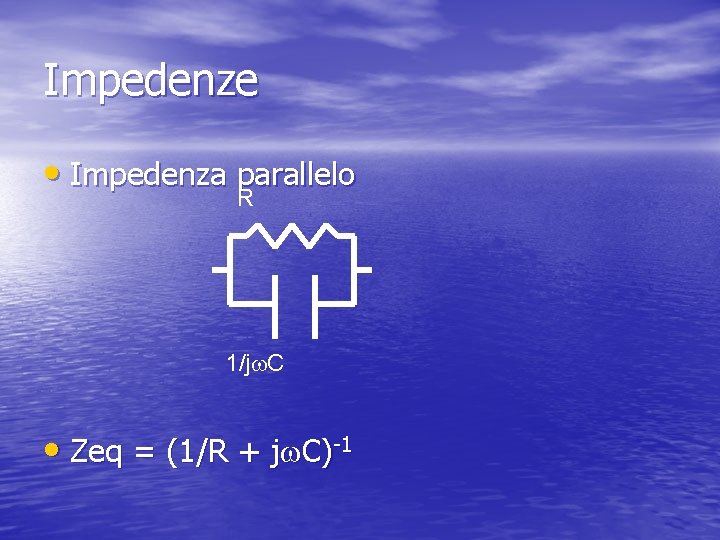

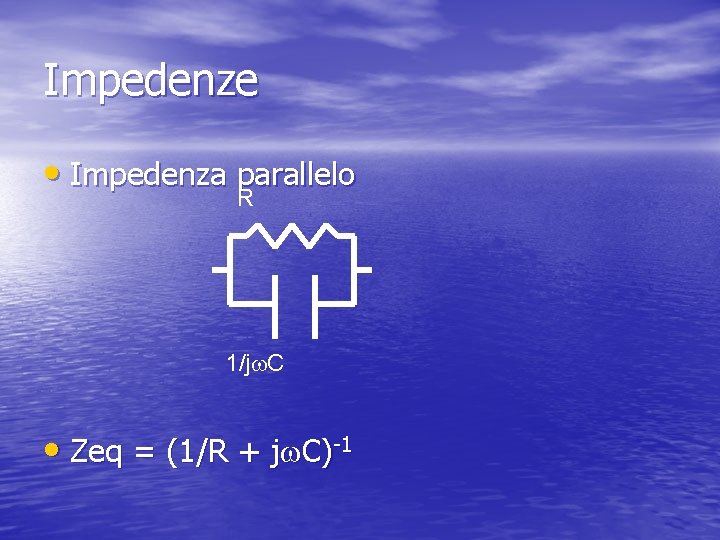

Impedenze • Impedenza parallelo R 1/jw. C • Zeq = (1/R + jw. C)-1

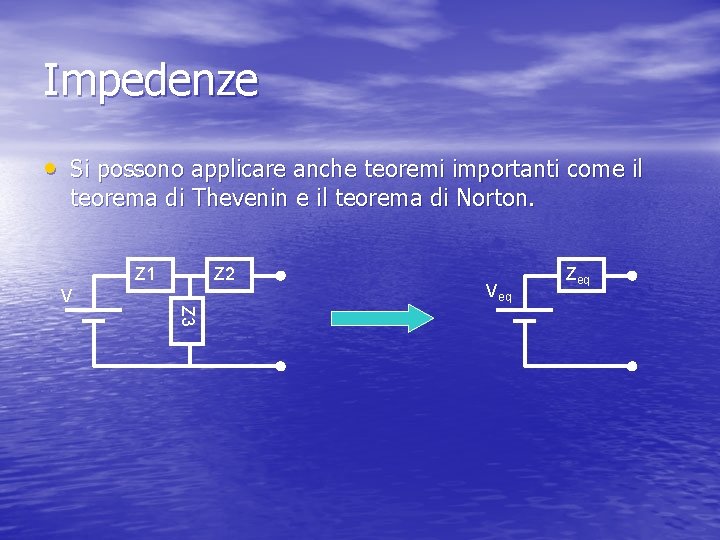

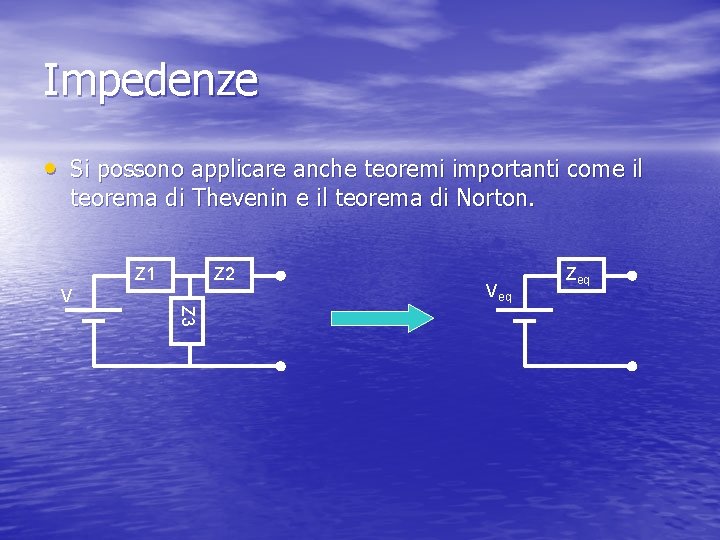

Impedenze • Si possono applicare anche teoremi importanti come il teorema di Thevenin e il teorema di Norton. Z 1 Z 3 V Z 2 Veq Zeq

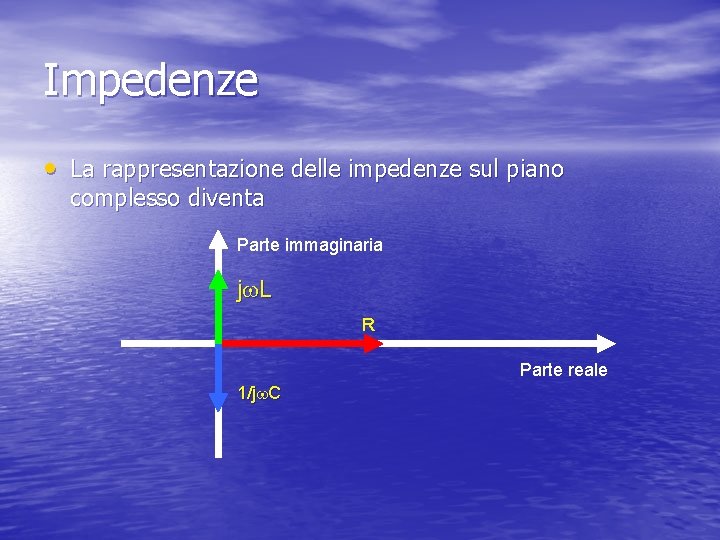

Impedenze • La rappresentazione delle impedenze sul piano complesso diventa Parte immaginaria j w. L R Parte reale 1/jw. C

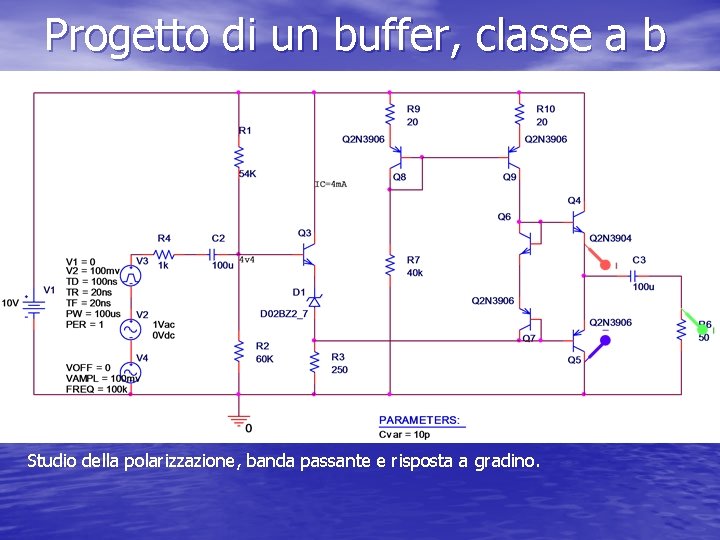

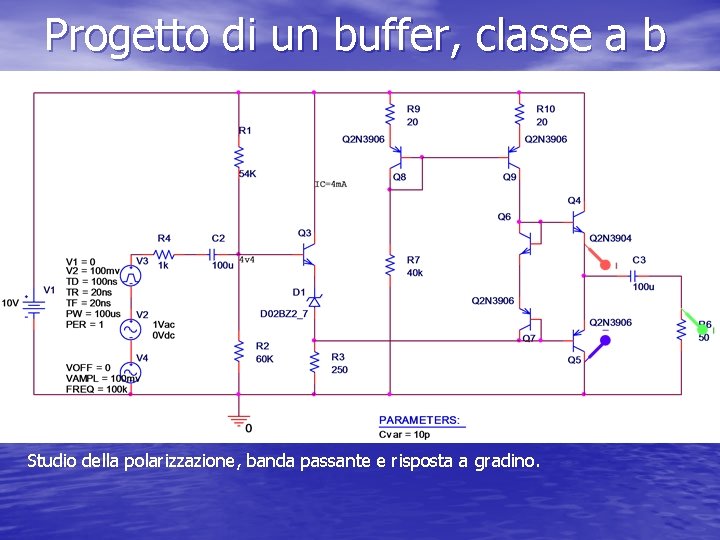

Progetto di un buffer, classe a b Studio della polarizzazione, banda passante e risposta a gradino.

Misura delle correnti di uscita. polarizzazione dei BJT di uscita.

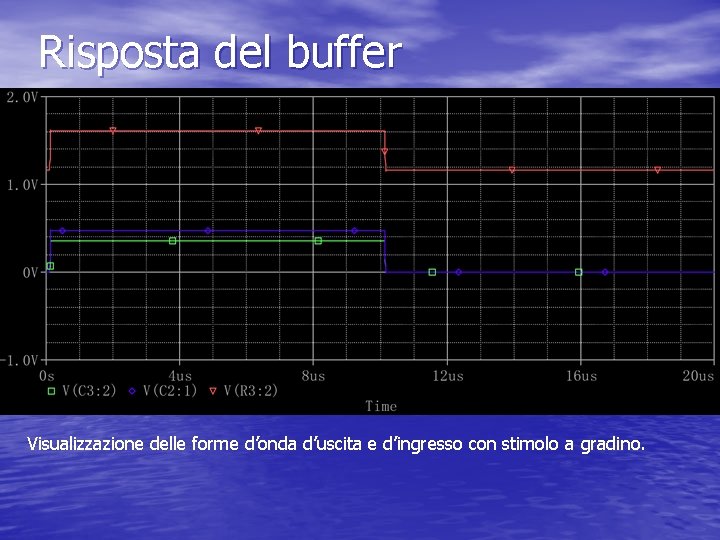

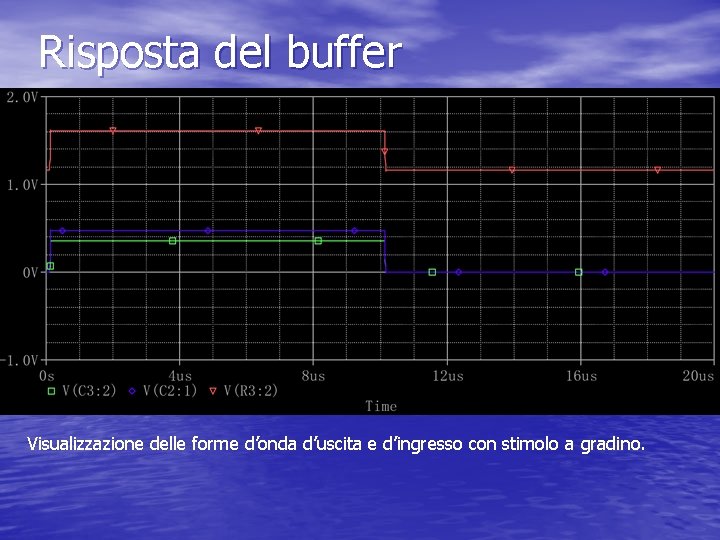

Risposta del buffer Visualizzazione delle forme d’onda d’uscita e d’ingresso con stimolo a gradino.

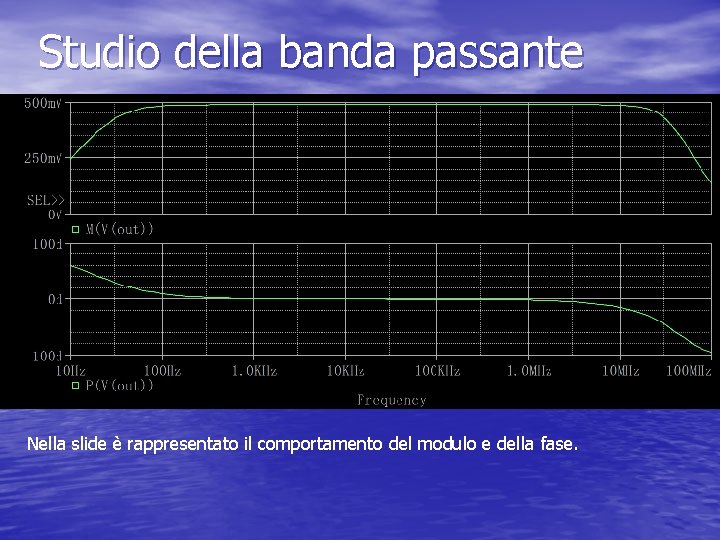

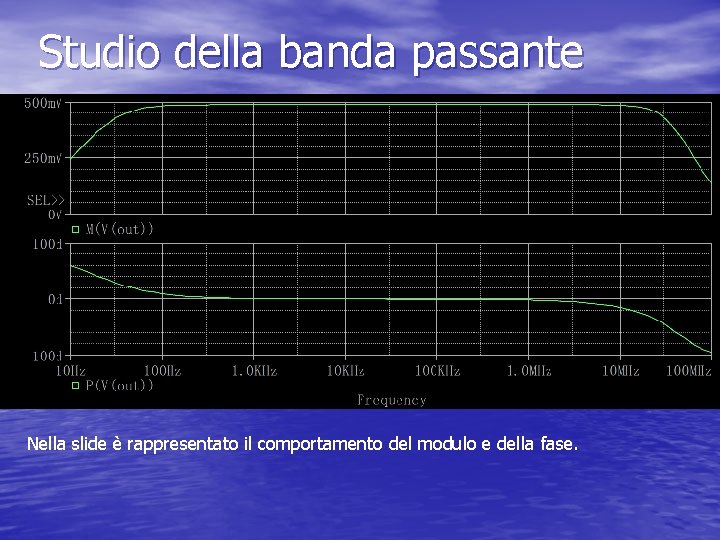

Studio della banda passante Nella slide è rappresentato il comportamento del modulo e della fase.

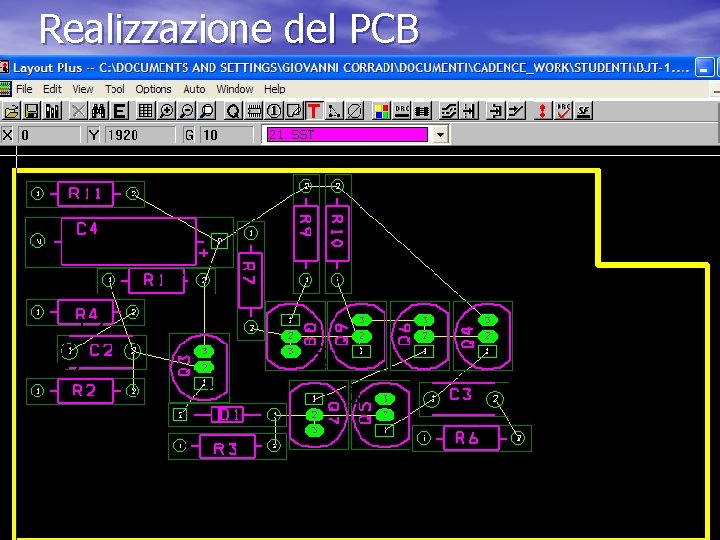

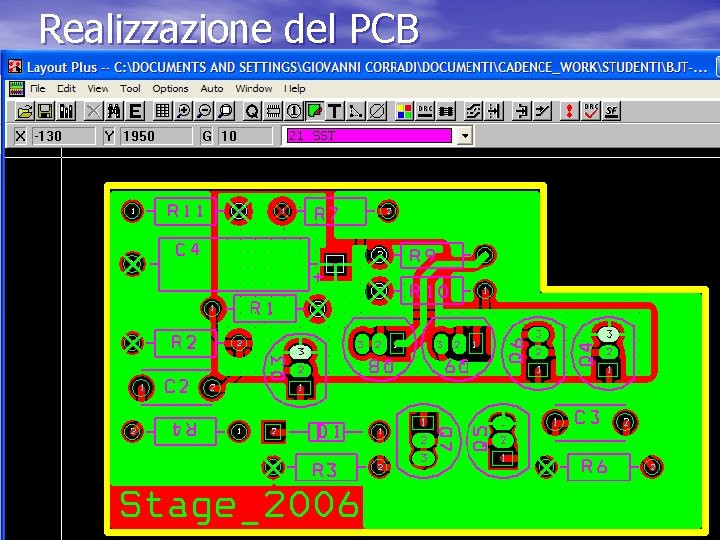

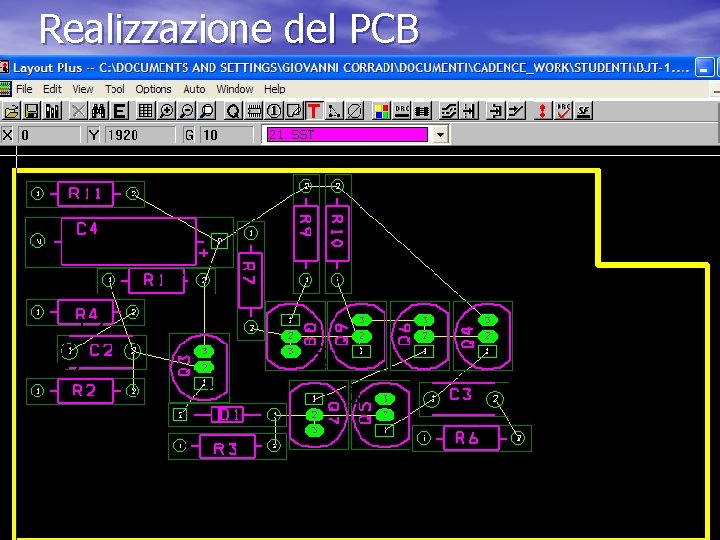

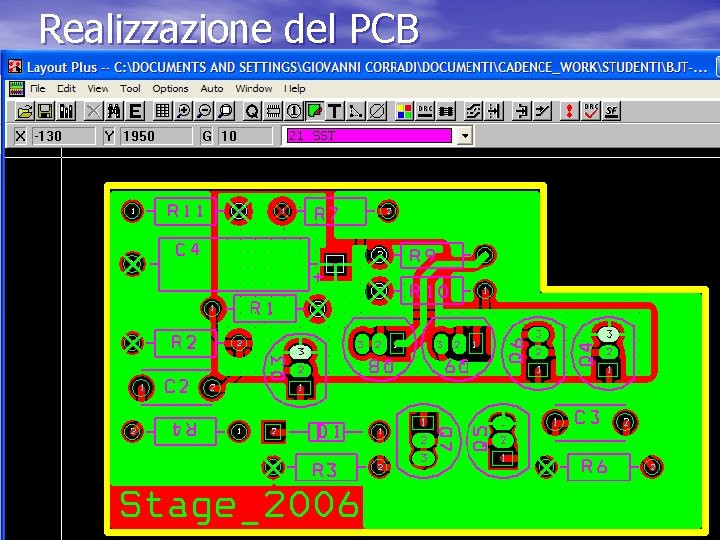

Realizzazione del PCB

Realizzazione del PCB • Assegnazione dei footprint • Studio delle dimensioni • Importazione dei componenti in modo automatico a PCB layout • Studio della disposizione dei componenti ottimizzando capacità e induttanze di perdita • Connessioni tramite piste dei nodi

Realizzazione del PCB

CONCLUSIONI • Durante questa esperienza formativa, abbiamo analizzato il comportamento di alcuni circuiti elettronici, tramite un simulatore virtuale: “SPICE” e realizzato il progetto di un buffer. L’ obbiettivo principale: • nonostante il poco tempo a disposizione e vista la difficolta’ e vastita’ degli argomenti presentati, rimaneva quello di stimolare la nostra curiosita’ per prendere coscienza della complessita’ del meraviglioso mondo della progettazione elettronica. • Grazie alle dispenze che ci sono state fornite, abbiamo potuto affrontare al meglio tutte le problematiche si sono presentate durante la progettazione. • Nel tentativo di conseguire questo ambizioso traguardo si e’ voluto aumentare la voglia di comprendere meglio la tecnologia elettronica che ci circonda.

RINGRAZIAMENTI • tutta l’organizzazione del SIS-Divulgazione, per l’efficienza dell’ organizzazione e accoglienza; • i nostri tutors G. Corradi, D. Tagnani, M. Bazzi; • i nostri professori per essersi impegnati nella realizzazione dello stage; • Il Professore Mario Calvetti Direttore dell’ INFN per la sua disponibilita’ allo svolgimento dei corsi