CORPORATE INSTITUTE OF SCIENCE TECHNOLOGY BHOPAL DEPARTMENT OF

CORPORATE INSTITUTE OF SCIENCE & TECHNOLOGY , BHOPAL DEPARTMENT OF ELECTRONICS & COMMUNICATIONS MICRO CODED CONTROLLER - PROF. RAKESH K. JHA 1

ALTERNATIVES FOR CONTROL UNIT (CU) Hard-wired (hardware) Random logic, programmable logic array (PLA), or ROM Fast Inflexible Firmware Microprogrammed or microcoded CU Control implemented like a computer (microcomputer) Microinstructions Microprogramming Flexible Changes to instruction set possible Completely different instruction sets can be emulated Speed limited by microcomputer memory 2

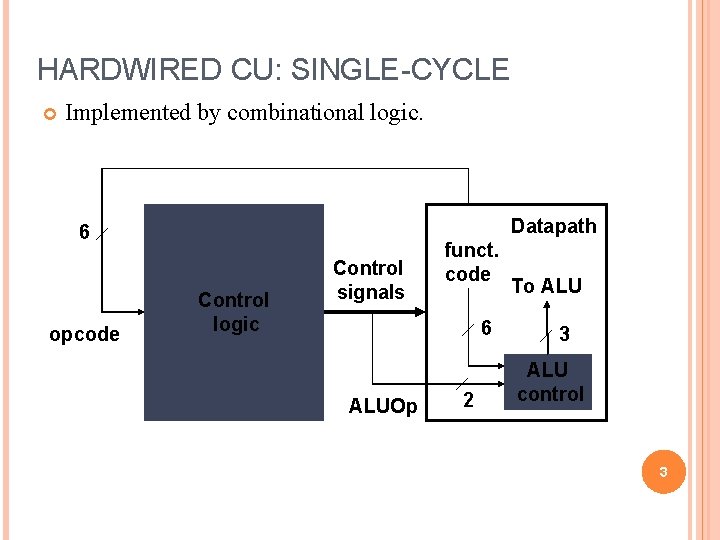

HARDWIRED CU: SINGLE-CYCLE Implemented by combinational logic. Datapath 6 opcode Control logic Control signals funct. code 6 ALUOp 2 To ALU 3 ALU control 3

16 -20 Single-cycle Datapath 0 -15 0 -5 11 -15 0 mux 1 1 mux 0 ALU Memto. Reg ALUSrc zero Mem. Write Mem. Read Data mem. 0 mux 1 Instr. mem. Reg. Write ALU PC 1 mux 0 21 -25 1 mux 0 26 -31 Branch Reg. File opcode Jump Shift left 2 CONTROL 4 Add 0 -25 Reg. Dst Sign ext. Shift left 2 ALUOp ALU Cont. 4

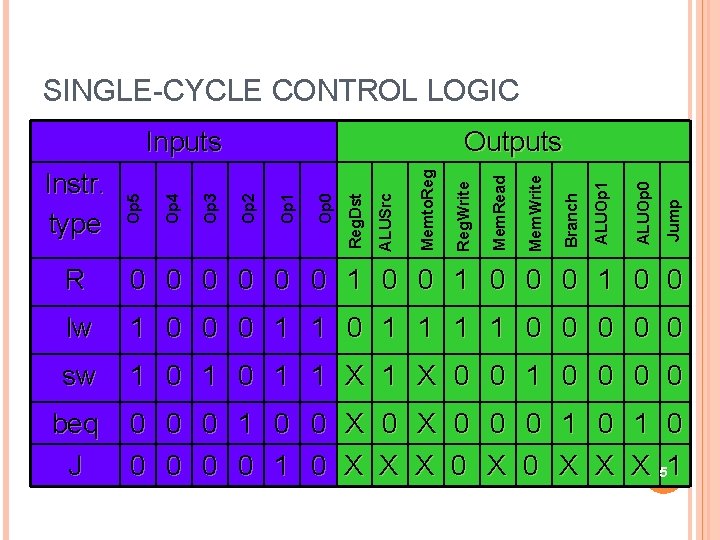

SINGLE-CYCLE CONTROL LOGIC Jump ALUOp 0 ALUOp 1 Branch Mem. Write Mem. Read Reg. Write Memto. Reg ALUSrc Reg. Dst Op 0 Op 1 Outputs Op 2 Op 3 Op 4 Instr. type Op 5 Inputs R 0 0 0 1 0 0 lw 1 0 0 0 1 1 1 1 0 0 0 sw 1 0 1 1 X 0 0 1 0 0 beq J 0 0 0 1 0 0 X 0 0 0 1 0 X X X 51

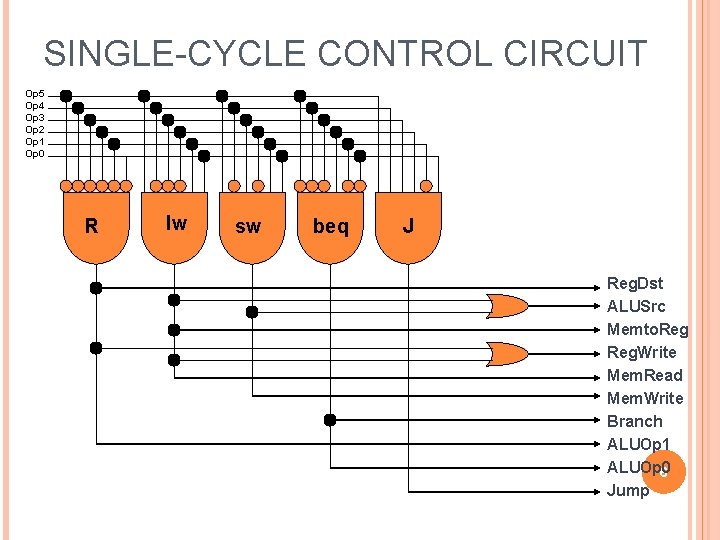

SINGLE-CYCLE CONTROL CIRCUIT Op 5 Op 4 Op 3 Op 2 Op 1 Op 0 R lw sw beq J Reg. Dst ALUSrc Memto. Reg. Write Mem. Read Mem. Write Branch ALUOp 1 ALUOp 0 6 Jump

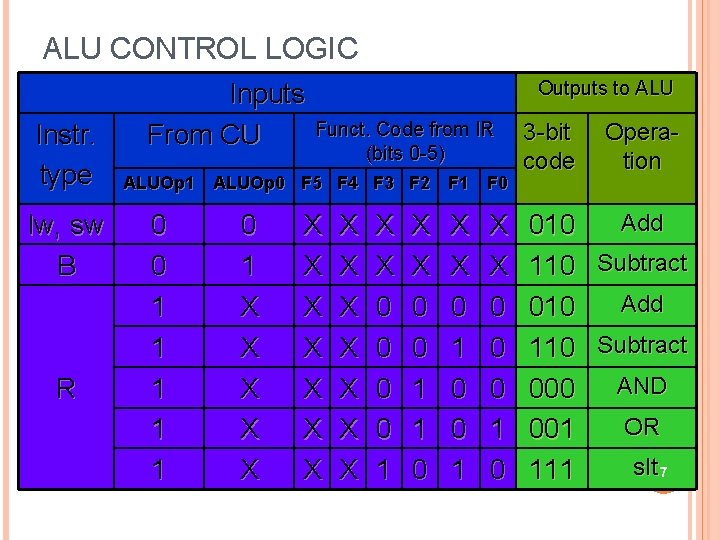

ALU CONTROL LOGIC Instr. type lw, sw B R Inputs From CU Outputs to ALU Funct. Code from IR (bits 0 -5) ALUOp 1 ALUOp 0 F 5 F 4 F 3 F 2 F 1 F 0 0 0 1 1 1 0 1 X X X X X X 0 0 1 X X 0 0 1 1 0 X X 0 1 0 0 1 X X 0 0 0 1 0 3 -bit code Operation Add 010 110 Subtract 000 AND OR 001 slt 7 111

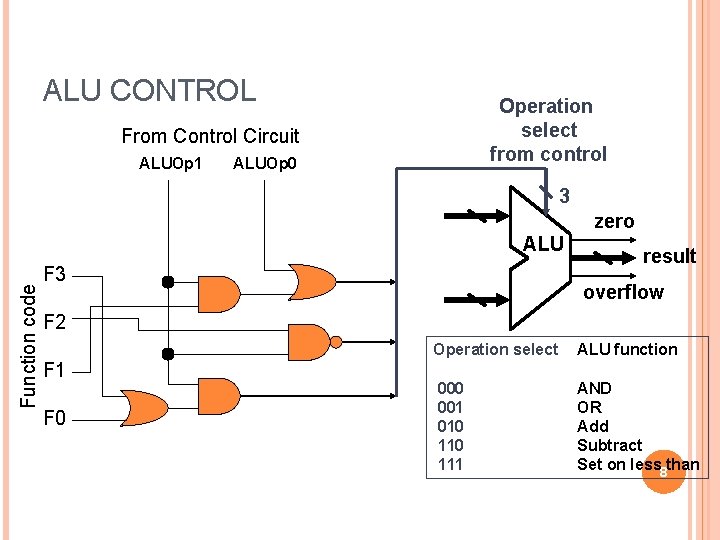

ALU CONTROL Operation select from control From Control Circuit ALUOp 1 ALUOp 0 3 zero Function code ALU F 3 result overflow F 2 F 1 F 0 Operation select ALU function 000 001 010 111 AND OR Add Subtract Set on less 8 than

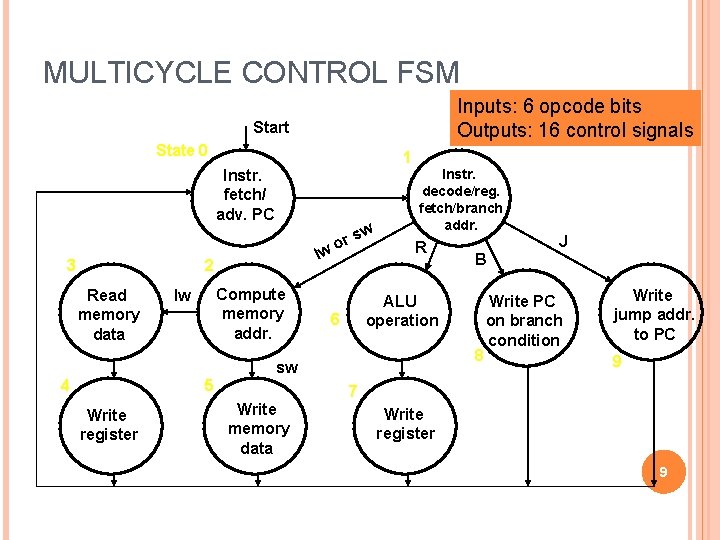

MULTICYCLE CONTROL FSM Inputs: 6 opcode bits Outputs: 16 control signals Start State 0 1 Instr. fetch/ adv. PC 3 or lw 2 Read memory data Compute memory addr. lw sw Instr. decode/reg. fetch/branch addr. R 5 Write register B ALU operation 6 8 sw 4 J Write PC on branch condition Write jump addr. to PC 9 7 Write memory data Write register 9

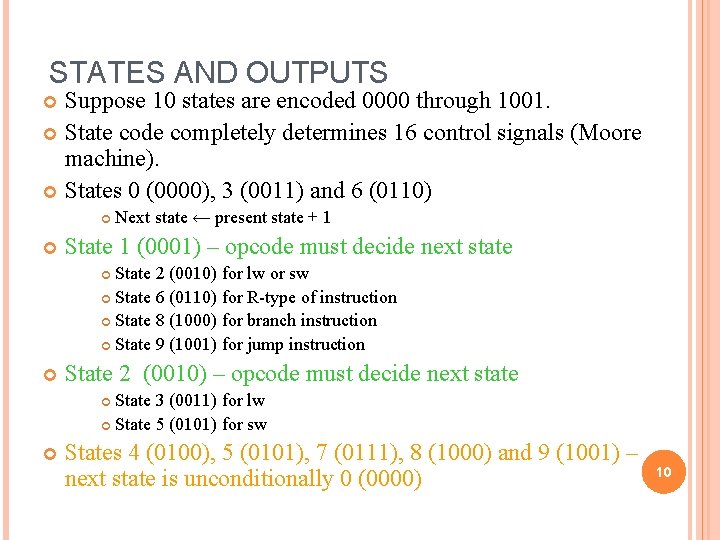

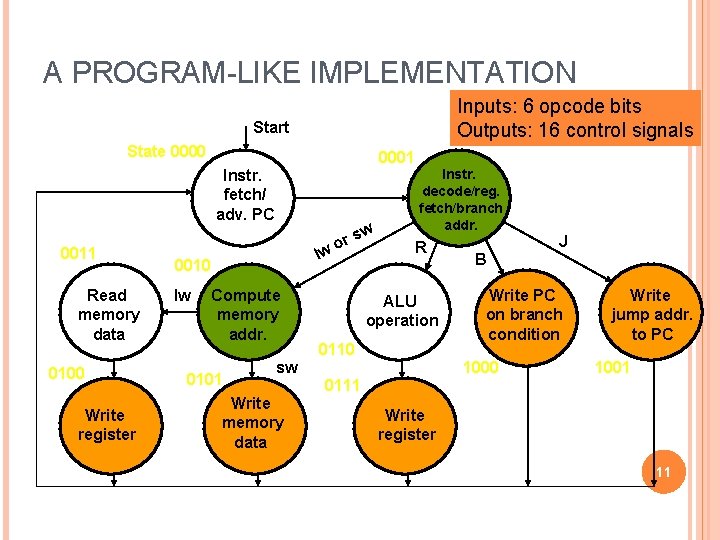

STATES AND OUTPUTS Suppose 10 states are encoded 0000 through 1001. State code completely determines 16 control signals (Moore machine). States 0 (0000), 3 (0011) and 6 (0110) Next state ← present state + 1 State 1 (0001) – opcode must decide next state State 2 (0010) for lw or sw State 6 (0110) for R-type of instruction State 8 (1000) for branch instruction State 9 (1001) for jump instruction State 2 (0010) – opcode must decide next state State 3 (0011) for lw State 5 (0101) for sw States 4 (0100), 5 (0101), 7 (0111), 8 (1000) and 9 (1001) – next state is unconditionally 0 (0000) 10

A PROGRAM-LIKE IMPLEMENTATION Inputs: 6 opcode bits Outputs: 16 control signals Start State 0000 0001 Instr. fetch/ adv. PC 0011 Read memory data 0100 Write register or lw 0010 lw Compute memory addr. 0101 sw Instr. decode/reg. fetch/branch addr. R ALU operation 0110 sw Write memory data J B Write PC on branch condition 1000 Write jump addr. to PC 1001 0111 Write register 11

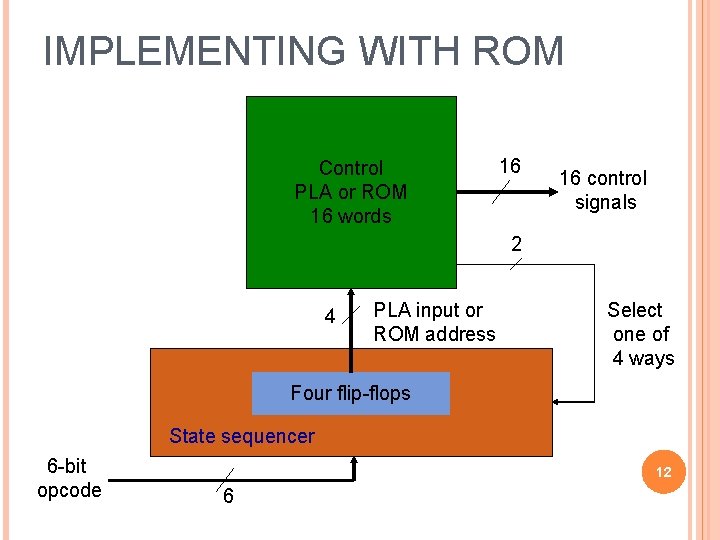

IMPLEMENTING WITH ROM Control PLA or ROM 16 words 16 16 control signals 2 4 PLA input or ROM address Select one of 4 ways Four flip-flops State sequencer 6 -bit opcode 12 6

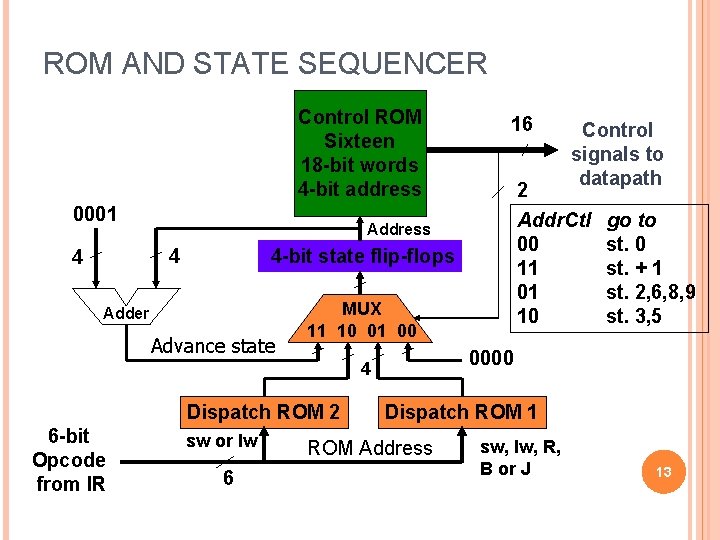

ROM AND STATE SEQUENCER Control ROM Sixteen 18 -bit words 4 -bit address 0001 4 -bit state flip-flops Adder Advance state MUX 11 10 01 00 6 -bit Opcode from IR sw or lw 6 go to st. 0 st. + 1 st. 2, 6, 8, 9 st. 3, 5 0000 4 Dispatch ROM 2 Control signals to datapath 2 Addr. Ctl 00 11 01 10 Address 4 4 16 Dispatch ROM 1 ROM Address sw, lw, R, B or J 13

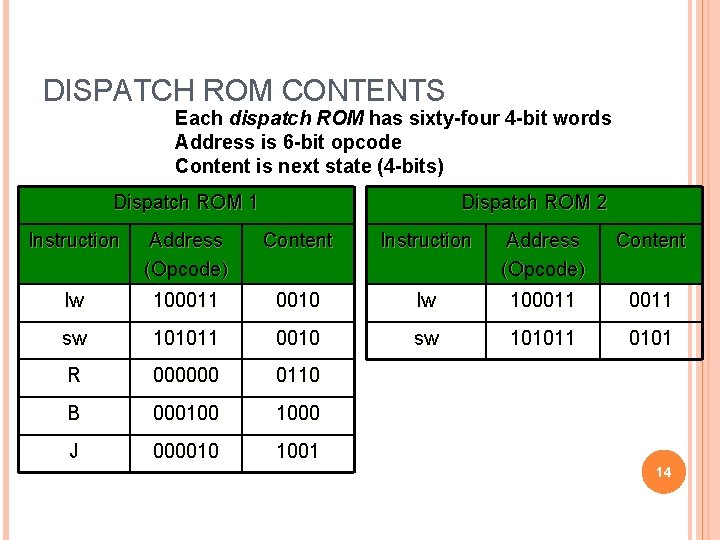

DISPATCH ROM CONTENTS Each dispatch ROM has sixty-four 4 -bit words Address is 6 -bit opcode Content is next state (4 -bits) Dispatch ROM 1 Dispatch ROM 2 Instruction Address (Opcode) Content lw 100011 0010 lw 100011 sw 101011 0010 sw 101011 0101 R 000000 0110 B 000100 1000 J 000010 1001 14

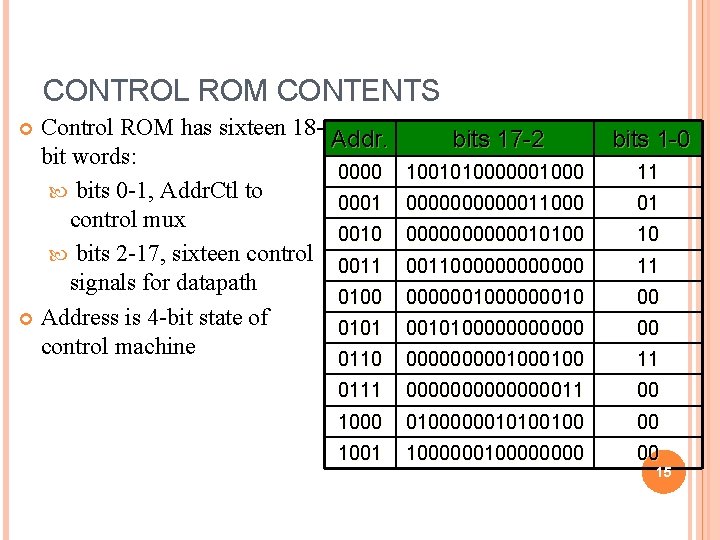

CONTROL ROM CONTENTS Control ROM has sixteen 18 Addr. bit words: 0000 bits 0 -1, Addr. Ctl to 0001 control mux 0010 bits 2 -17, sixteen control 0011 signals for datapath 0100 Address is 4 -bit state of 0101 control machine bits 17 -2 bits 1 -0 1001010000001000 11 00000011000 01 00000010100 10 0011000000 11 00000010 00 00101000000 00 0110 00000100 11 0111 000000011 00 1000 0100000010100100 00 1001 100000000 00 15

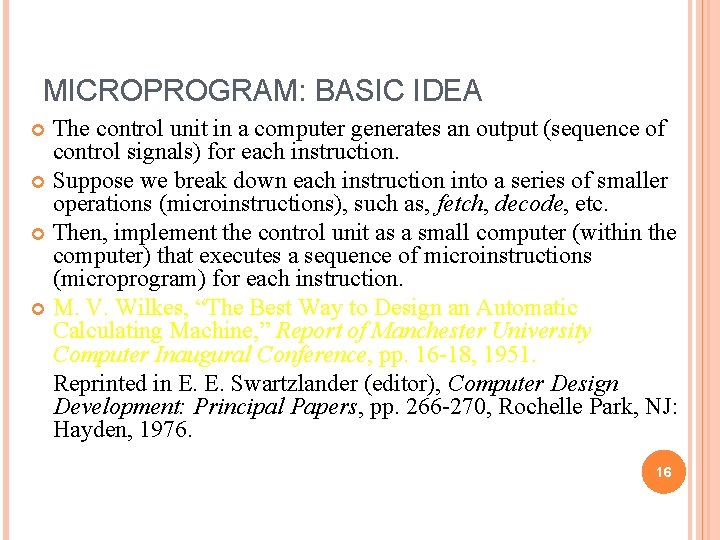

MICROPROGRAM: BASIC IDEA The control unit in a computer generates an output (sequence of control signals) for each instruction. Suppose we break down each instruction into a series of smaller operations (microinstructions), such as, fetch, decode, etc. Then, implement the control unit as a small computer (within the computer) that executes a sequence of microinstructions (microprogram) for each instruction. M. V. Wilkes, “The Best Way to Design an Automatic Calculating Machine, ” Report of Manchester University Computer Inaugural Conference, pp. 16 -18, 1951. Reprinted in E. E. Swartzlander (editor), Computer Design Development: Principal Papers, pp. 266 -270, Rochelle Park, NJ: Hayden, 1976. 16

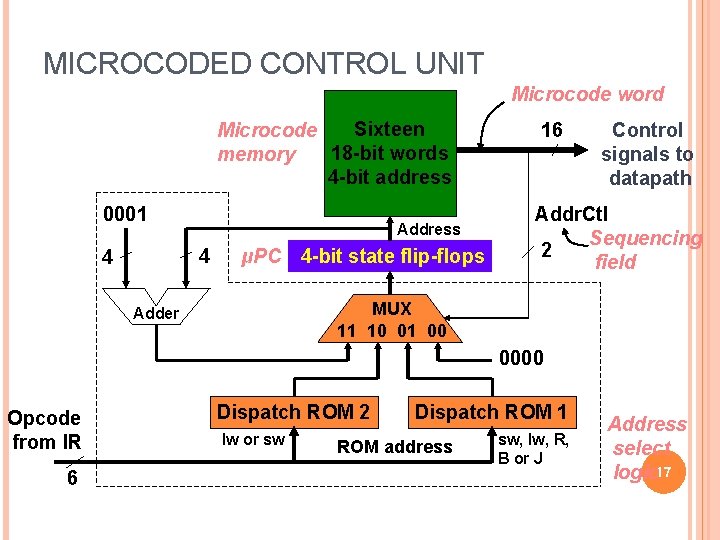

MICROCODED CONTROL UNIT Microcode word Sixteen Microcode 18 -bit words memory 4 -bit address 0001 Address 4 4 μPC 4 -bit state flip-flops 16 Control signals to datapath Addr. Ctl Sequencing 2 field MUX 11 10 01 00 Adder 0000 Opcode from IR 6 Dispatch ROM 2 lw or sw Dispatch ROM 1 ROM address sw, lw, R, B or J Address select logic 17

IMPLEMENTING THE IDEA Use a memory type implementation for control unit. Create a software infrastructure to automatically translate instructions into memory data (microcode): Microinstructions – define a machine language in which instructions can be described Microprogram – an instruction described as a sequence of microinstructions Microassembler – converts microprogram to (binary) microcode Is there a micro-compiler? 18

MICROPROGRAMMING A microinstruction set is defined. To program the control of a computer for an instruction set, a programmer writes a microprogram for each machine instruction. Each micrprogram is converted into microcode, specific to the datapath hardware, by a microassembler and the entire microcode is loaded in the microcode memory of the control unit (CU). 19

THE END 20

- Slides: 20