CORE Generator System V 3 1 i IP

- Slides: 30

® CORE Generator System V 3. 1 i IP Catalog and CORE Delivery System

Agenda Core Generator Overview w What’s New in 3. 1 i? w Smart IP Technology w Using the Core Generator w Xilinx IP Center w Design Reuse & the Core Generator w Summary ® www. xilinx. com

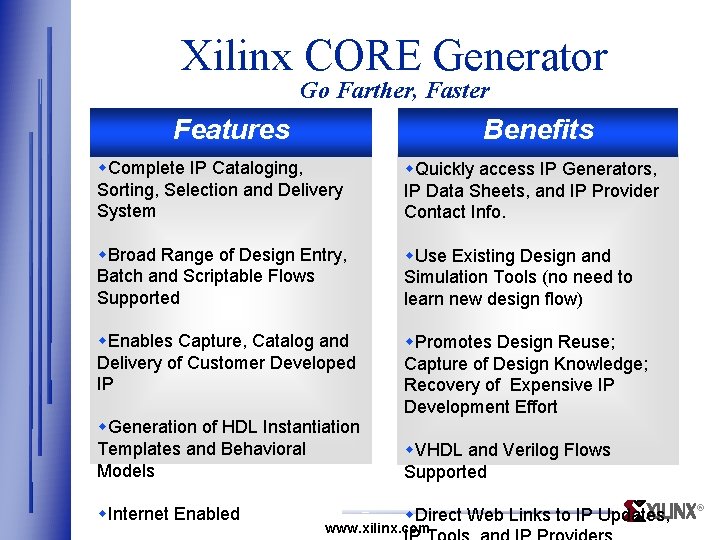

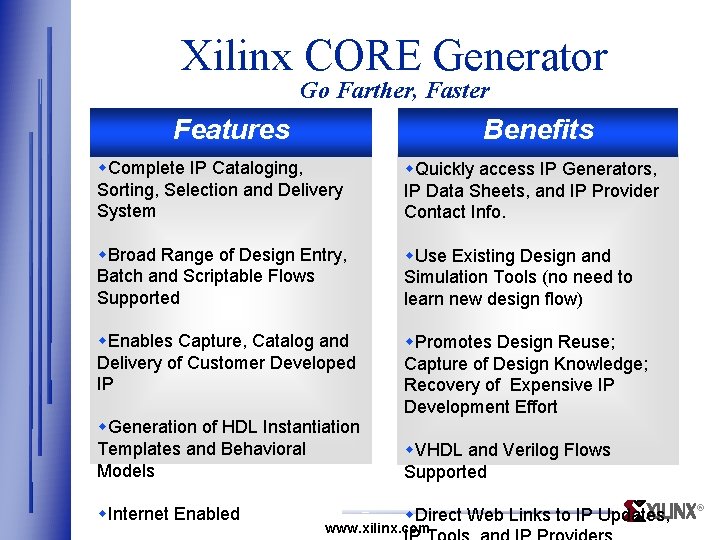

Xilinx CORE Generator Go Farther, Faster Features Benefits w. Complete IP Cataloging, Sorting, Selection and Delivery System w. Quickly access IP Generators, IP Data Sheets, and IP Provider Contact Info. w. Broad Range of Design Entry, Batch and Scriptable Flows Supported w. Use Existing Design and Simulation Tools (no need to learn new design flow) w. Enables Capture, Catalog and Delivery of Customer Developed IP w. Promotes Design Reuse; Capture of Design Knowledge; Recovery of Expensive IP Development Effort w. Generation of HDL Instantiation Templates and Behavioral Models w. VHDL and Verilog Flows Supported w. Internet Enabled w. Direct Web Links to IP Updates, www. xilinx. com ®

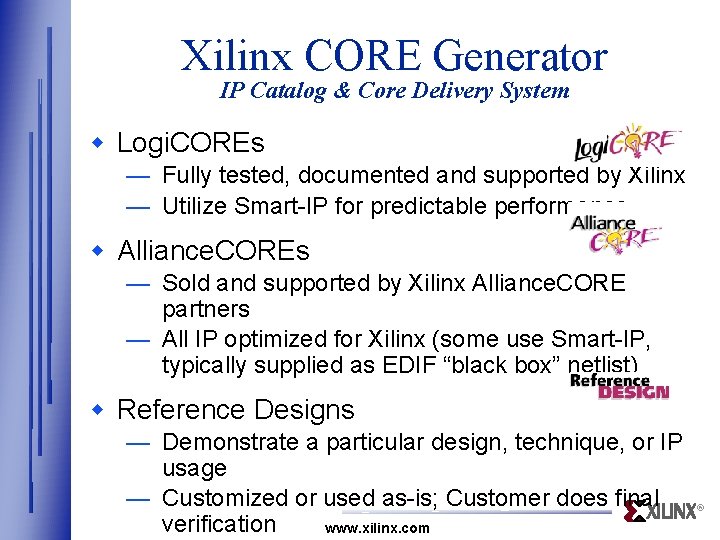

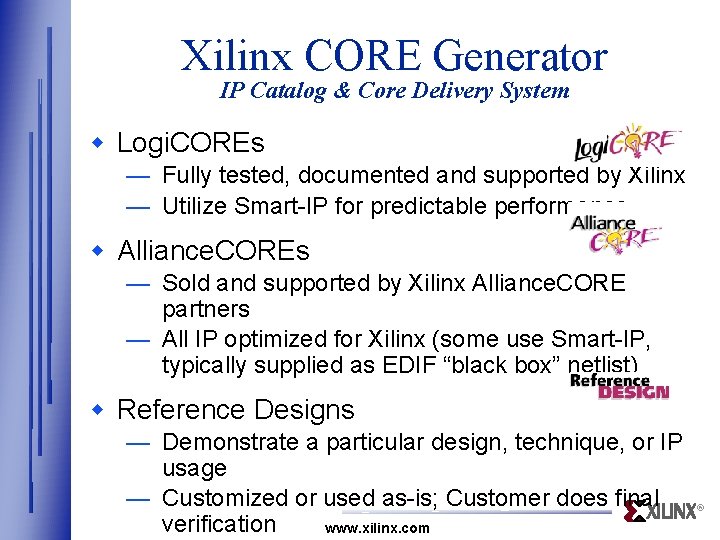

Xilinx CORE Generator IP Catalog & Core Delivery System w Logi. COREs — Fully tested, documented and supported by Xilinx — Utilize Smart-IP for predictable performance w Alliance. COREs — Sold and supported by Xilinx Alliance. CORE partners — All IP optimized for Xilinx (some use Smart-IP, typically supplied as EDIF “black box” netlist) w Reference Designs — Demonstrate a particular design, technique, or IP usage — Customized or used as-is; Customer does final verification www. xilinx. com ®

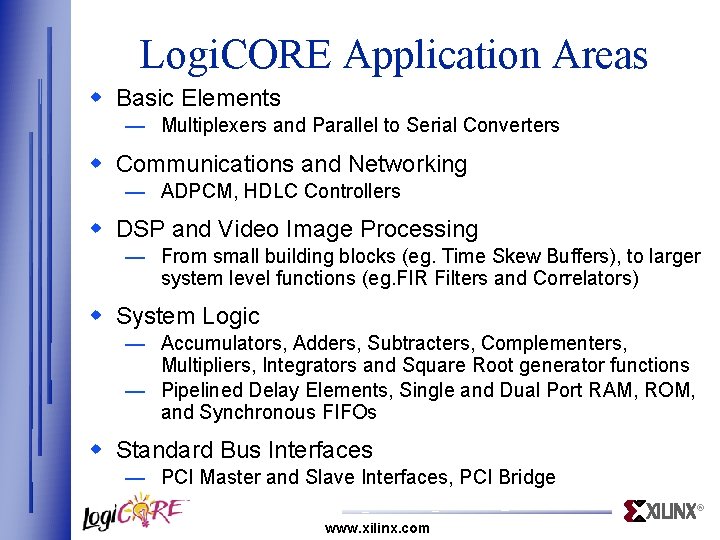

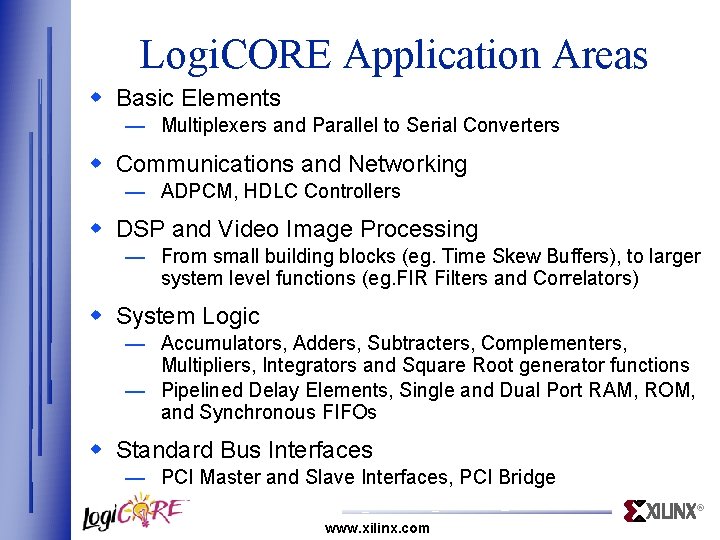

Logi. CORE Application Areas w Basic Elements — Multiplexers and Parallel to Serial Converters w Communications and Networking — ADPCM, HDLC Controllers w DSP and Video Image Processing — From small building blocks (eg. Time Skew Buffers), to larger system level functions (eg. FIR Filters and Correlators) w System Logic — Accumulators, Adders, Subtracters, Complementers, Multipliers, Integrators and Square Root generator functions — Pipelined Delay Elements, Single and Dual Port RAM, ROM, and Synchronous FIFOs w Standard Bus Interfaces — PCI Master and Slave Interfaces, PCI Bridge ® www. xilinx. com

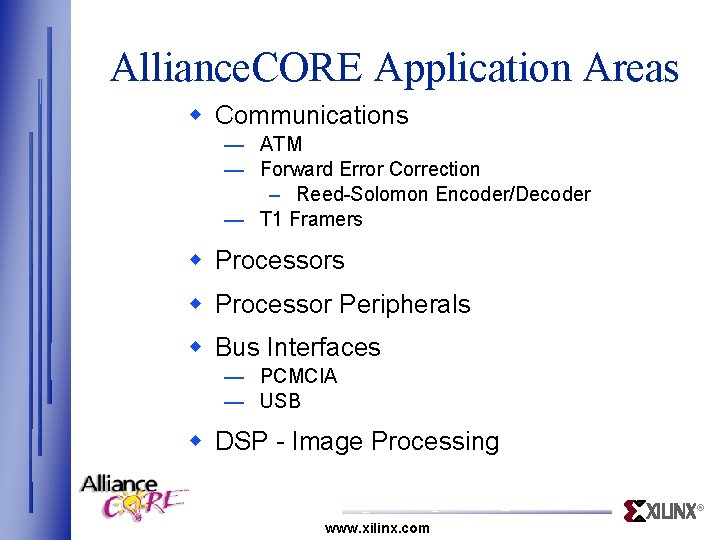

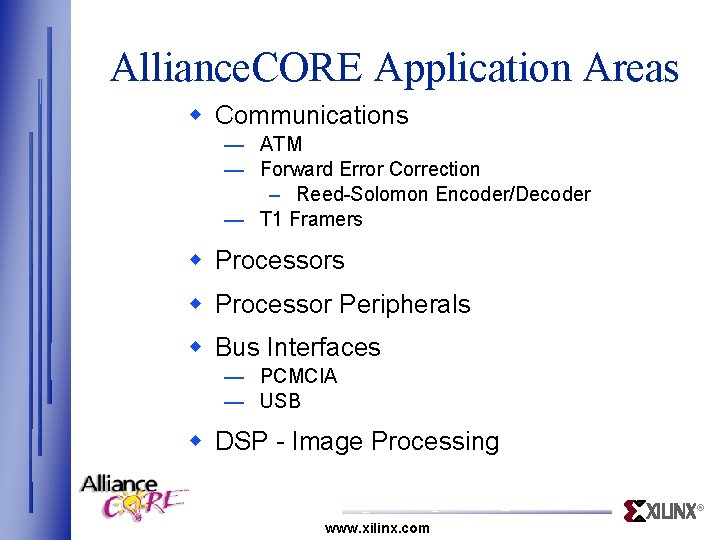

Alliance. CORE Application Areas w Communications — ATM — Forward Error Correction – Reed-Solomon Encoder/Decoder — T 1 Framers w Processor Peripherals w Bus Interfaces — PCMCIA — USB w DSP - Image Processing ® www. xilinx. com

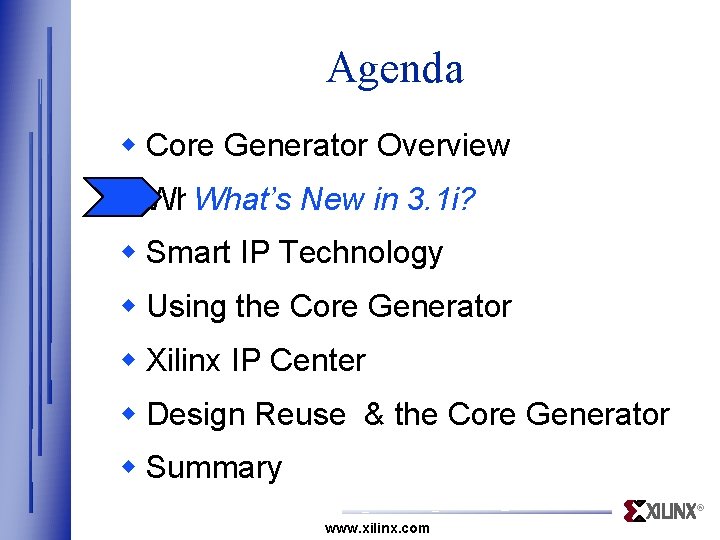

Agenda w Core Generator Overview w What’s New in 3. 1 i? w Smart IP Technology w Using the Core Generator w Xilinx IP Center w Design Reuse & the Core Generator w Summary ® www. xilinx. com

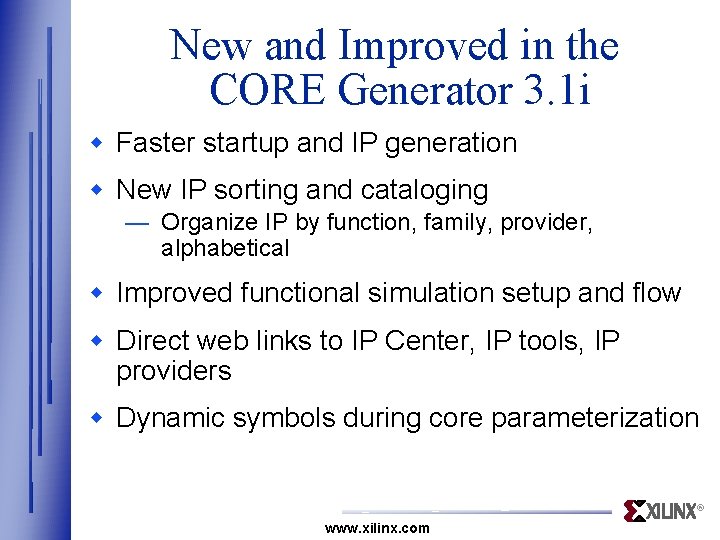

New and Improved in the CORE Generator 3. 1 i w Faster startup and IP generation w New IP sorting and cataloging — Organize IP by function, family, provider, alphabetical w Improved functional simulation setup and flow w Direct web links to IP Center, IP tools, IP providers w Dynamic symbols during core parameterization ® www. xilinx. com

Agenda w Core Generator Overview w What’s New in 3. 1 i? Smart IP Technology w Using the Core Generator w Xilinx IP Center w Design Reuse & the Core Generator w Summary ® www. xilinx. com

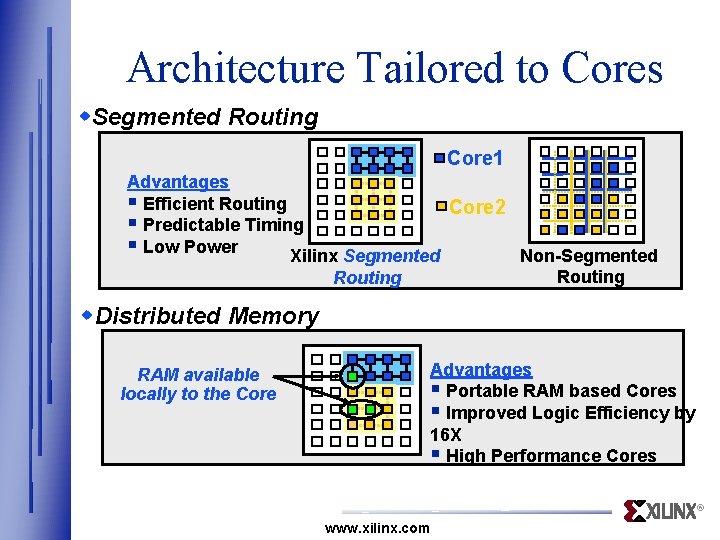

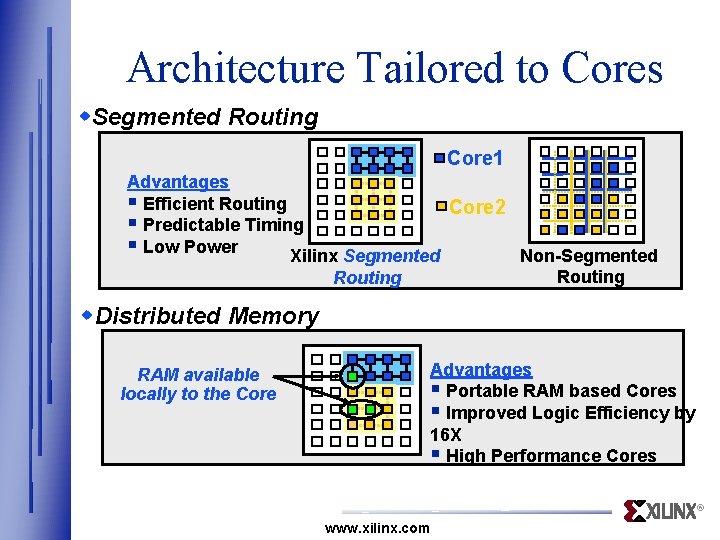

Architecture Tailored to Cores w. Segmented Routing Core 1 Advantages § Efficient Routing Core 2 § Predictable Timing § Low Power Non-Segmented Xilinx Segmented Routing w. Distributed Memory Advantages § Portable RAM based Cores § Improved Logic Efficiency by 16 X § High Performance Cores RAM available locally to the Core ® www. xilinx. com

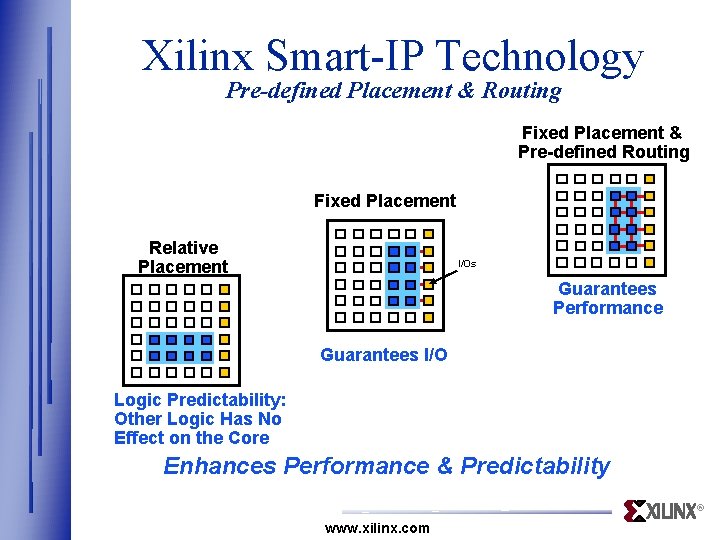

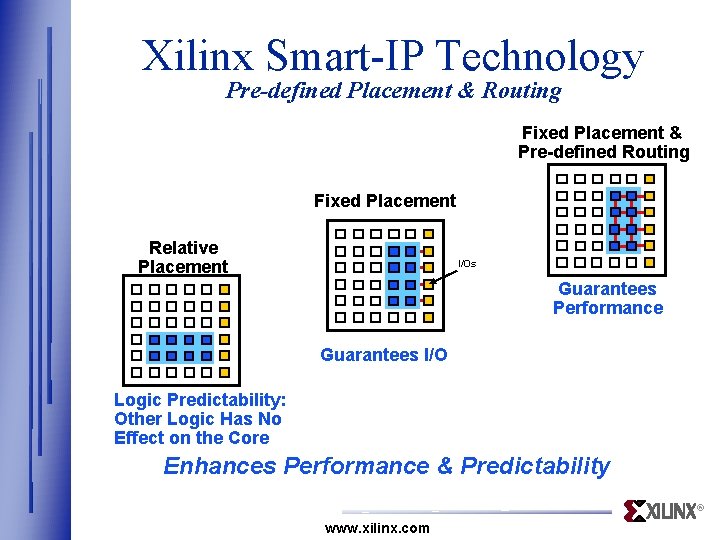

Xilinx Smart-IP Technology Pre-defined Placement & Routing Fixed Placement & Pre-defined Routing Fixed Placement Relative Placement I/Os Guarantees Performance Guarantees I/O Logic Predictability: Other Logic Has No Effect on the Core Enhances Performance & Predictability ® www. xilinx. com

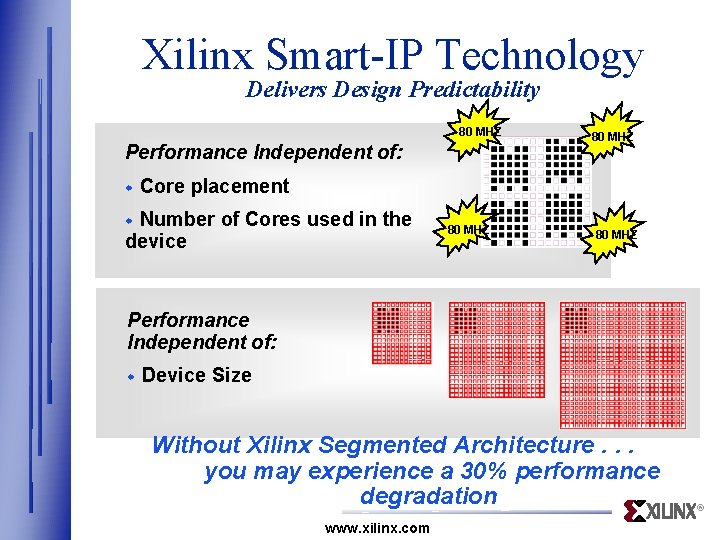

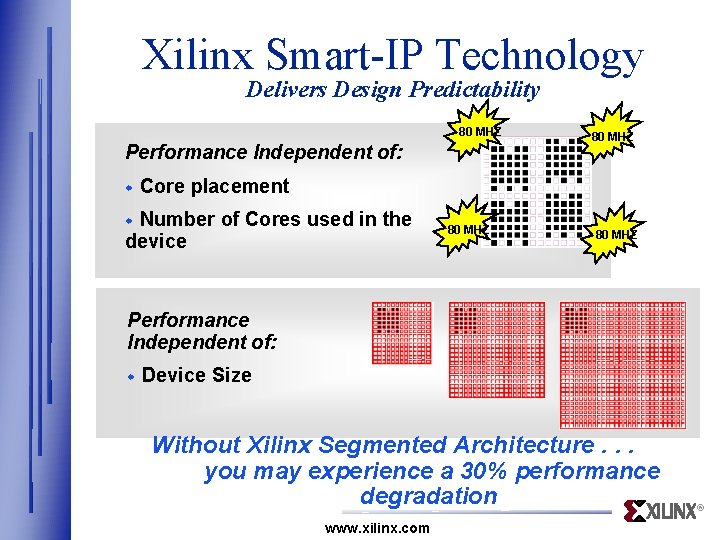

Xilinx Smart-IP Technology Delivers Design Predictability 80 MHZ Performance Independent of: w 80 MHZ Core placement Number of Cores used in the device w 80 MHZ Performance Independent of: w Device Size Without Xilinx Segmented Architecture. . . you may experience a 30% performance degradation www. xilinx. com ®

Agenda w Core Generator Overview w What’s New in 3. 1 i? w Smart IP Technology Using Core Generator w Using the Core Generator w Xilinx IP Center w Design Reuse & the Core Generator w Summary ® www. xilinx. com

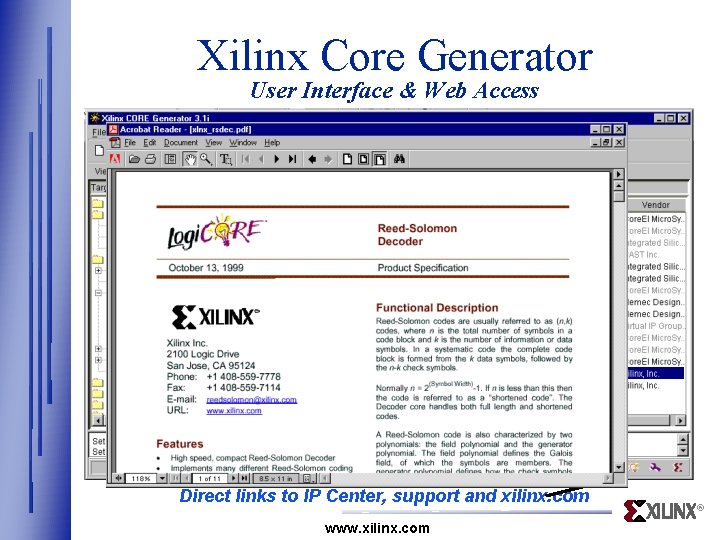

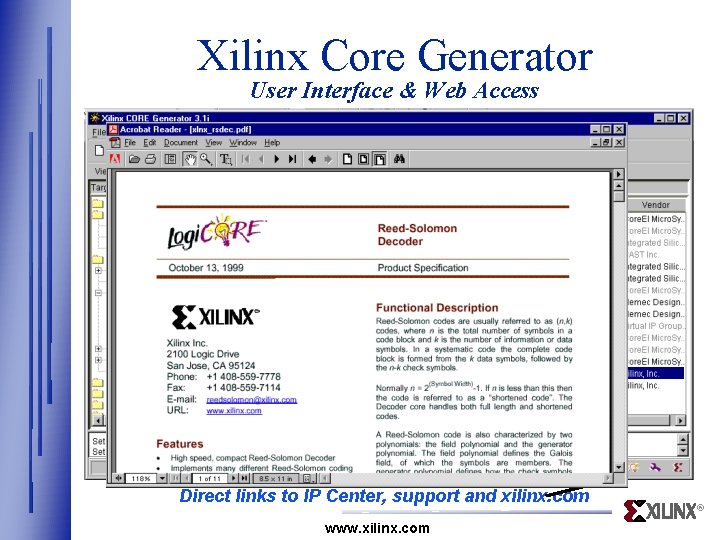

Xilinx Core Generator User Interface & Web Access Direct links to IP Center, support and xilinx. com www. xilinx. com ®

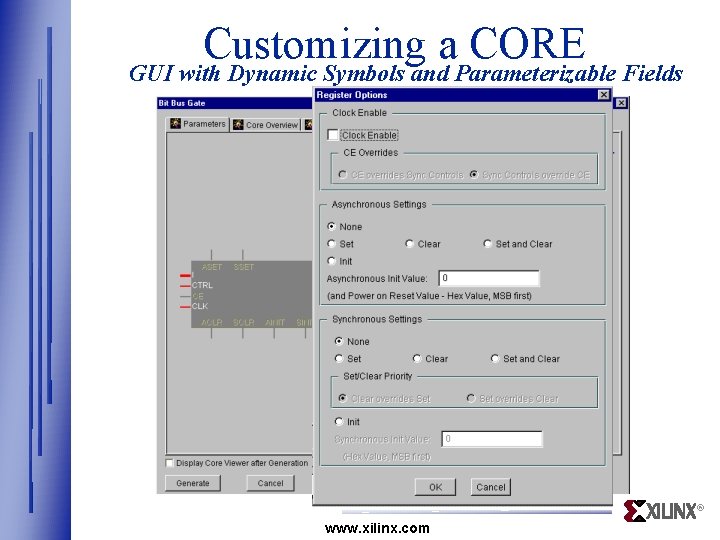

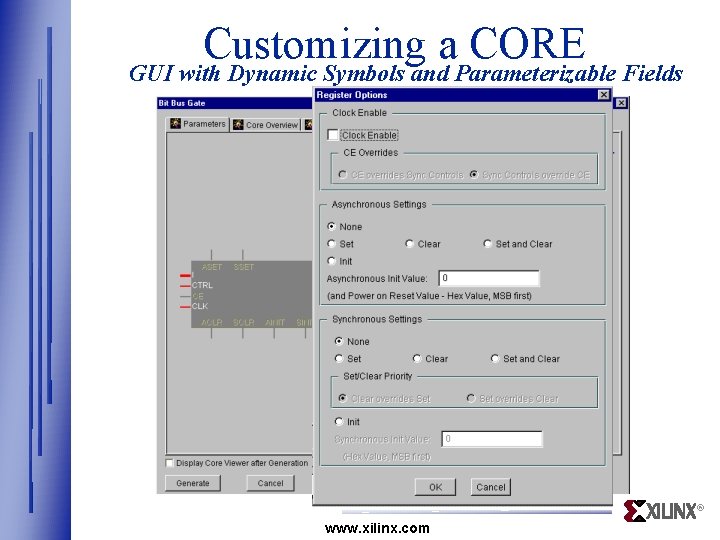

Customizing a CORE GUI with Dynamic Symbols and Parameterizable Fields ® www. xilinx. com

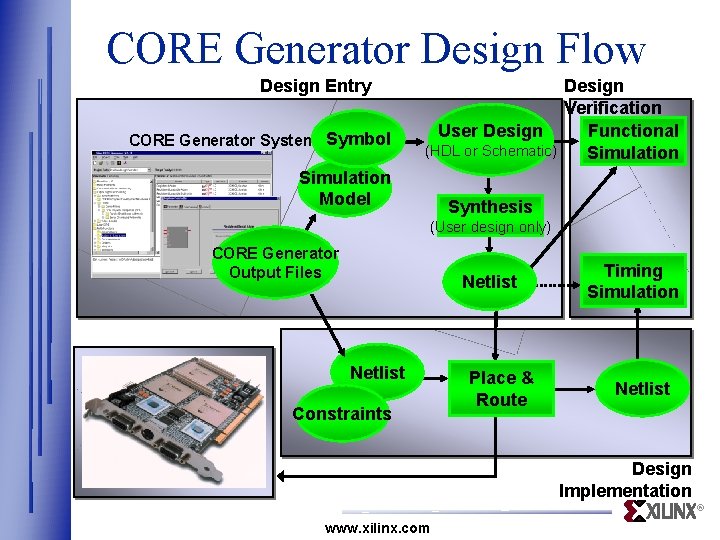

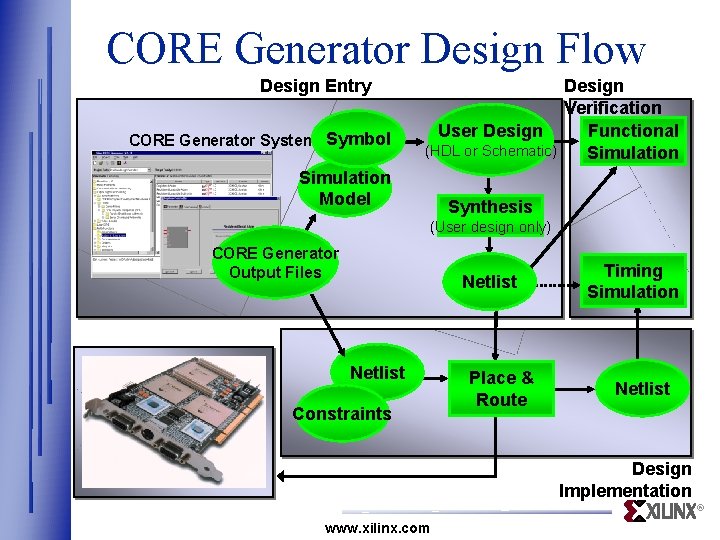

CORE Generator Design Flow Design Entry CORE Generator System Symbol Design Verification Functional User Design (HDL or Schematic) Simulation Model Synthesis (User design only) CORE Generator Output Files Netlist Constraints Place & Route Timing Simulation Netlist Design Implementation ® www. xilinx. com

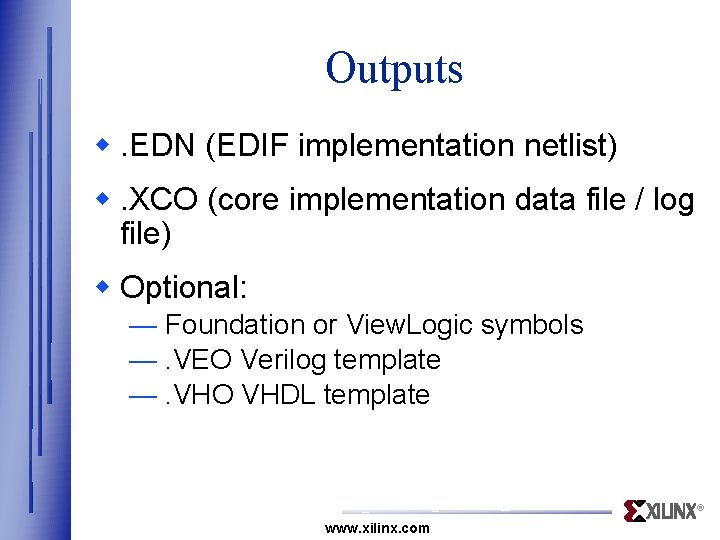

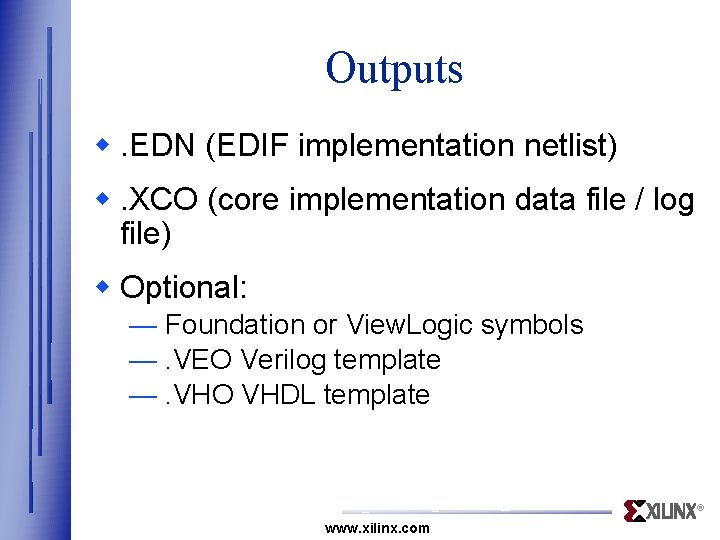

Outputs w. EDN (EDIF implementation netlist) w. XCO (core implementation data file / log file) w Optional: — Foundation or View. Logic symbols —. VEO Verilog template —. VHO VHDL template ® www. xilinx. com

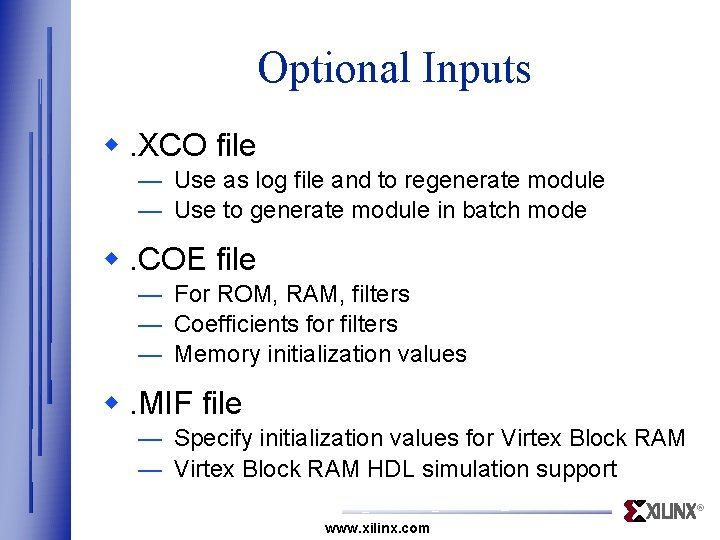

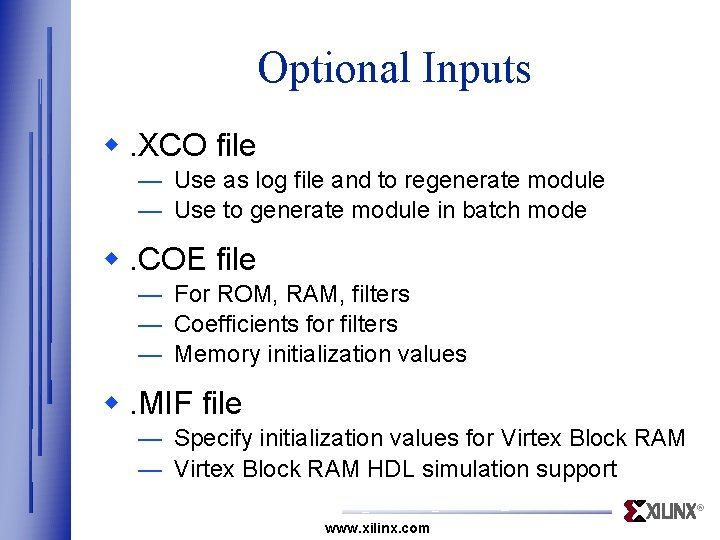

Optional Inputs w. XCO file — Use as log file and to regenerate module — Use to generate module in batch mode w. COE file — For ROM, RAM, filters — Coefficients for filters — Memory initialization values w. MIF file — Specify initialization values for Virtex Block RAM — Virtex Block RAM HDL simulation support ® www. xilinx. com

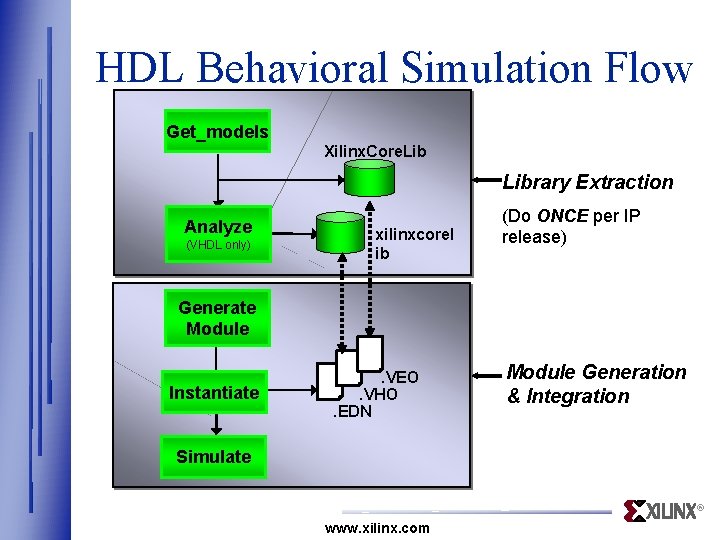

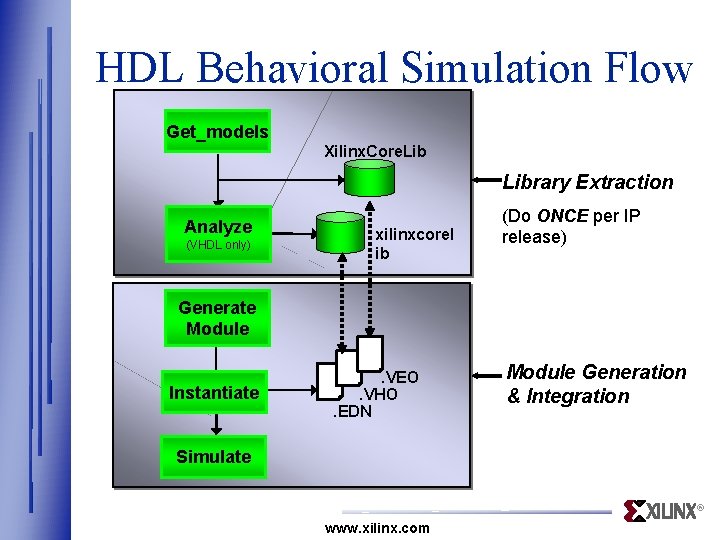

HDL Behavioral Simulation Flow Get_models Xilinx. Core. Library Extraction Analyze (VHDL only) xilinxcorel ib (Do ONCE per IP release) Generate Module Instantiate . VEO. VHO. EDN Module Generation & Integration Simulate ® www. xilinx. com

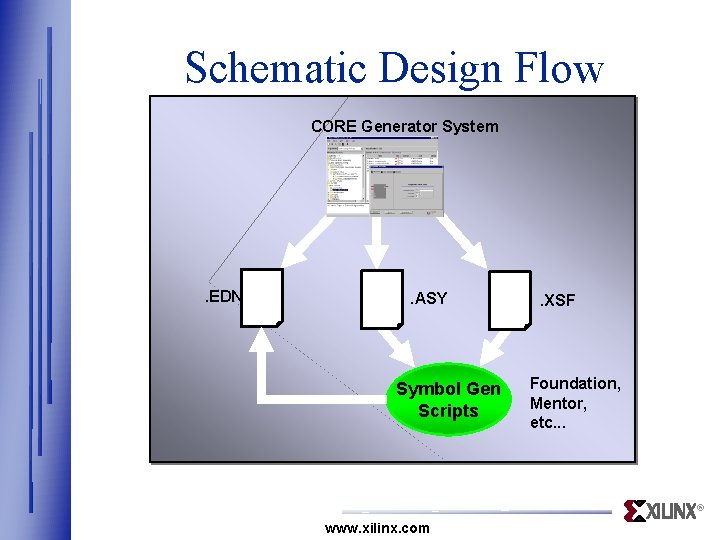

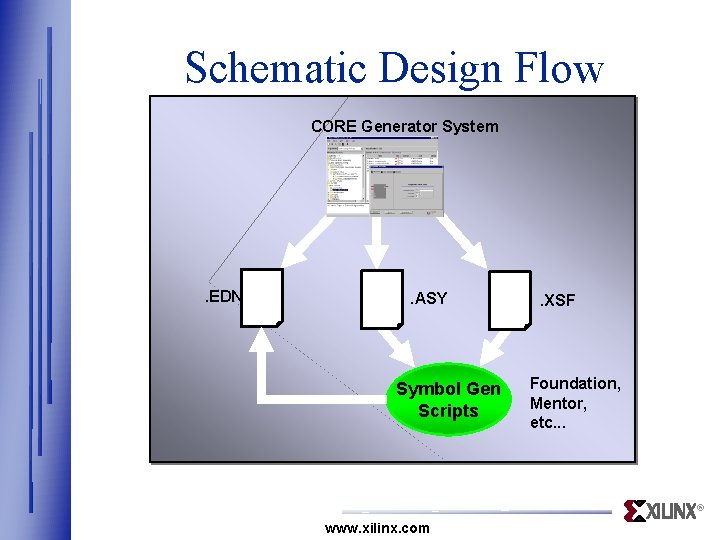

Schematic Design Flow CORE Generator System . EDN . ASY Symbol Gen Scripts . XSF Foundation, Mentor, etc. . . ® www. xilinx. com

Agenda w Core Generator Overview w What’s New in 3. 1 i? w Smart IP Technology w Using the Core Generator w Xilinx IP Center w Design Reuse & the Core Generator w Summary ® www. xilinx. com

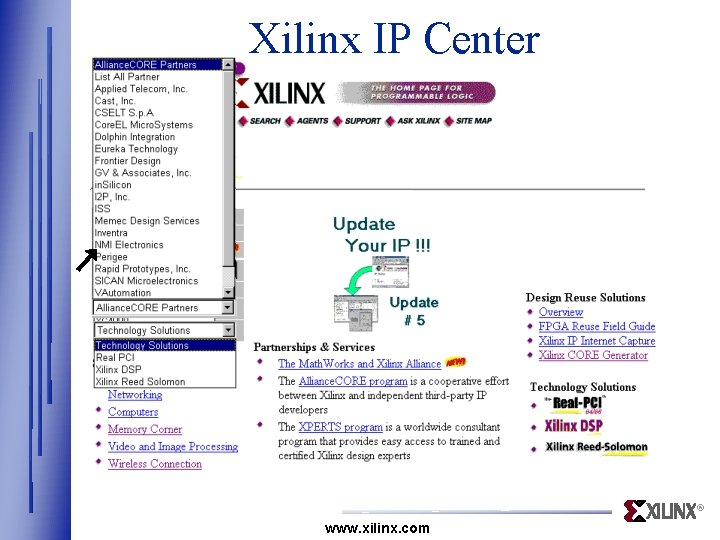

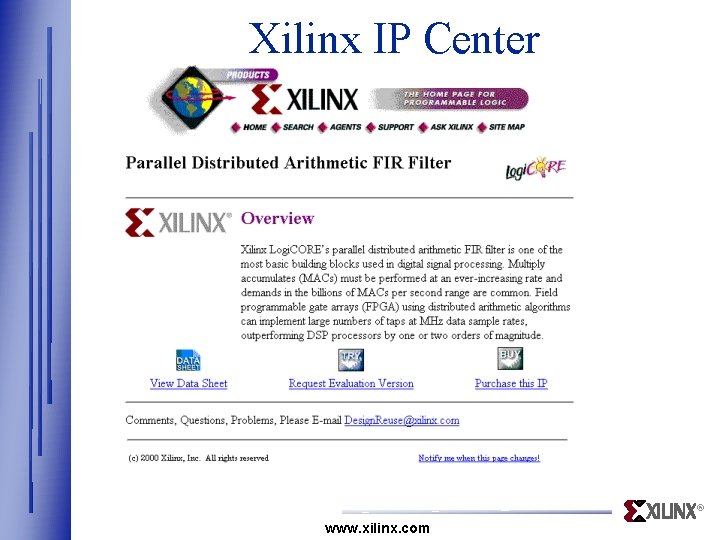

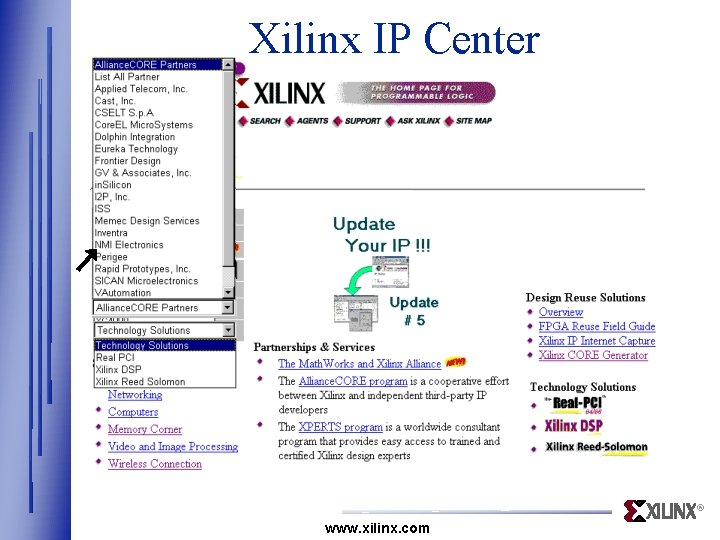

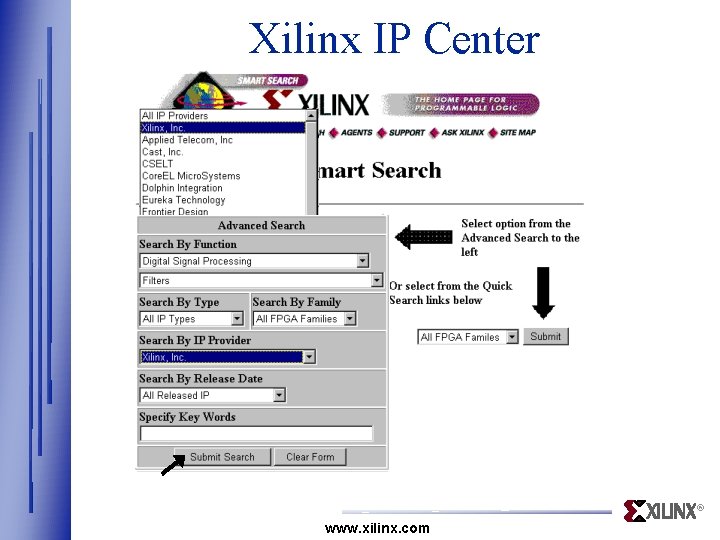

Xilinx IP Center ® www. xilinx. com

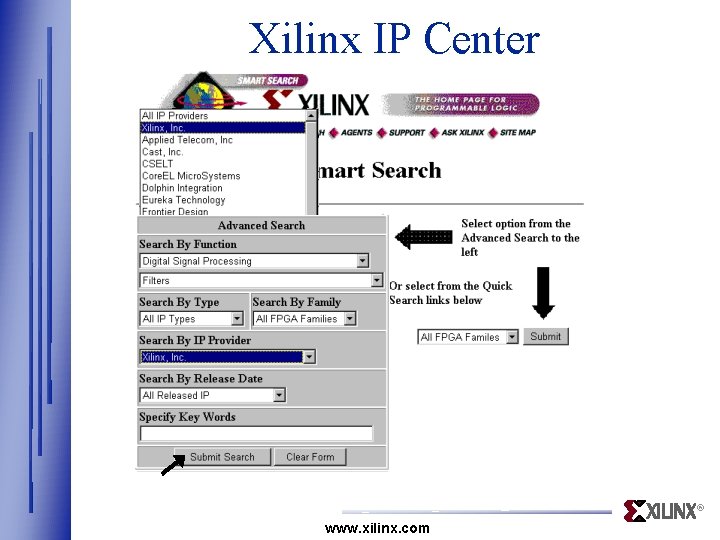

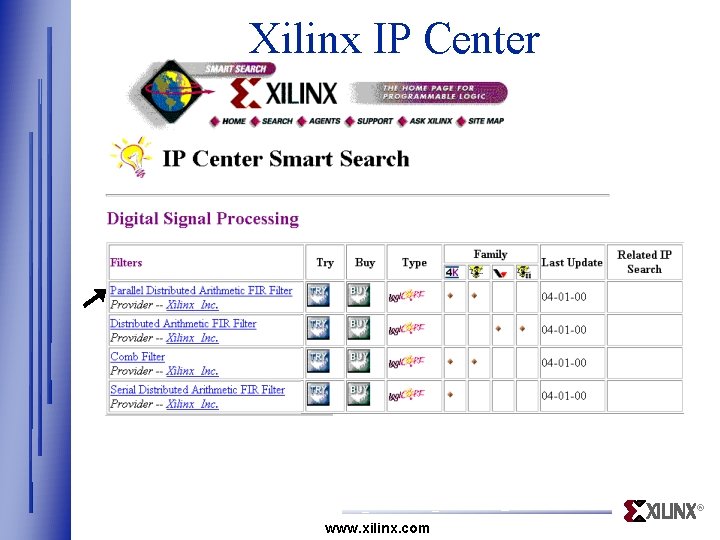

Xilinx IP Center ® www. xilinx. com

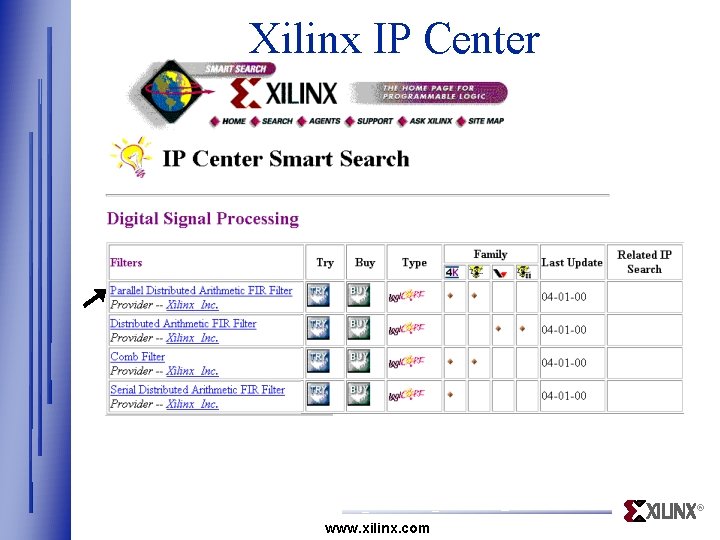

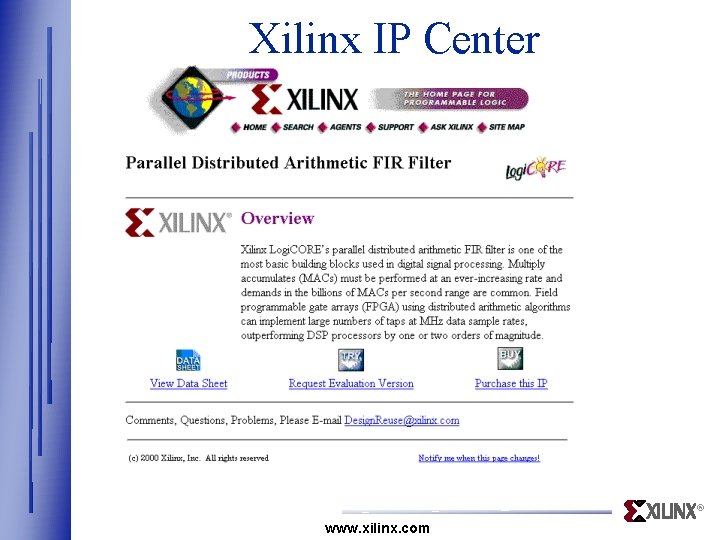

Xilinx IP Center ® www. xilinx. com

Xilinx IP Center ® www. xilinx. com

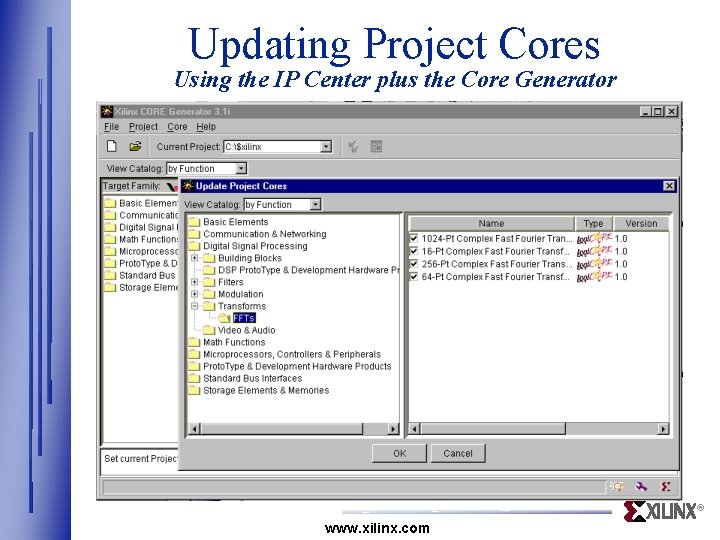

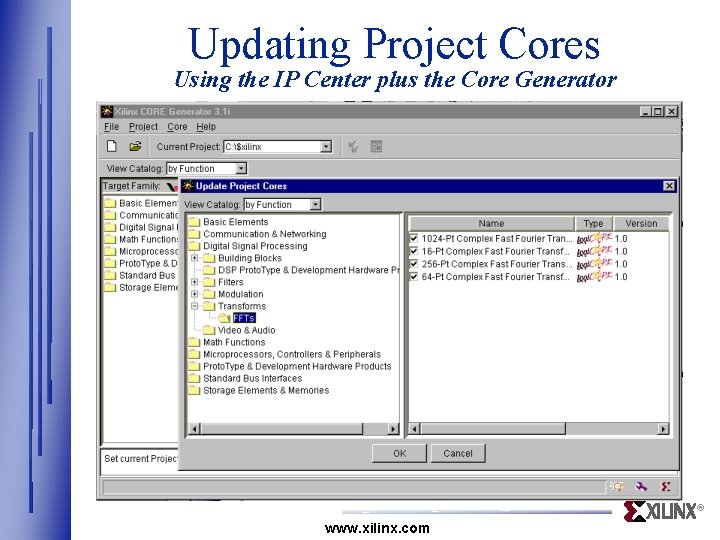

Updating Project Cores Using the IP Center plus the Core Generator ® www. xilinx. com

Agenda w Core Generator Overview w What’s New in 3. 1 i? w Smart IP Technology w Using the Core Generator w Xilinx IP Center w Design Reuse & the Core Generator w Summary ® www. xilinx. com

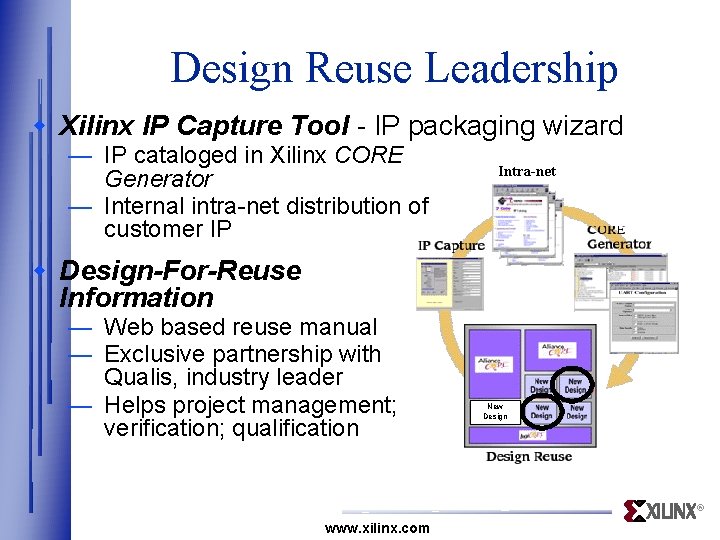

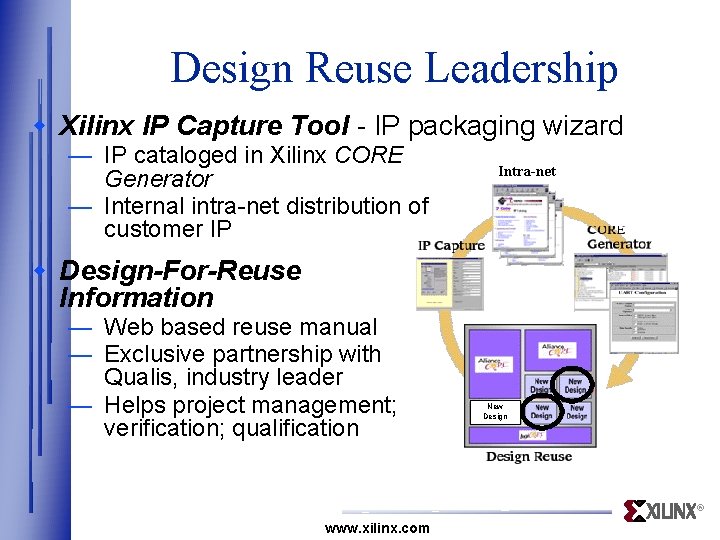

Design Reuse Leadership w Xilinx IP Capture Tool - IP packaging wizard — IP cataloged in Xilinx CORE Generator — Internal intra-net distribution of customer IP Intra-net w Design-For-Reuse Information — Web based reuse manual — Exclusive partnership with Qualis, industry leader — Helps project management; verification; qualification New Design ® www. xilinx. com

Xilinx Resources w Web Summary — Xilinx IP Center — www. xilinx. com / IPcenter — Links to all available cores resources available — CORE Generator & IP modules tech tips — www. xilinx. com/support/techsup/journals/coregen/in dex. htm — Links to known issues, documentation and data sheets w Email — hotline@xilinx. com (general issues) www. xilinx. com ®

Xilinx CORE Generator Solution Summary w Delivers a complete catalog of IP — Includes Xilinx Logi. CORE, Alliance. CORE, user IP — All IP is delivered through the same IP delivery tool — Catalog and reuse your IP with the IP Capture Tool w Delivers a complete solution — Behavioral models, synthesis templates, netlists — Smart-IP guarantees performance — Logi. COREs automatically support new architectures — IP Center delivers the latest free or licensed IP technology § Xilinx gives you the advantage with: — Faster time-to-market and www. xilinx. com ®