COPING WITH INTERCONNECT Digital Integrated Circuits Interconnect Prentice

- Slides: 66

COPING WITH INTERCONNECT Digital Integrated Circuits Interconnect © Prentice Hall 1995

Impact of Interconnect Parasitics Digital Integrated Circuits Interconnect © Prentice Hall 1995

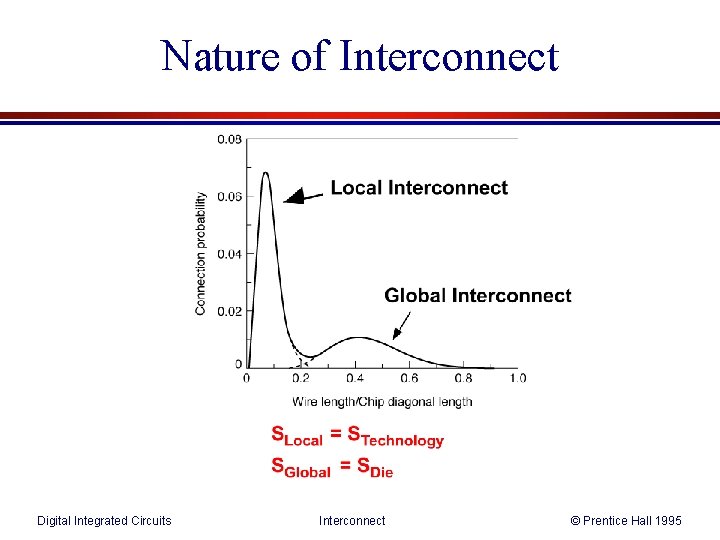

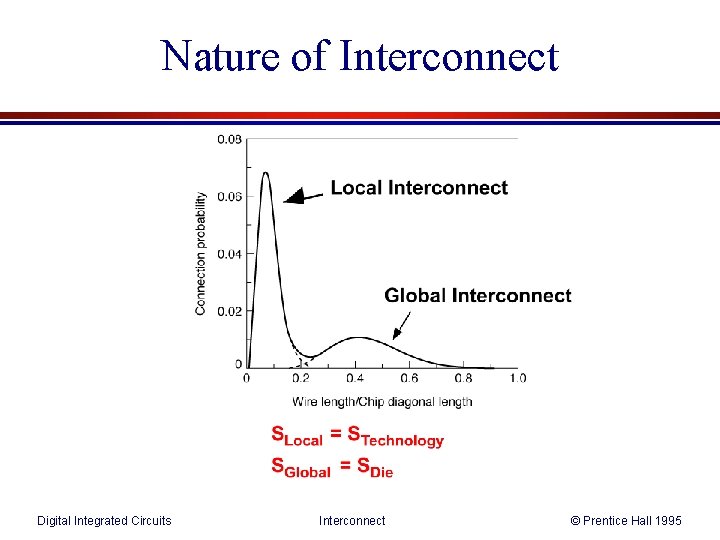

Nature of Interconnect Digital Integrated Circuits Interconnect © Prentice Hall 1995

INTERCONNECT Digital Integrated Circuits Interconnect © Prentice Hall 1995

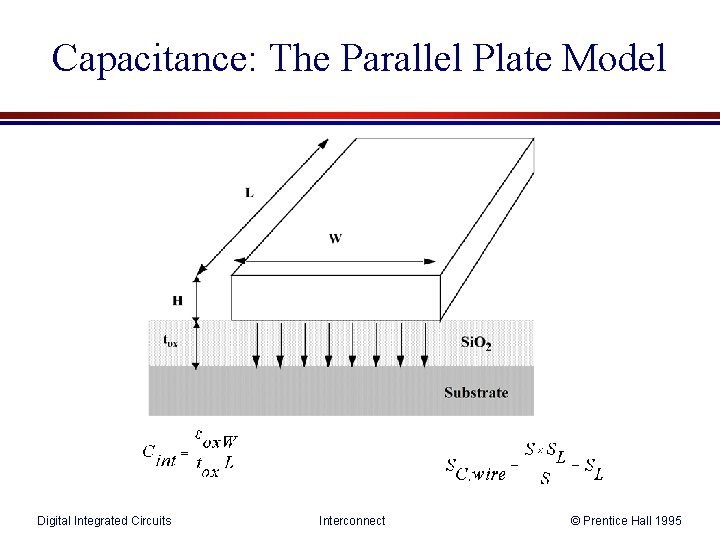

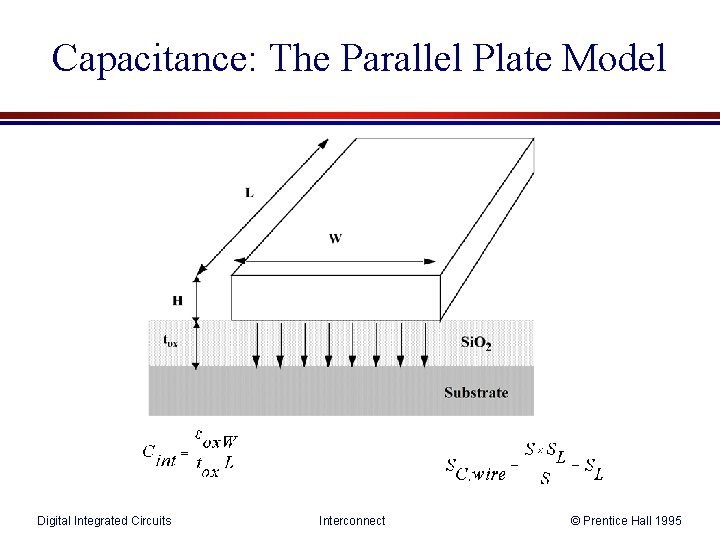

Capacitance: The Parallel Plate Model Digital Integrated Circuits Interconnect © Prentice Hall 1995

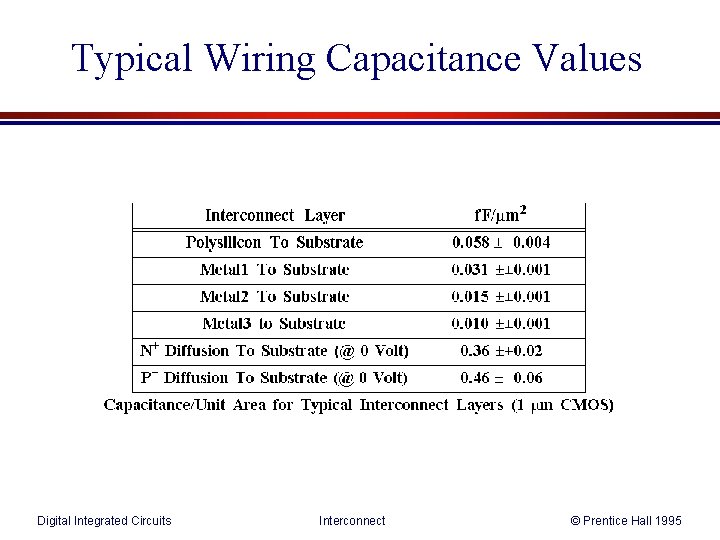

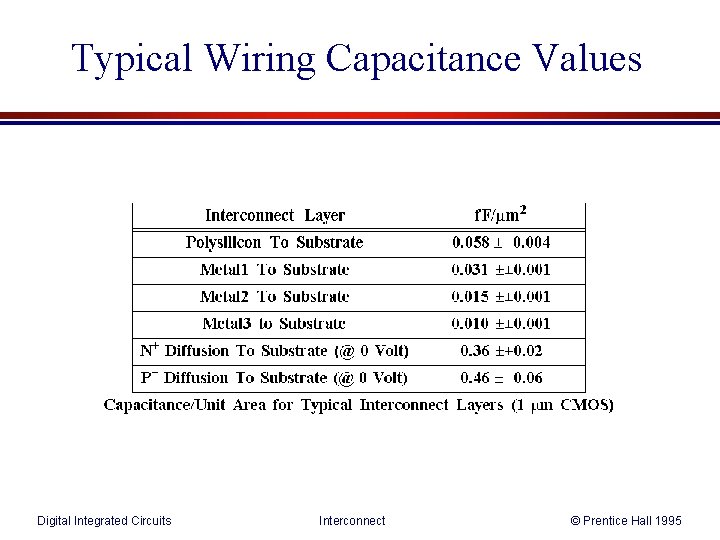

Typical Wiring Capacitance Values Digital Integrated Circuits Interconnect © Prentice Hall 1995

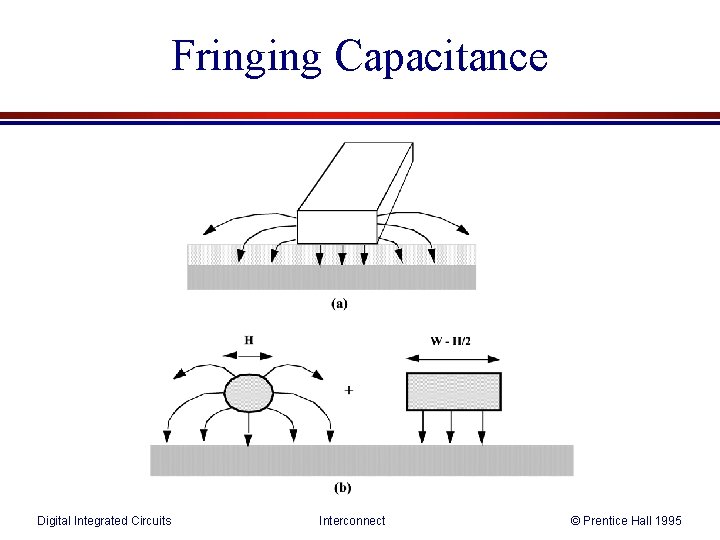

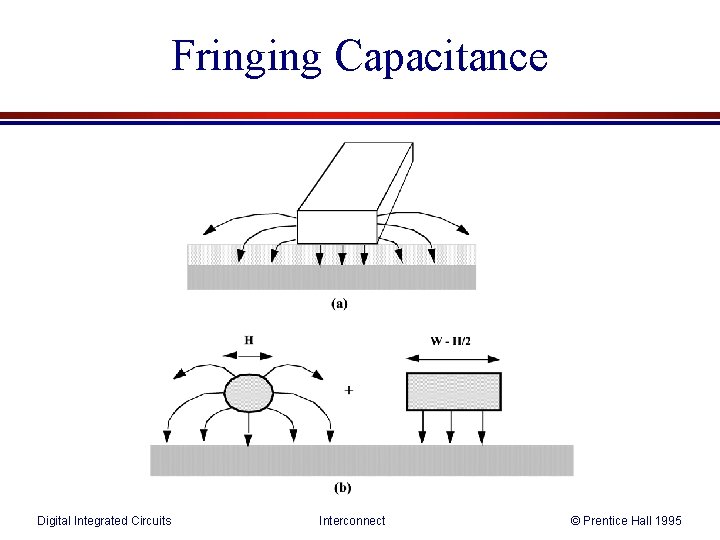

Fringing Capacitance Digital Integrated Circuits Interconnect © Prentice Hall 1995

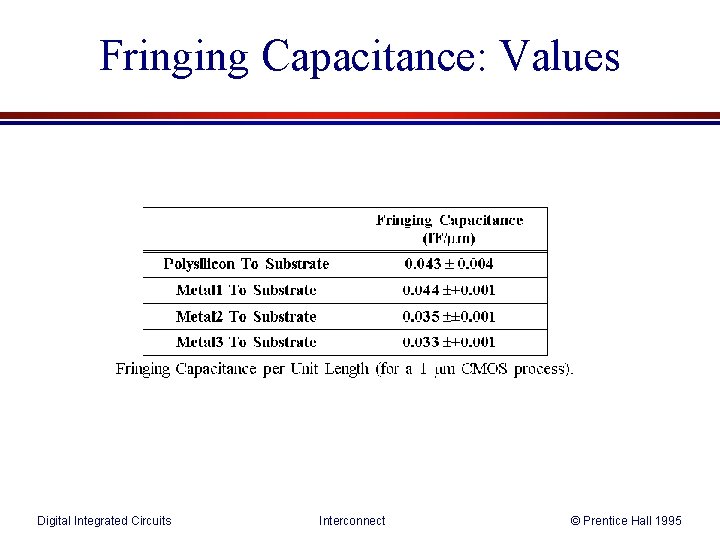

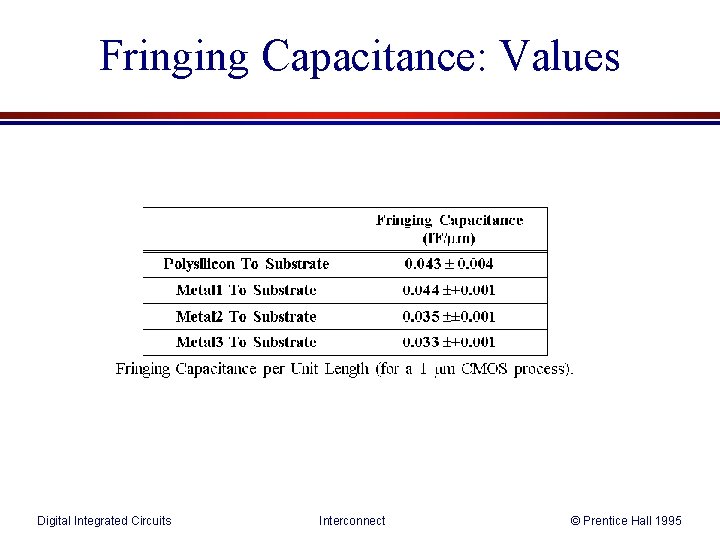

Fringing Capacitance: Values Digital Integrated Circuits Interconnect © Prentice Hall 1995

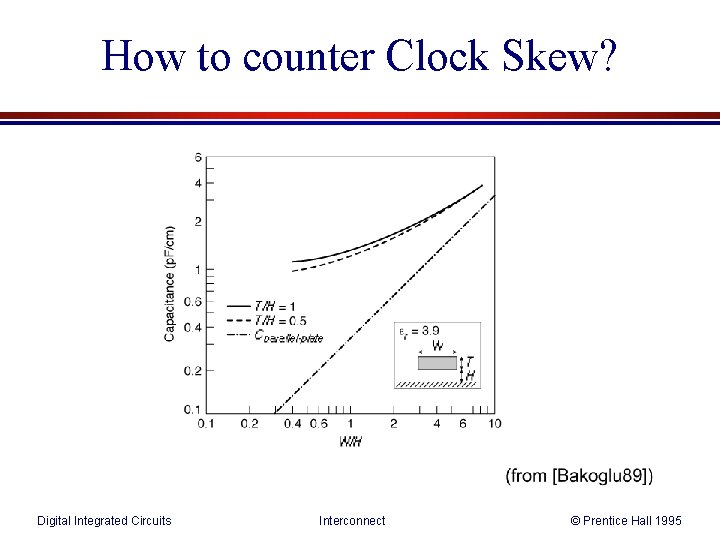

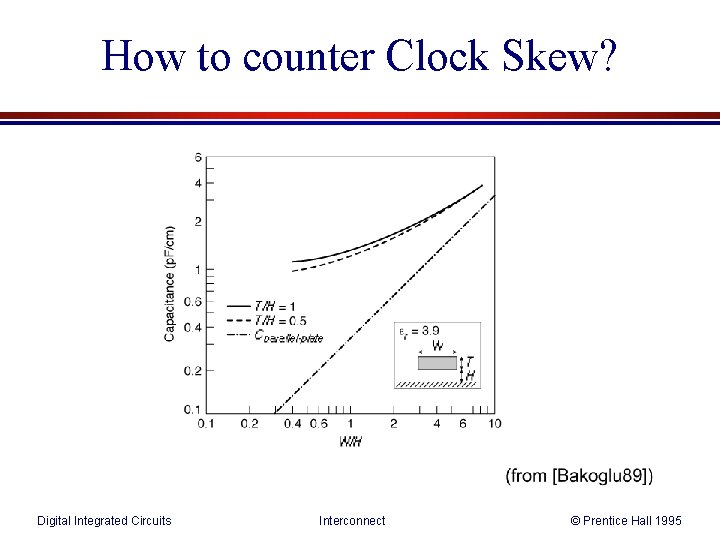

How to counter Clock Skew? Digital Integrated Circuits Interconnect © Prentice Hall 1995

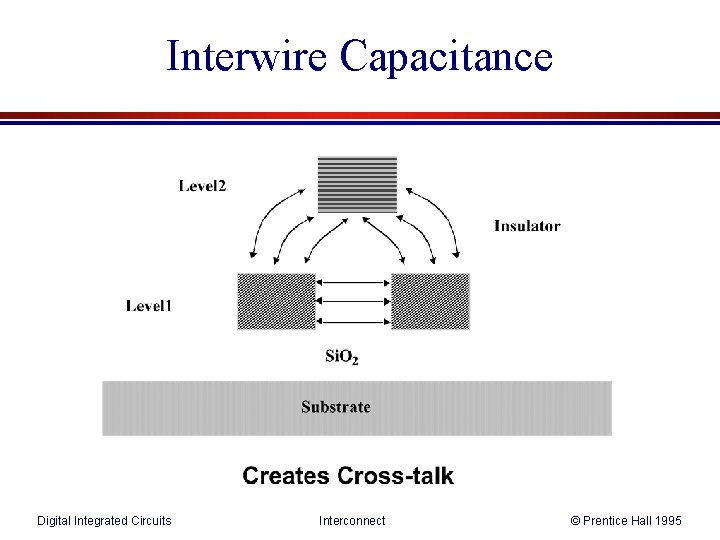

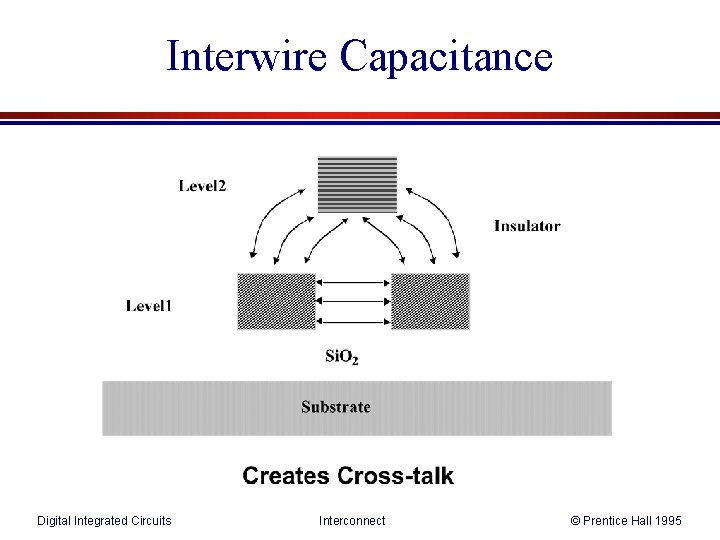

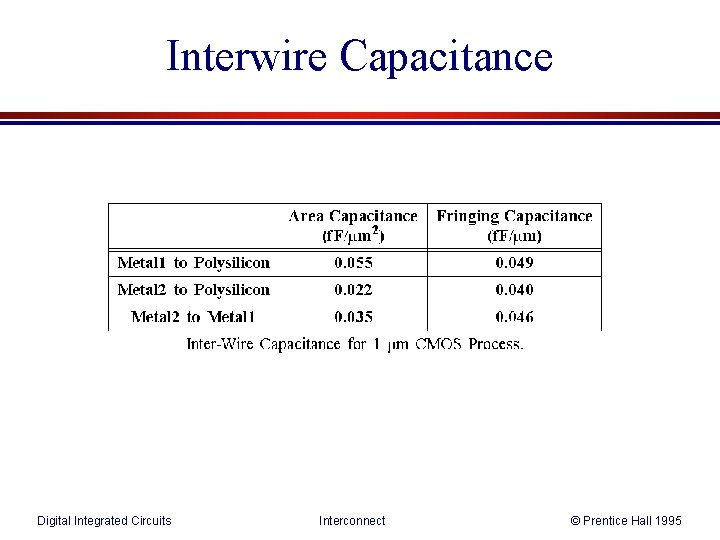

Interwire Capacitance Digital Integrated Circuits Interconnect © Prentice Hall 1995

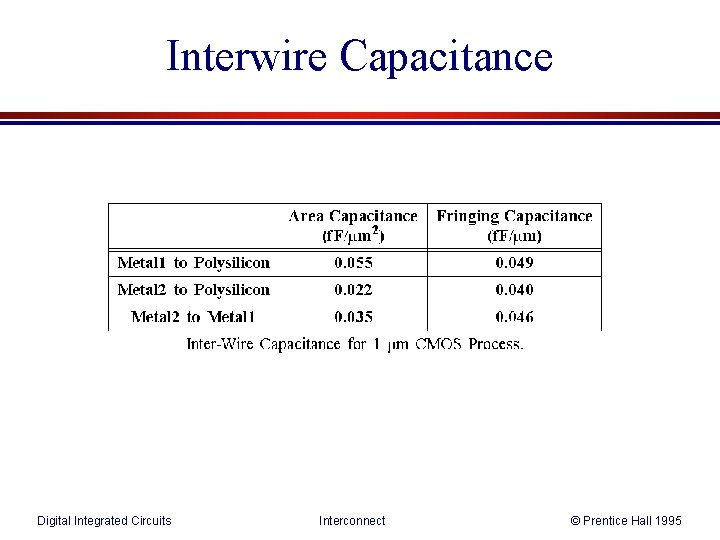

Interwire Capacitance Digital Integrated Circuits Interconnect © Prentice Hall 1995

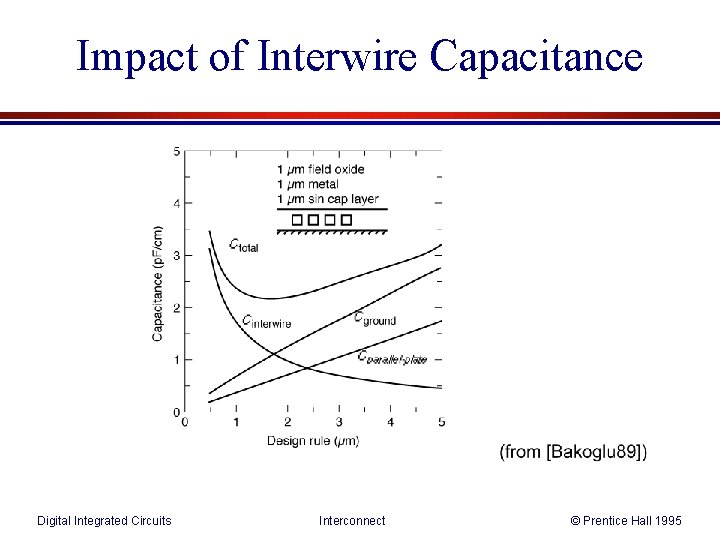

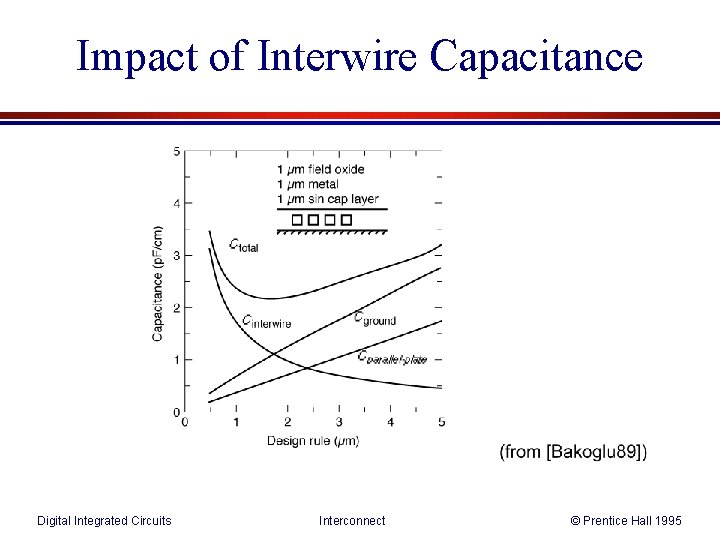

Impact of Interwire Capacitance Digital Integrated Circuits Interconnect © Prentice Hall 1995

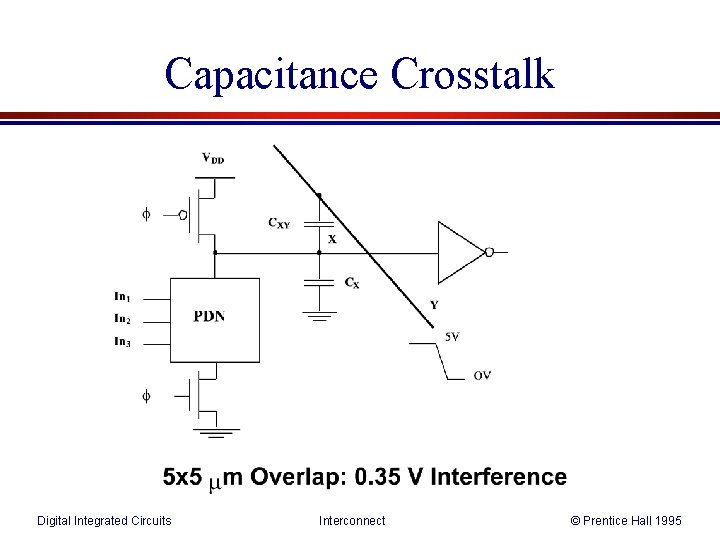

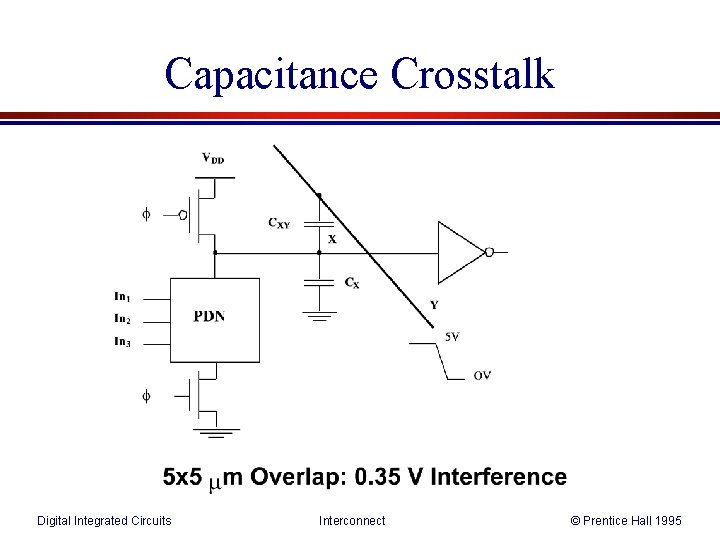

Capacitance Crosstalk Digital Integrated Circuits Interconnect © Prentice Hall 1995

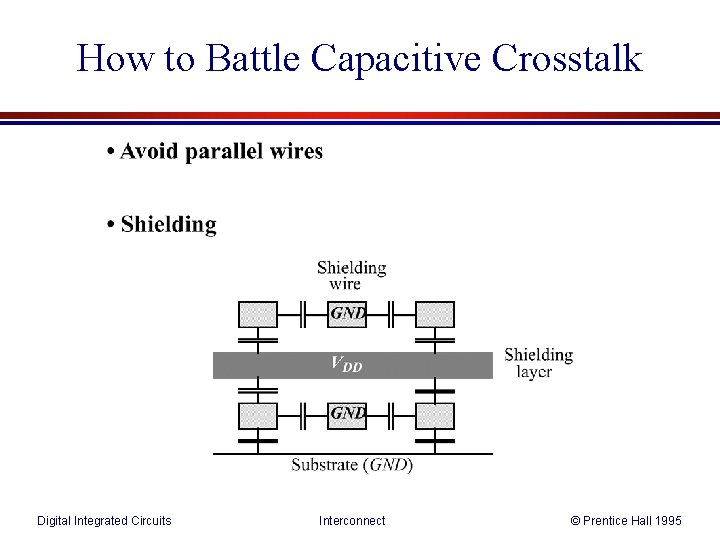

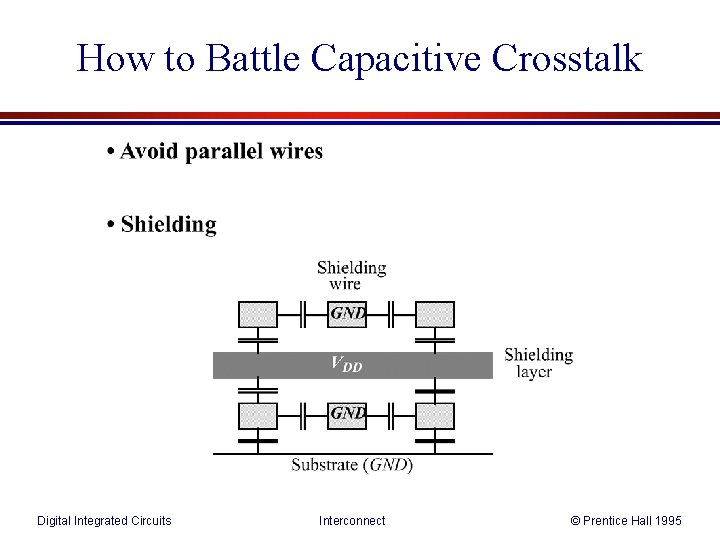

How to Battle Capacitive Crosstalk Digital Integrated Circuits Interconnect © Prentice Hall 1995

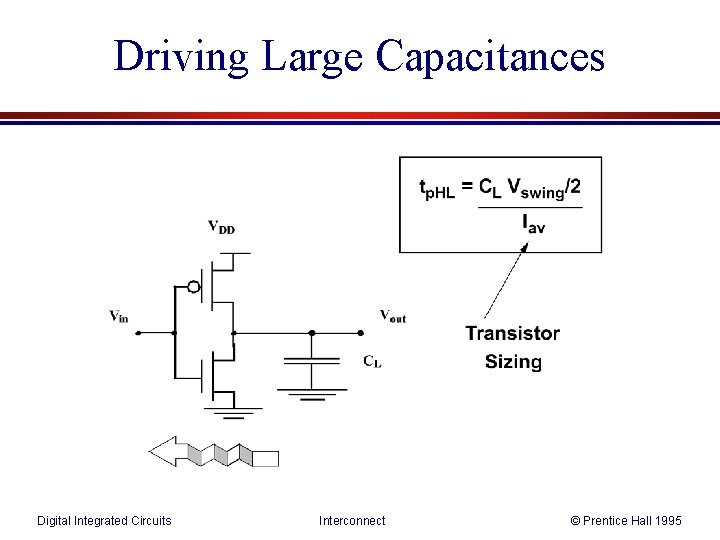

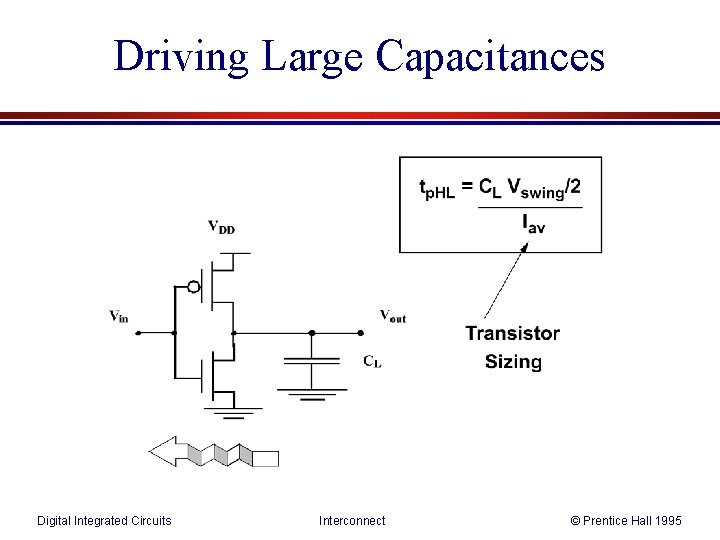

Driving Large Capacitances Digital Integrated Circuits Interconnect © Prentice Hall 1995

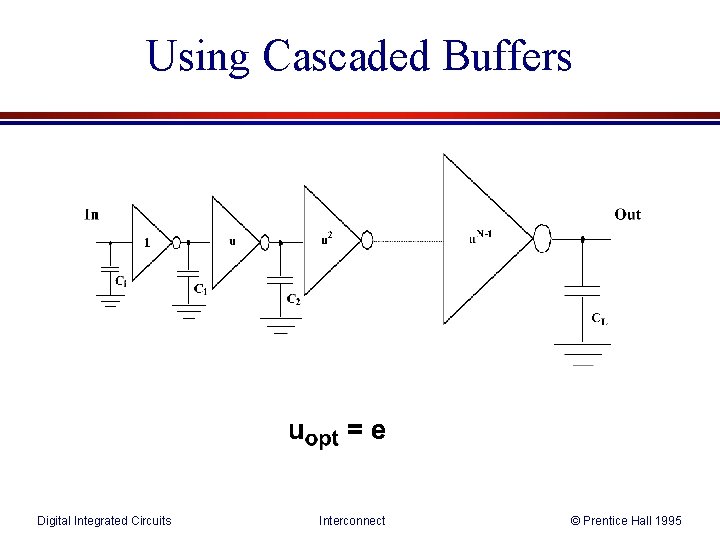

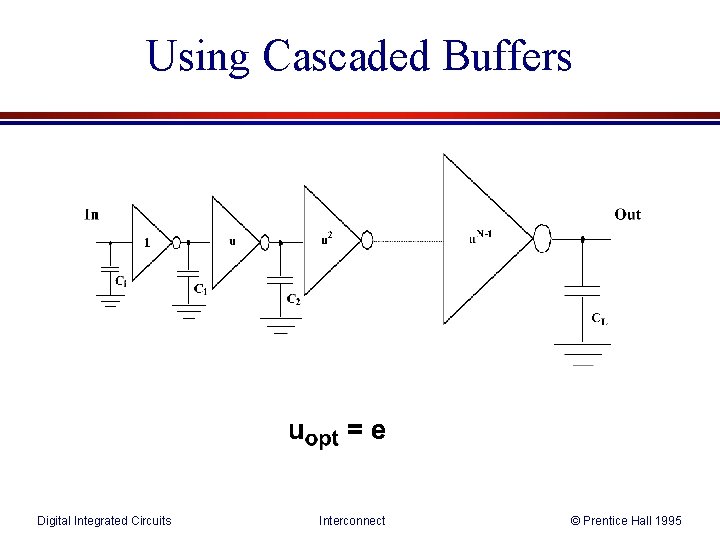

Using Cascaded Buffers Digital Integrated Circuits Interconnect © Prentice Hall 1995

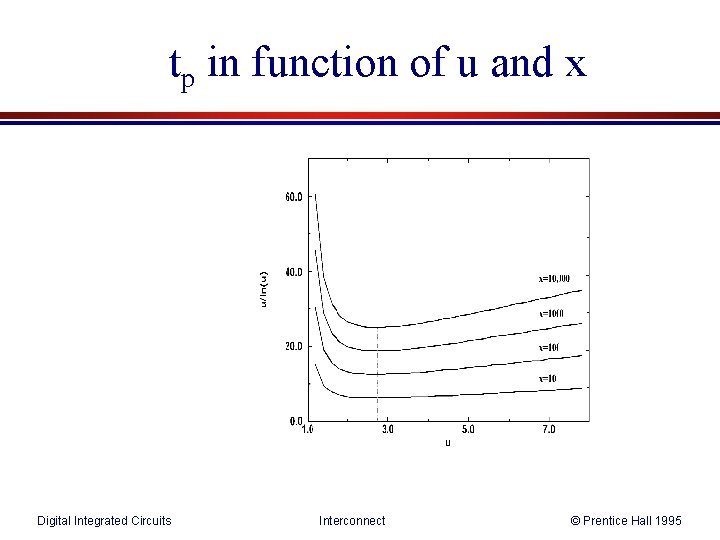

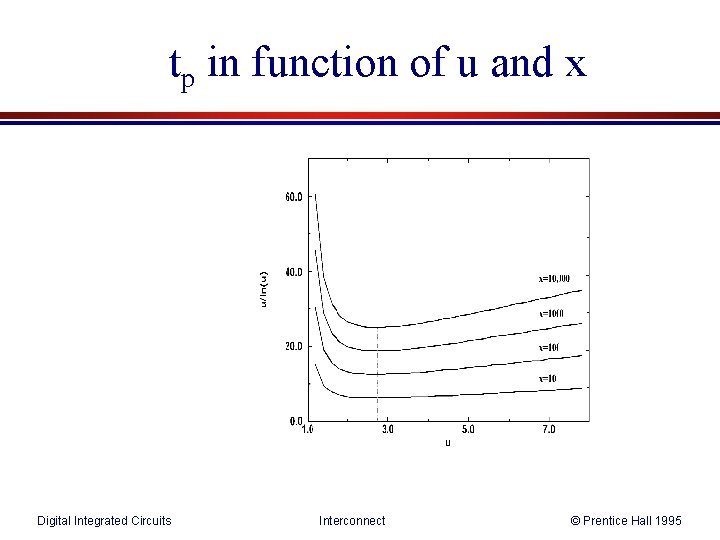

tp in function of u and x Digital Integrated Circuits Interconnect © Prentice Hall 1995

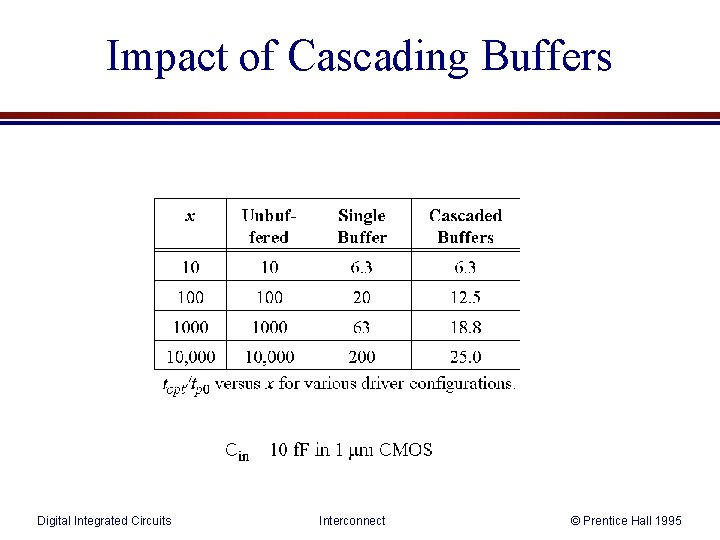

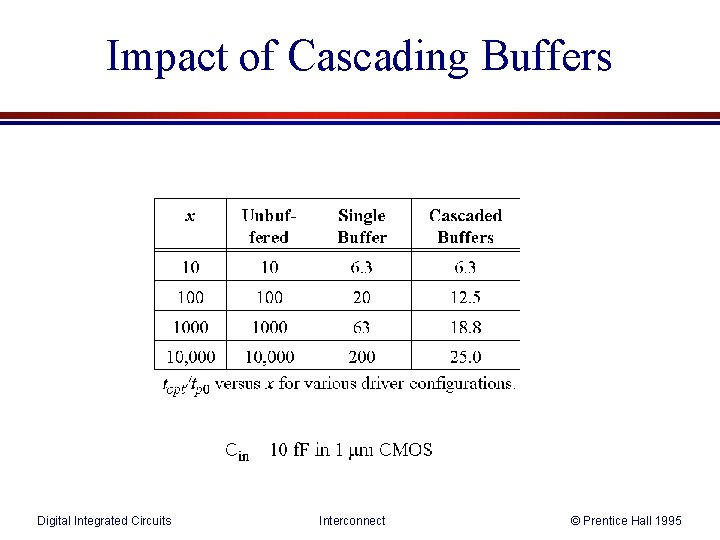

Impact of Cascading Buffers Digital Integrated Circuits Interconnect © Prentice Hall 1995

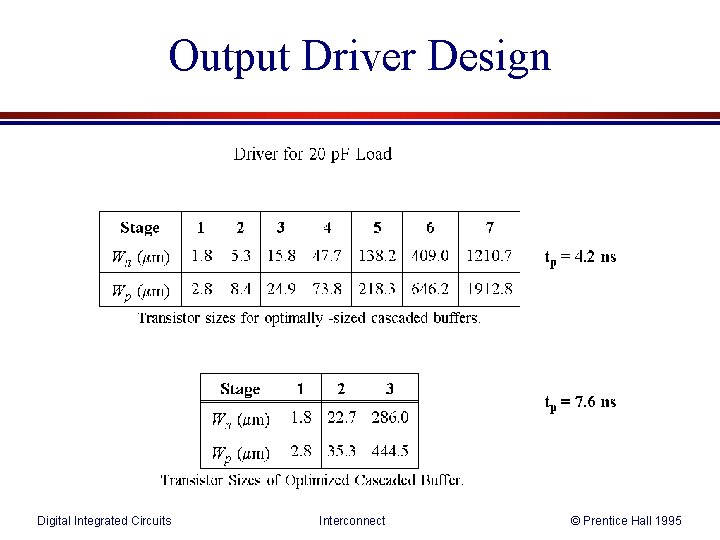

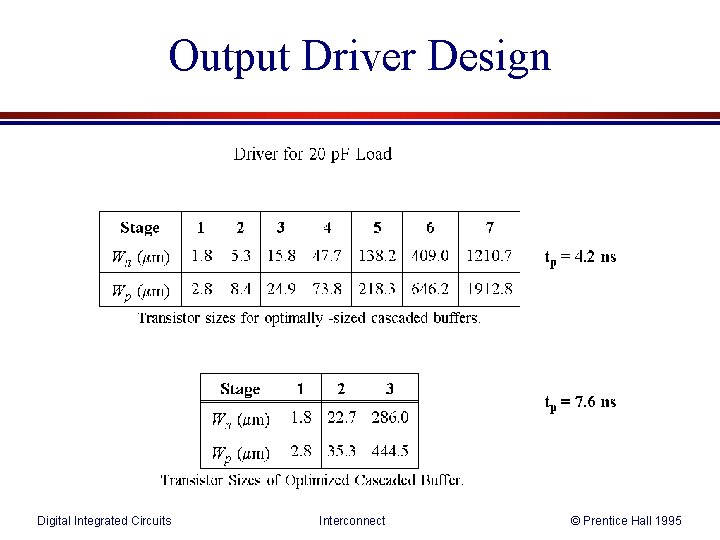

Output Driver Design Digital Integrated Circuits Interconnect © Prentice Hall 1995

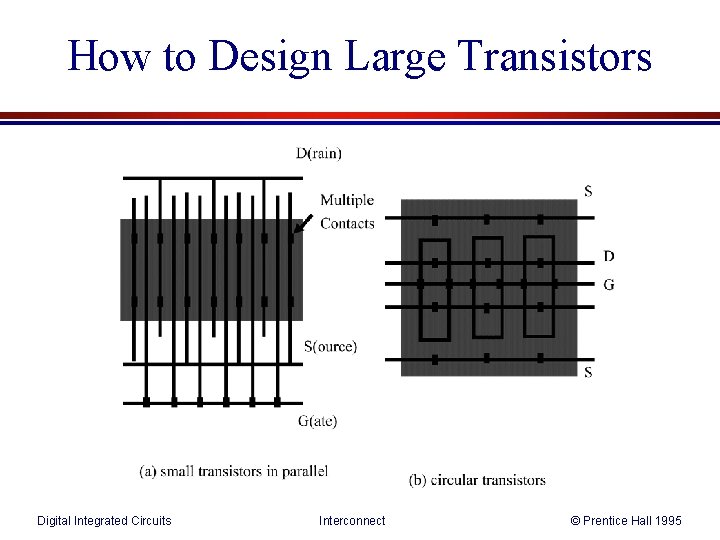

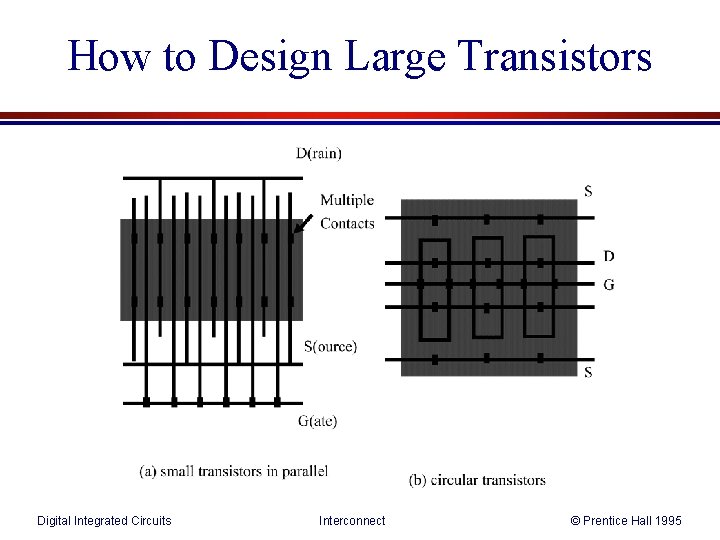

How to Design Large Transistors Digital Integrated Circuits Interconnect © Prentice Hall 1995

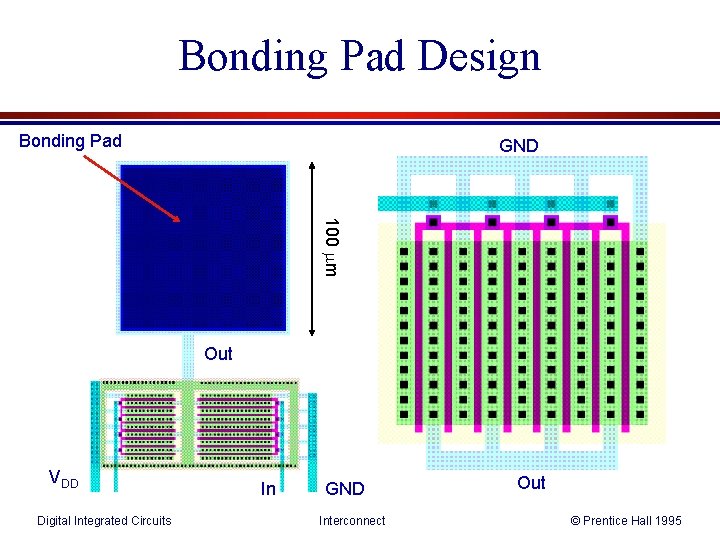

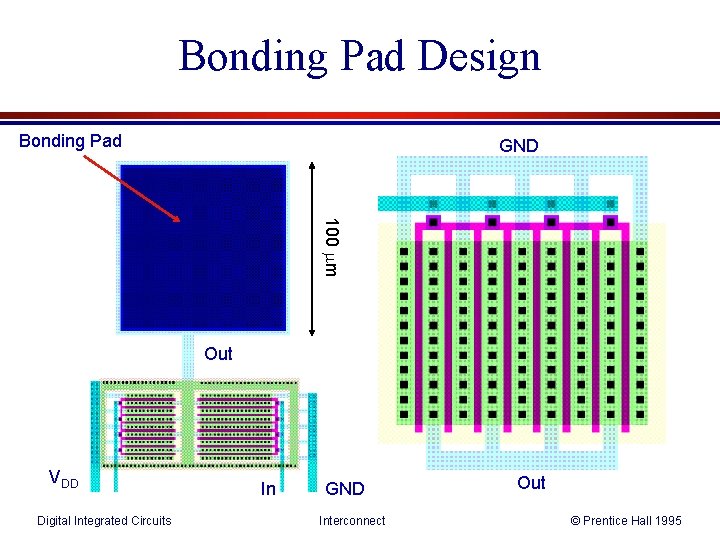

Bonding Pad Design Bonding Pad GND 100 mm Out VDD Digital Integrated Circuits In GND Interconnect Out © Prentice Hall 1995

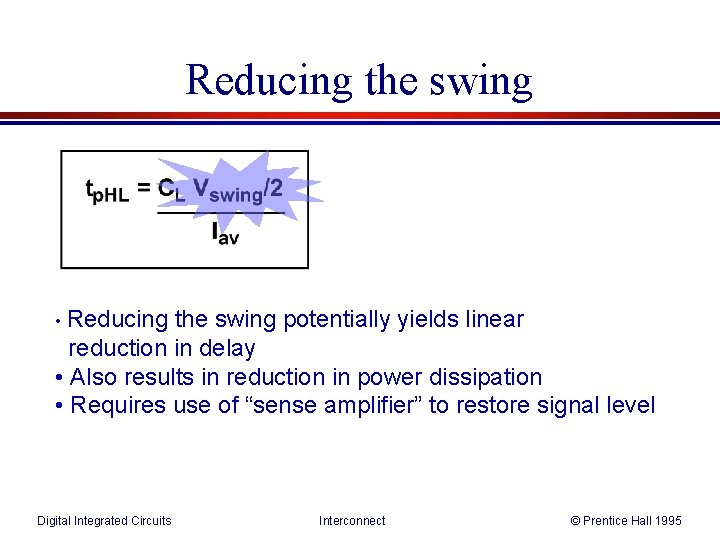

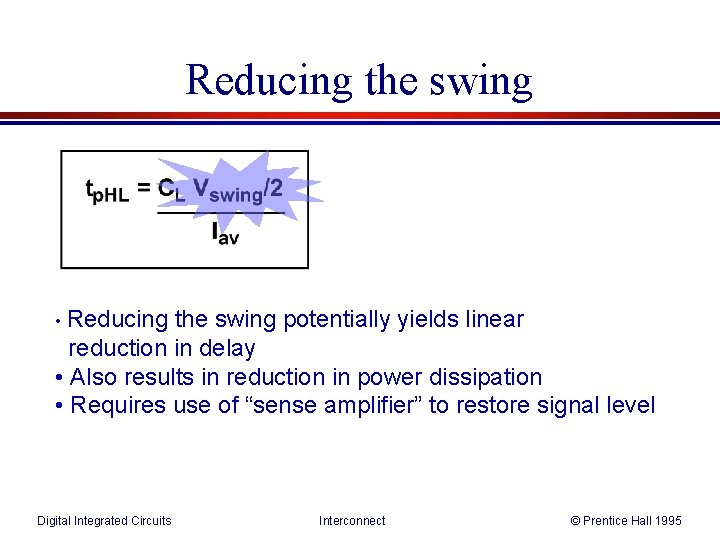

Reducing the swing • Reducing the swing potentially yields linear reduction in delay • Also results in reduction in power dissipation • Requires use of “sense amplifier” to restore signal level Digital Integrated Circuits Interconnect © Prentice Hall 1995

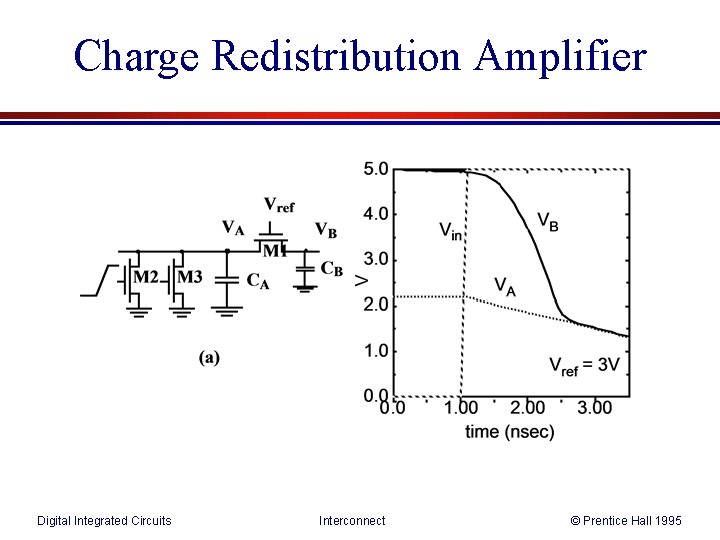

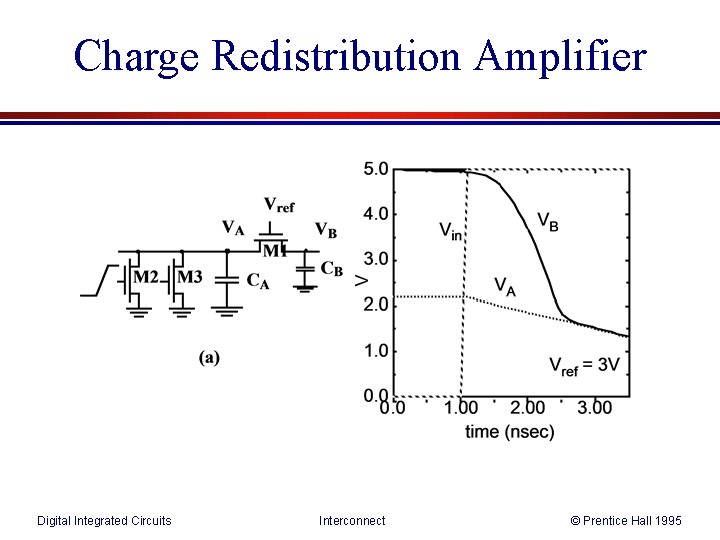

Charge Redistribution Amplifier Digital Integrated Circuits Interconnect © Prentice Hall 1995

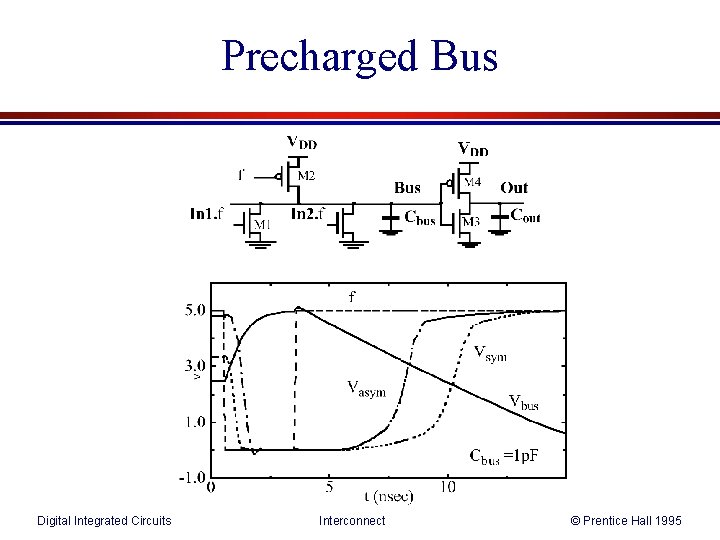

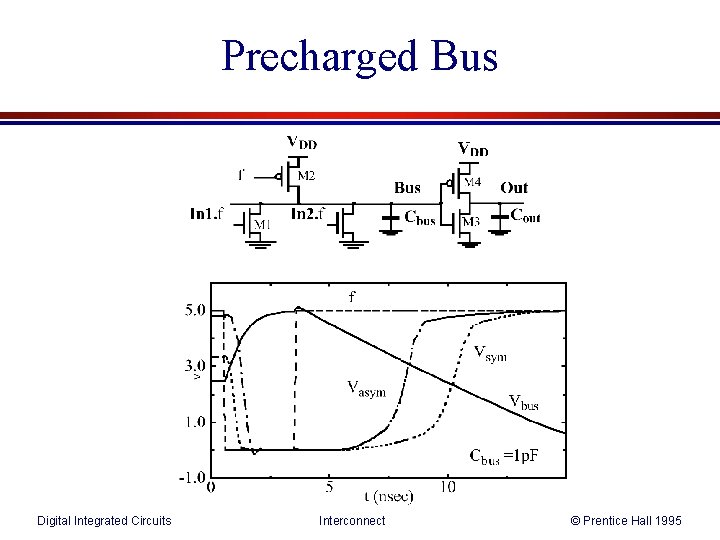

Precharged Bus Digital Integrated Circuits Interconnect © Prentice Hall 1995

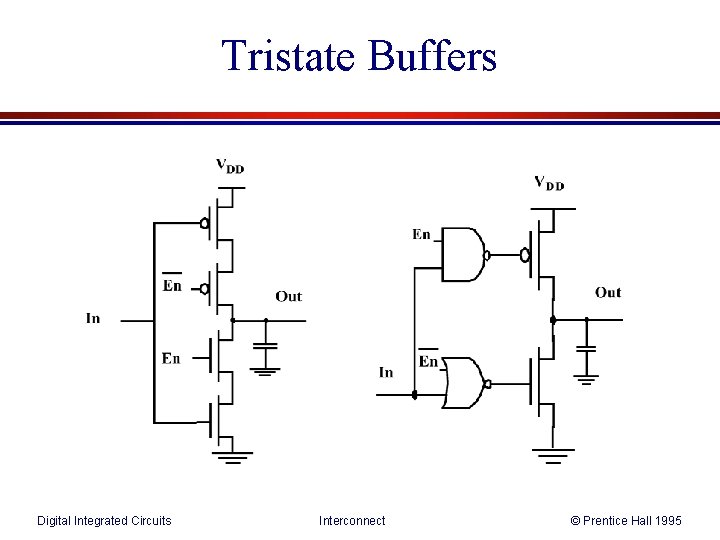

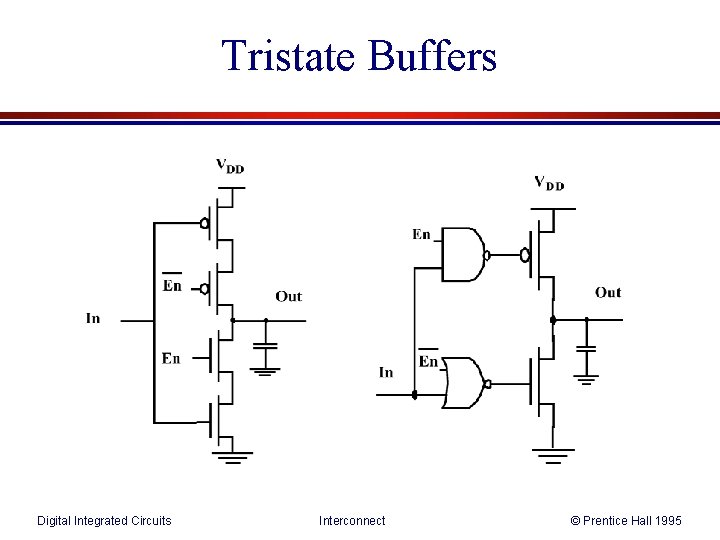

Tristate Buffers Digital Integrated Circuits Interconnect © Prentice Hall 1995

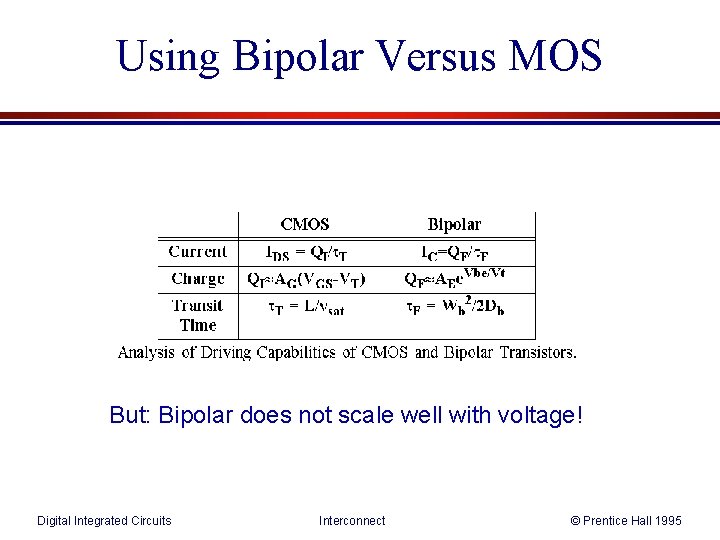

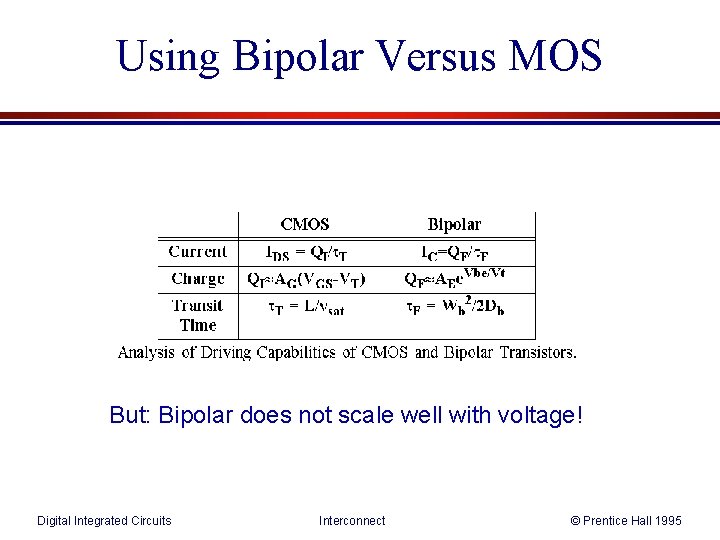

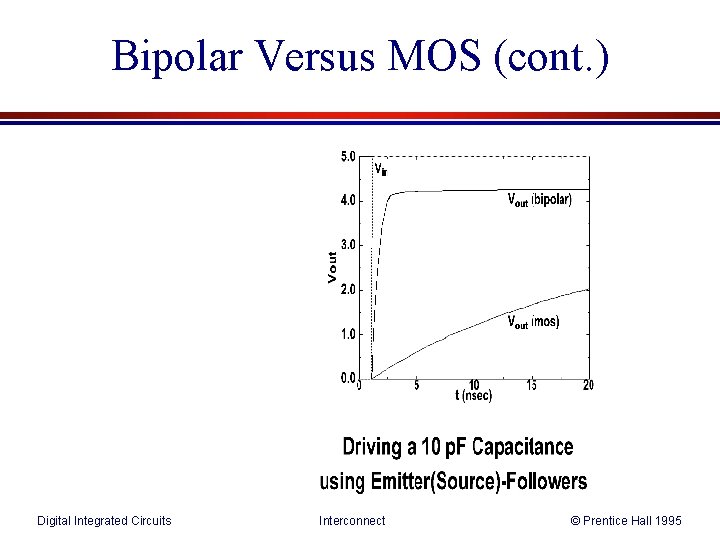

Using Bipolar Versus MOS But: Bipolar does not scale well with voltage! Digital Integrated Circuits Interconnect © Prentice Hall 1995

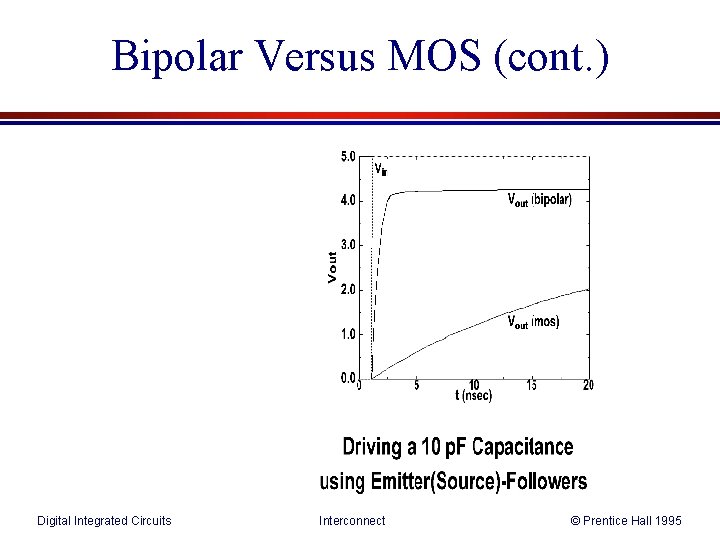

Bipolar Versus MOS (cont. ) Digital Integrated Circuits Interconnect © Prentice Hall 1995

INTERCONNECT Digital Integrated Circuits Interconnect © Prentice Hall 1995

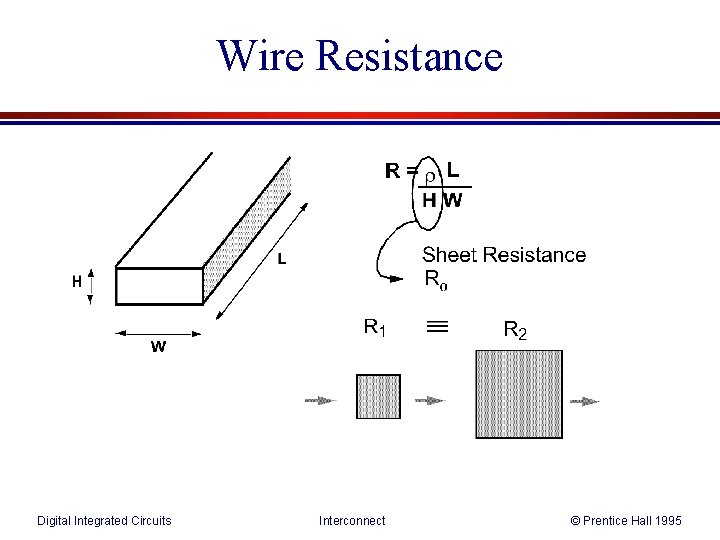

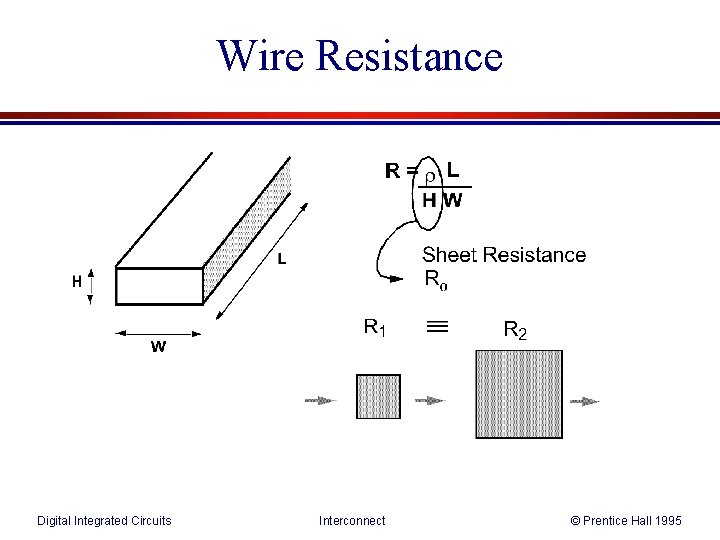

Wire Resistance Digital Integrated Circuits Interconnect © Prentice Hall 1995

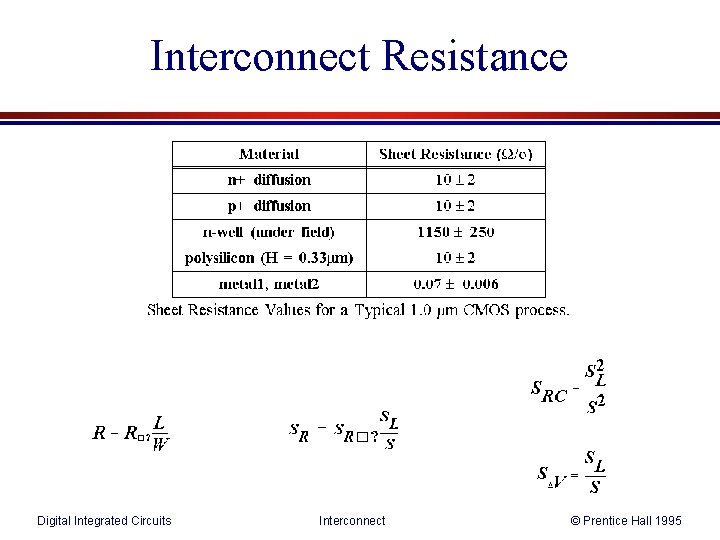

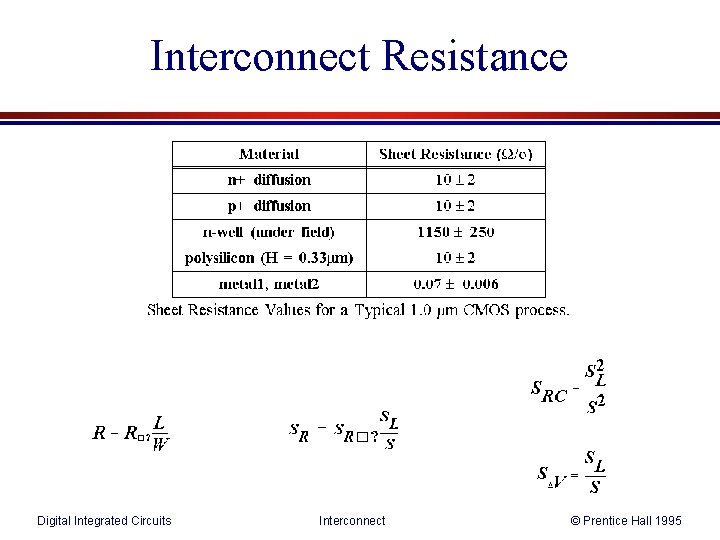

Interconnect Resistance Digital Integrated Circuits Interconnect © Prentice Hall 1995

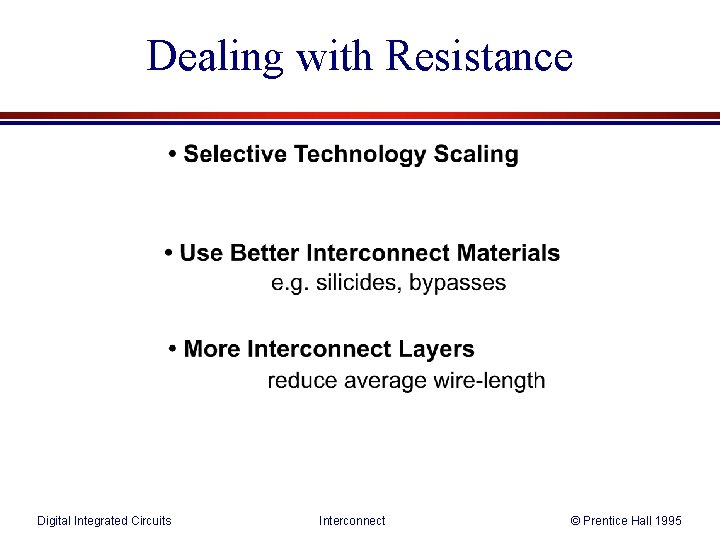

Dealing with Resistance Digital Integrated Circuits Interconnect © Prentice Hall 1995

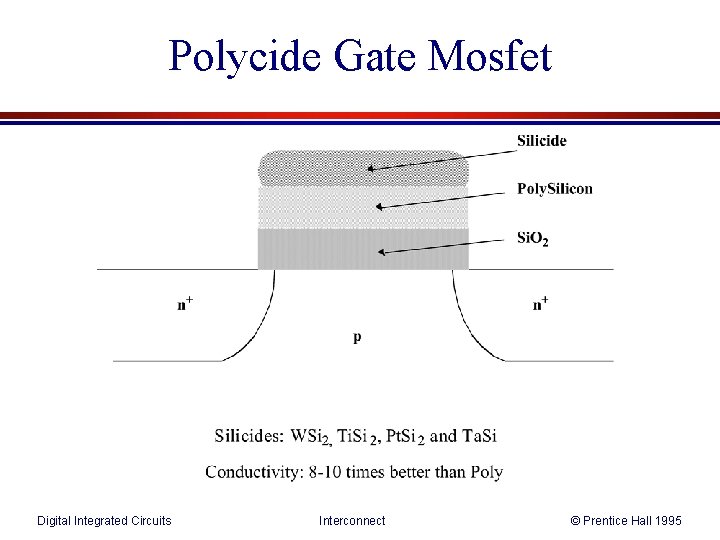

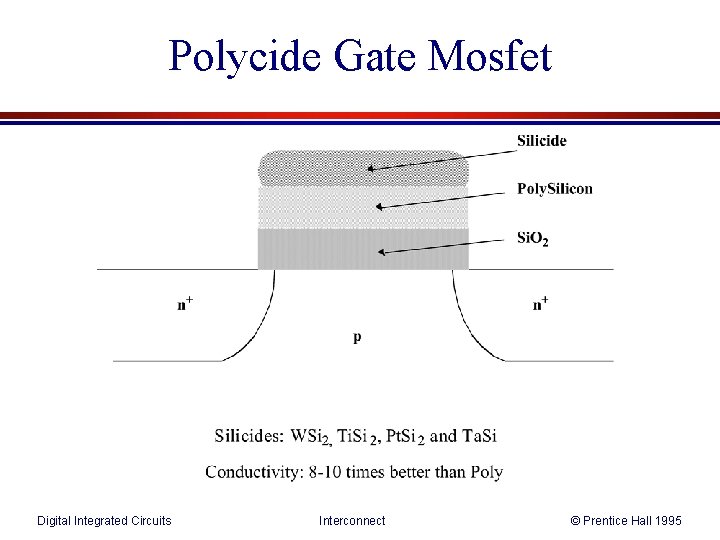

Polycide Gate Mosfet Digital Integrated Circuits Interconnect © Prentice Hall 1995

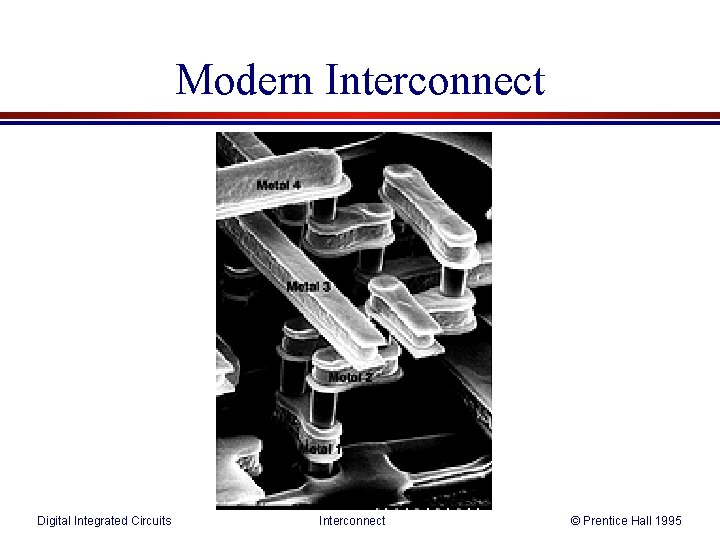

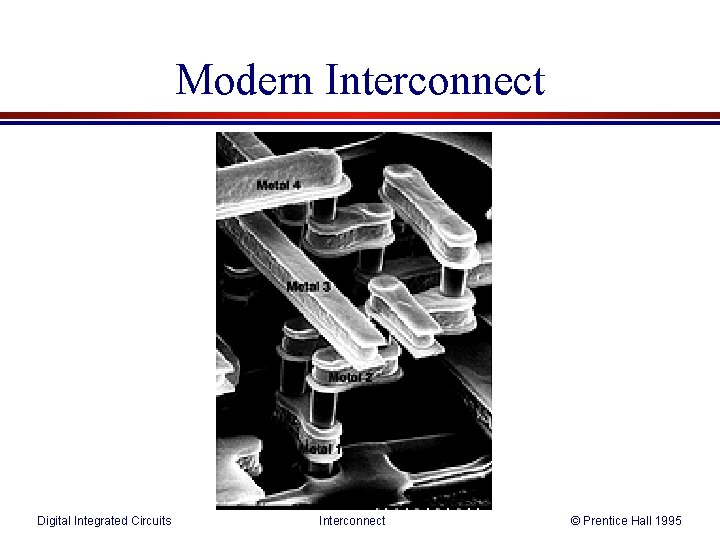

Modern Interconnect Digital Integrated Circuits Interconnect © Prentice Hall 1995

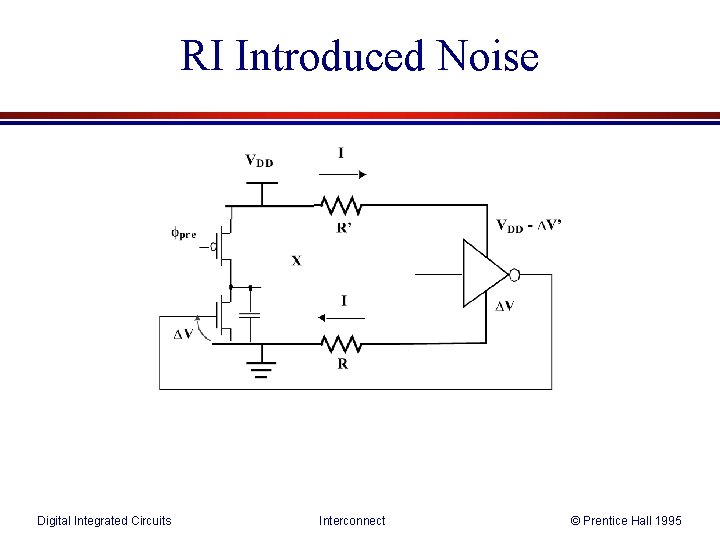

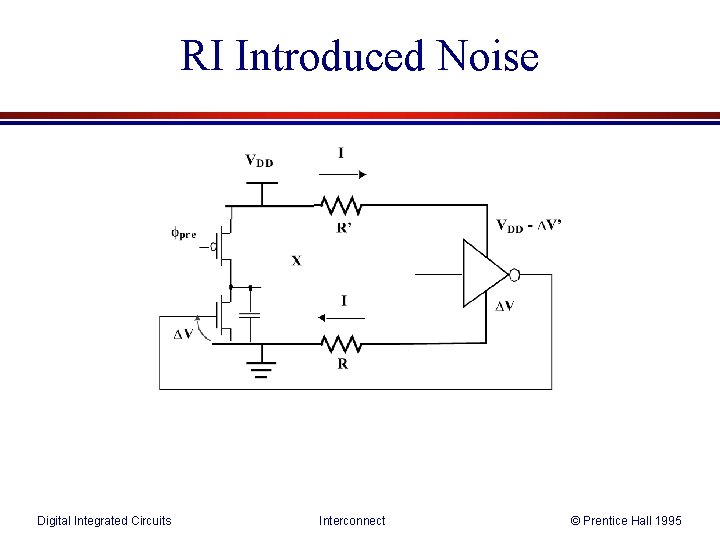

RI Introduced Noise Digital Integrated Circuits Interconnect © Prentice Hall 1995

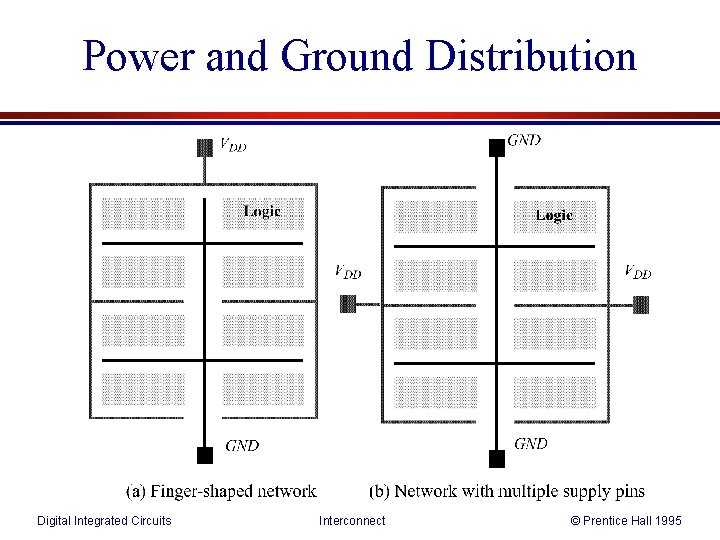

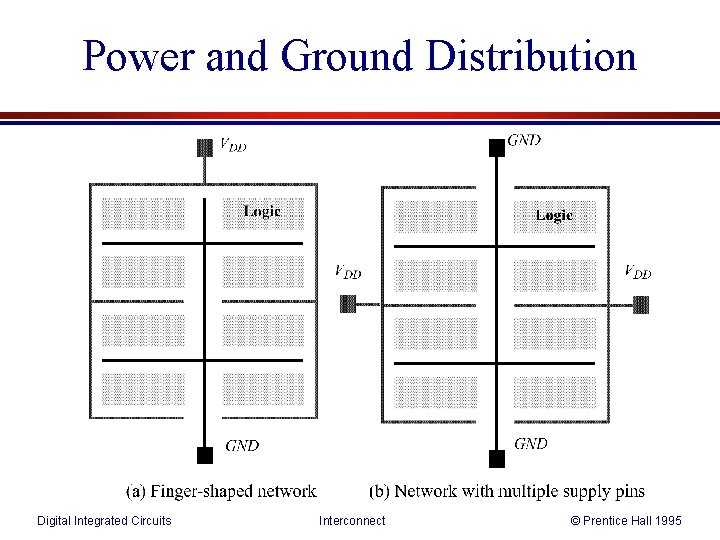

Power and Ground Distribution Digital Integrated Circuits Interconnect © Prentice Hall 1995

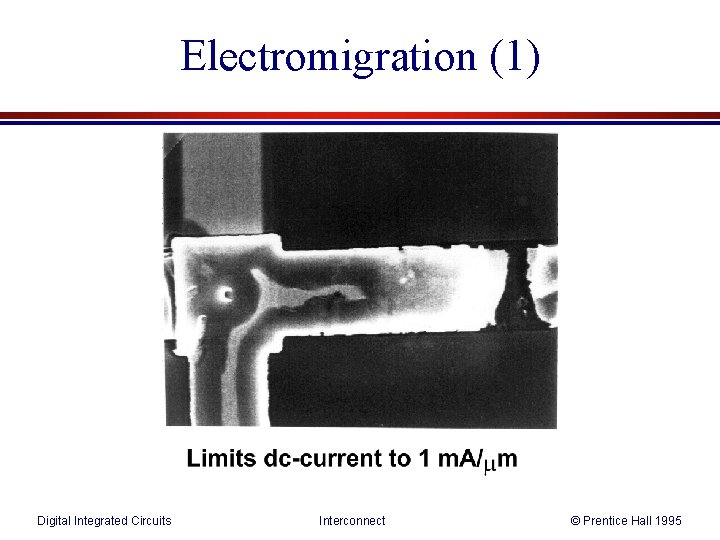

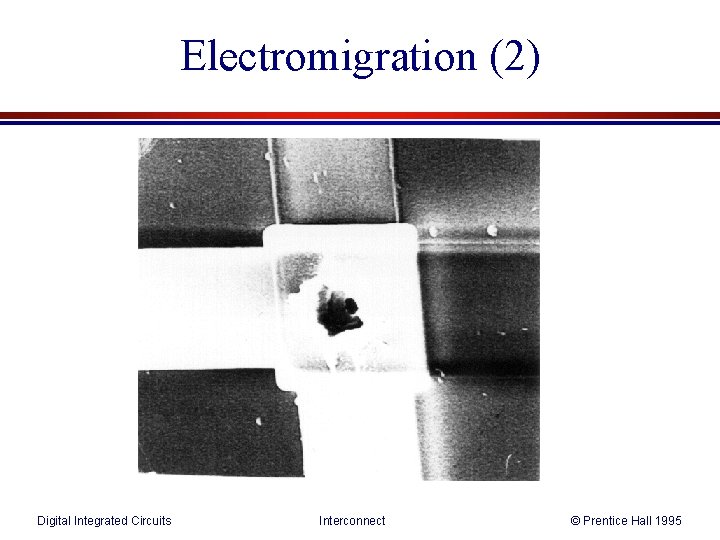

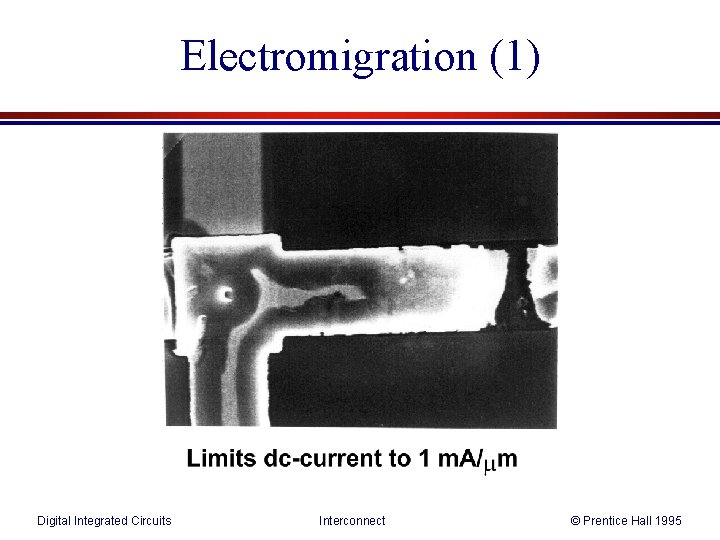

Electromigration (1) Digital Integrated Circuits Interconnect © Prentice Hall 1995

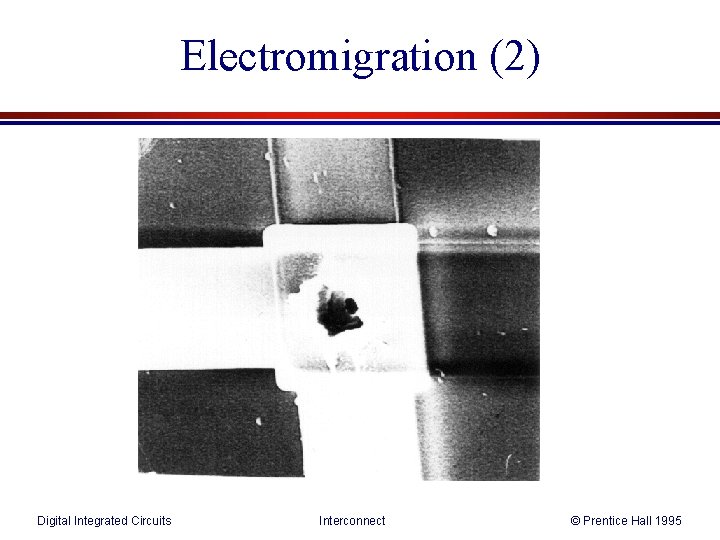

Electromigration (2) Digital Integrated Circuits Interconnect © Prentice Hall 1995

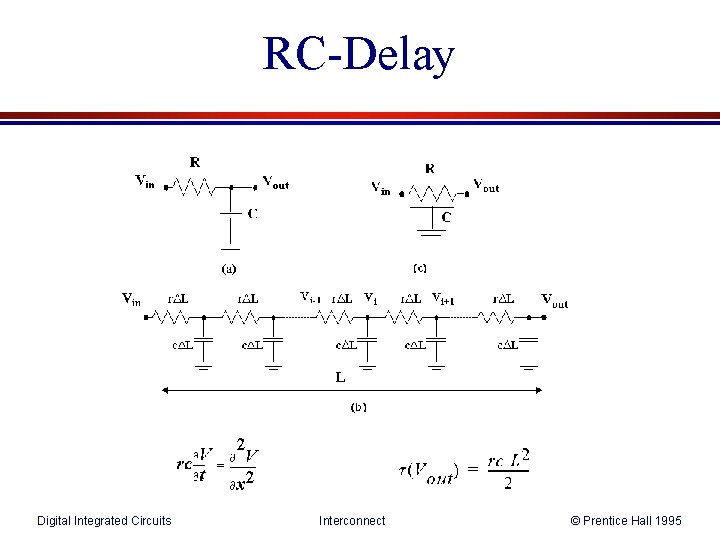

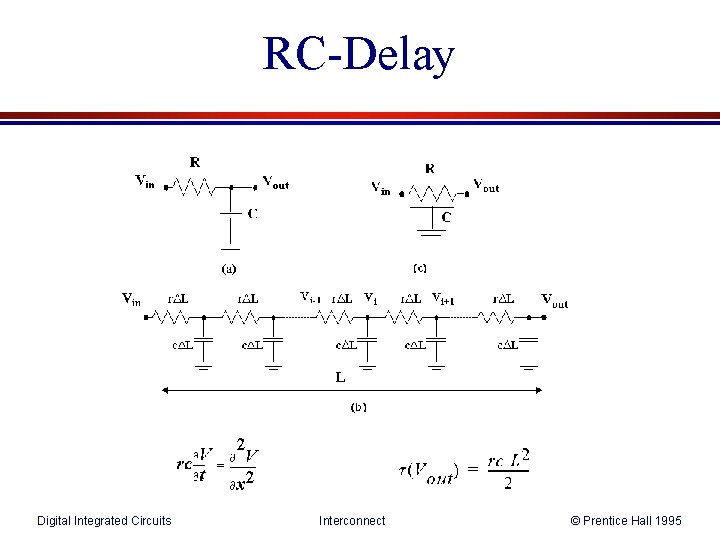

RC-Delay Digital Integrated Circuits Interconnect © Prentice Hall 1995

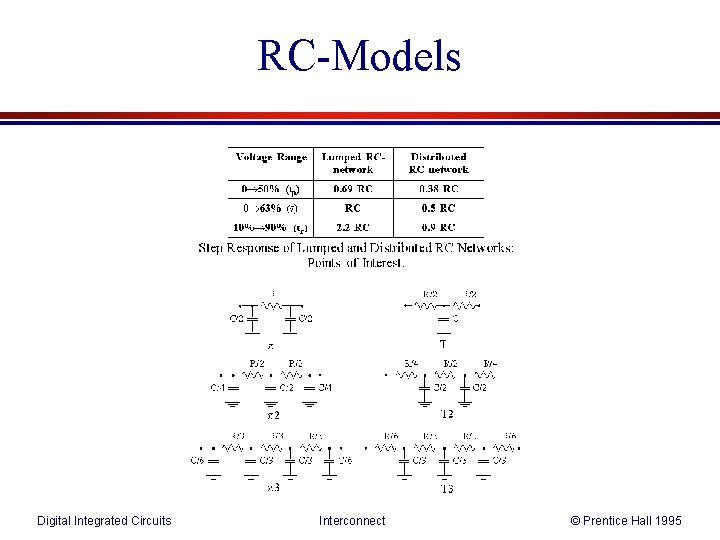

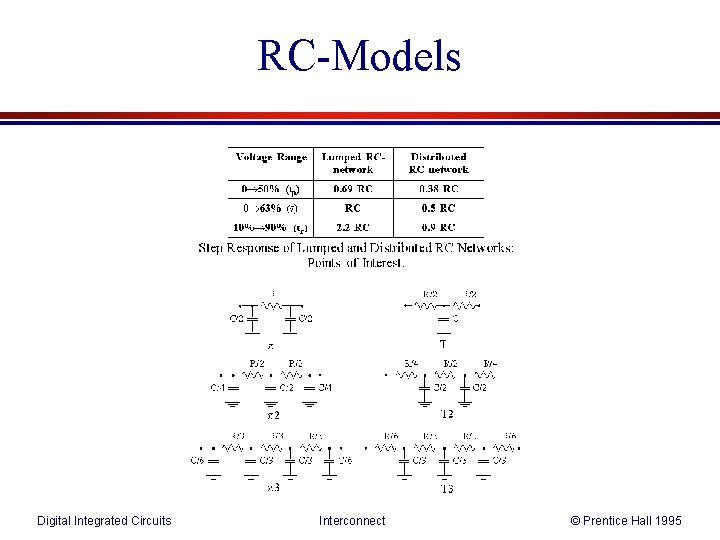

RC-Models Digital Integrated Circuits Interconnect © Prentice Hall 1995

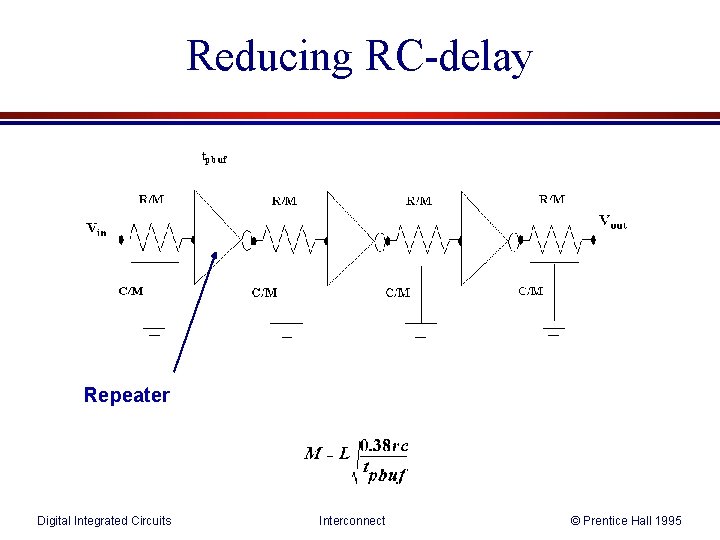

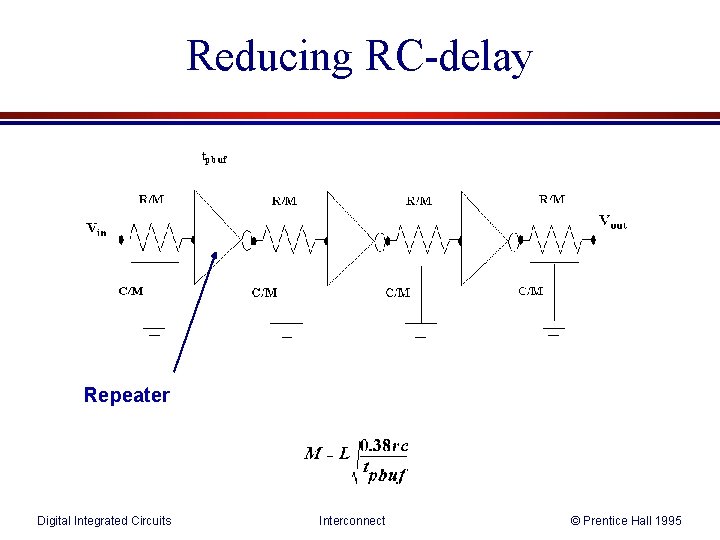

Reducing RC-delay Repeater Digital Integrated Circuits Interconnect © Prentice Hall 1995

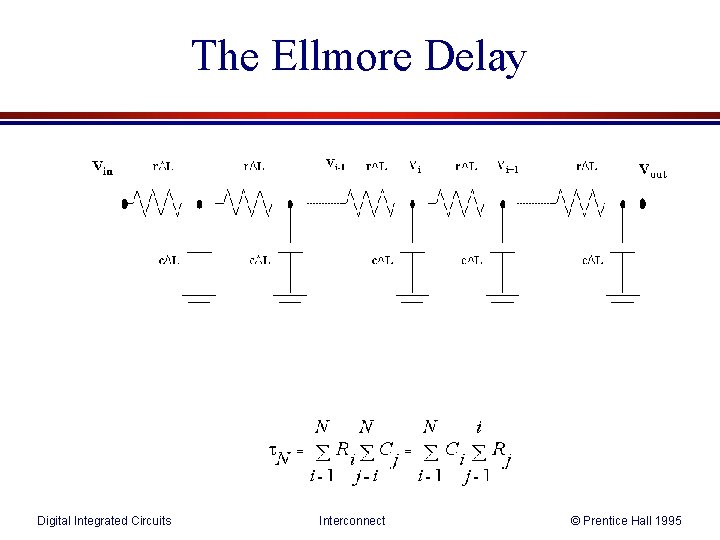

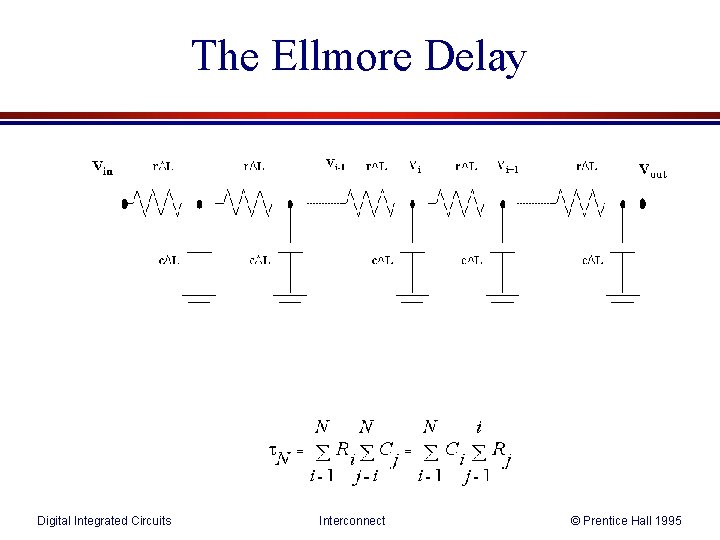

The Ellmore Delay Digital Integrated Circuits Interconnect © Prentice Hall 1995

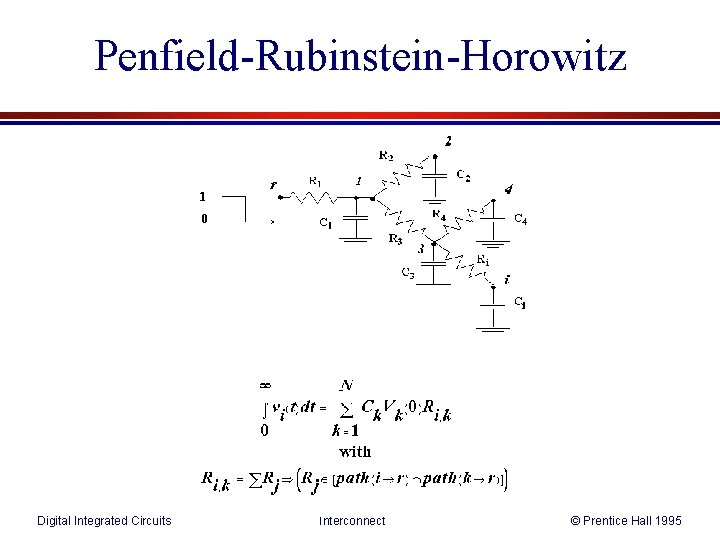

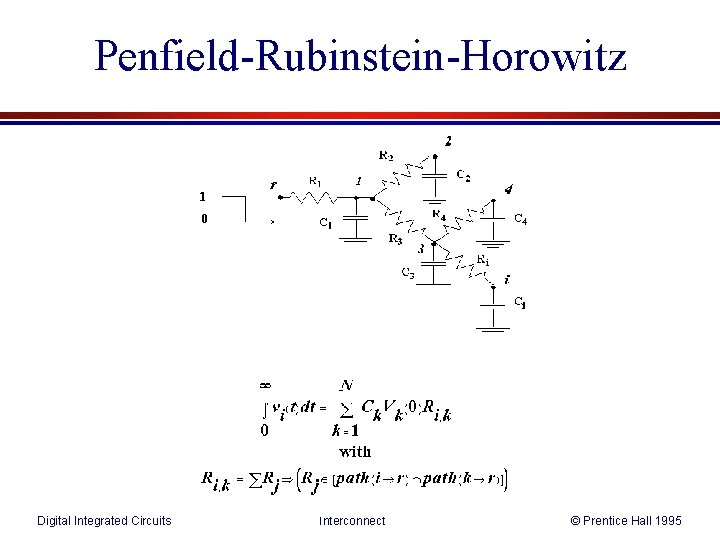

Penfield-Rubinstein-Horowitz Digital Integrated Circuits Interconnect © Prentice Hall 1995

INTERCONNECT Digital Integrated Circuits Interconnect © Prentice Hall 1995

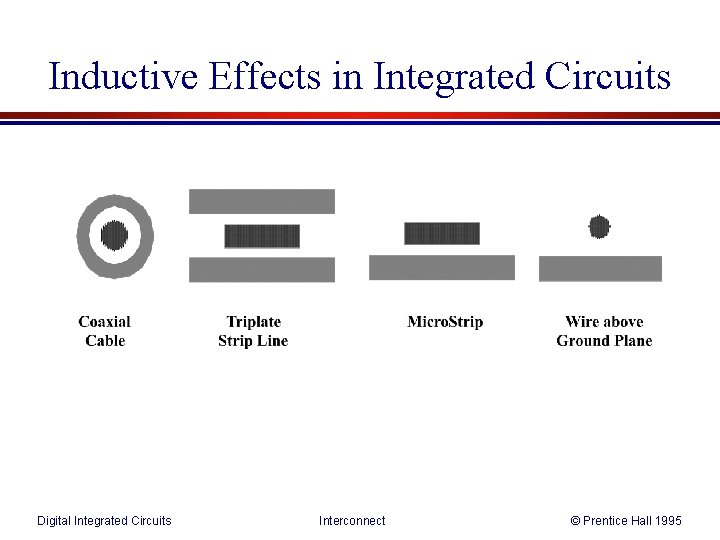

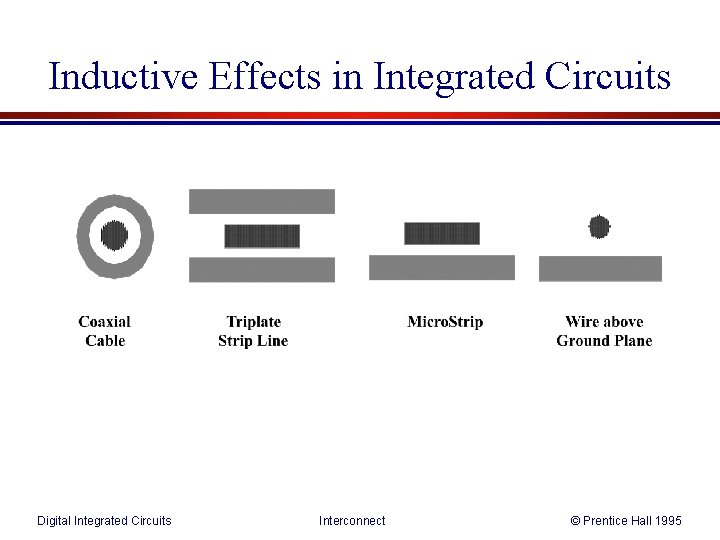

Inductive Effects in Integrated Circuits Digital Integrated Circuits Interconnect © Prentice Hall 1995

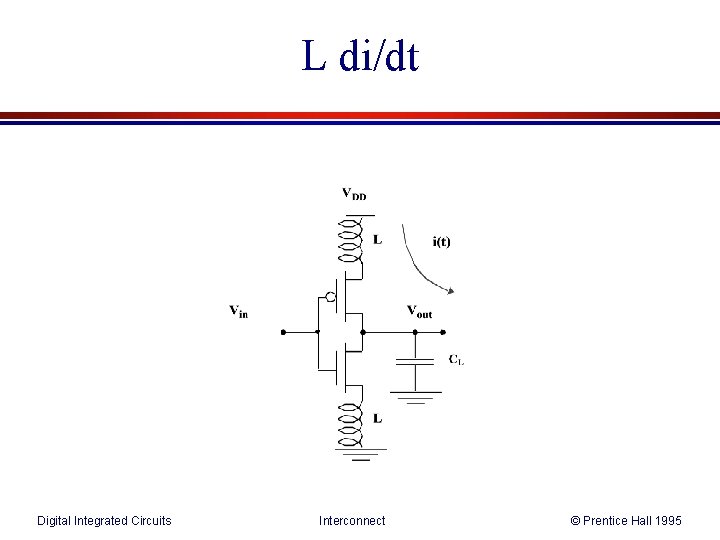

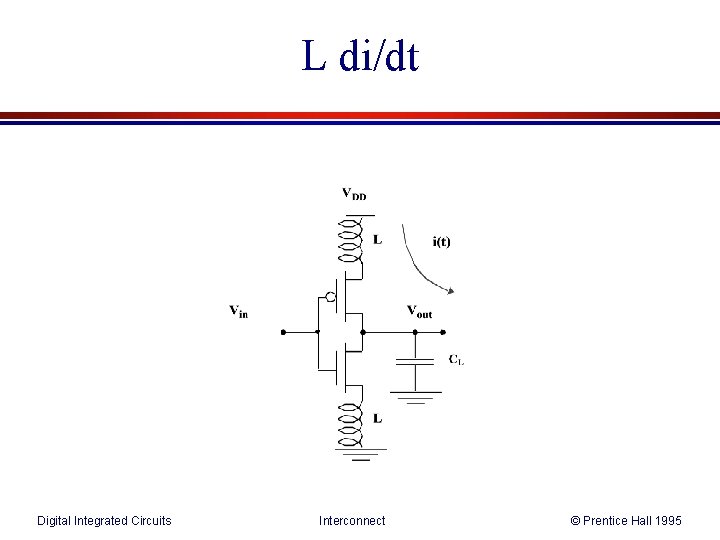

L di/dt Digital Integrated Circuits Interconnect © Prentice Hall 1995

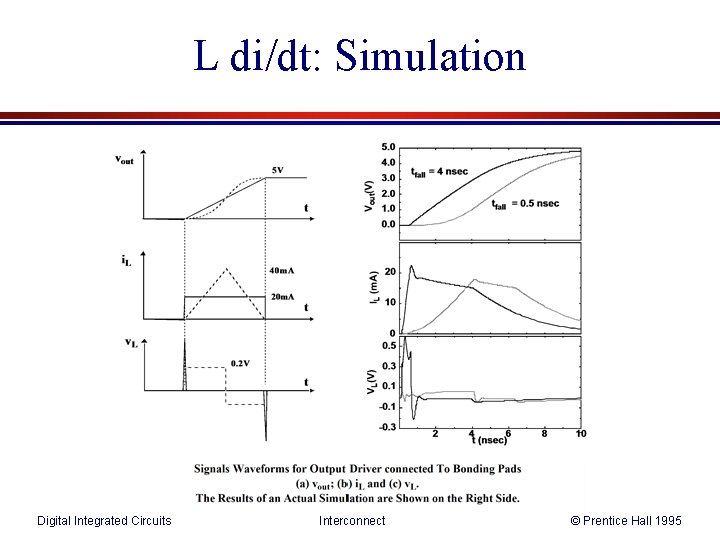

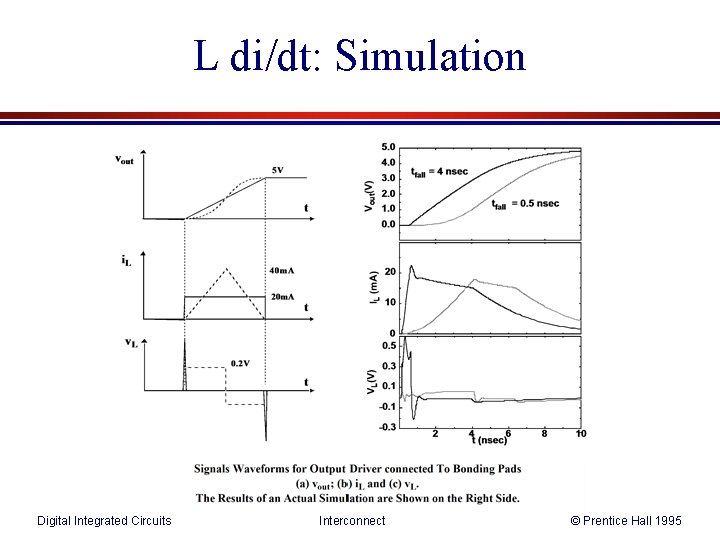

L di/dt: Simulation Digital Integrated Circuits Interconnect © Prentice Hall 1995

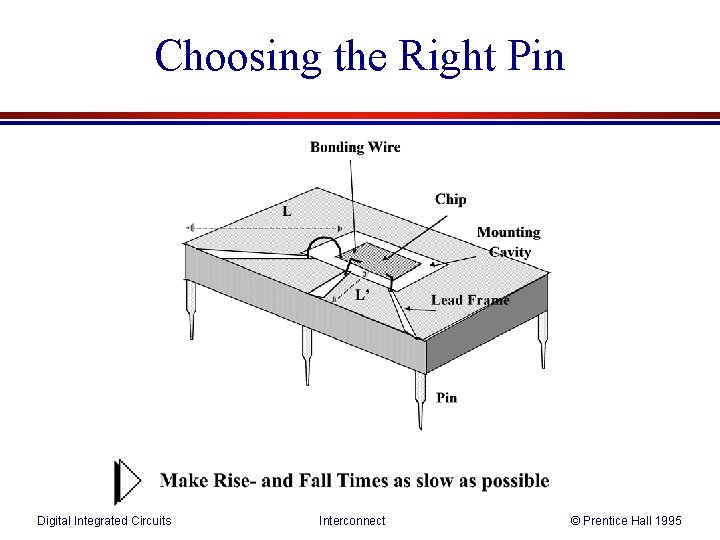

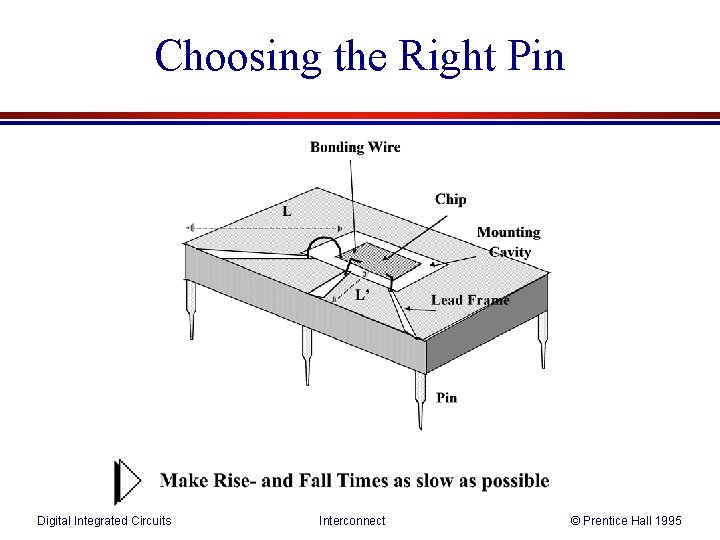

Choosing the Right Pin Digital Integrated Circuits Interconnect © Prentice Hall 1995

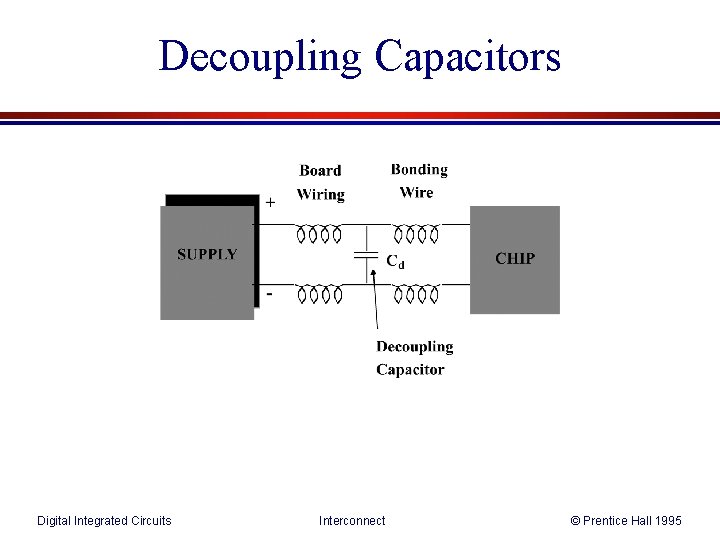

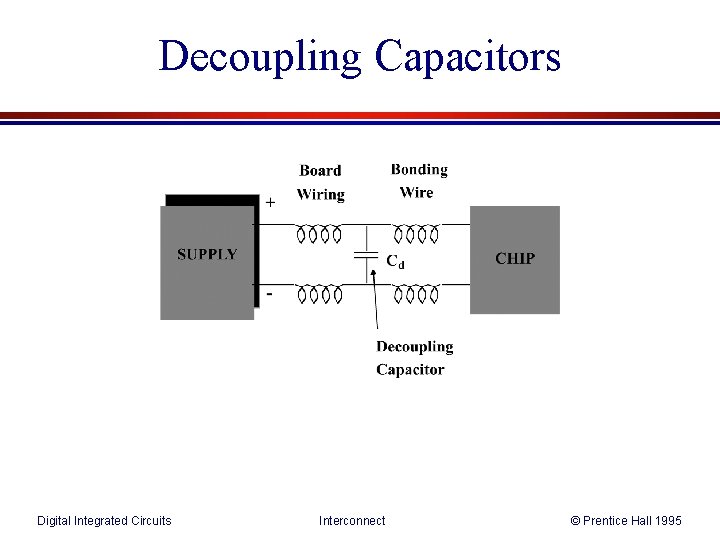

Decoupling Capacitors Digital Integrated Circuits Interconnect © Prentice Hall 1995

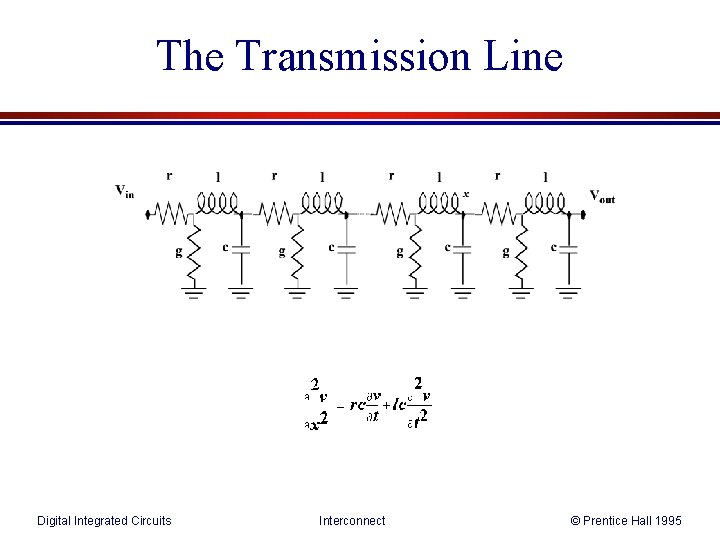

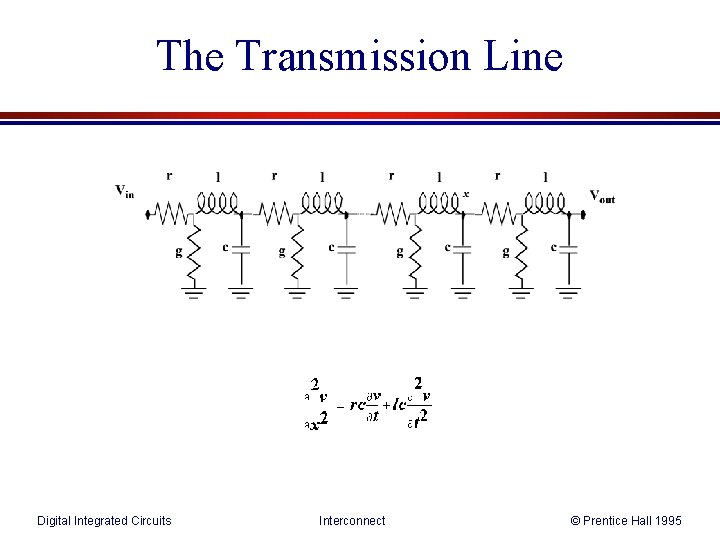

The Transmission Line Digital Integrated Circuits Interconnect © Prentice Hall 1995

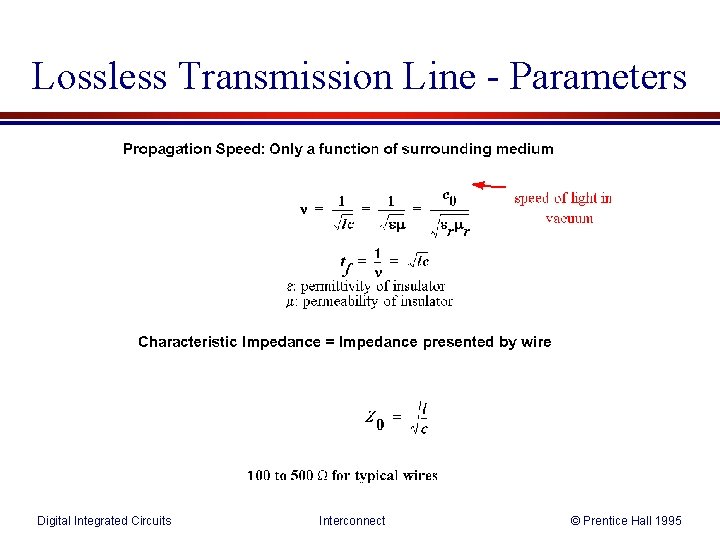

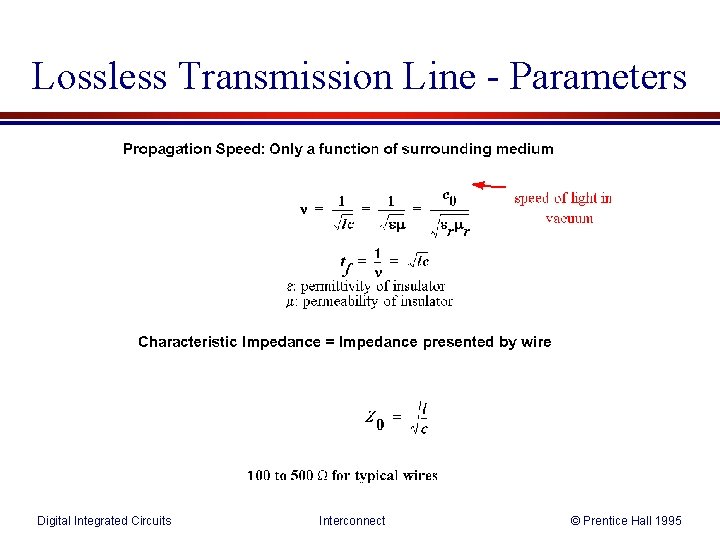

Lossless Transmission Line - Parameters Digital Integrated Circuits Interconnect © Prentice Hall 1995

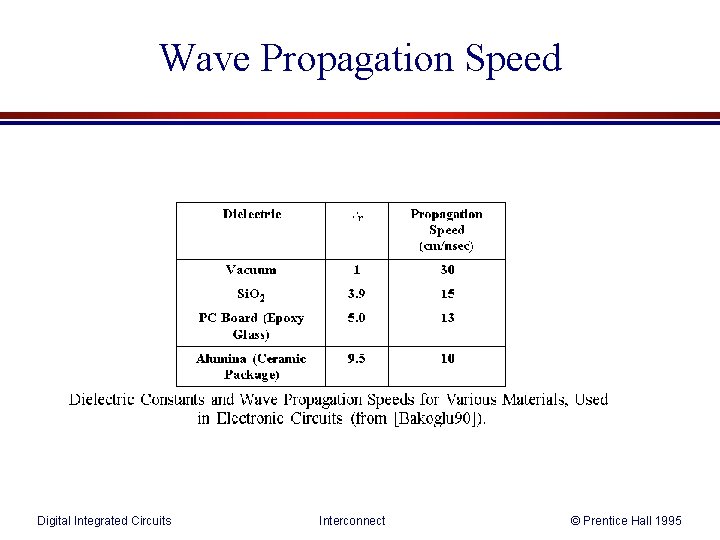

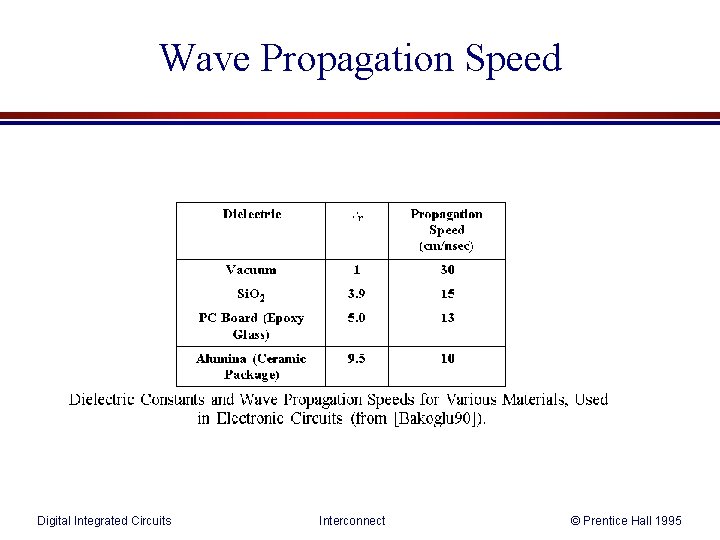

Wave Propagation Speed Digital Integrated Circuits Interconnect © Prentice Hall 1995

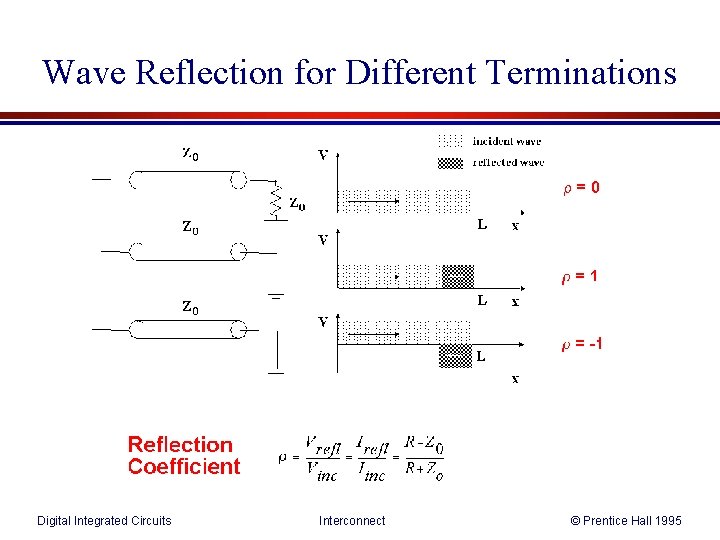

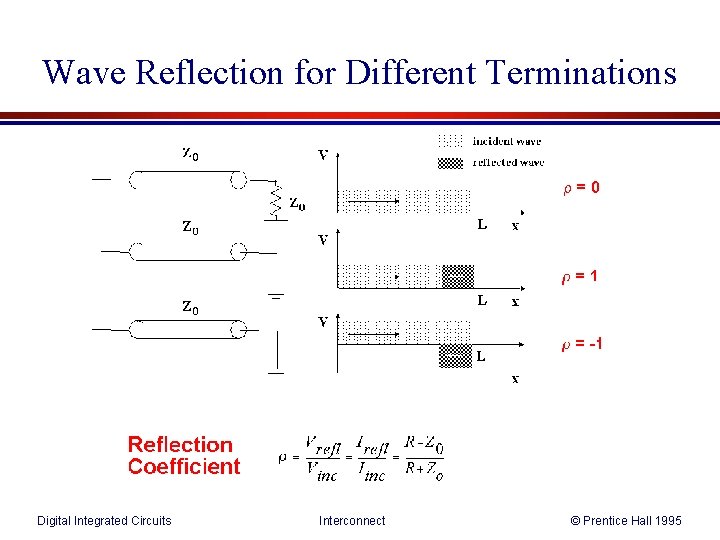

Wave Reflection for Different Terminations Digital Integrated Circuits Interconnect © Prentice Hall 1995

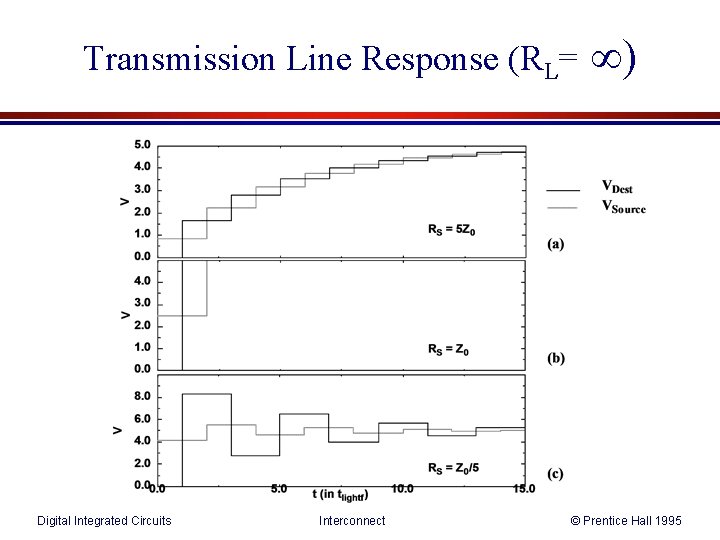

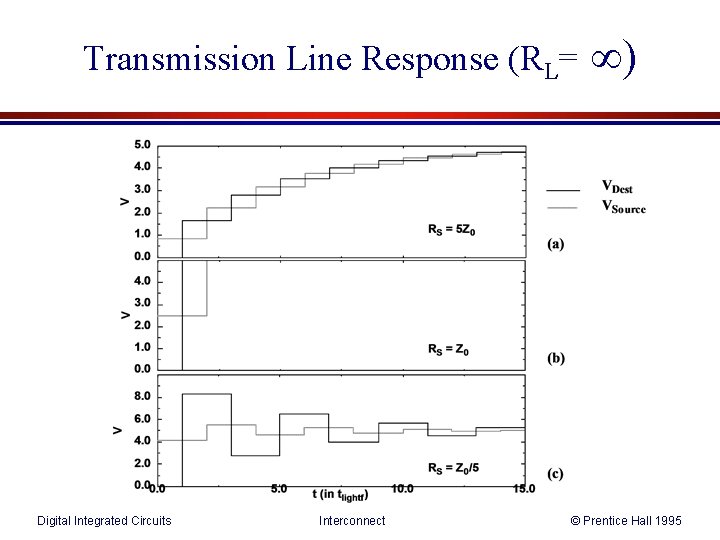

Transmission Line Response (RL= Digital Integrated Circuits Interconnect ) © Prentice Hall 1995

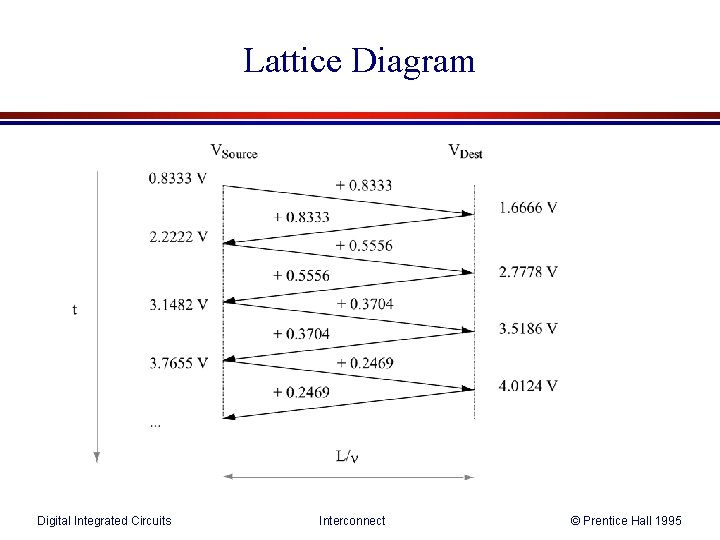

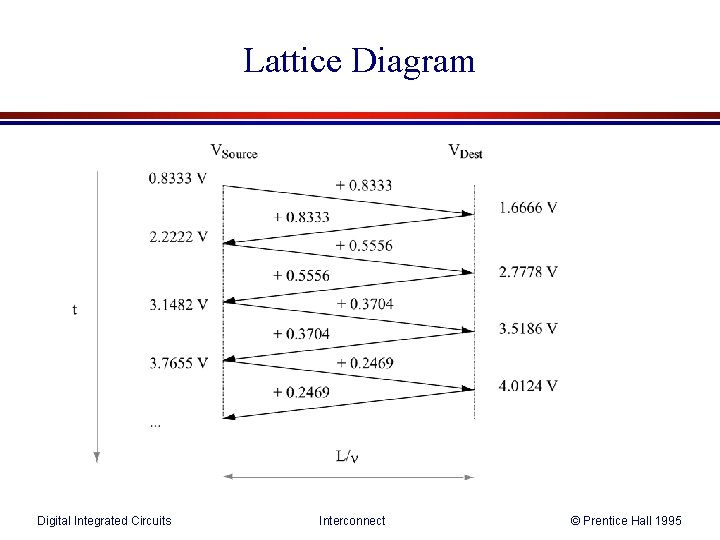

Lattice Diagram Digital Integrated Circuits Interconnect © Prentice Hall 1995

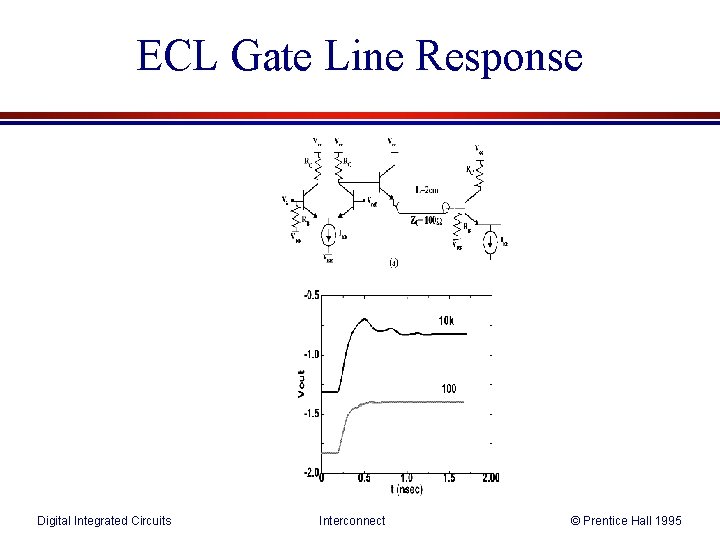

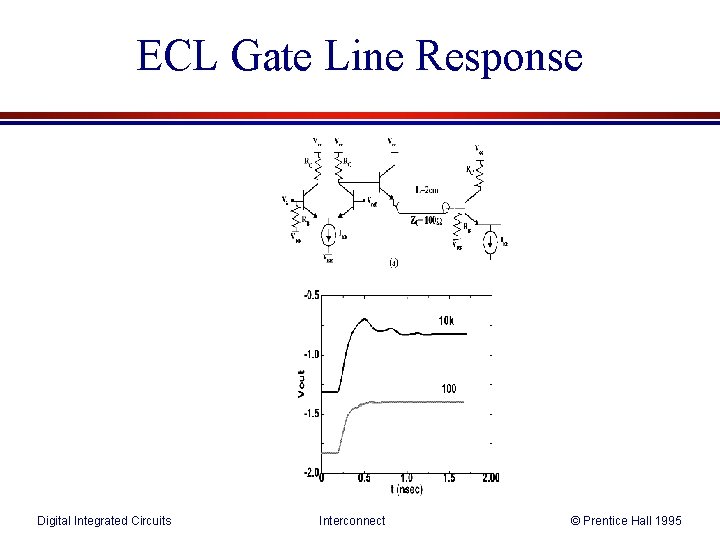

ECL Gate Line Response Digital Integrated Circuits Interconnect © Prentice Hall 1995

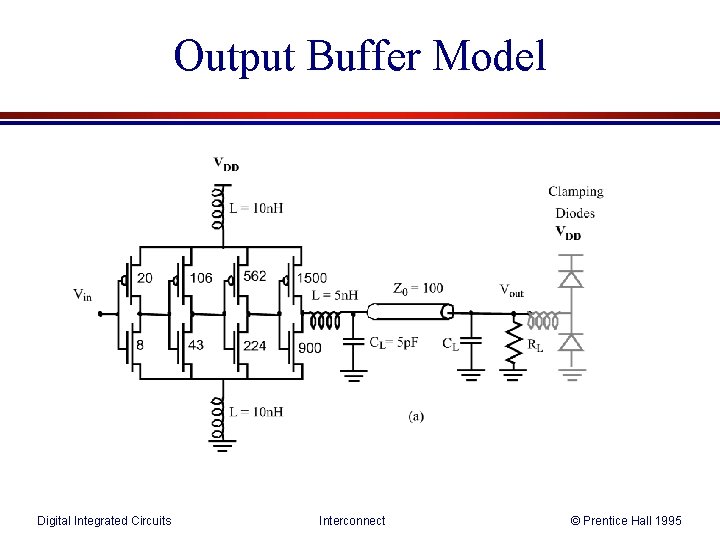

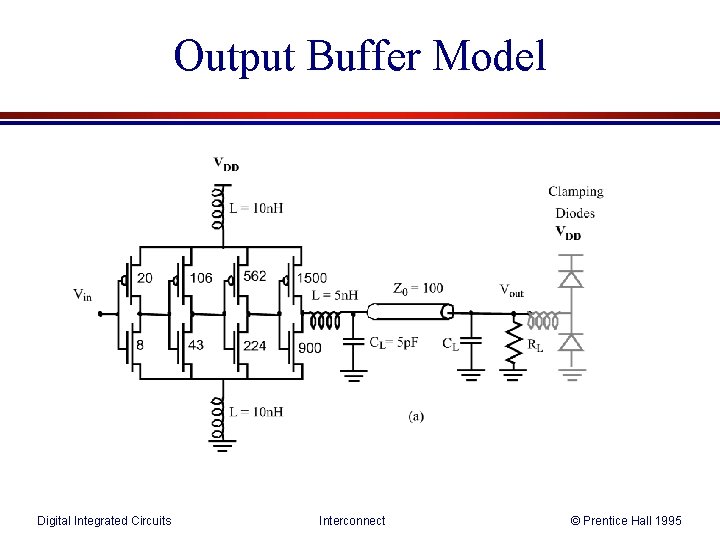

Output Buffer Model Digital Integrated Circuits Interconnect © Prentice Hall 1995

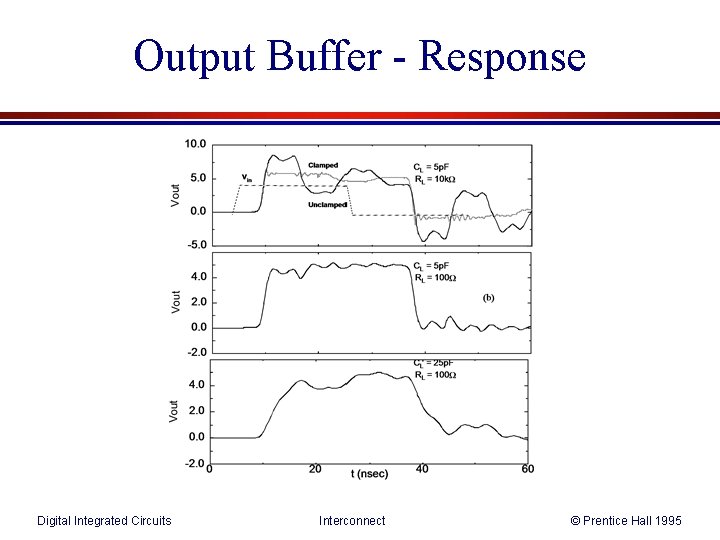

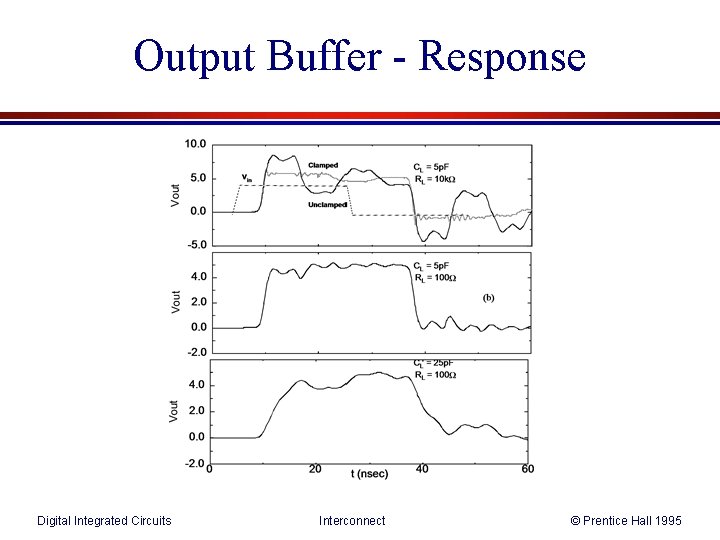

Output Buffer - Response Digital Integrated Circuits Interconnect © Prentice Hall 1995

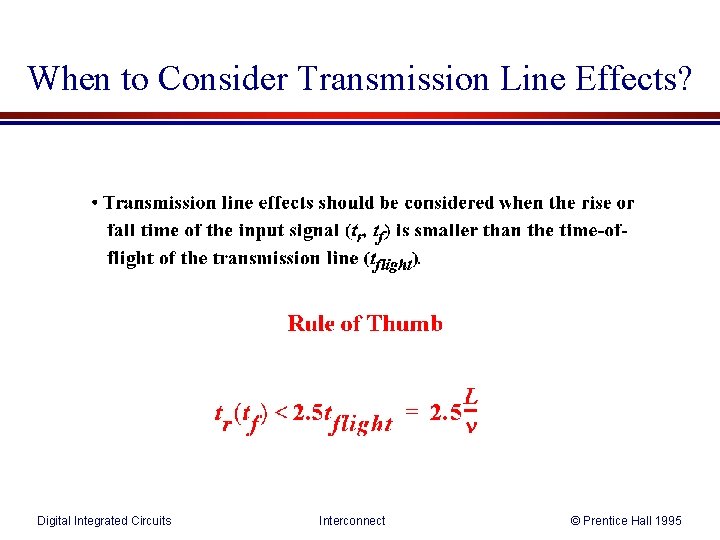

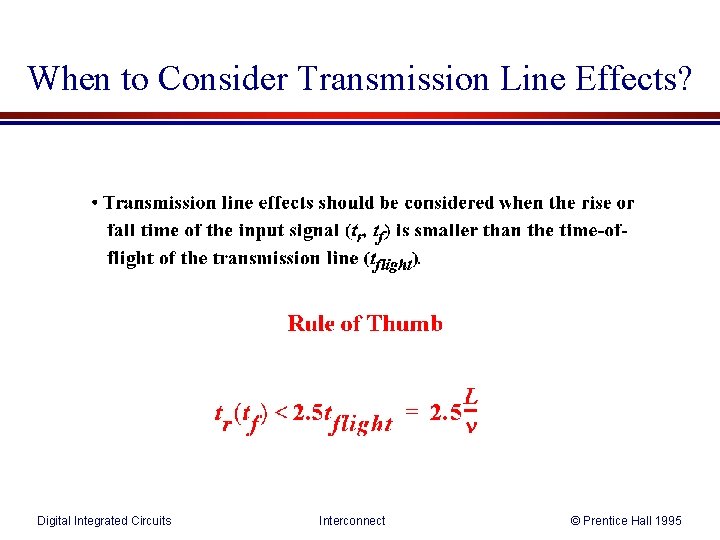

When to Consider Transmission Line Effects? Digital Integrated Circuits Interconnect © Prentice Hall 1995

Packaging Digital Integrated Circuits Interconnect © Prentice Hall 1995

Bonding Techniques Digital Integrated Circuits Interconnect © Prentice Hall 1995

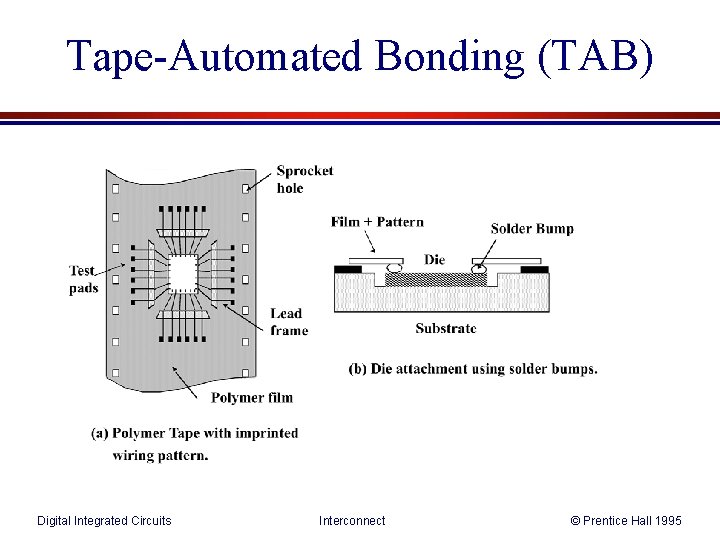

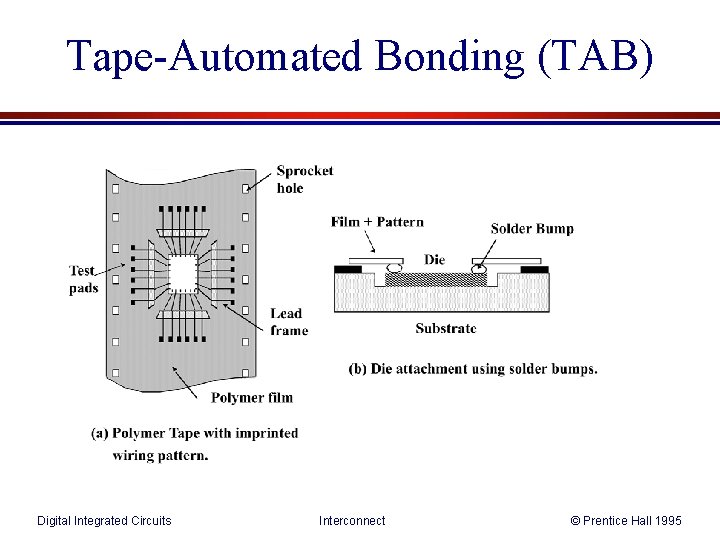

Tape-Automated Bonding (TAB) Digital Integrated Circuits Interconnect © Prentice Hall 1995

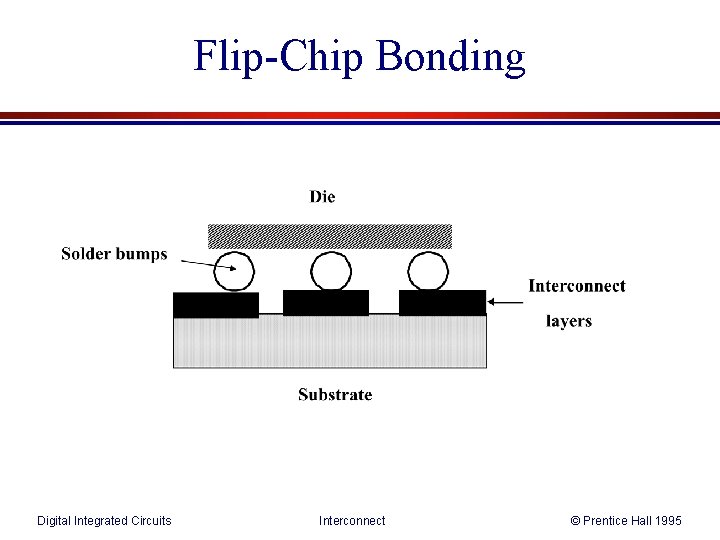

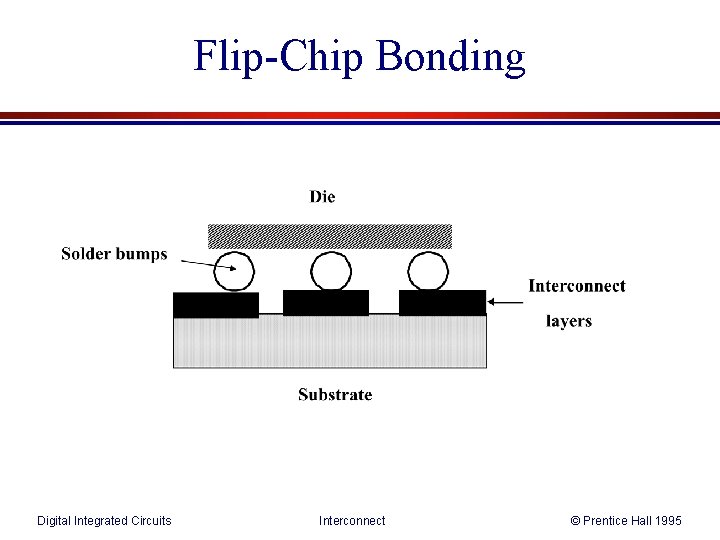

Flip-Chip Bonding Digital Integrated Circuits Interconnect © Prentice Hall 1995

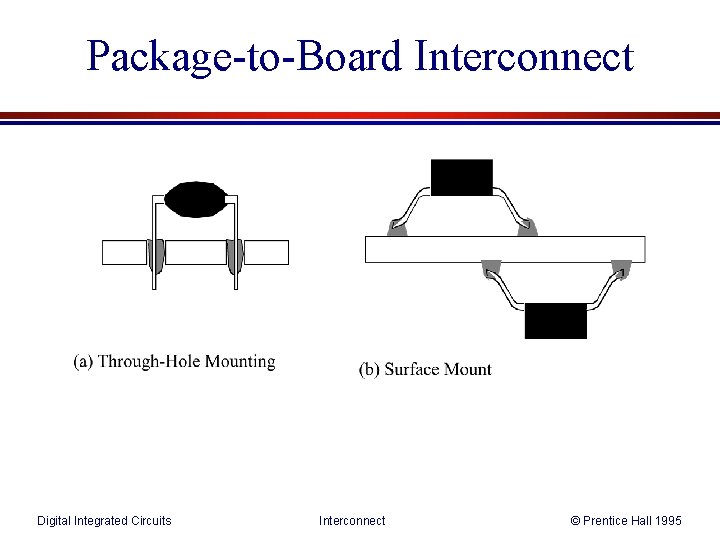

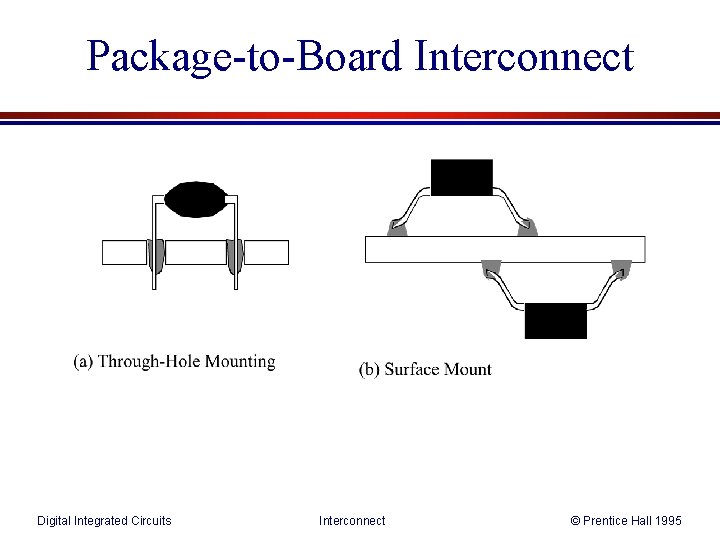

Package-to-Board Interconnect Digital Integrated Circuits Interconnect © Prentice Hall 1995

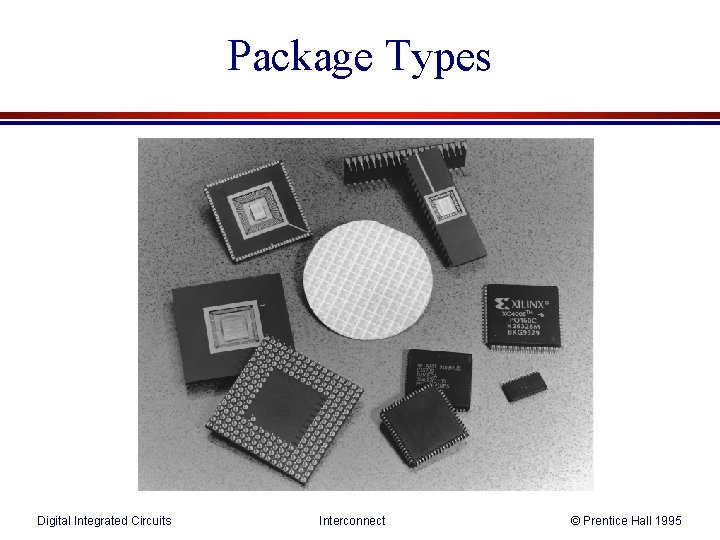

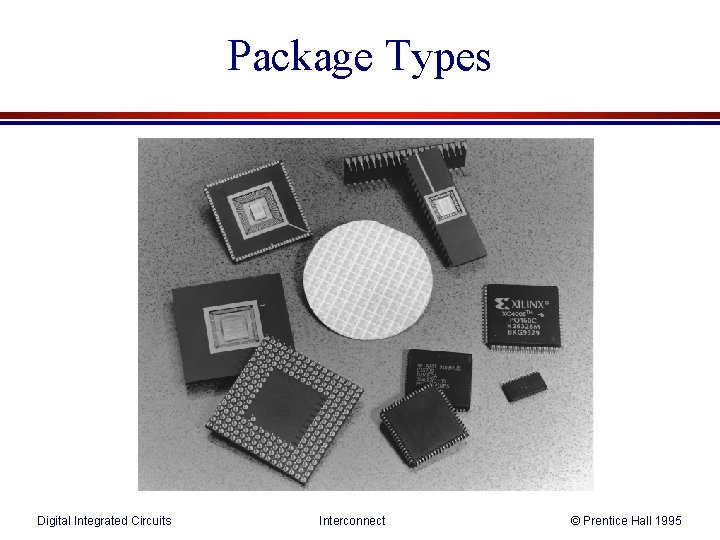

Package Types Digital Integrated Circuits Interconnect © Prentice Hall 1995

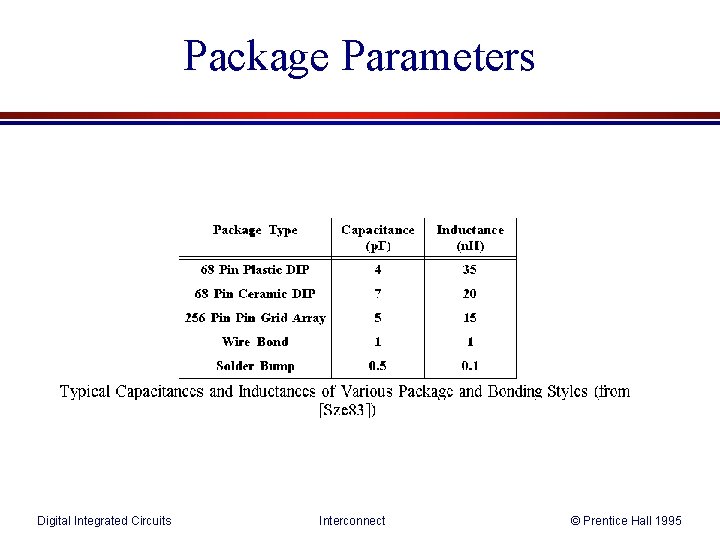

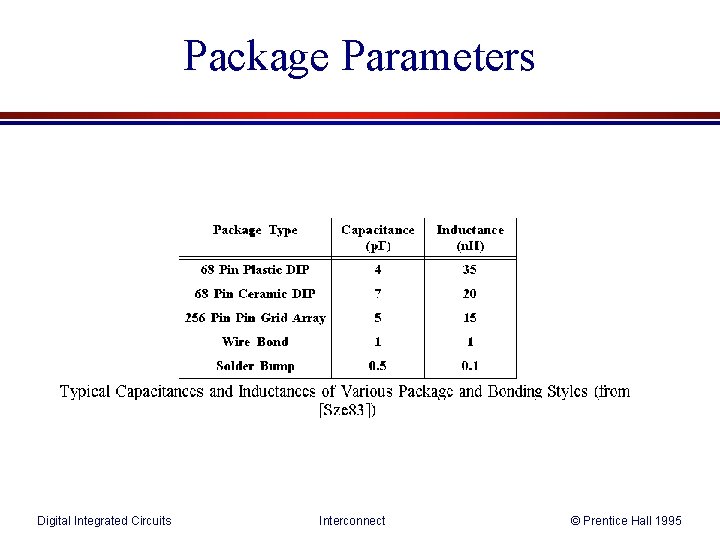

Package Parameters Digital Integrated Circuits Interconnect © Prentice Hall 1995

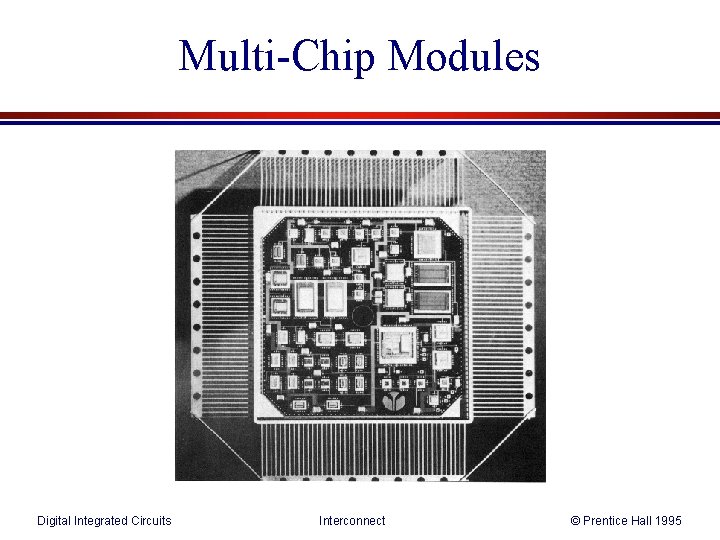

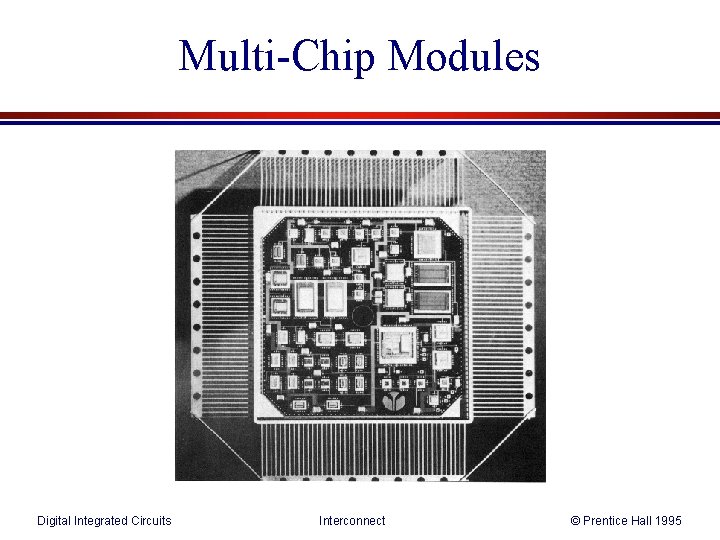

Multi-Chip Modules Digital Integrated Circuits Interconnect © Prentice Hall 1995