Controller Synthesis for Pipelined Circuits Using Uninterpreted Functions

- Slides: 26

Controller Synthesis for Pipelined Circuits Using Uninterpreted Functions Georg Hofferek and Roderick Bloem. MEMOCODE 2011

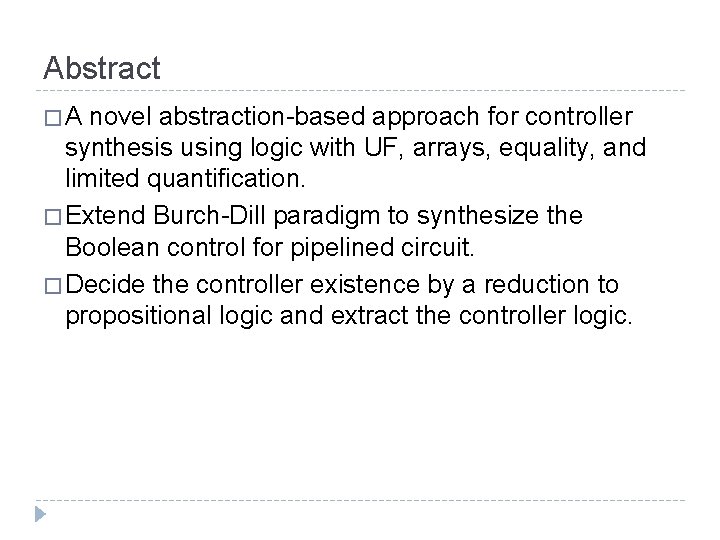

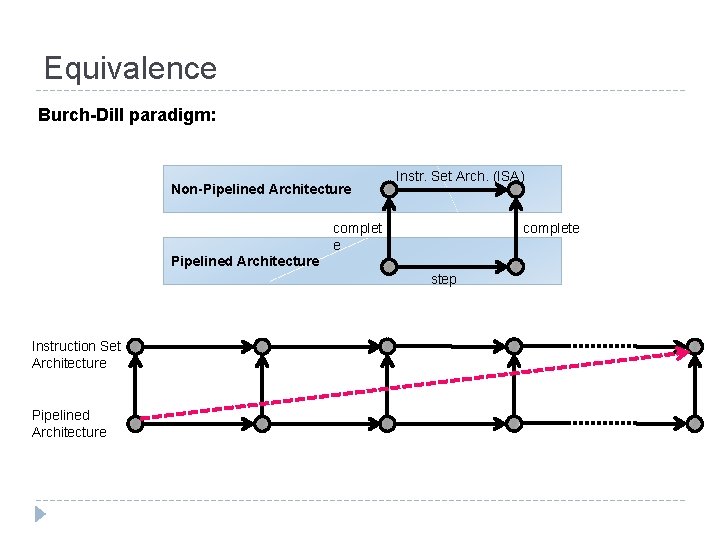

Abstract �A novel abstraction-based approach for controller synthesis using logic with UF, arrays, equality, and limited quantification. � Extend Burch-Dill paradigm to synthesize the Boolean control for pipelined circuit. � Decide the controller existence by a reduction to propositional logic and extract the controller logic.

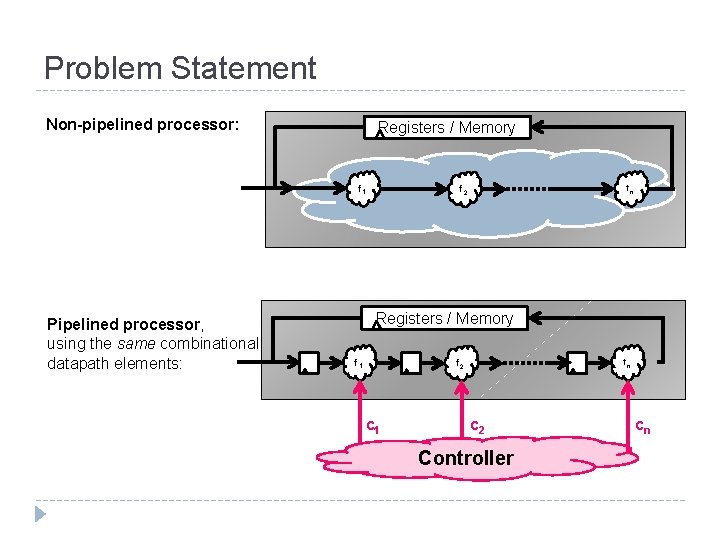

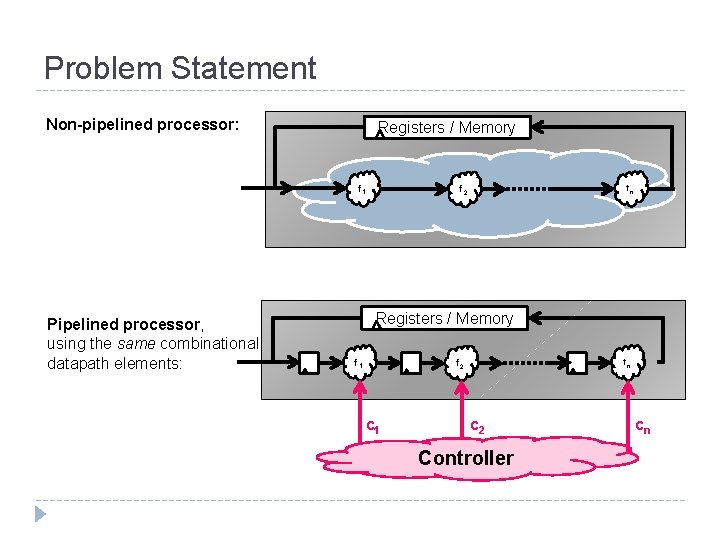

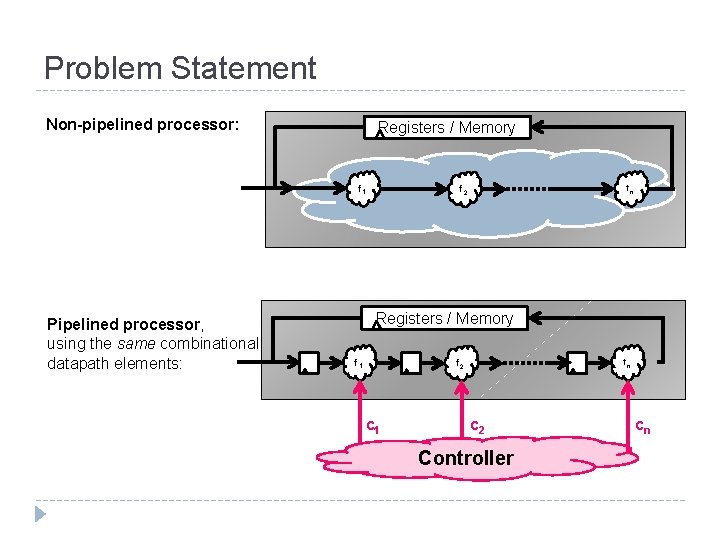

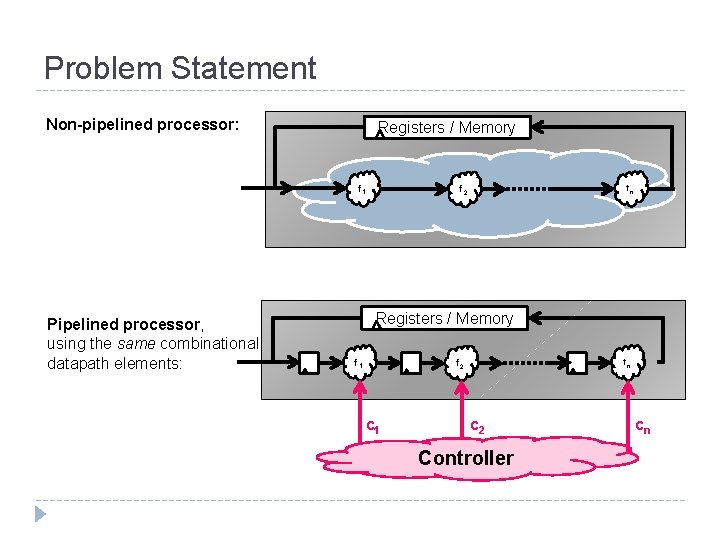

Problem Statement Non-pipelined processor: Registers / Memory f 1 Pipelined processor, using the same combinational datapath elements: f 2 fn Registers / Memory f 1 f 2 c 1 fn c 2 Controller cn

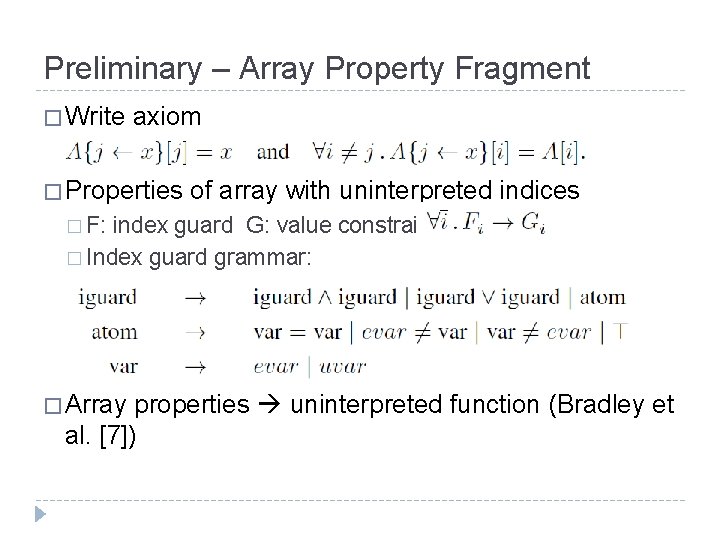

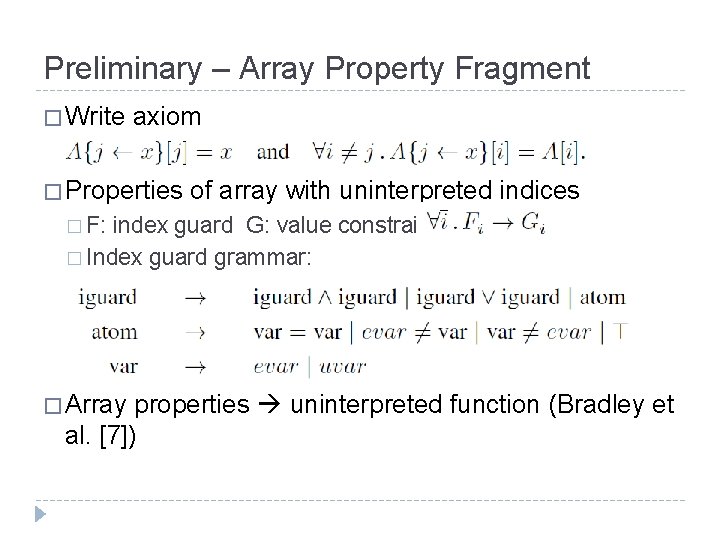

Preliminary – Array Property Fragment � Write axiom � Properties of array with uninterpreted indices � F: index guard G: value constraint � Index guard grammar: � Array properties uninterpreted function (Bradley et al. [7])

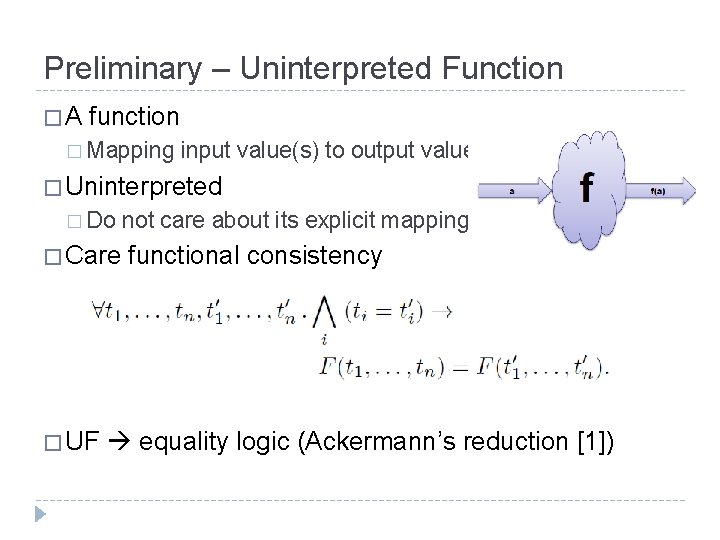

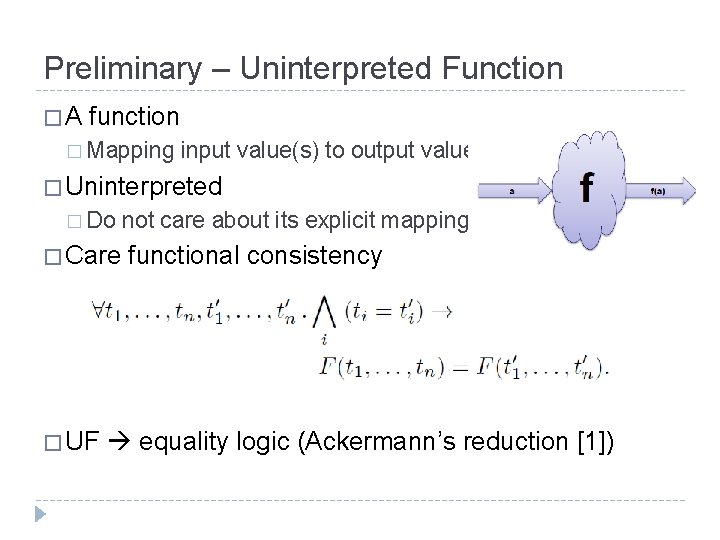

Preliminary – Uninterpreted Function �A function � Mapping input value(s) to output value � Uninterpreted � Do � Care � UF not care about its explicit mapping functional consistency equality logic (Ackermann’s reduction [1])

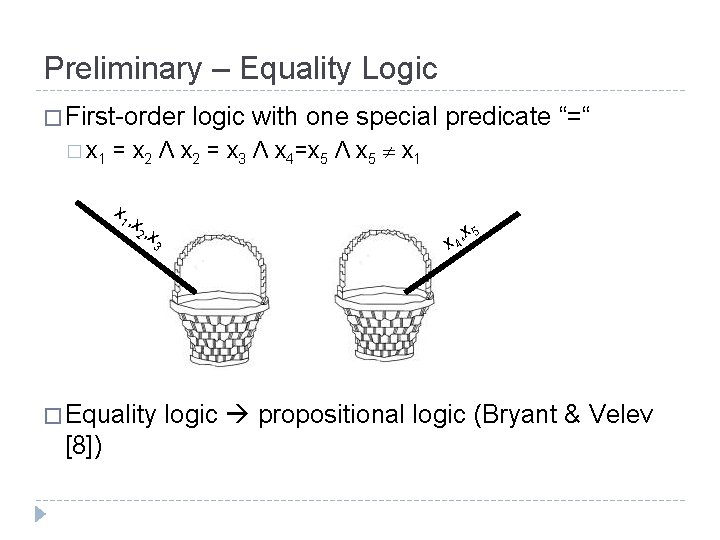

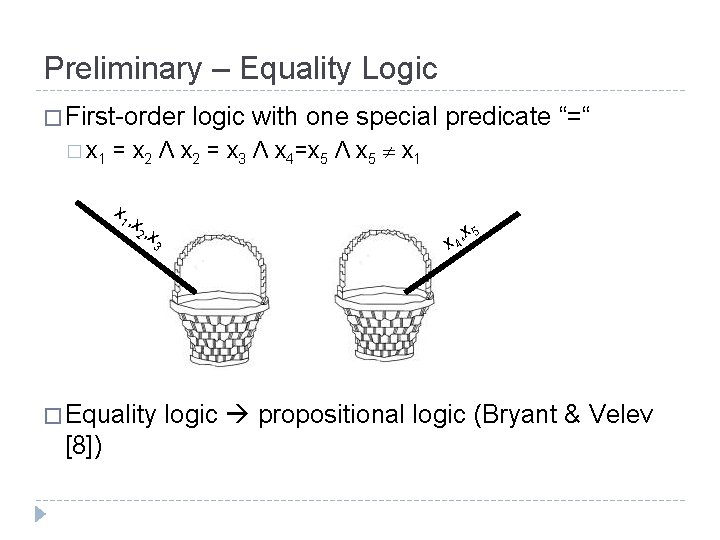

Preliminary – Equality Logic � First-order � x 1 = x 2 Λ x 2 = x 3 Λ x 4=x 5 Λ x 5 x 1 , x 2 , x 3 � Equality [8]) logic with one special predicate “=“ , x 5 x 4 logic propositional logic (Bryant & Velev

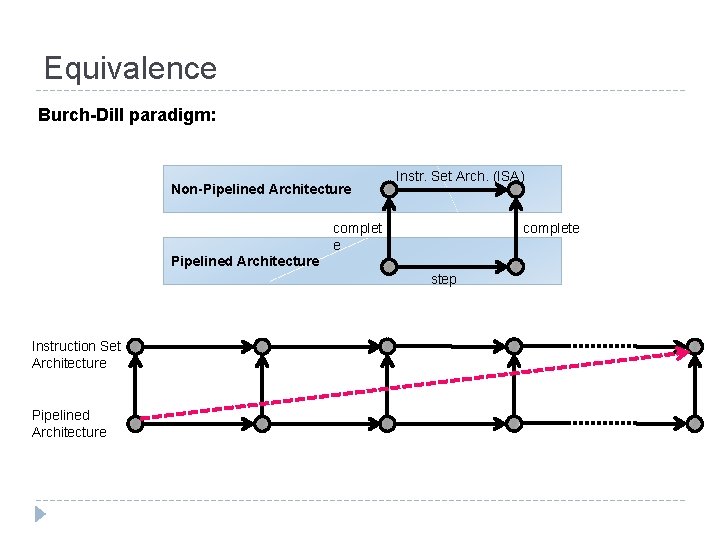

Equivalence Burch-Dill paradigm: Non-Pipelined Architecture Instr. Set Arch. (ISA) complet e complete Pipelined Architecture step Instruction Set Architecture Pipelined Architecture

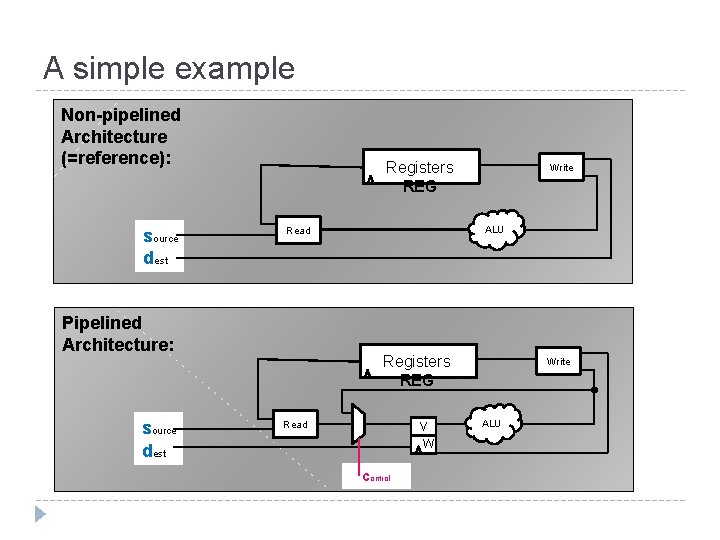

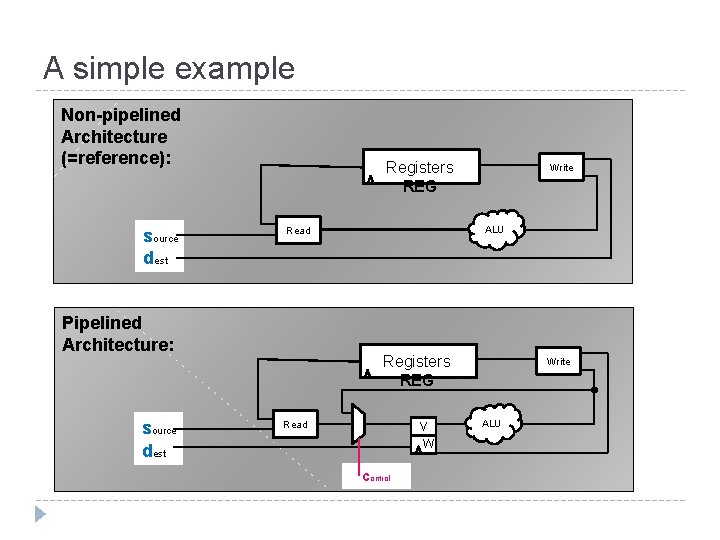

A simple example Non-pipelined Architecture (=reference): source dest Registers REG source dest ALU Read Pipelined Architecture: Write Registers REG v w Read control Write ALU

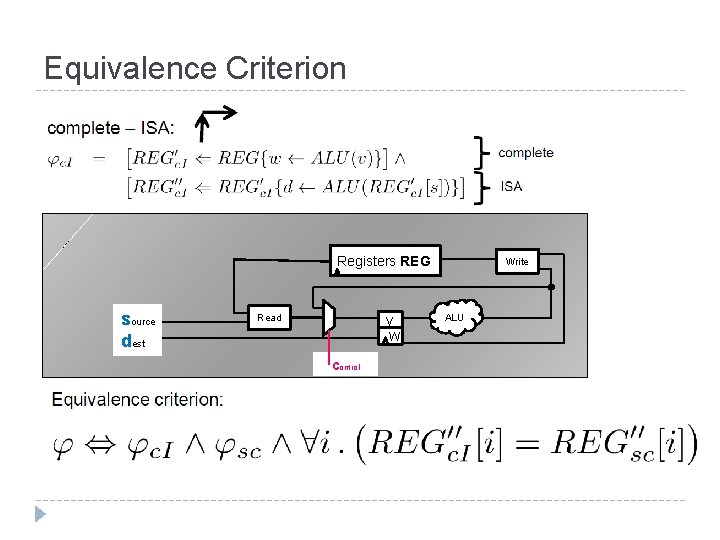

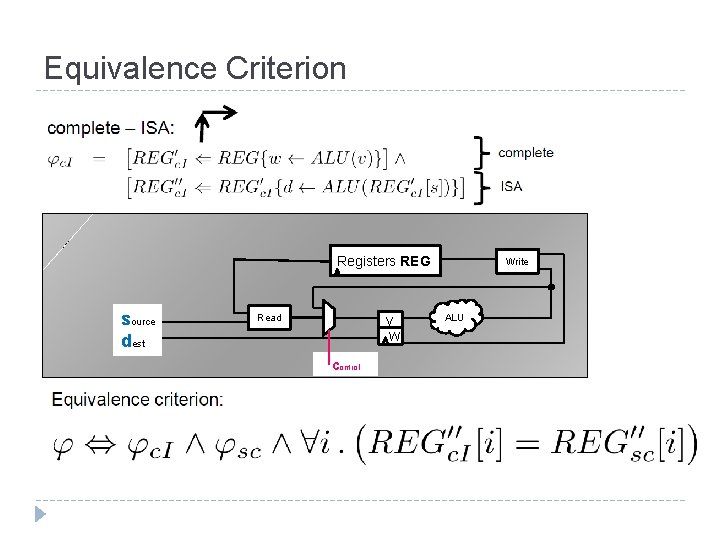

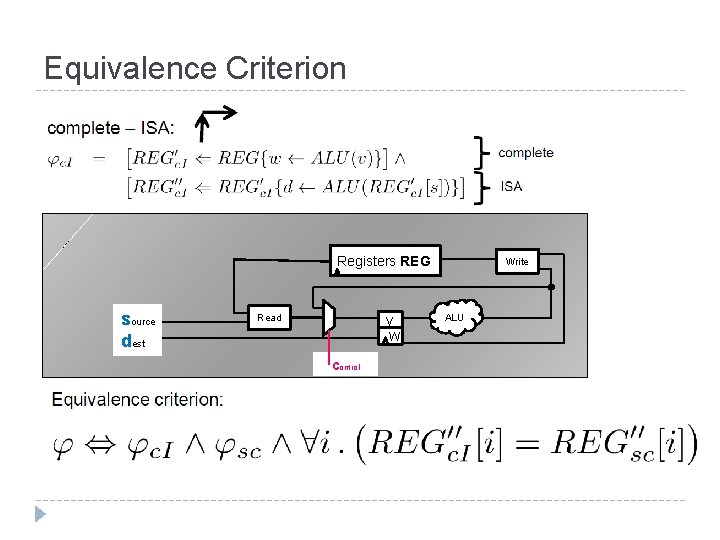

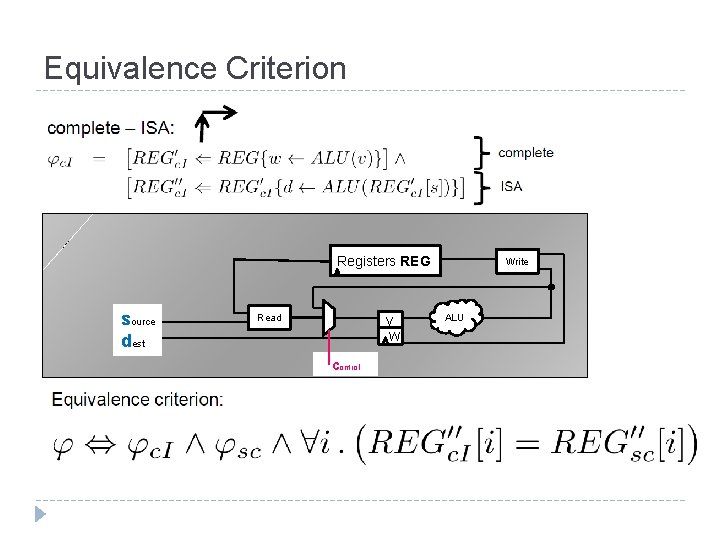

Equivalence Criterion Registers REG source dest v w Read control Write ALU

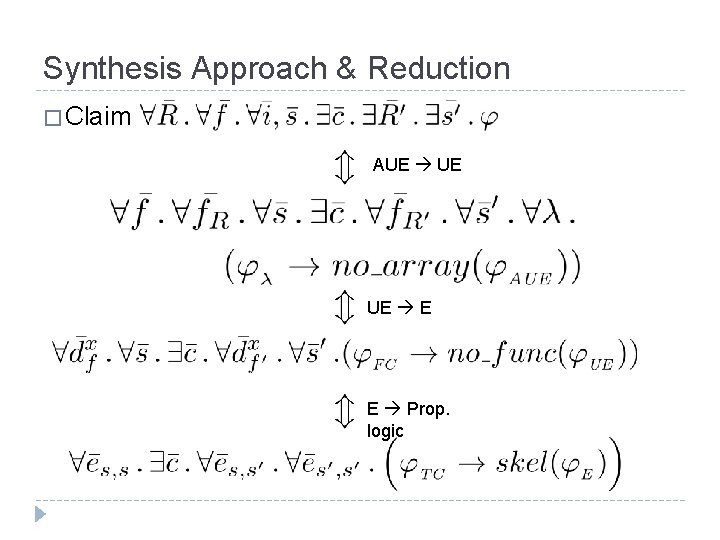

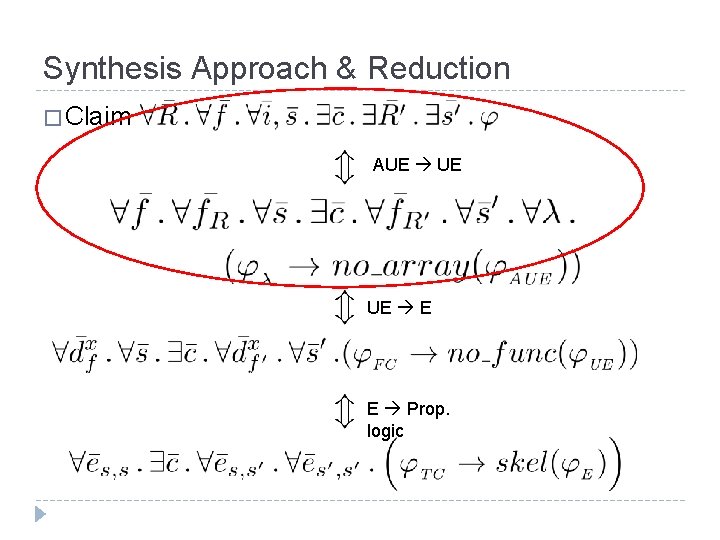

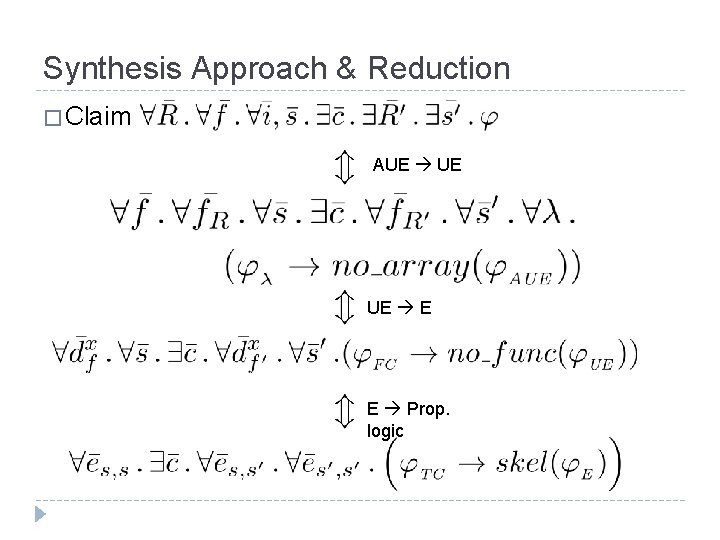

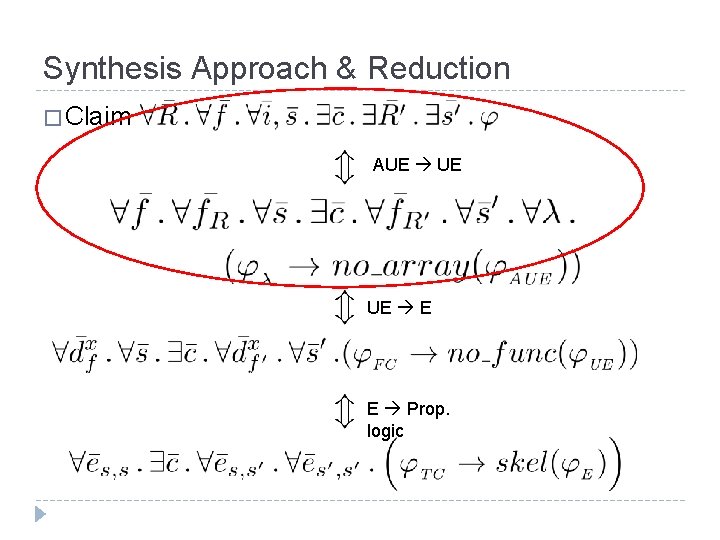

Synthesis Approach & Reduction � Claim: AUE UE UE E E Prop. logic

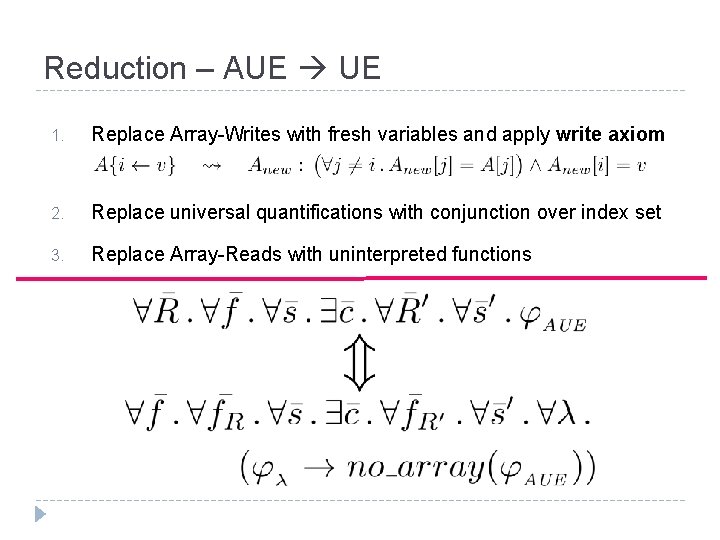

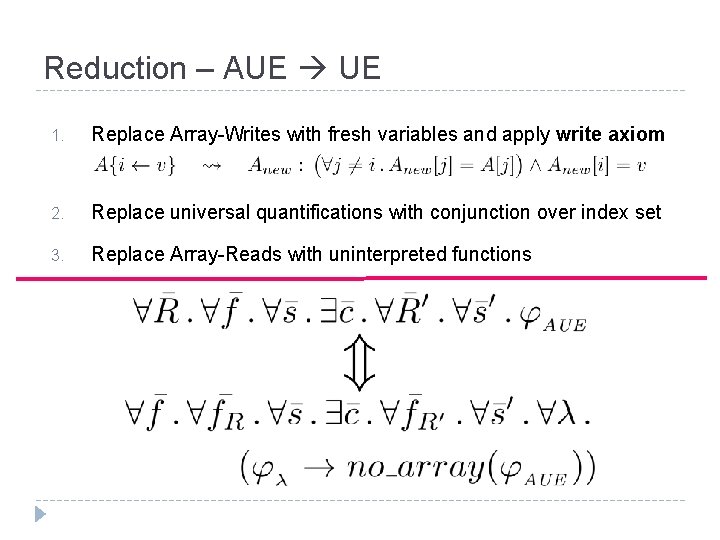

Reduction – AUE UE 1. Replace Array-Writes with fresh variables and apply write axiom 2. Replace universal quantifications with conjunction over index set 3. Replace Array-Reads with uninterpreted functions

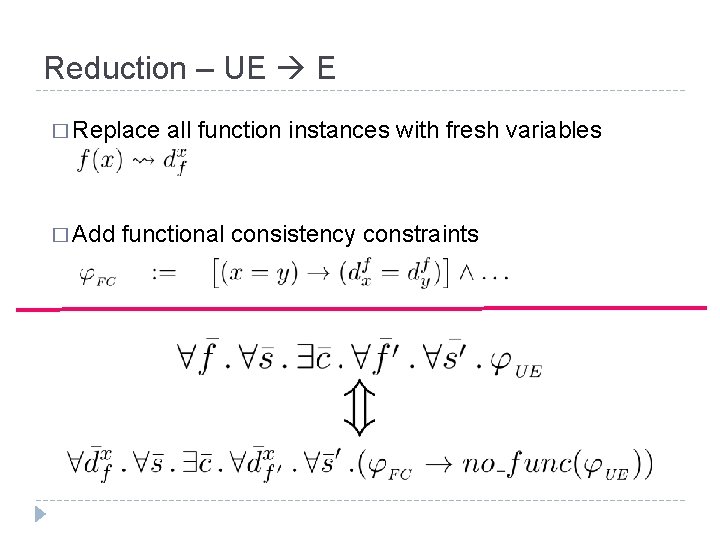

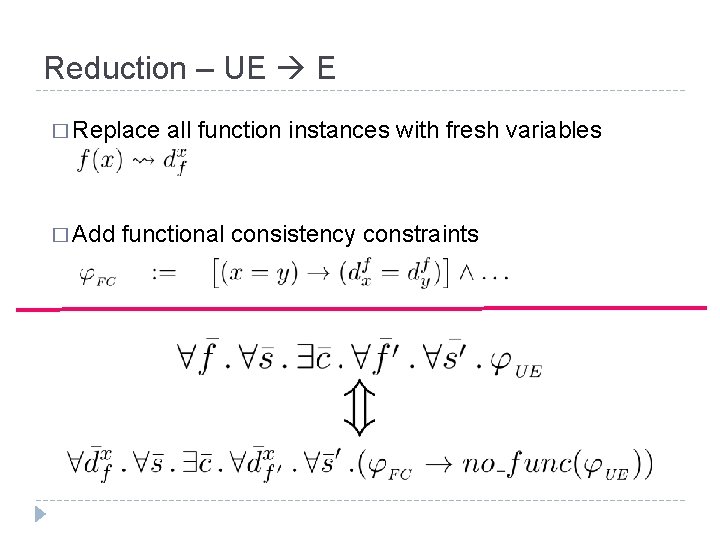

Reduction – UE E � Replace � Add all function instances with fresh variables functional consistency constraints

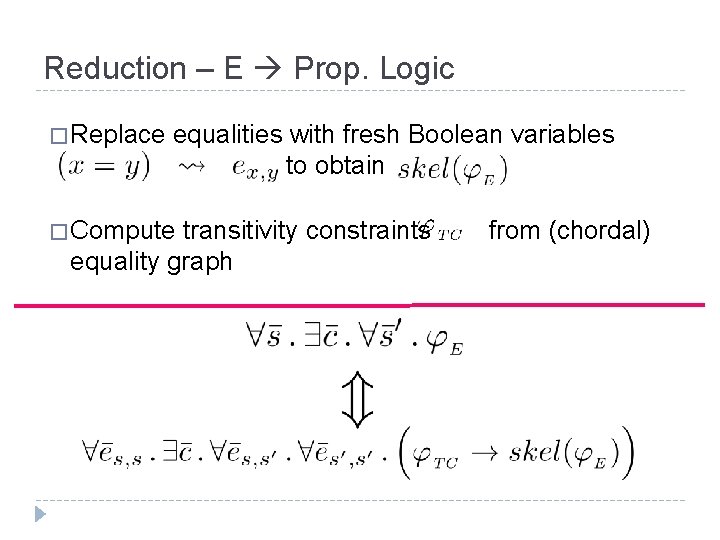

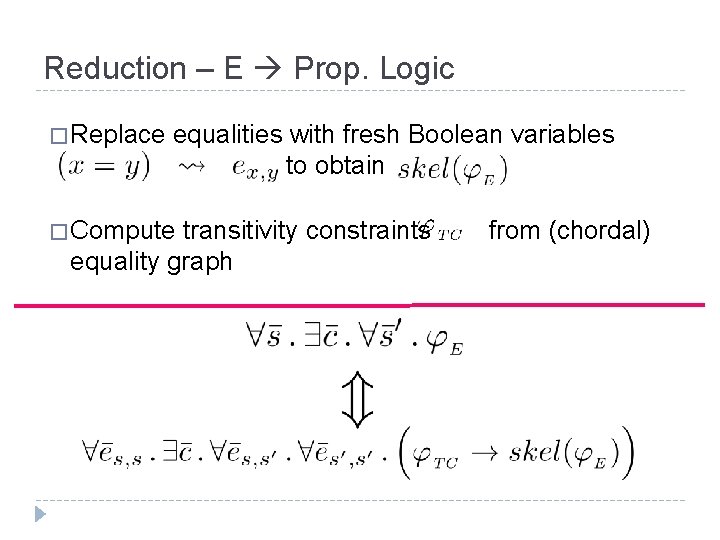

Reduction – E Prop. Logic � Replace equalities with fresh Boolean variables to obtain � Compute transitivity constraints equality graph from (chordal)

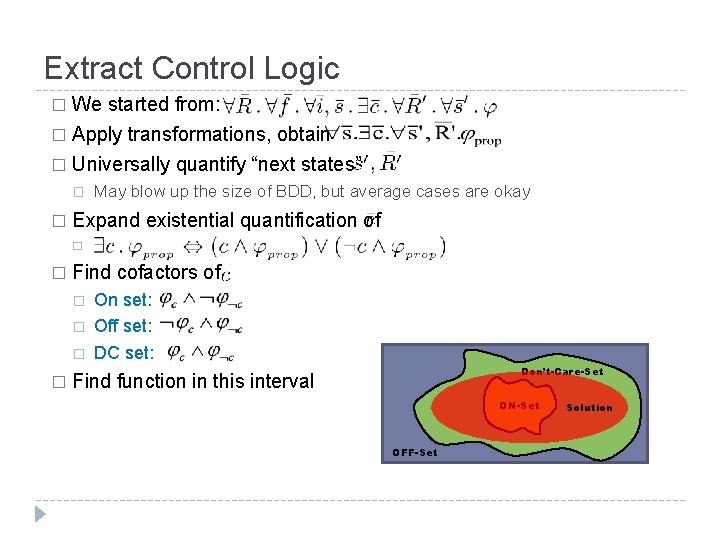

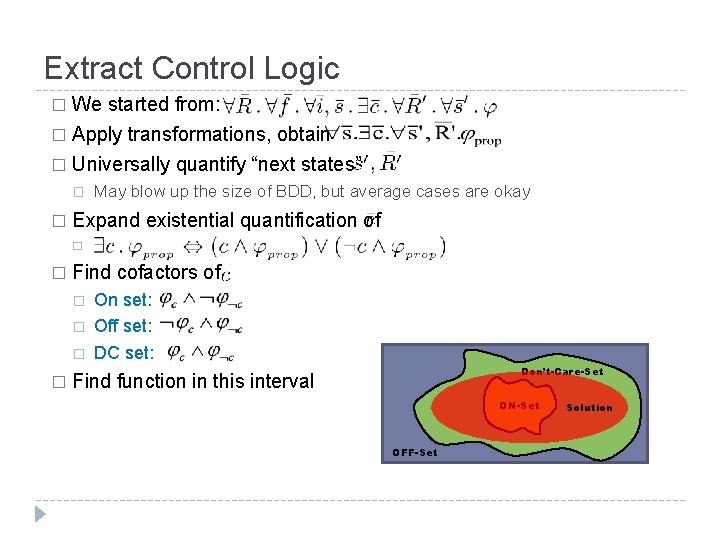

Extract Control Logic We started from: � Apply transformations, obtain � � Universally quantify “next states” � � May blow up the size of BDD, but average cases are okay Expand existential quantification of � � Find cofactors of � � On set: Off set: DC set: Don’t-Care-Set Find function in this interval ON-Set OFF-Set Solution

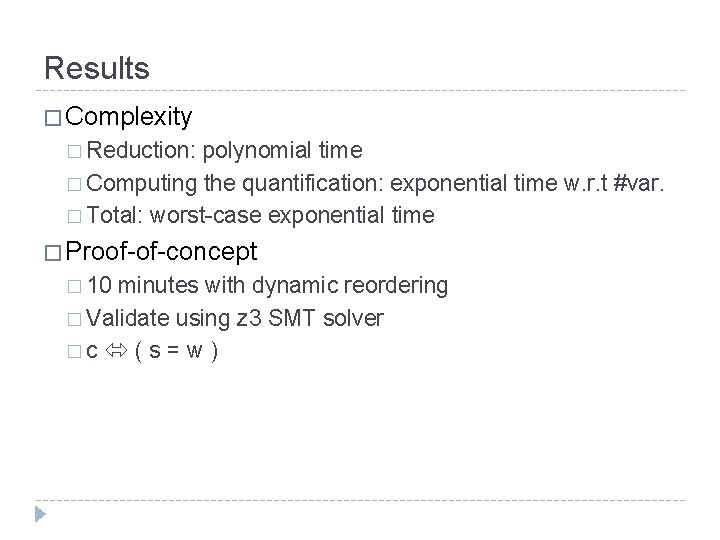

Results � Complexity � Reduction: polynomial time � Computing the quantification: exponential time w. r. t #var. � Total: worst-case exponential time � Proof-of-concept � 10 minutes with dynamic reordering � Validate using z 3 SMT solver �c ( s = w )

AUE UE 2012/9/13

Outline � Quick review � AUE UE reduction � Back to controller synthesis

Problem Statement Non-pipelined processor: Registers / Memory f 1 Pipelined processor, using the same combinational datapath elements: f 2 fn Registers / Memory f 1 f 2 c 1 fn c 2 Controller cn

Equivalence Criterion Registers REG source dest v w Read control Write ALU

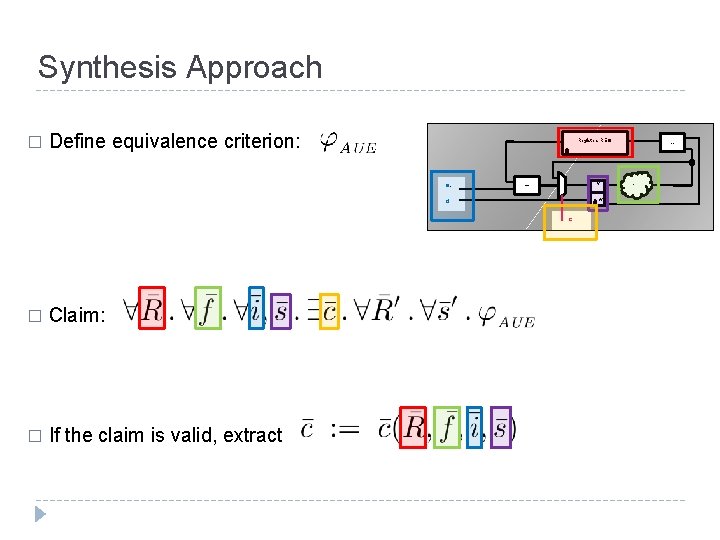

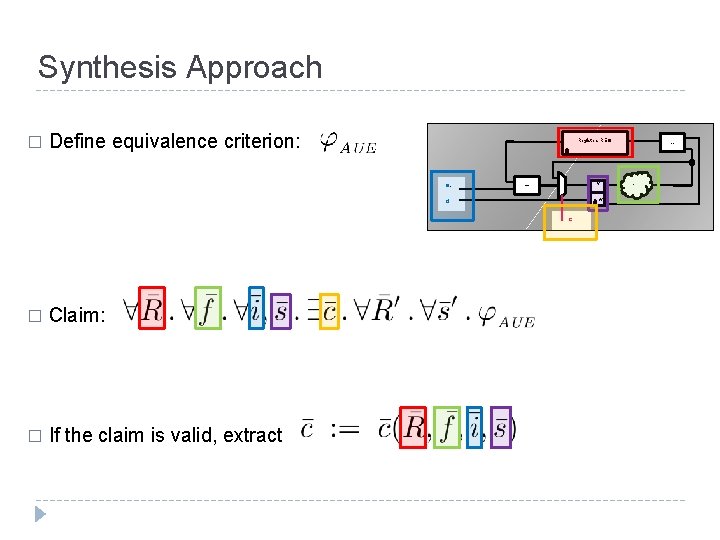

Synthesis Approach � Define equivalence criterion: Registers REG s ource v Read w d est c � Claim: � If the claim is valid, extract ontrol Write ALU

Synthesis Approach & Reduction � Claim: AUE UE UE E E Prop. logic

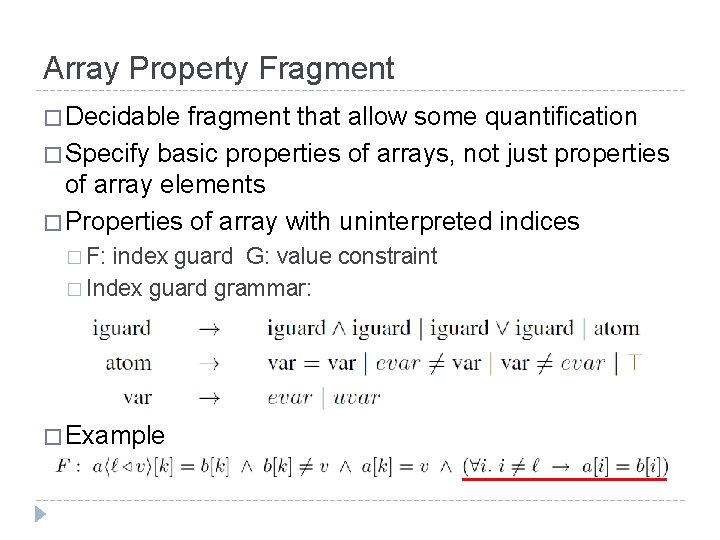

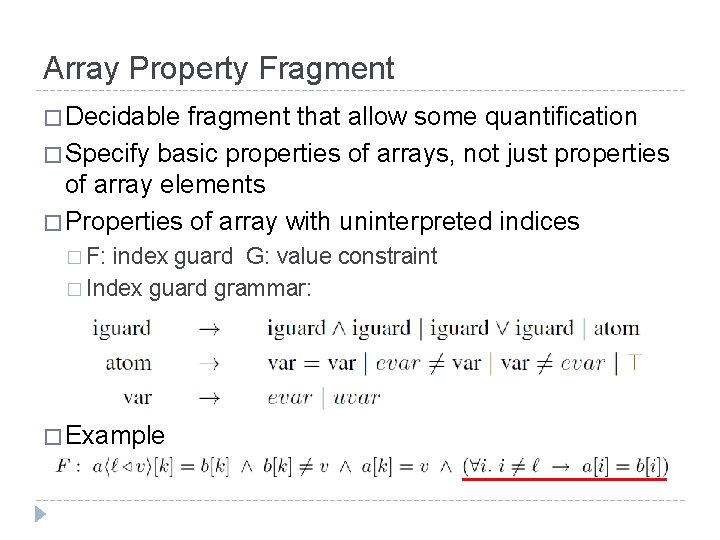

Array Property Fragment � Decidable fragment that allow some quantification � Specify basic properties of arrays, not just properties of array elements � Properties of array with uninterpreted indices � F: index guard G: value constraint � Index guard grammar: � Example

Reduction Example � Apply write axiom � Index set � Replace universal quantification by conjunction

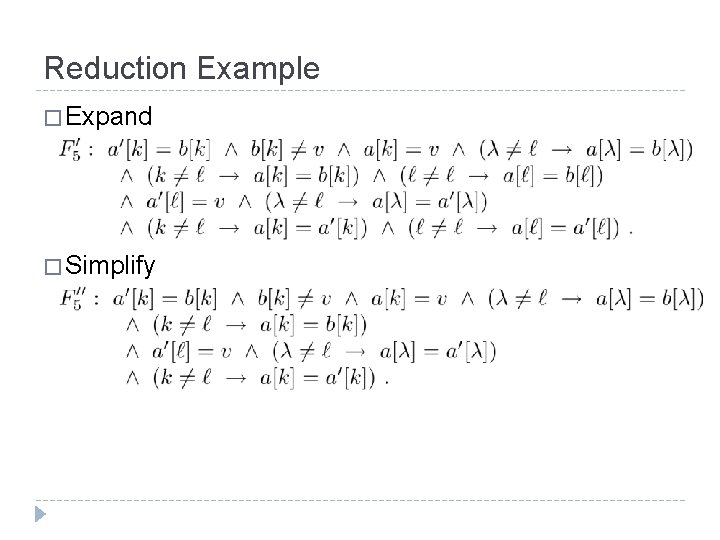

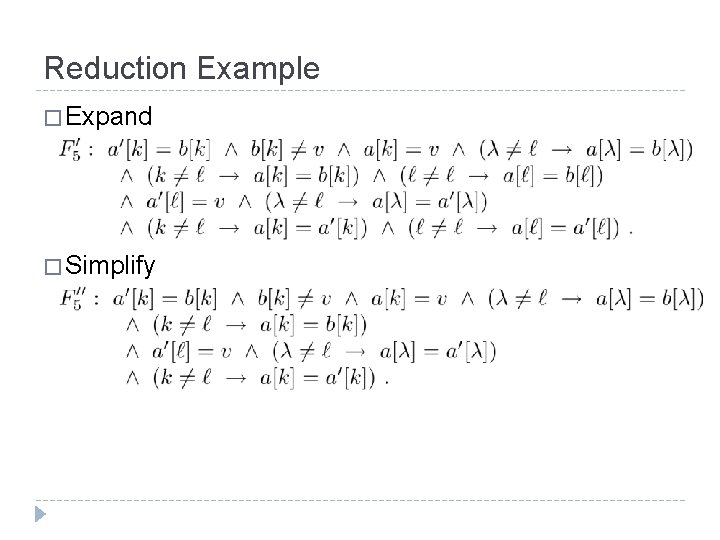

Reduction Example � Expand � Simplify

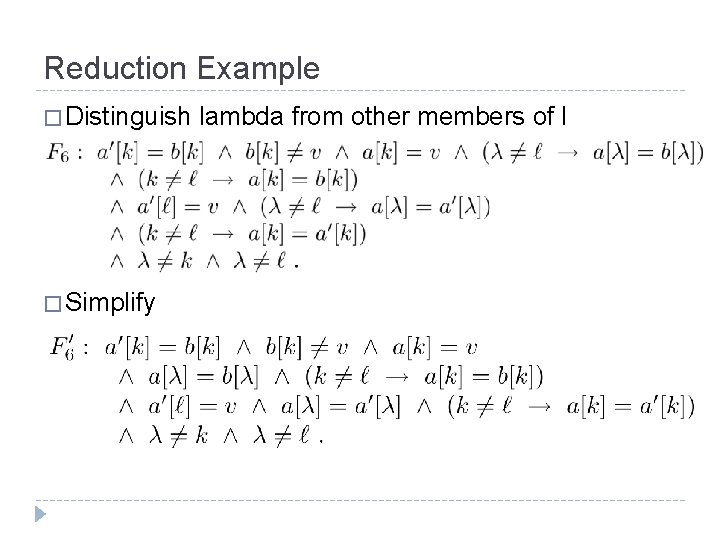

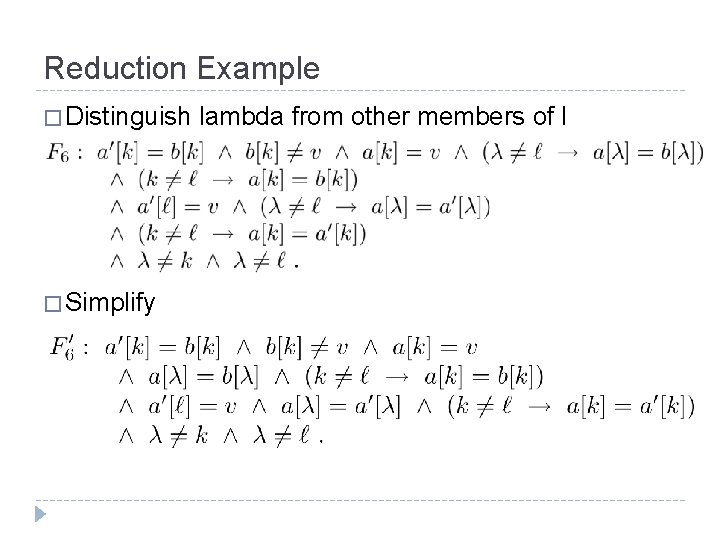

Reduction Example � Distinguish � Simplify lambda from other members of I

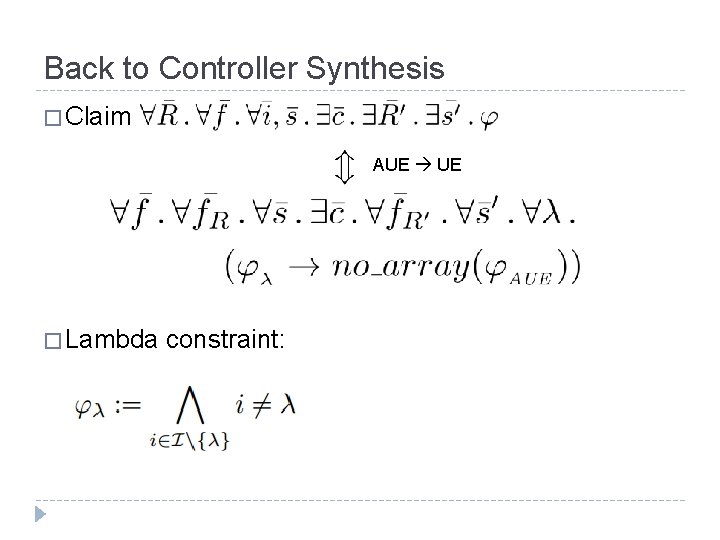

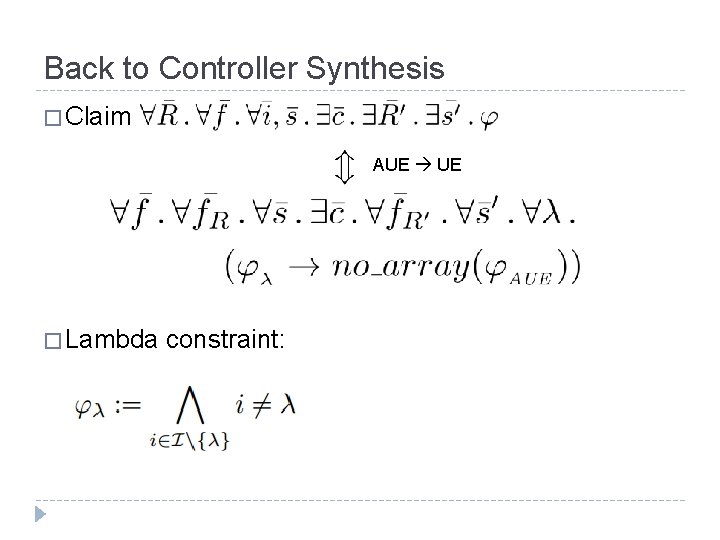

Back to Controller Synthesis � Claim: AUE UE � Lambda constraint: