Controller Area Network CAN Lecture 5 1 Reference

- Slides: 74

Controller Area Network (CAN) Lecture 5. 1

Reference MSCAN Block Guide V 02. 14 S 12 MSCANV 2. pdf

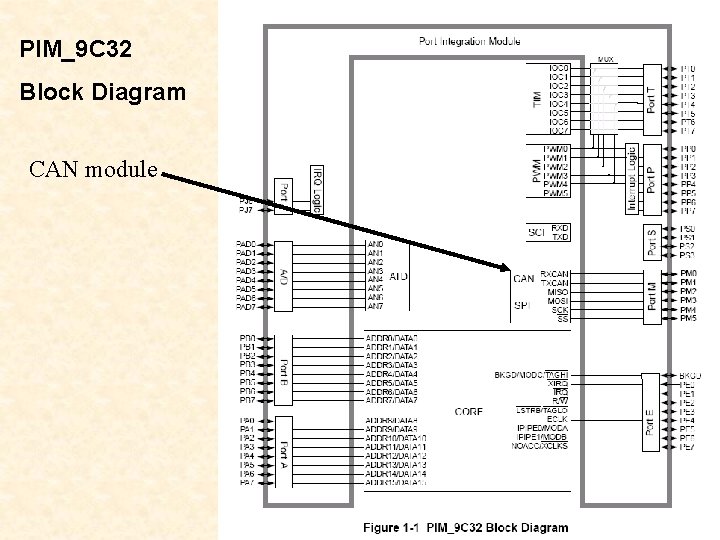

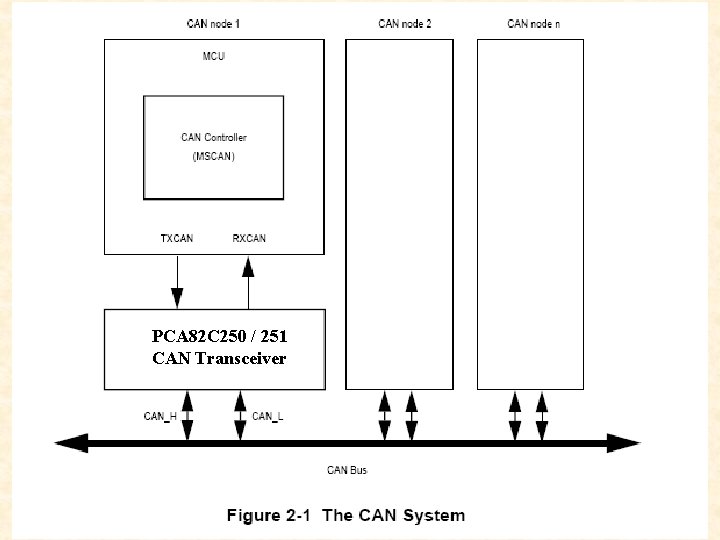

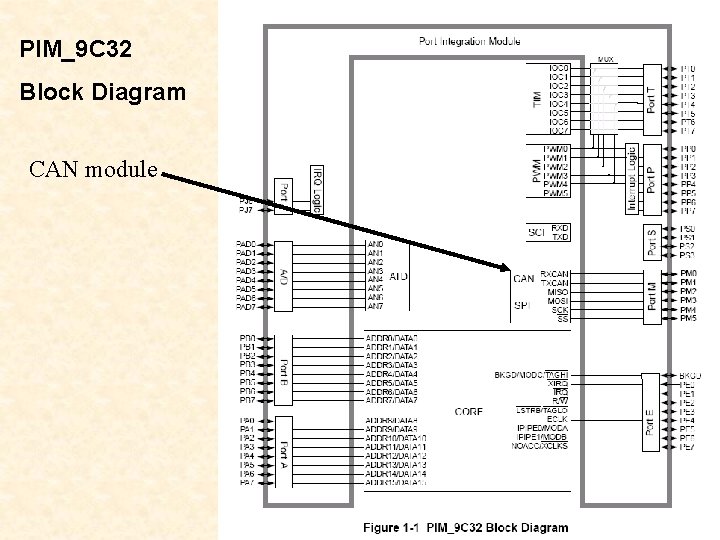

PIM_9 C 32 Block Diagram CAN module

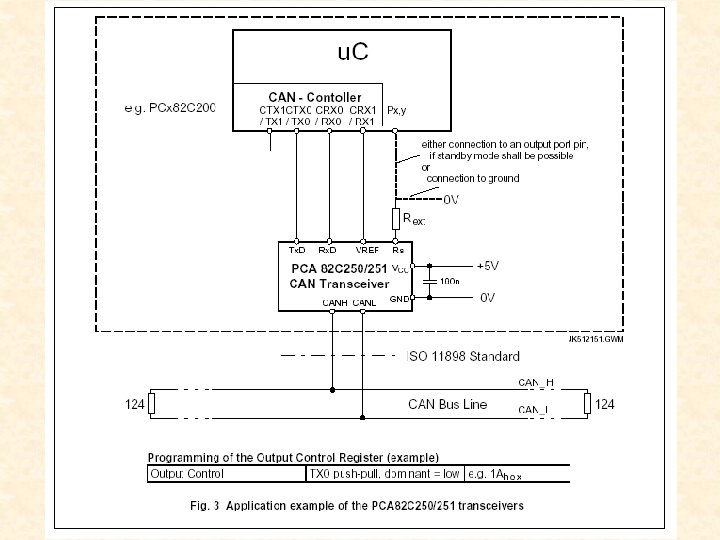

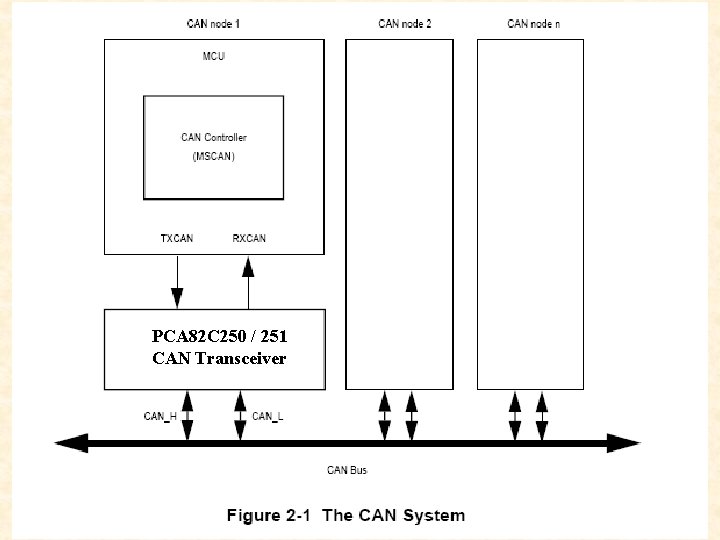

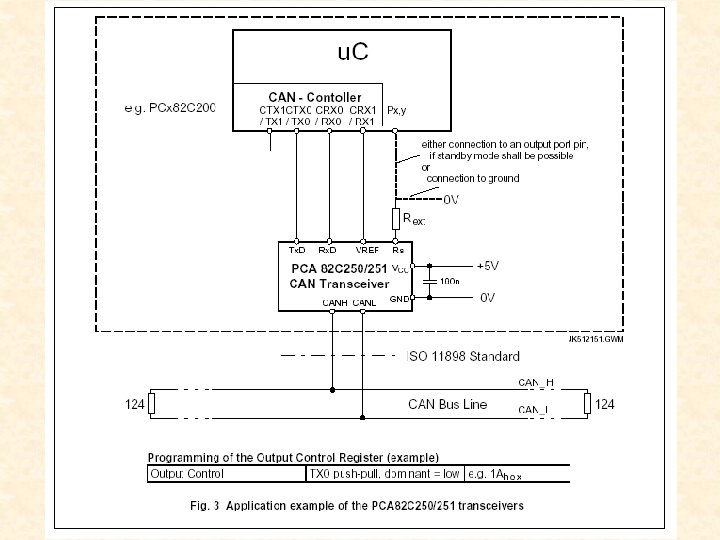

PCA 82 C 250 / 251 CAN Transceiver

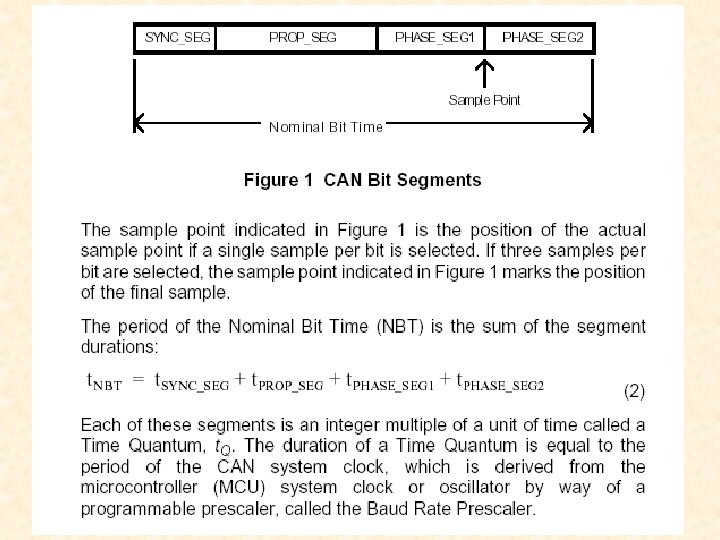

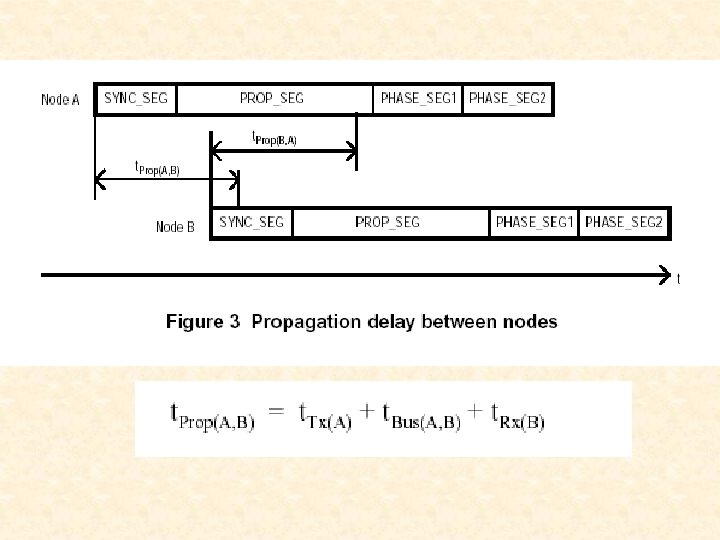

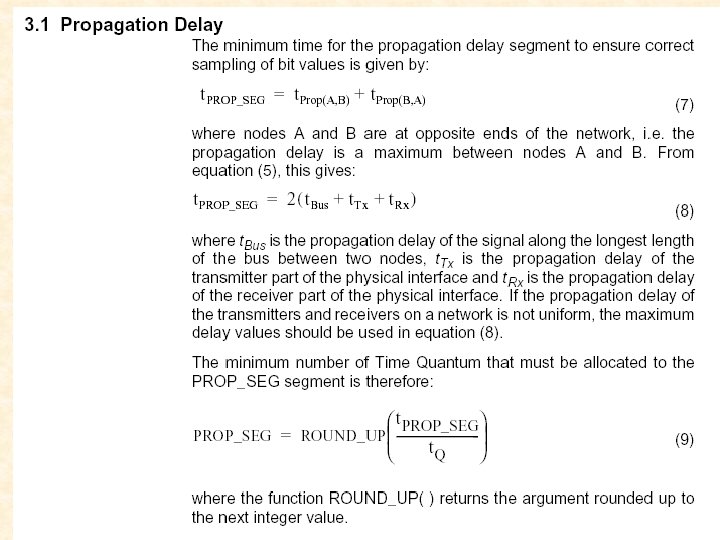

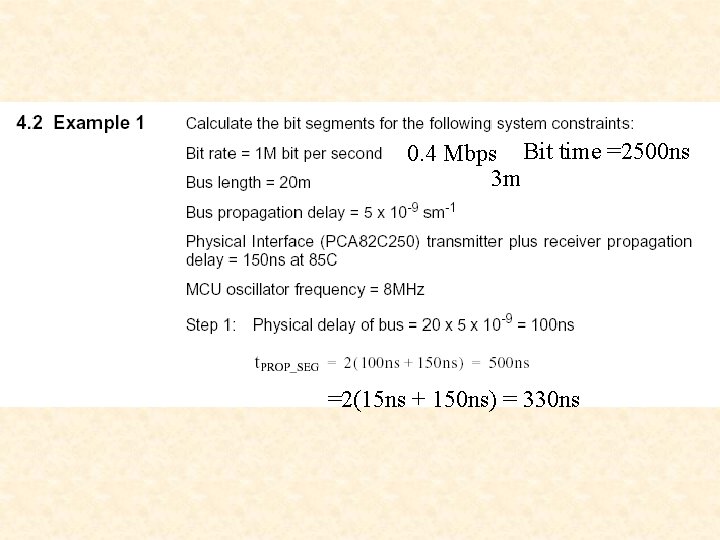

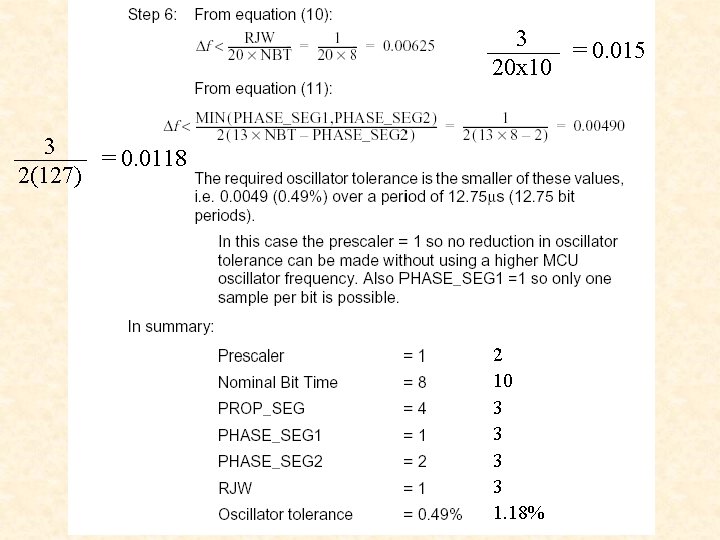

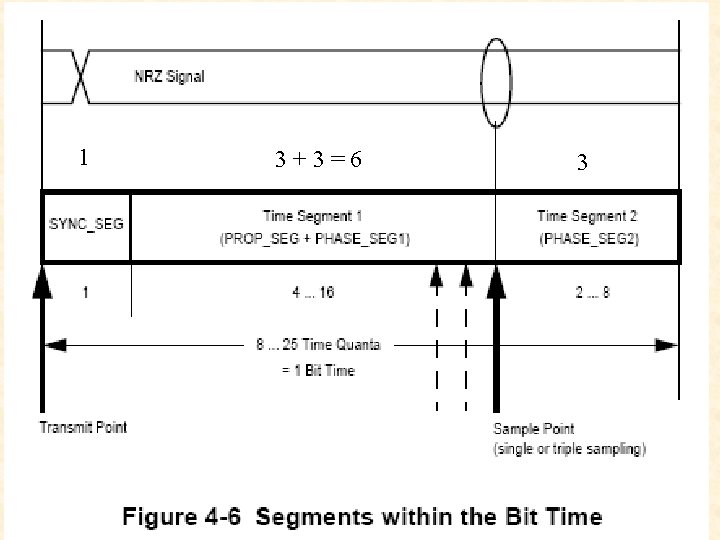

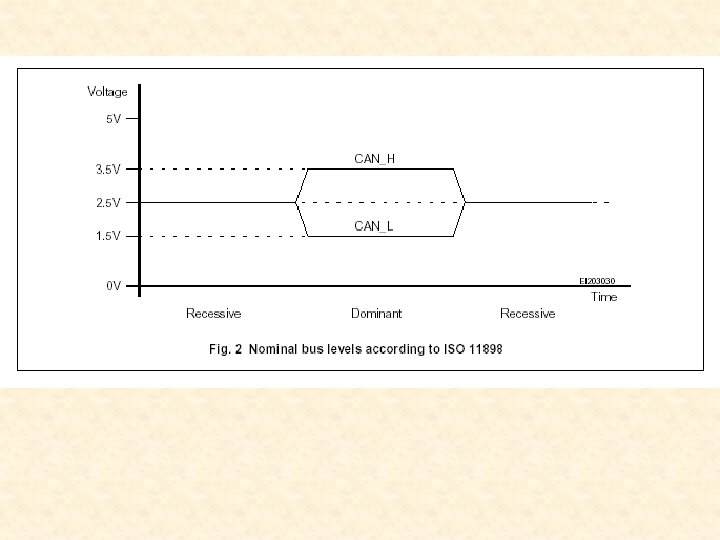

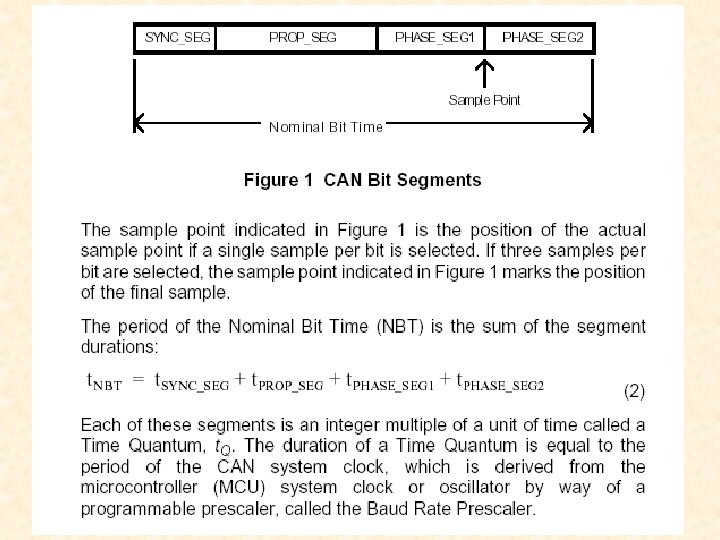

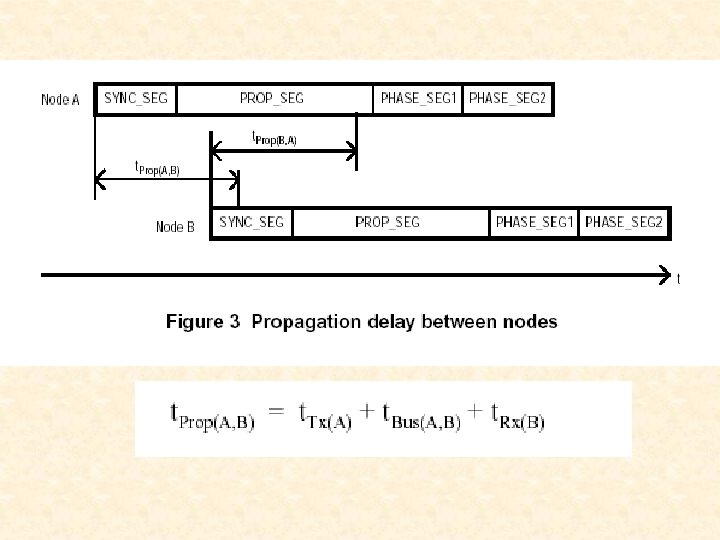

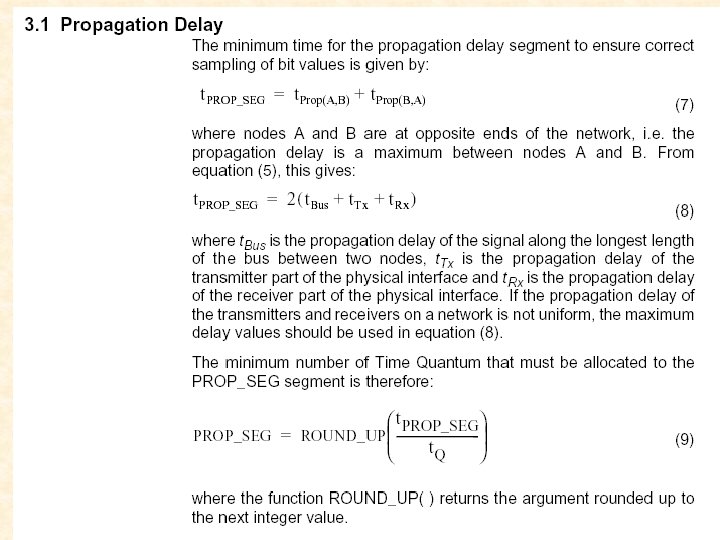

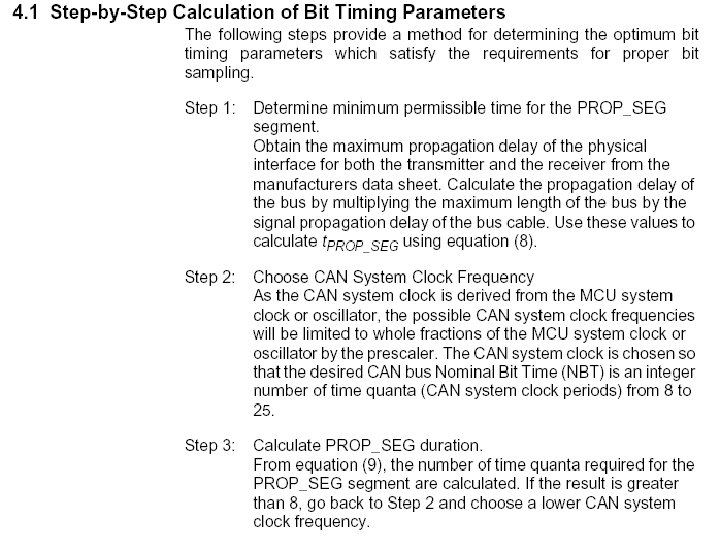

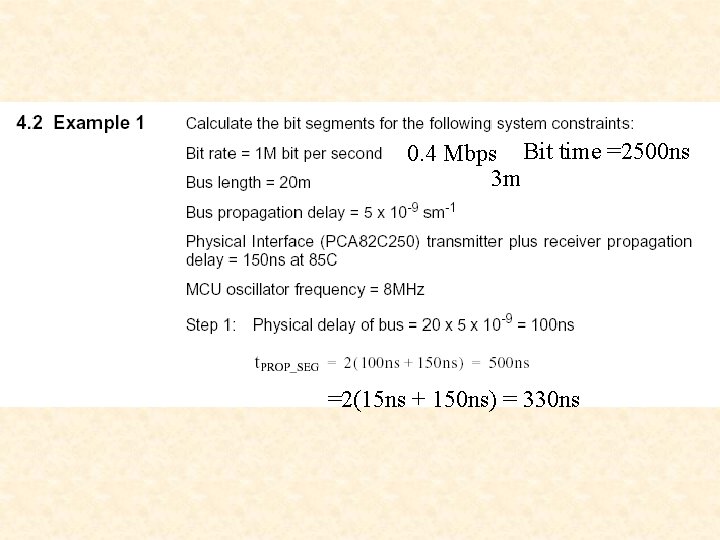

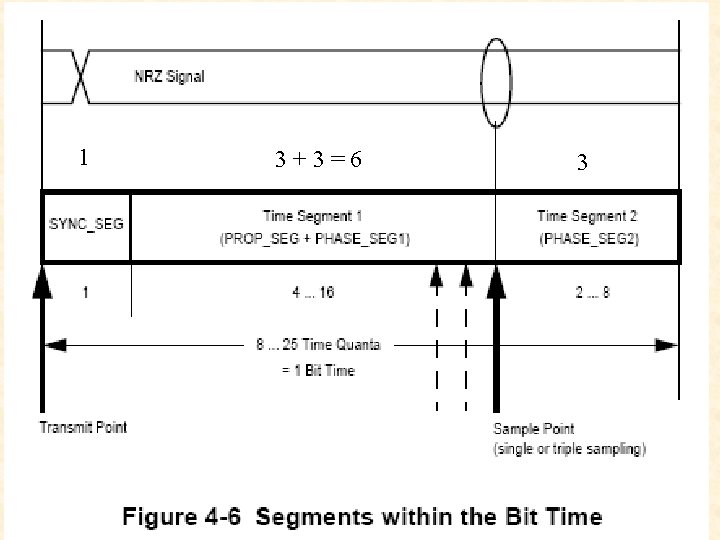

0. 4 Mbps Bit time =2500 ns 3 m =2(15 ns + 150 ns) = 330 ns

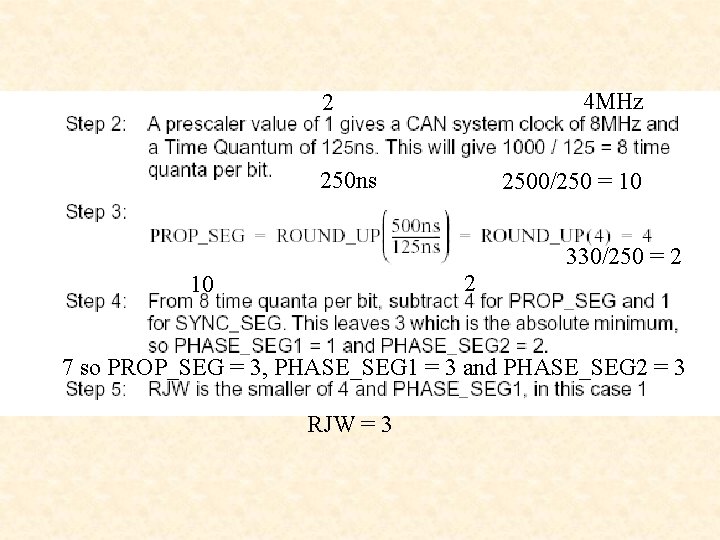

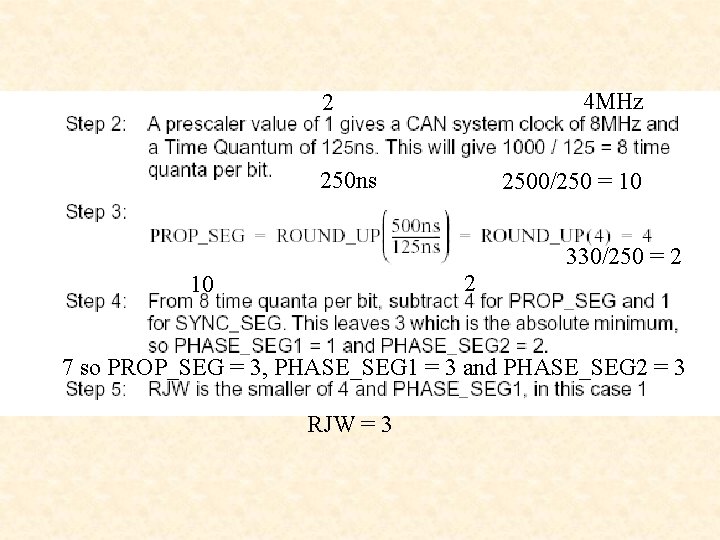

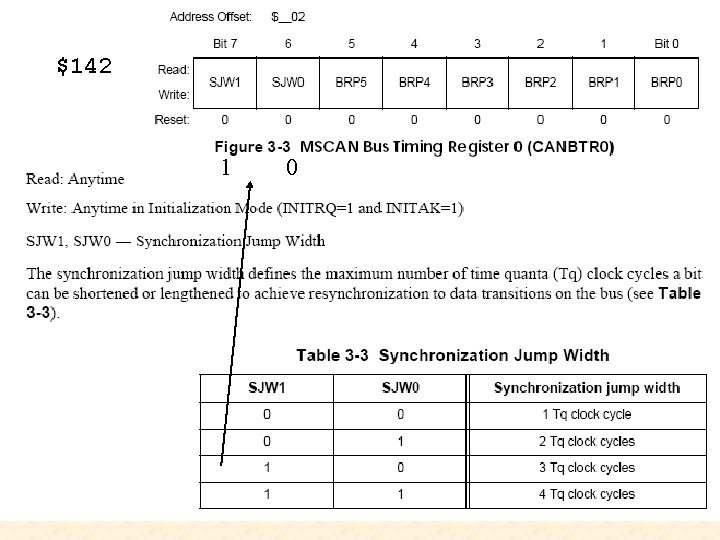

4 MHz 2 250 ns 2500/250 = 10 330/250 = 2 2 10 7 so PROP_SEG = 3, PHASE_SEG 1 = 3 and PHASE_SEG 2 = 3 RJW = 3

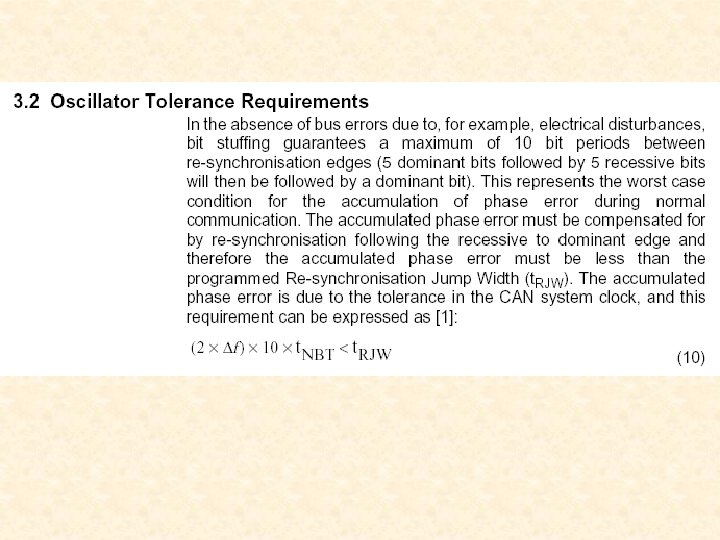

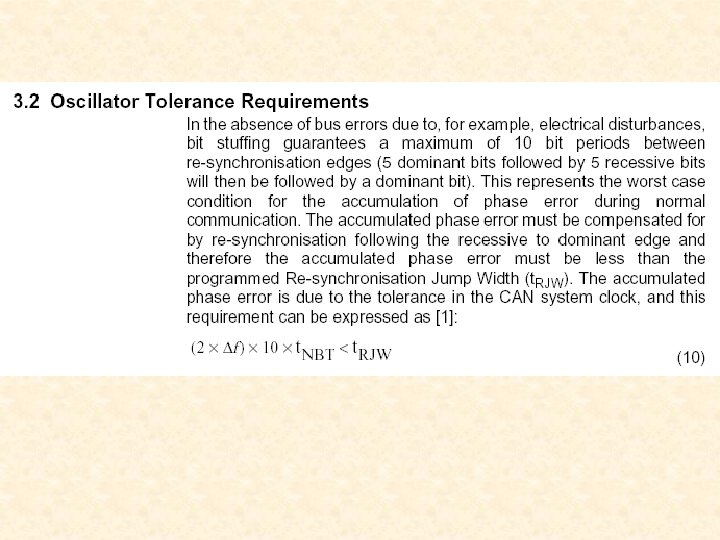

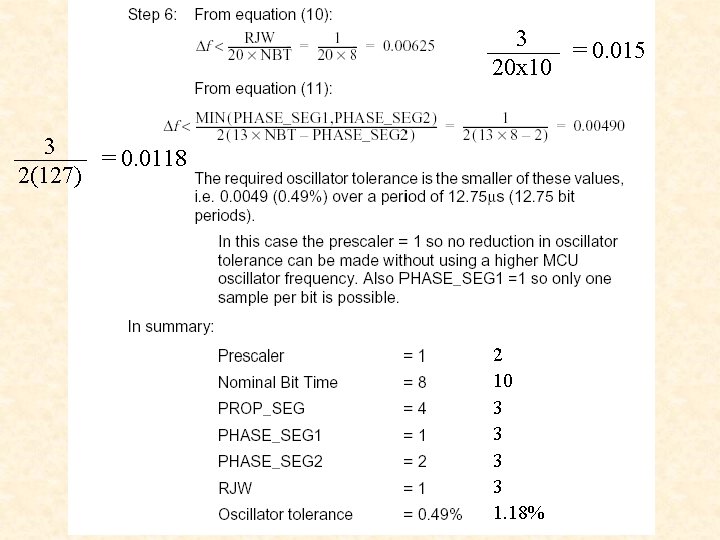

3 = 0. 015 20 x 10 3 = 0. 0118 2(127) 2 10 3 3 1. 18%

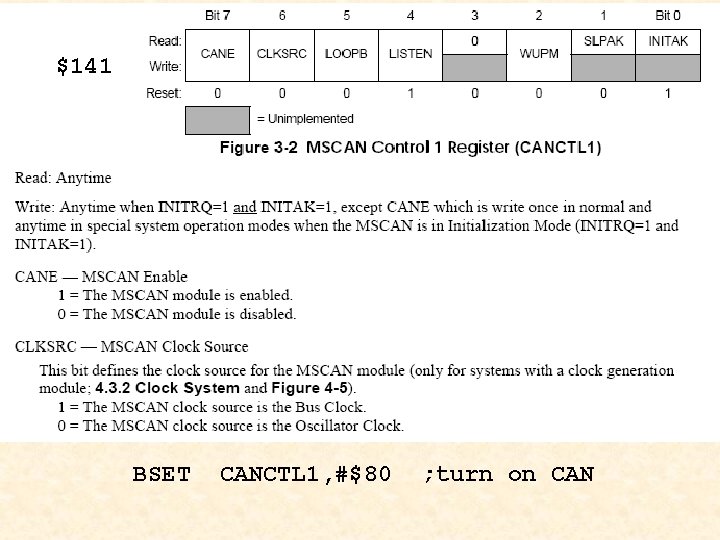

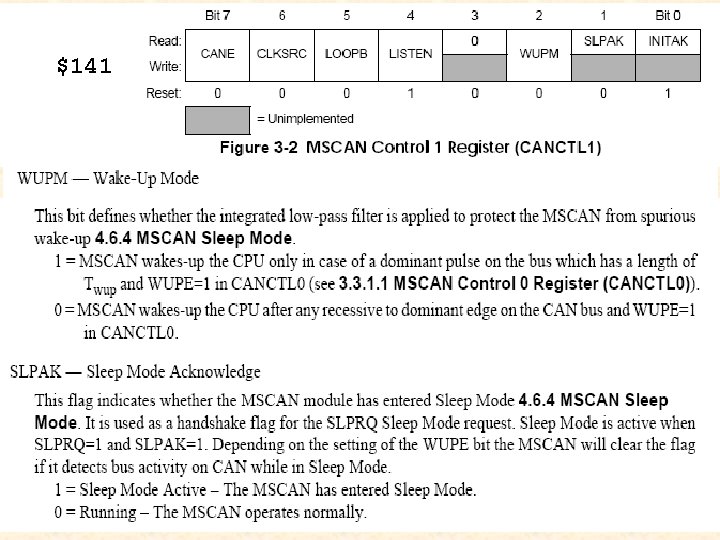

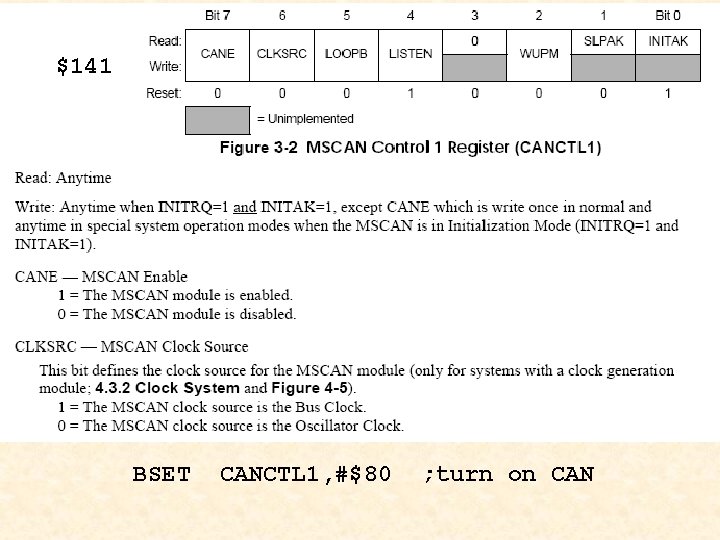

$141 BSET CANCTL 1, #$80 ; turn on CAN

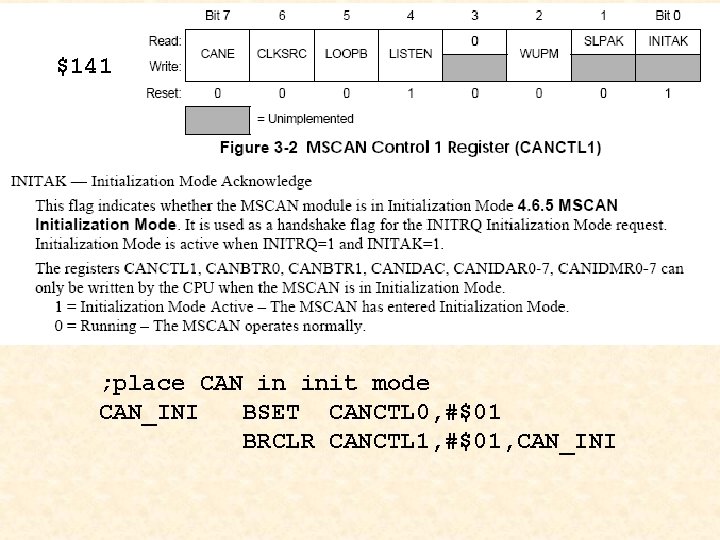

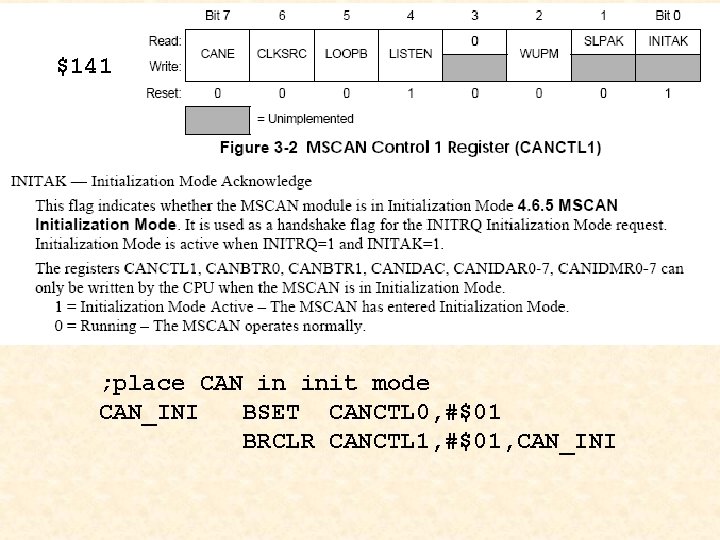

$141 ; place CAN in init mode CAN_INI BSET CANCTL 0, #$01 BRCLR CANCTL 1, #$01, CAN_INI

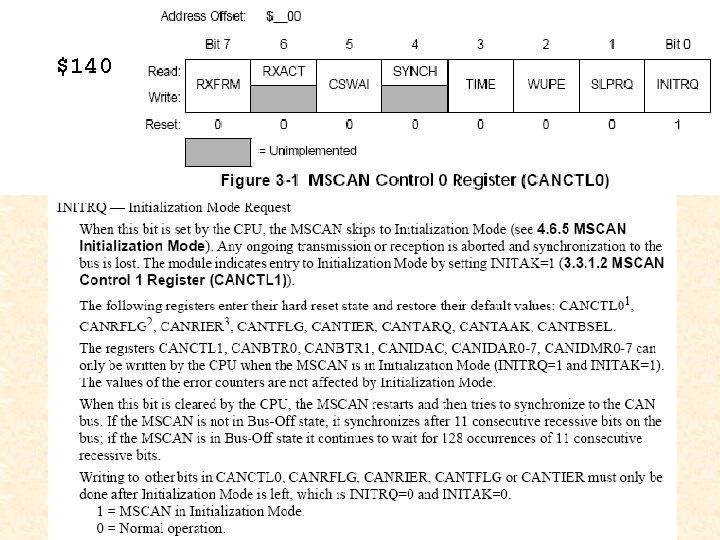

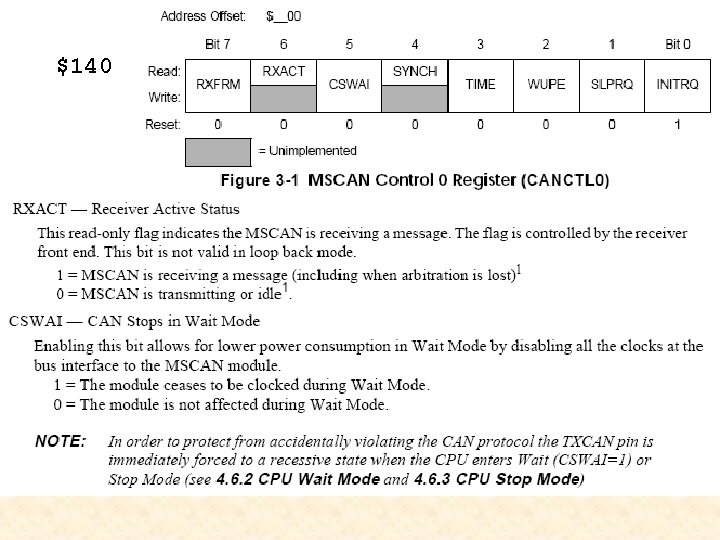

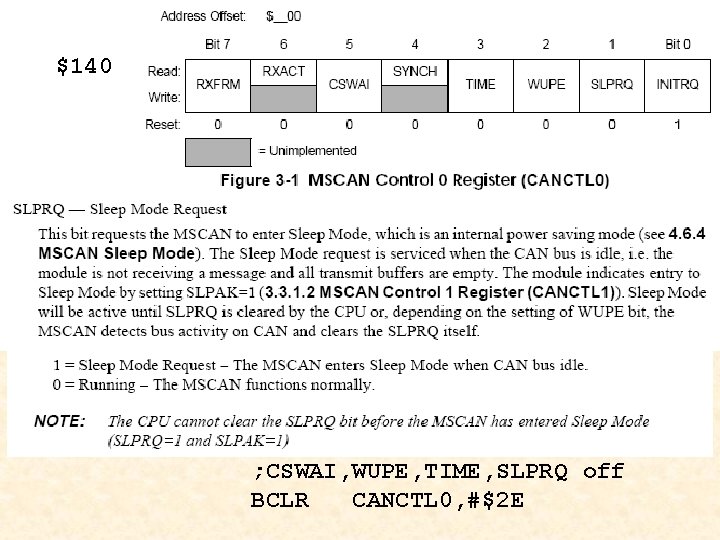

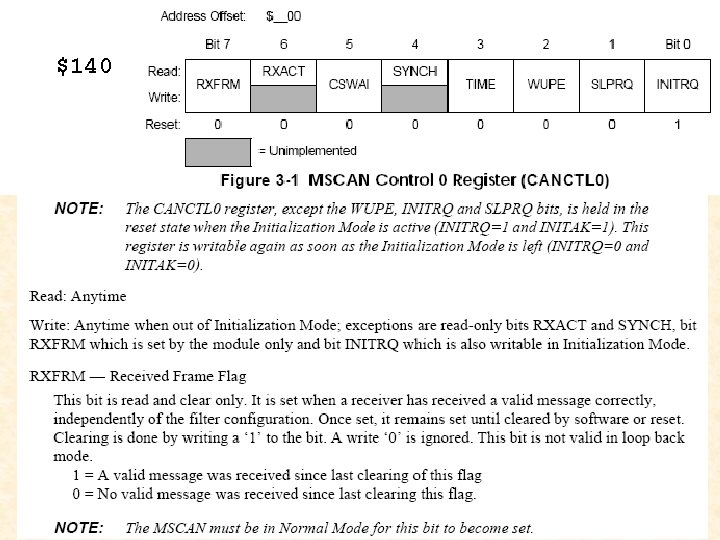

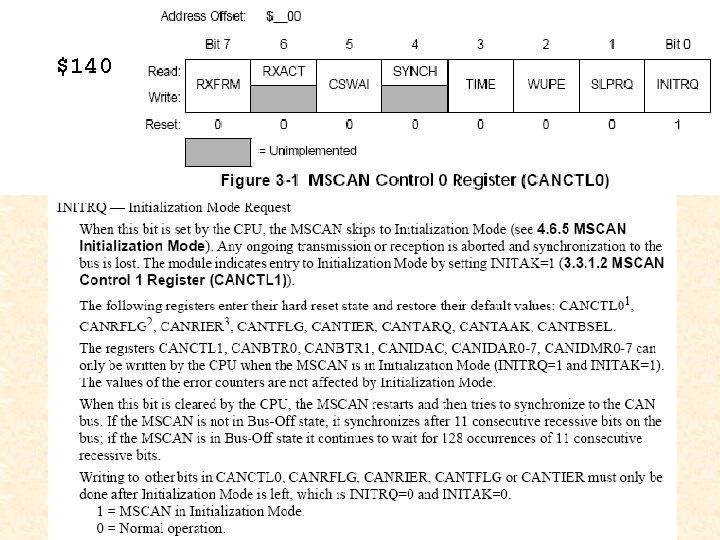

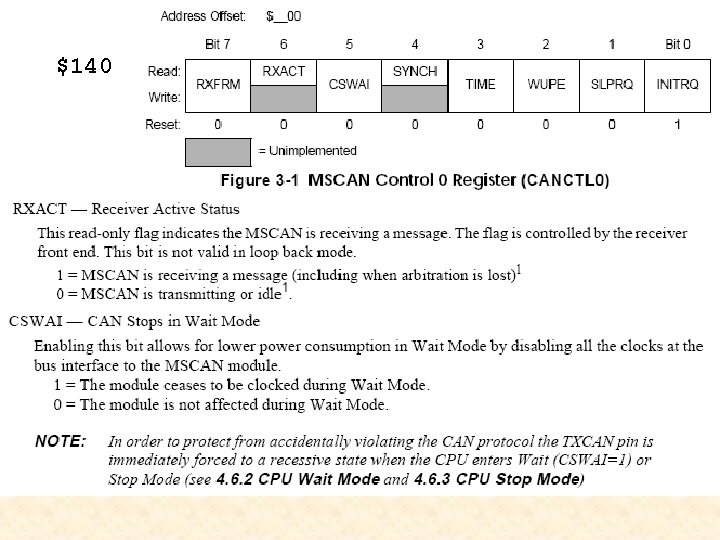

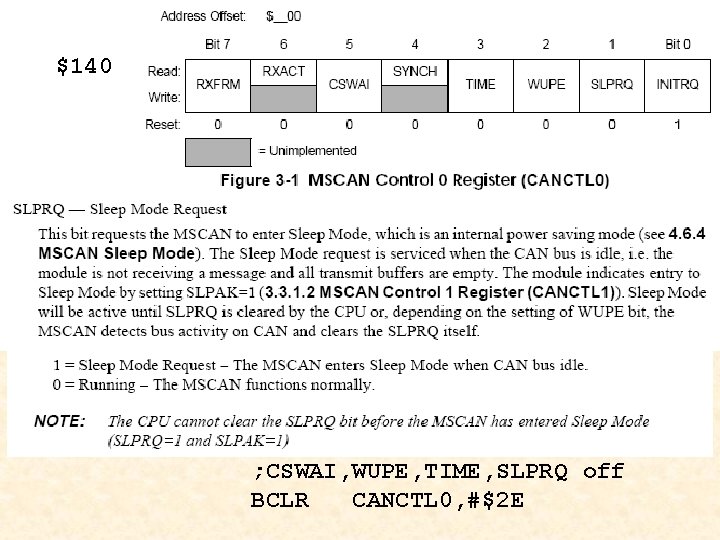

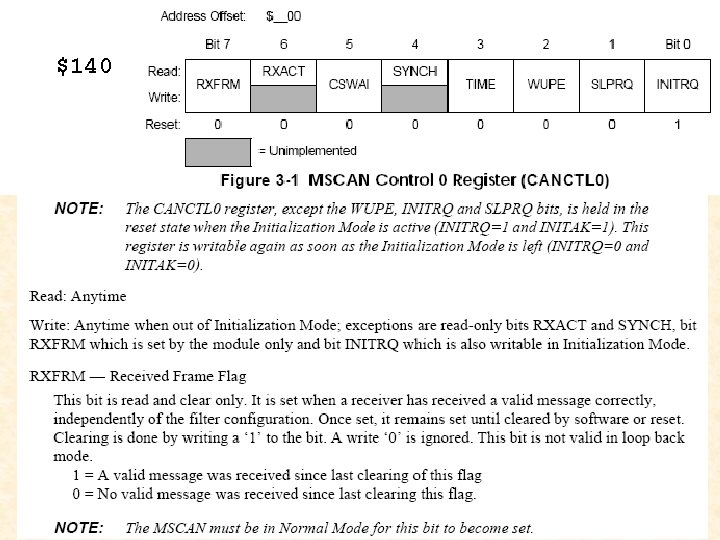

$140

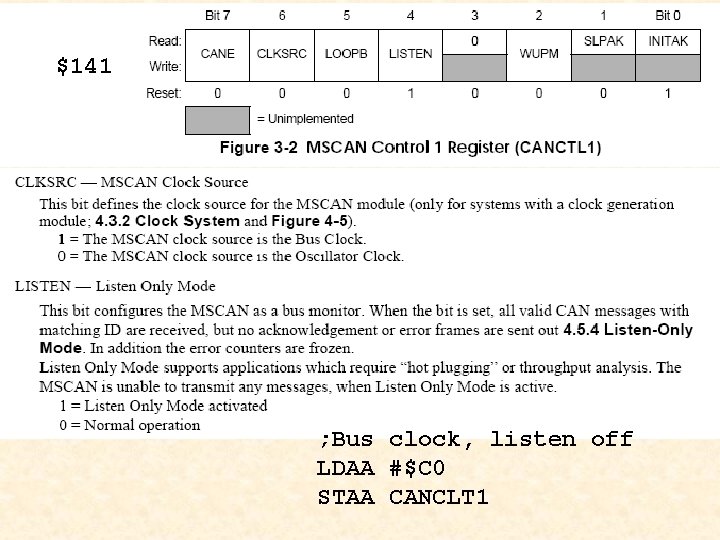

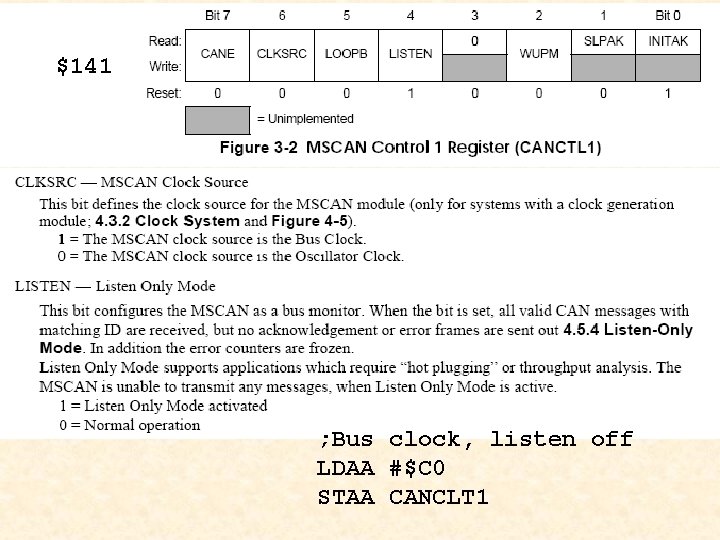

$141 ; Bus clock, listen off LDAA #$C 0 STAA CANCLT 1

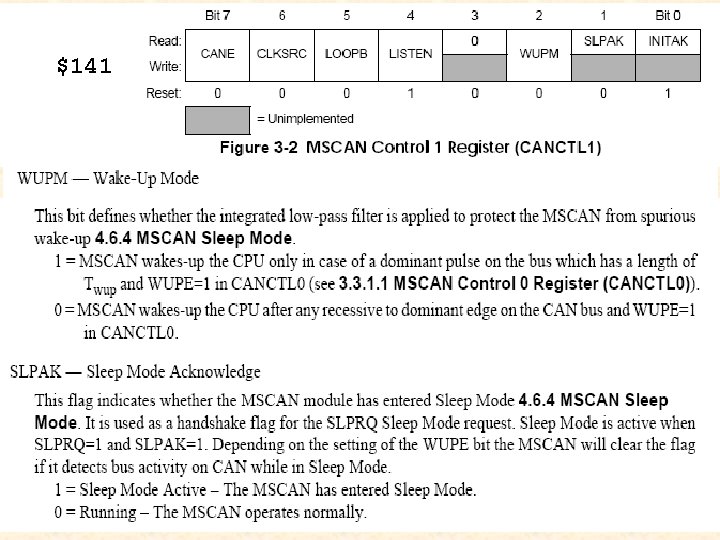

$141

$140

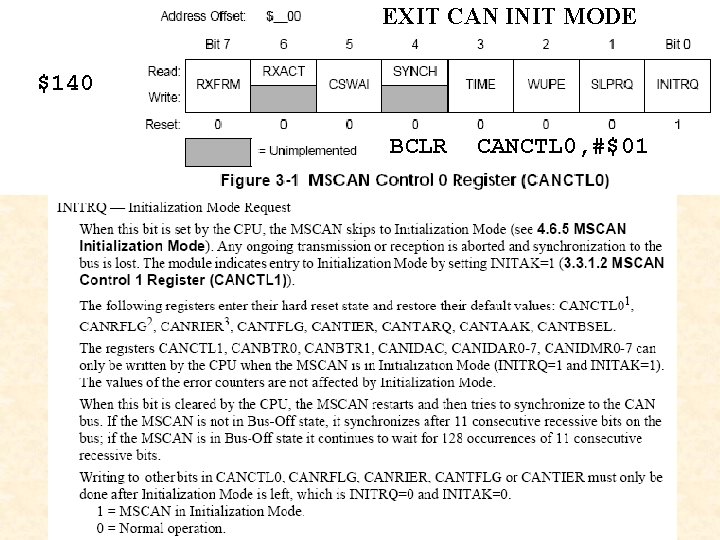

$140 ; CSWAI, WUPE, TIME, SLPRQ off BCLR CANCTL 0, #$2 E

$140 ; CSWAI, WUPE, TIME, SLPRQ off BCLR CANCTL 0, #$2 E

1 3+3=6 3

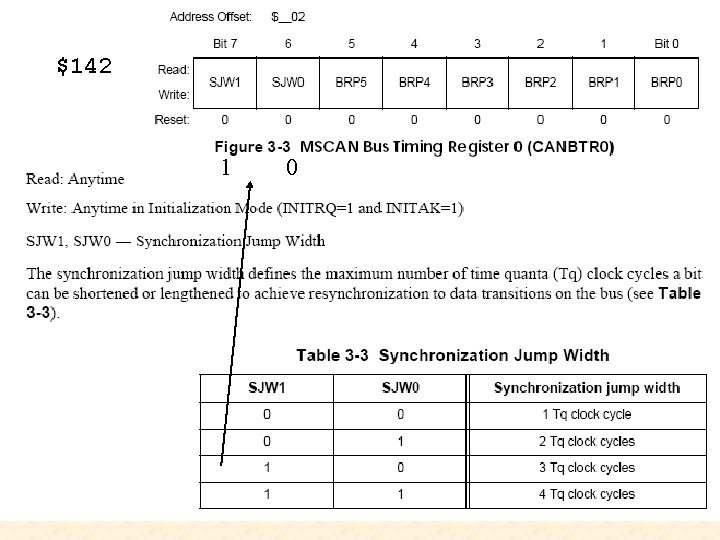

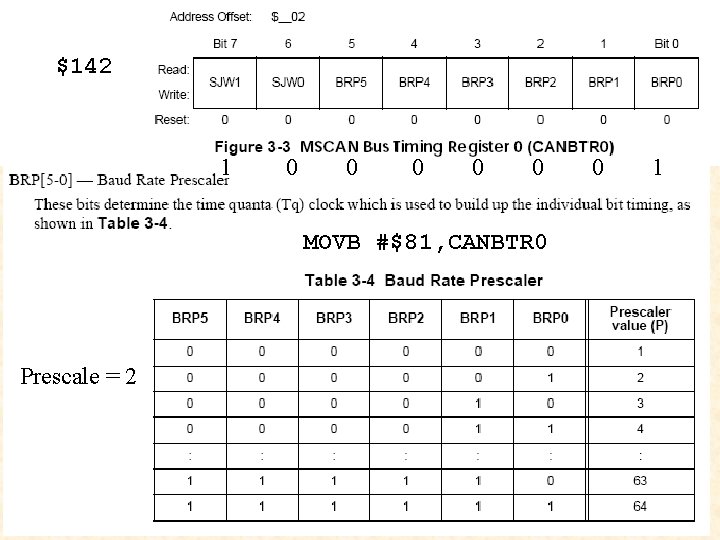

$142 1 0

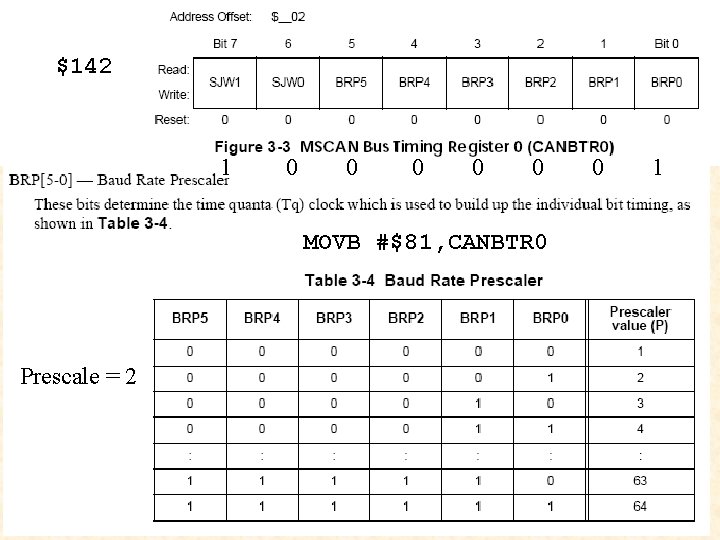

$142 1 0 0 0 MOVB #$81, CANBTR 0 Prescale = 2 0 1

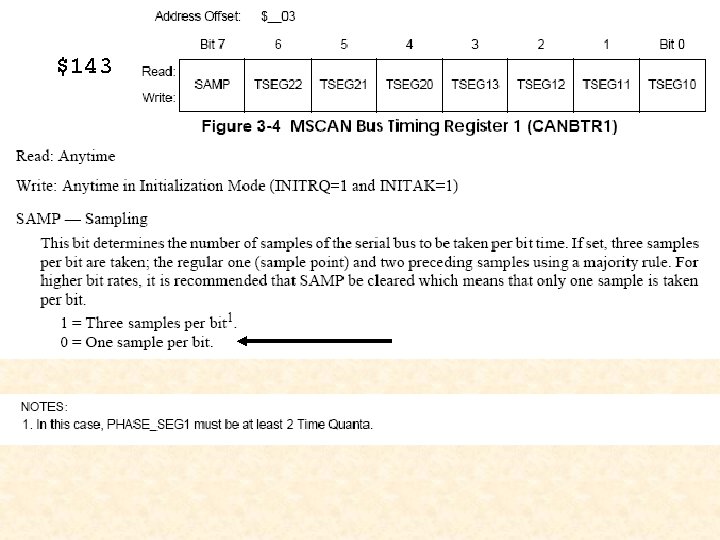

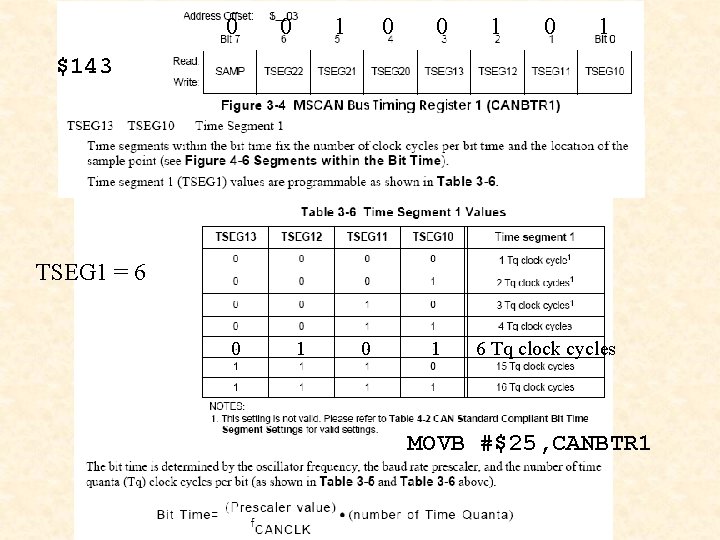

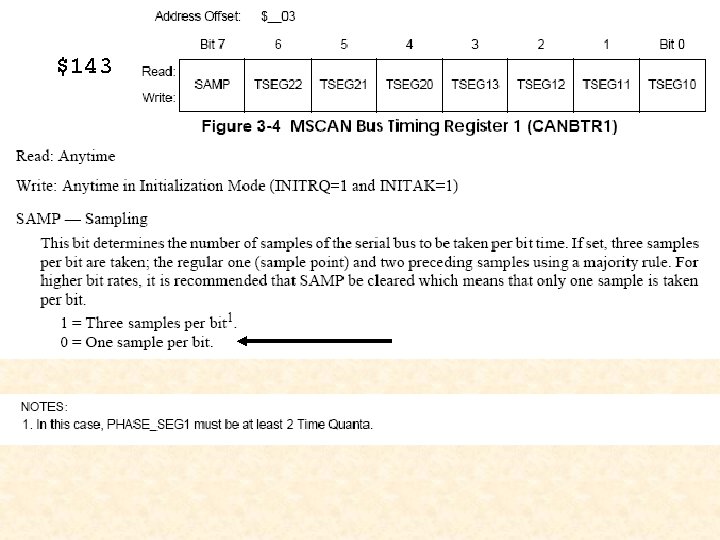

$143

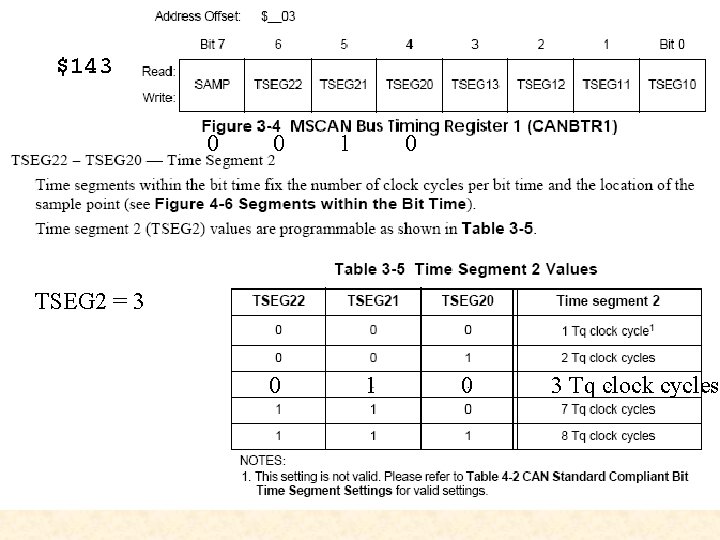

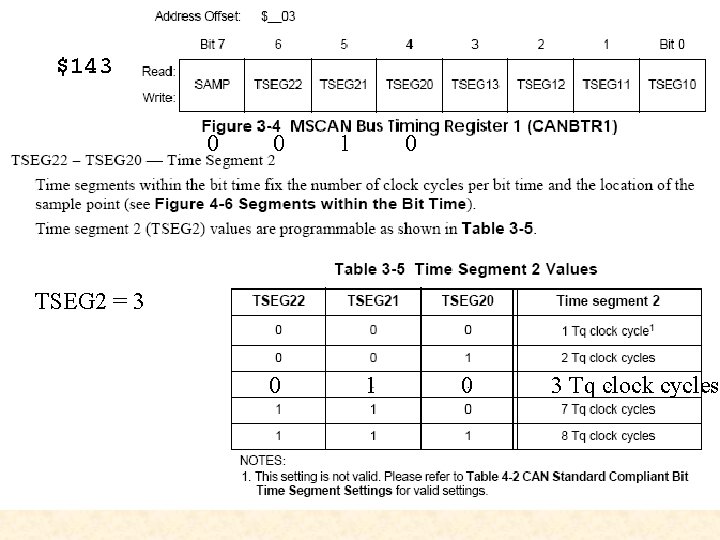

$143 0 0 1 0 TSEG 2 = 3 0 1 0 3 Tq clock cycles

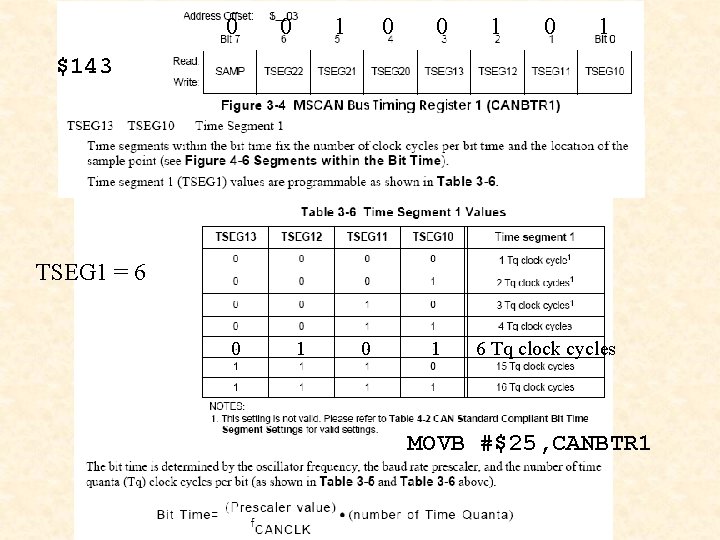

0 0 1 0 1 $143 TSEG 1 = 6 0 1 6 Tq clock cycles MOVB #$25, CANBTR 1

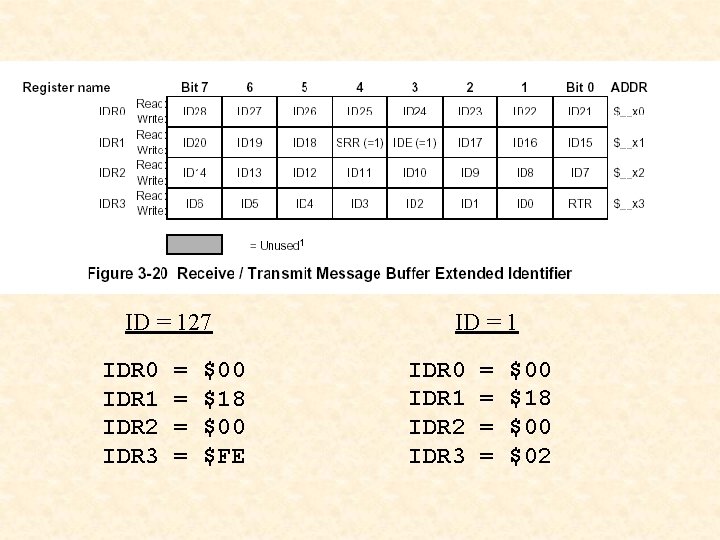

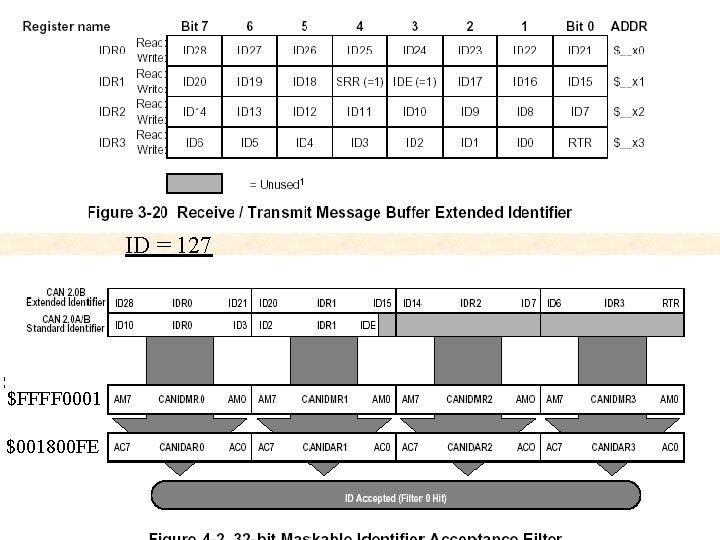

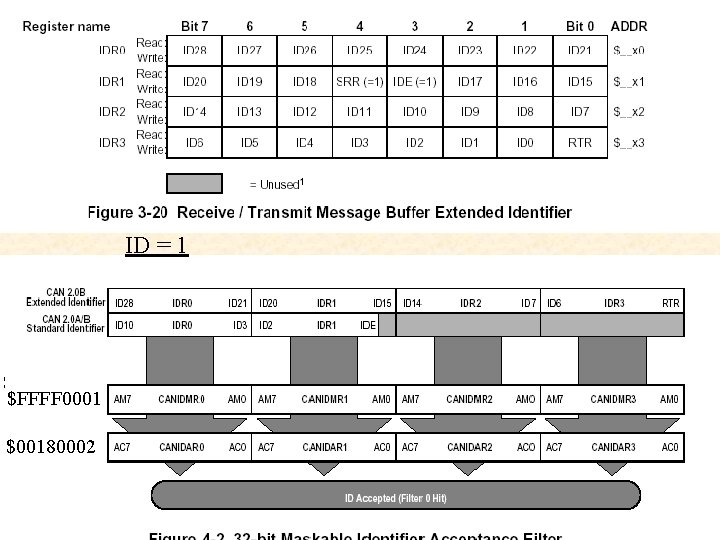

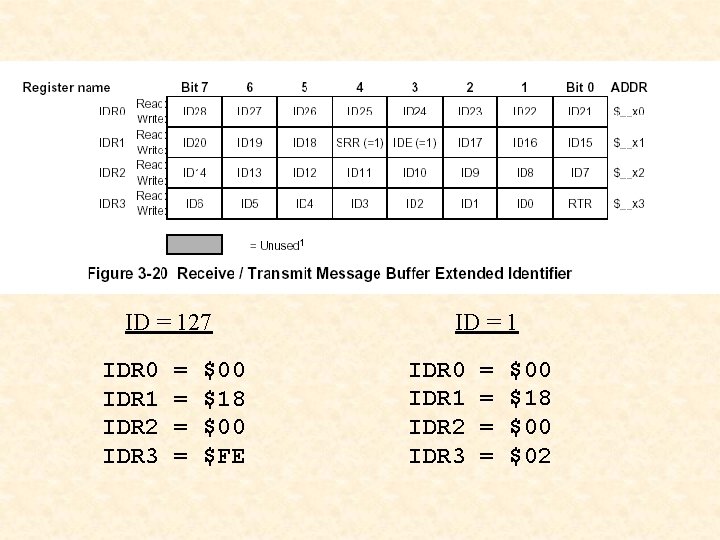

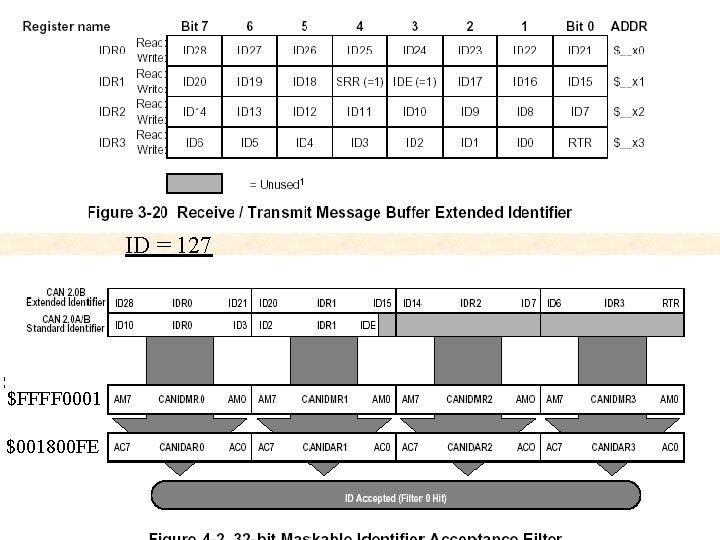

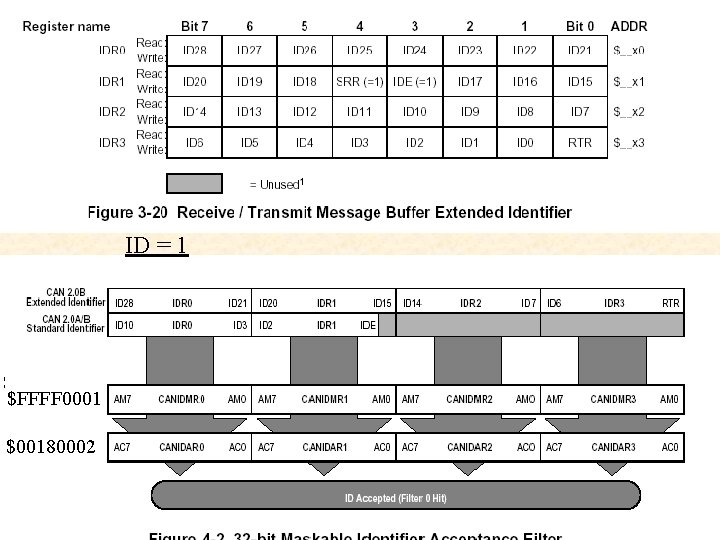

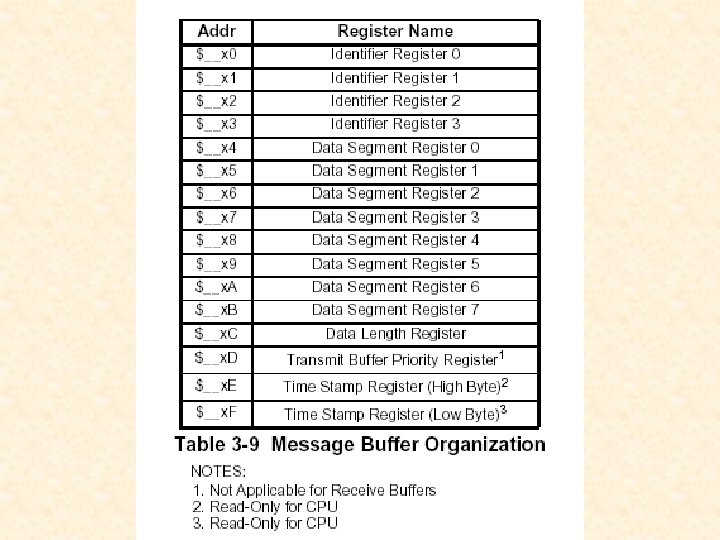

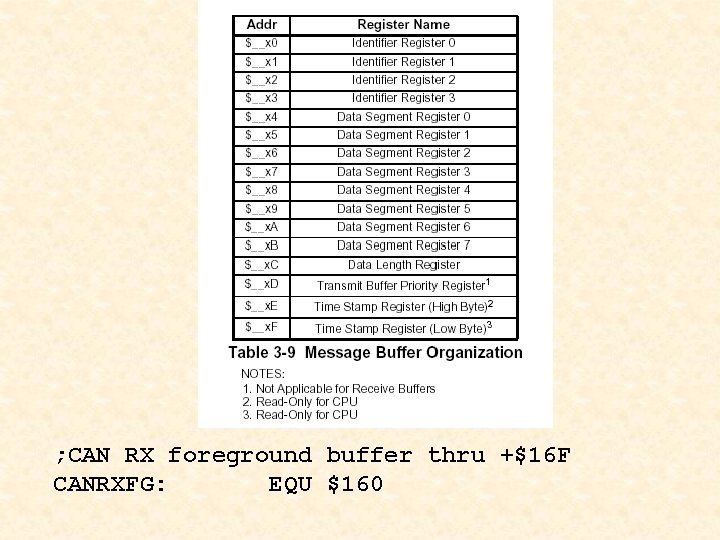

ID = 127 IDR 0 IDR 1 IDR 2 IDR 3 = = $00 $18 $00 $FE ID = 1 IDR 0 IDR 1 IDR 2 IDR 3 = = $00 $18 $00 $02

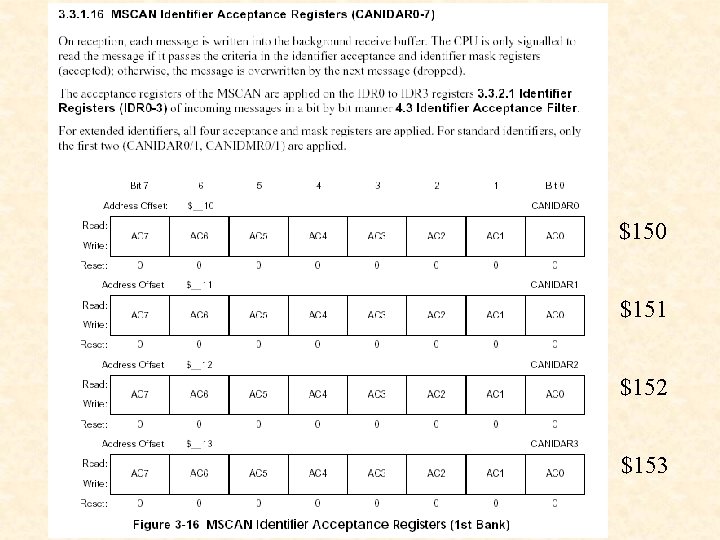

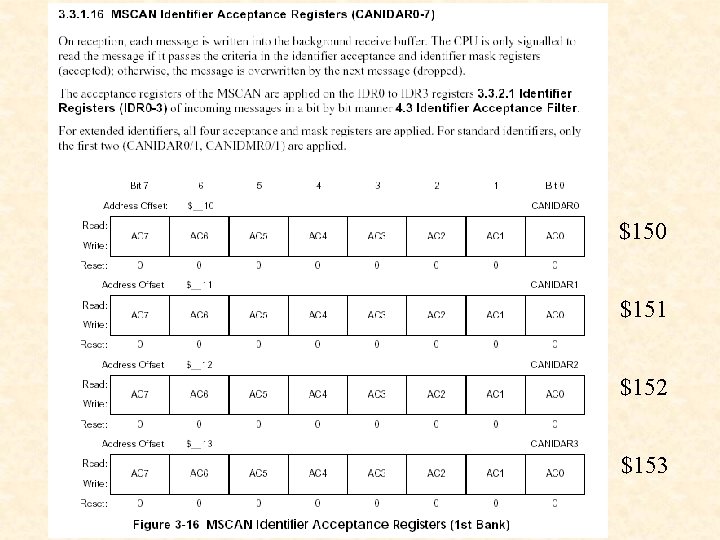

$150 $151 $152 $153

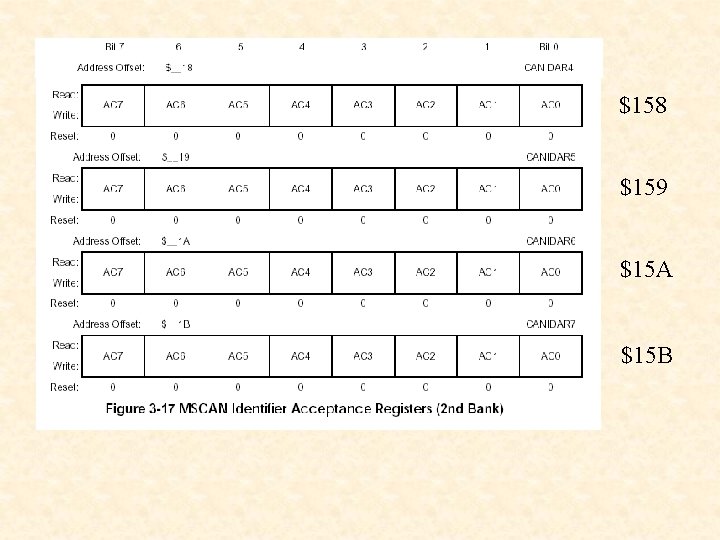

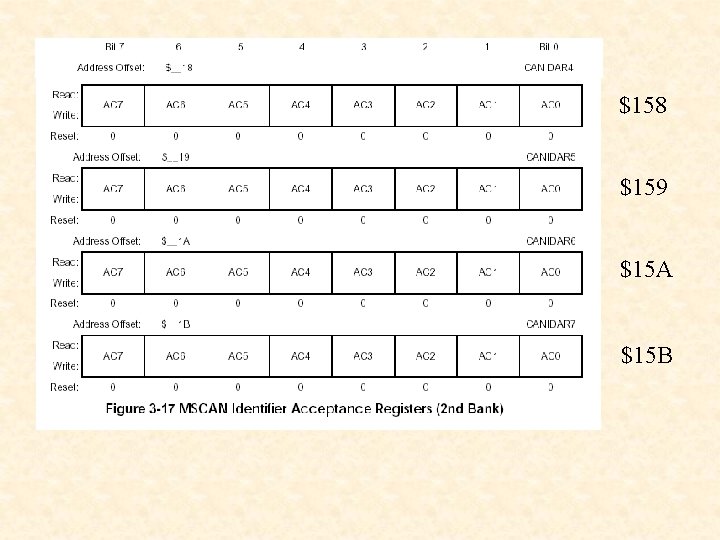

$158 $159 $15 A $15 B

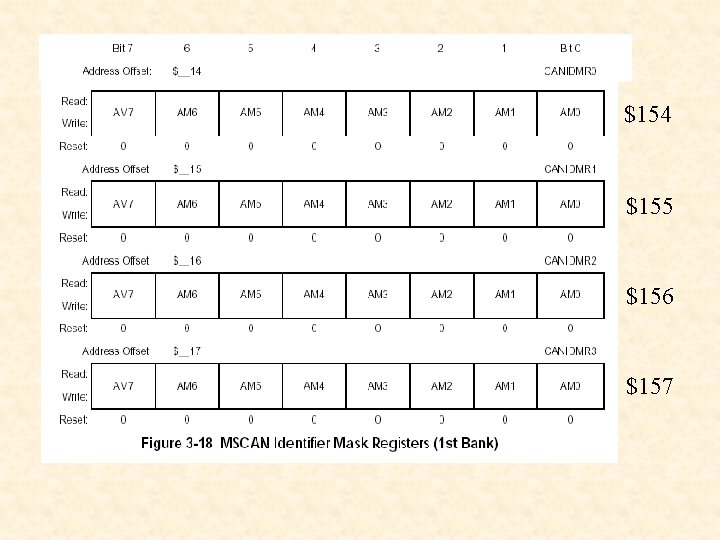

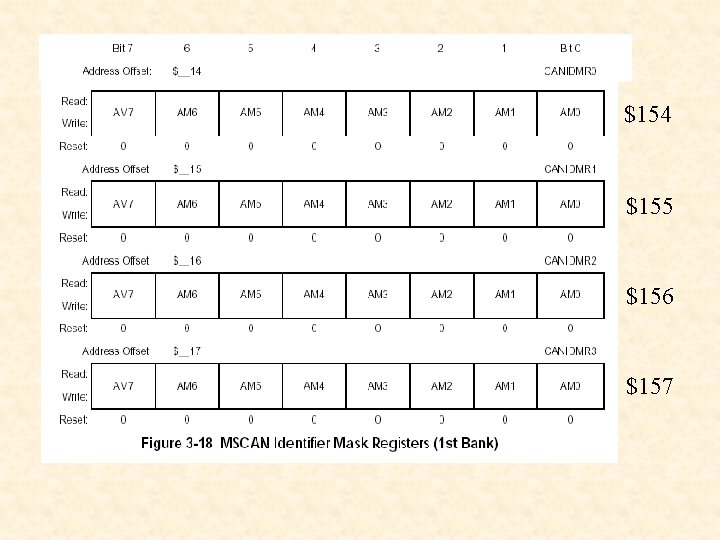

$154 $155 $156 $157

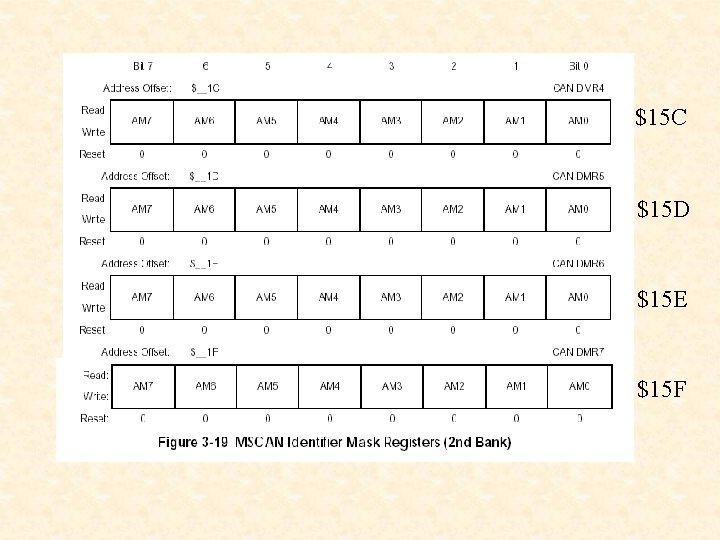

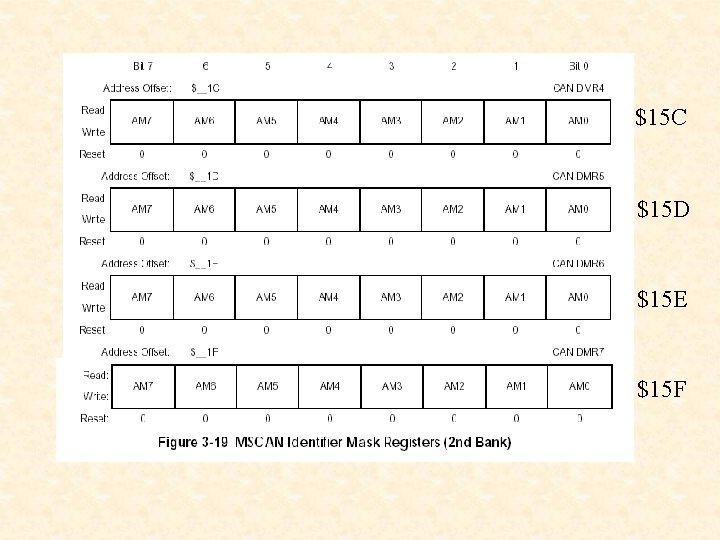

$15 C $15 D $15 E $15 F

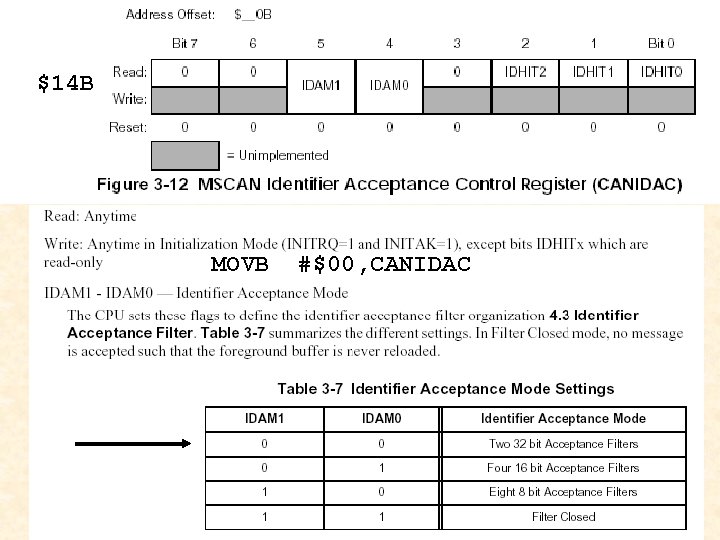

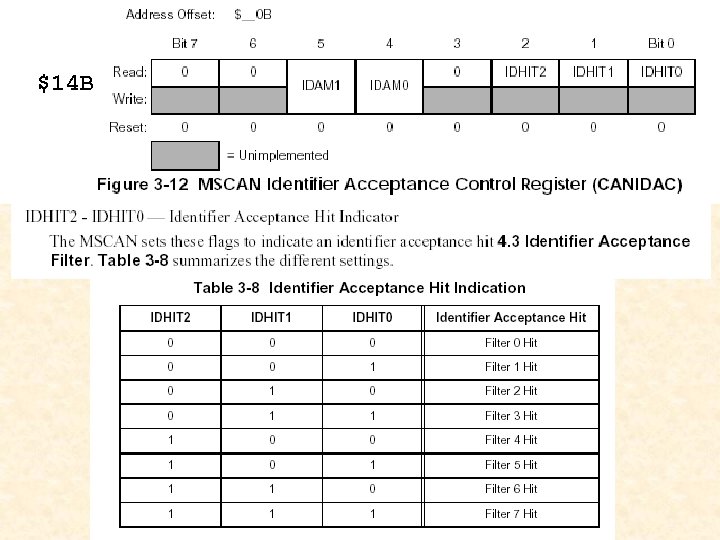

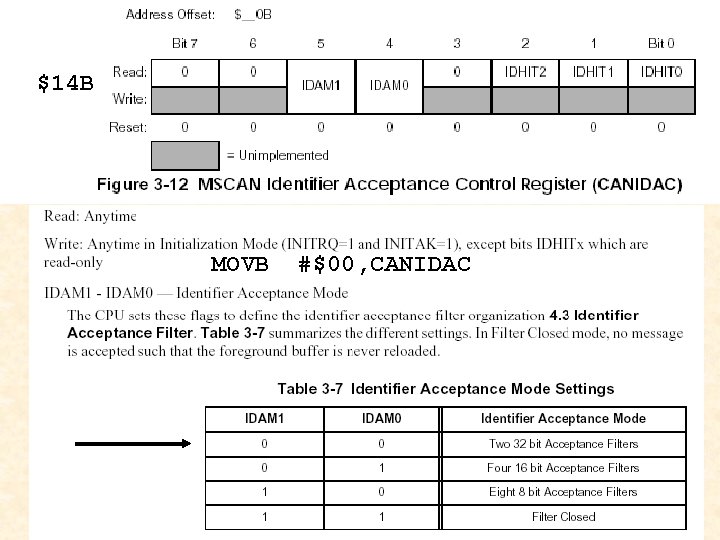

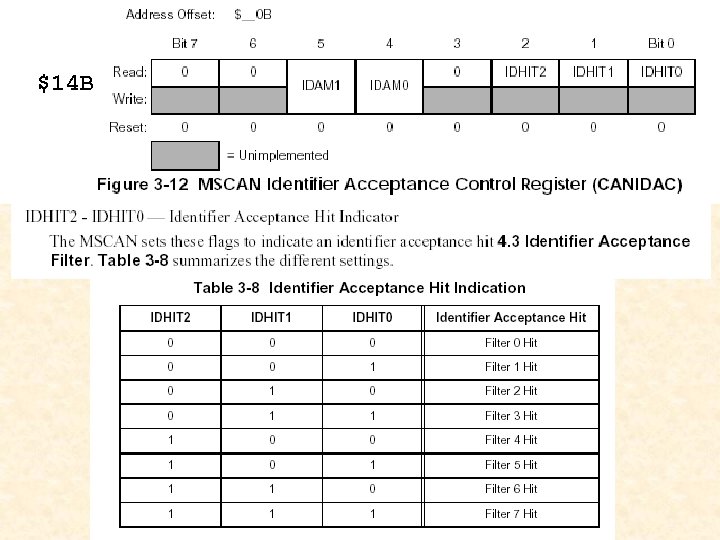

$14 B MOVB #$00, CANIDAC

ID = 127 $FFFF 0001 $001800 FE

ID = 1 $FFFF 0001 $00180002

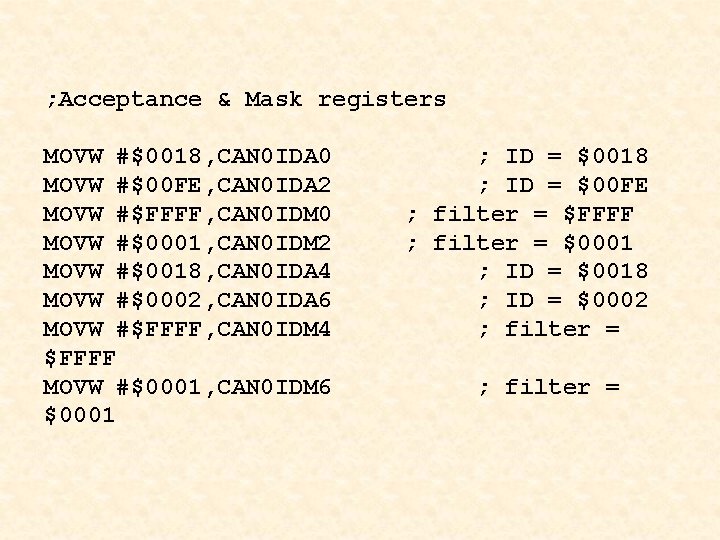

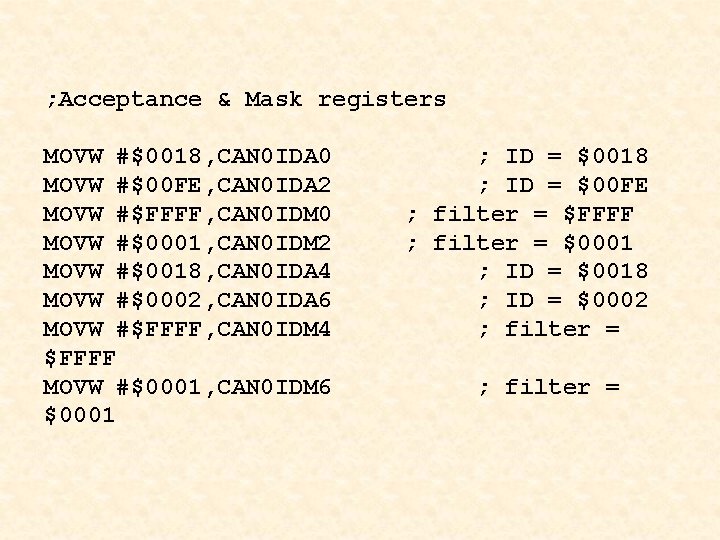

; Acceptance & Mask registers MOVW #$0018, CAN 0 IDA 0 MOVW #$00 FE, CAN 0 IDA 2 MOVW #$FFFF, CAN 0 IDM 0 MOVW #$0001, CAN 0 IDM 2 MOVW #$0018, CAN 0 IDA 4 MOVW #$0002, CAN 0 IDA 6 MOVW #$FFFF, CAN 0 IDM 4 $FFFF MOVW #$0001, CAN 0 IDM 6 $0001 ; ID = $0018 ; ID = $00 FE ; filter = $FFFF ; filter = $0001 ; ID = $0018 ; ID = $0002 ; filter =

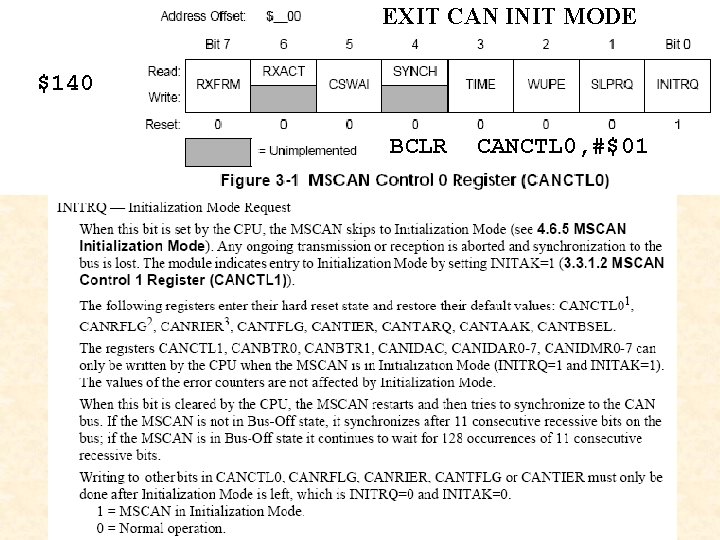

EXIT CAN INIT MODE $140 BCLR CANCTL 0, #$01

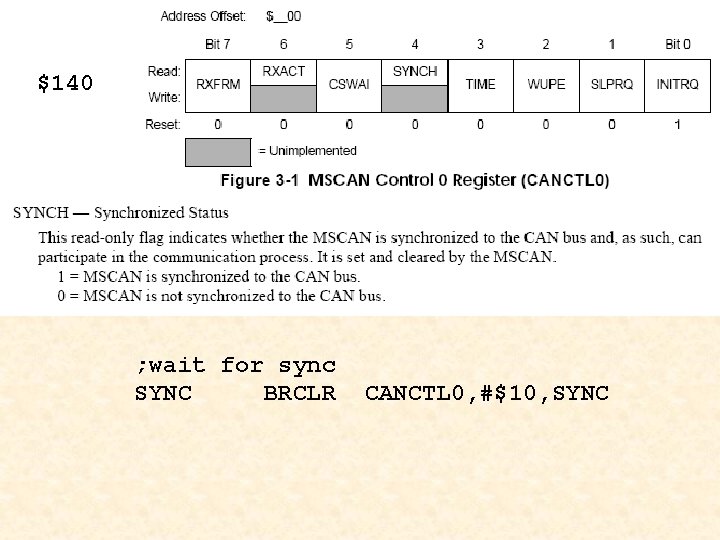

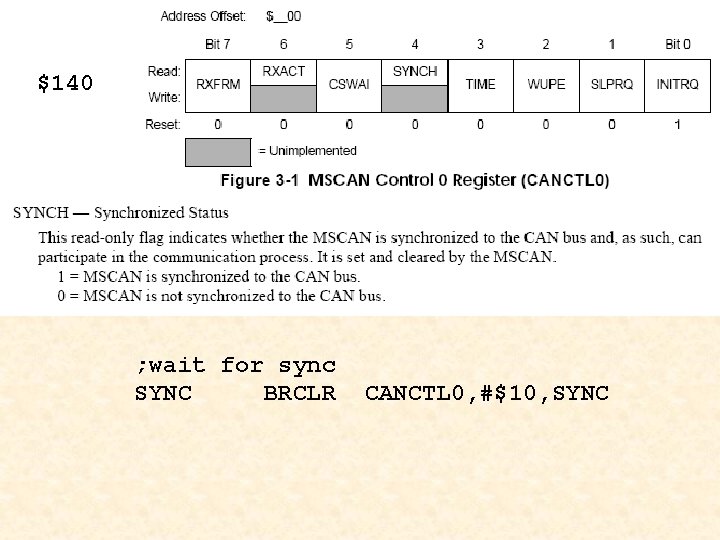

$140 ; wait for sync SYNC BRCLR CANCTL 0, #$10, SYNC

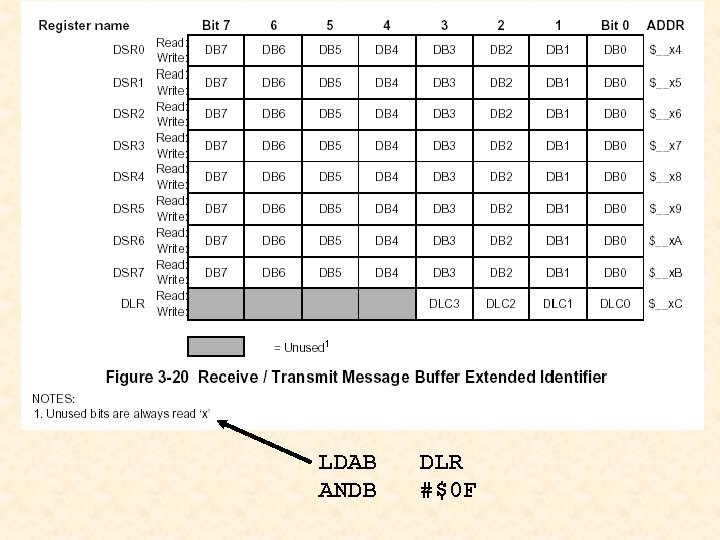

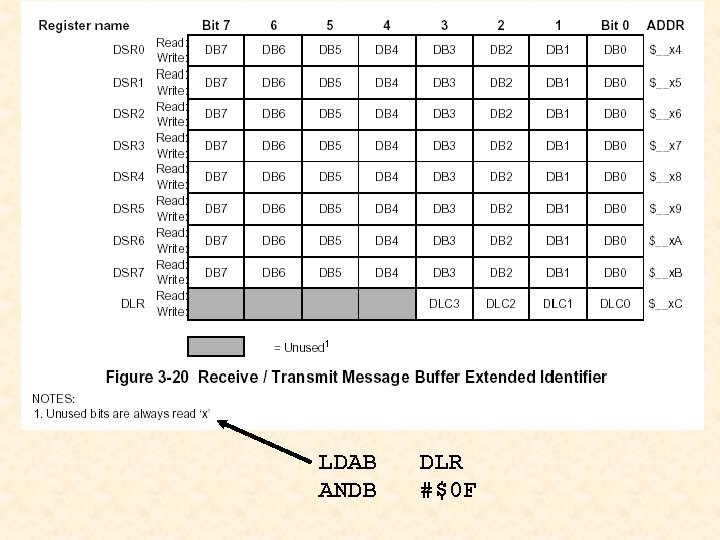

LDAB ANDB DLR #$0 F

$14 B

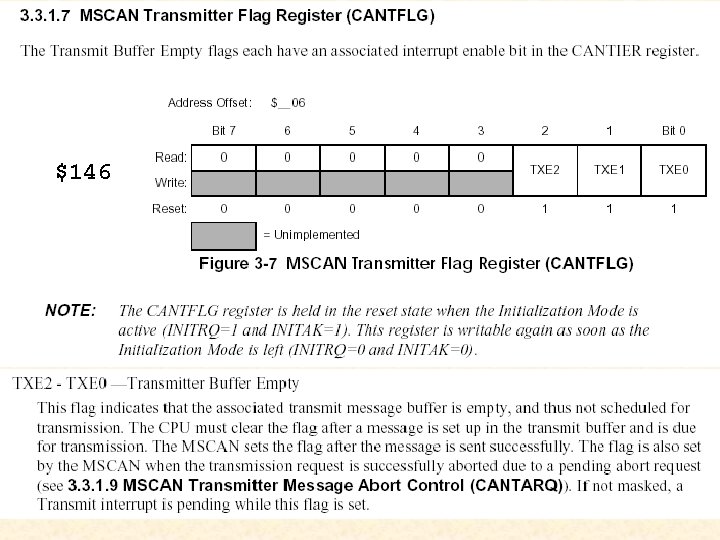

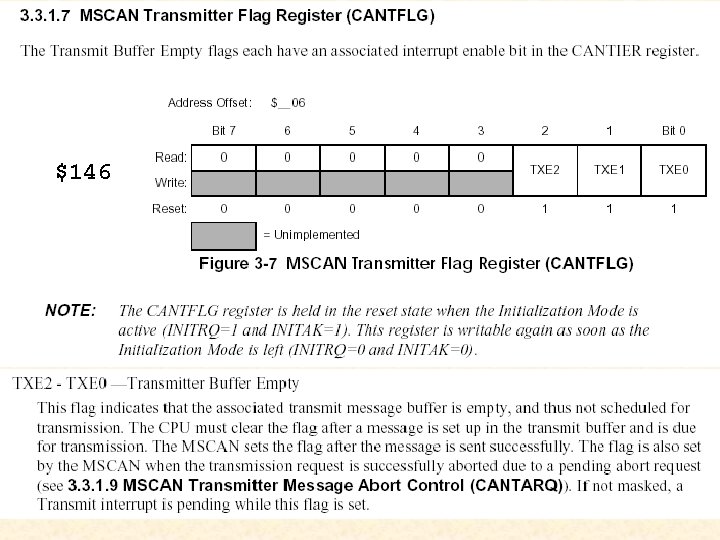

$146

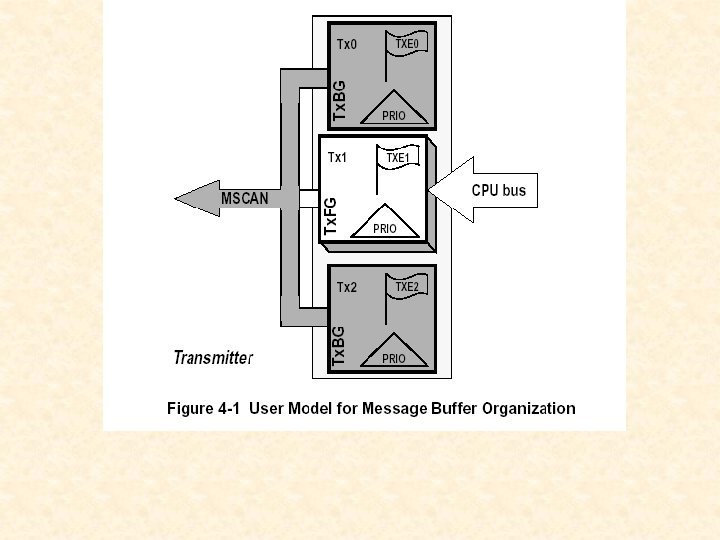

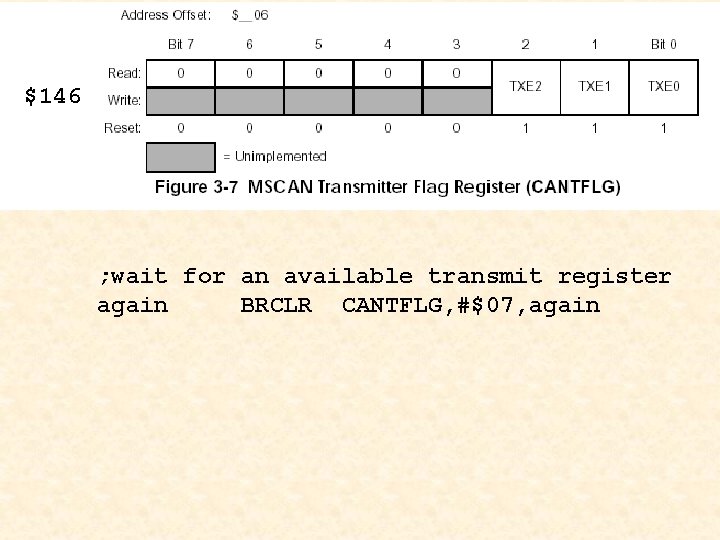

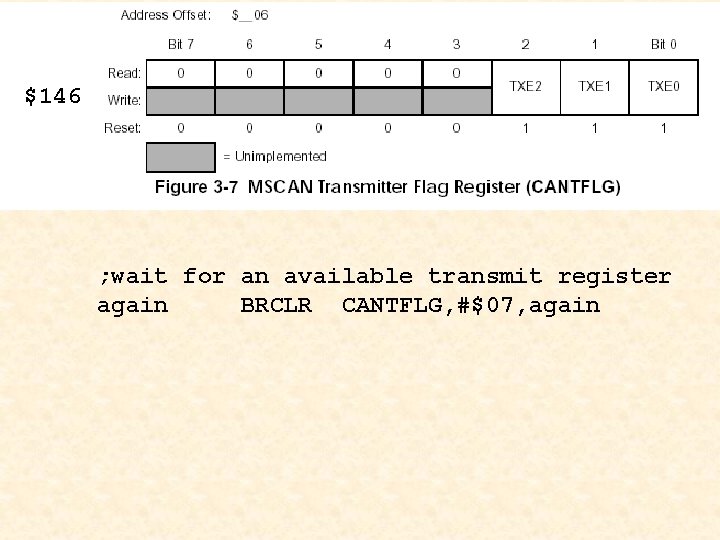

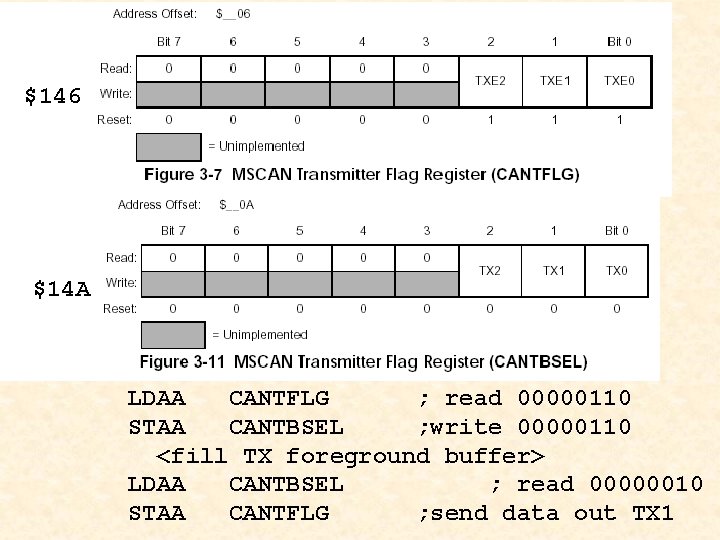

$146 ; wait for an available transmit register again BRCLR CANTFLG, #$07, again

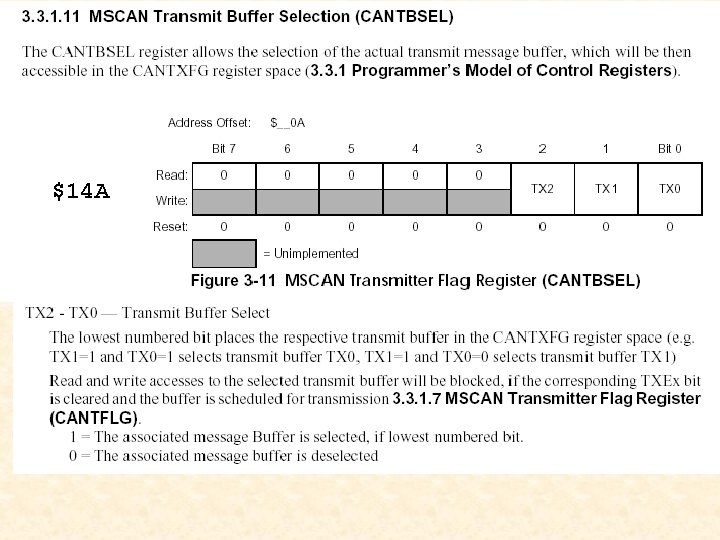

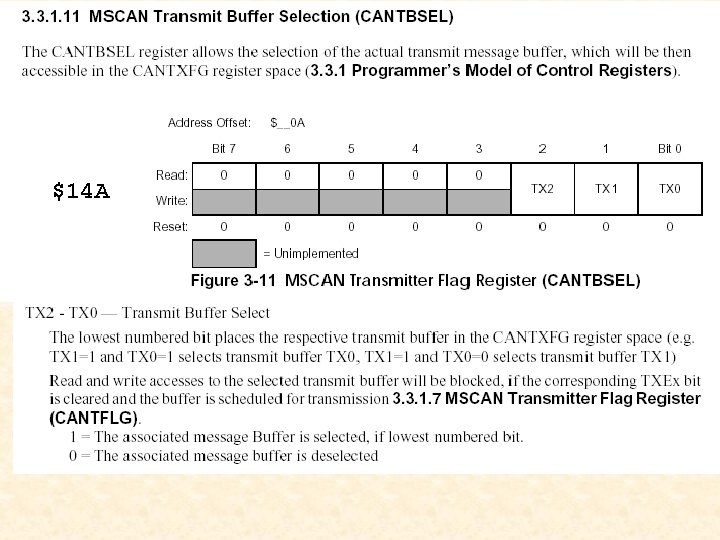

$14 A

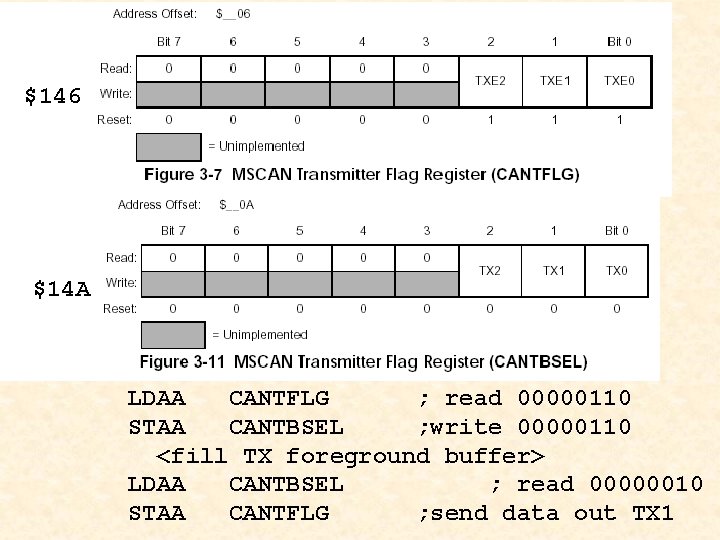

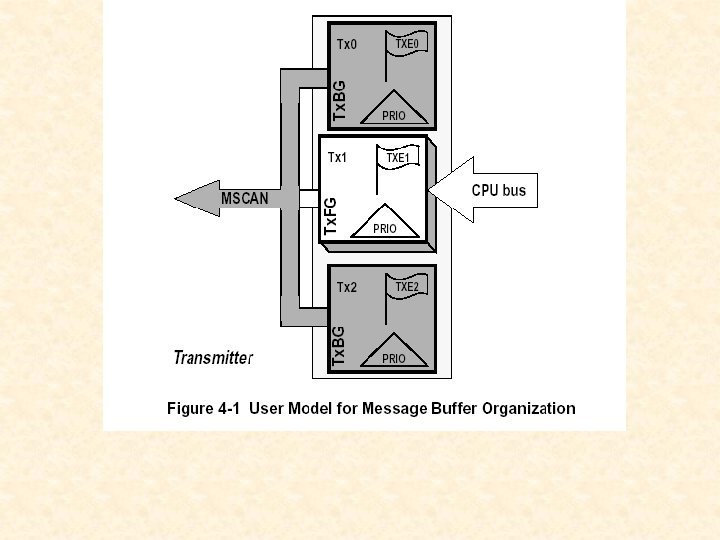

$146 $14 A LDAA CANTFLG ; read 00000110 STAA CANTBSEL ; write 00000110 <fill TX foreground buffer> LDAA CANTBSEL ; read 00000010 STAA CANTFLG ; send data out TX 1

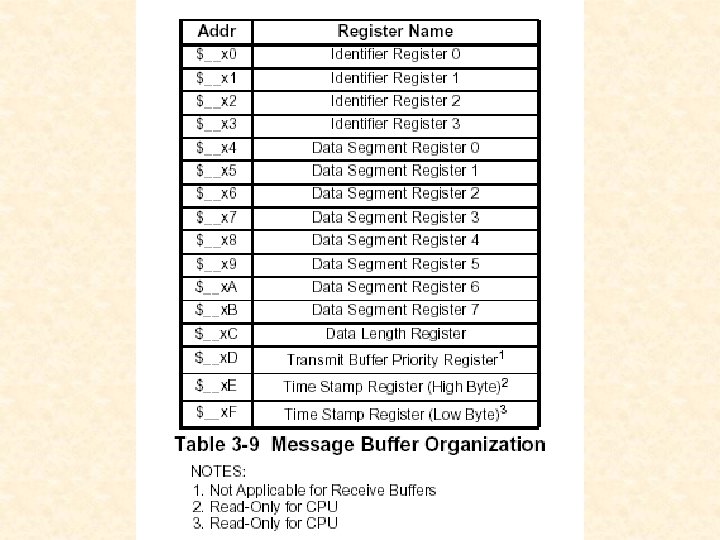

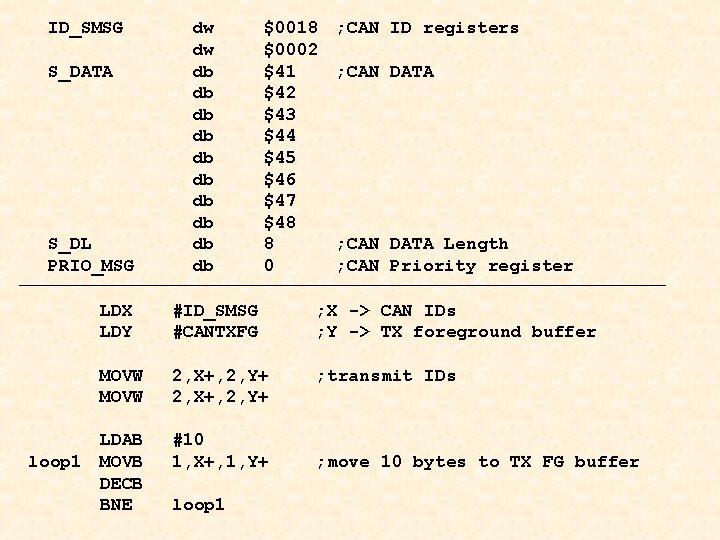

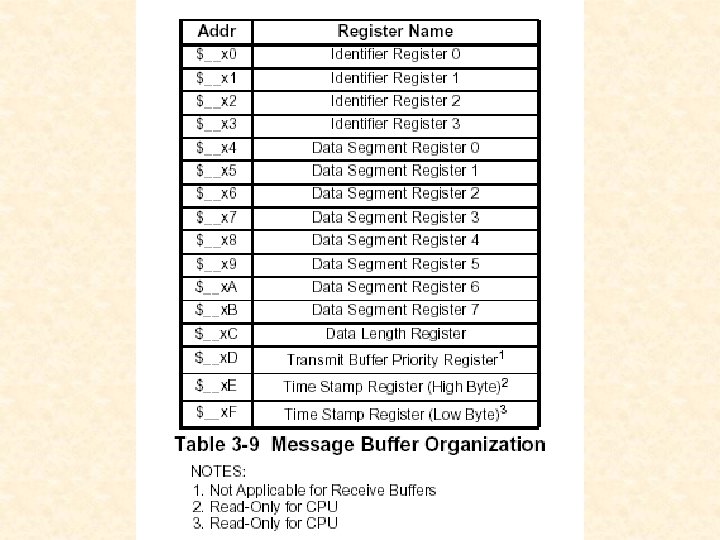

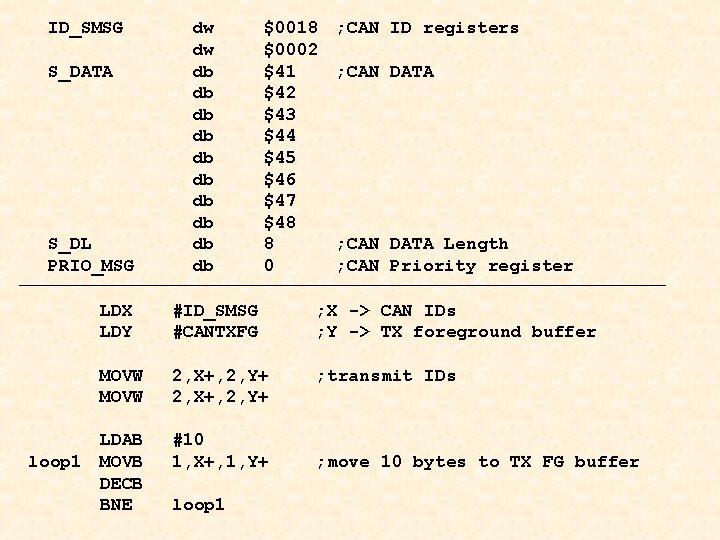

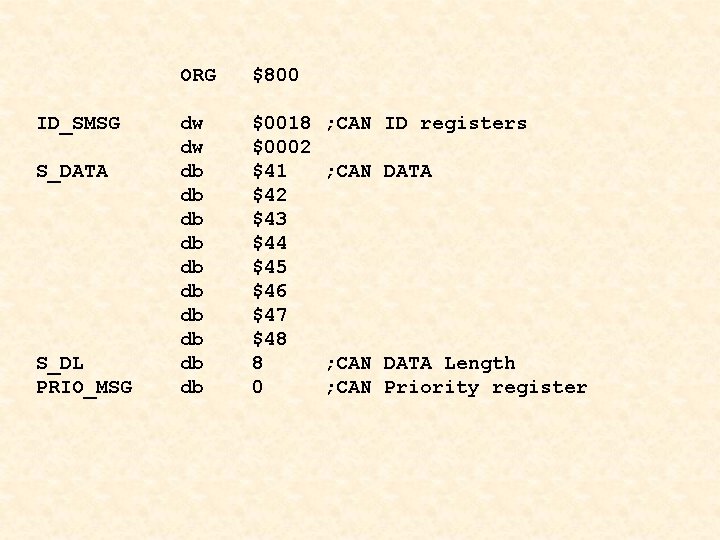

ID_SMSG S_DATA S_DL PRIO_MSG loop 1 dw dw db db db $0018 $0002 $41 $42 $43 $44 $45 $46 $47 $48 8 0 ; CAN ID registers ; CAN DATA Length ; CAN Priority register LDX LDY #ID_SMSG #CANTXFG ; X -> CAN IDs ; Y -> TX foreground buffer MOVW 2, X+, 2, Y+ ; transmit IDs LDAB MOVB DECB BNE #10 1, X+, 1, Y+ loop 1 ; move 10 bytes to TX FG buffer

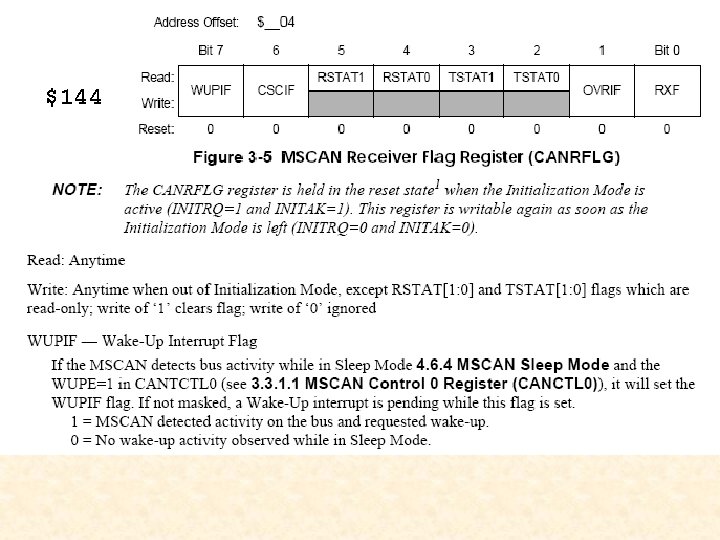

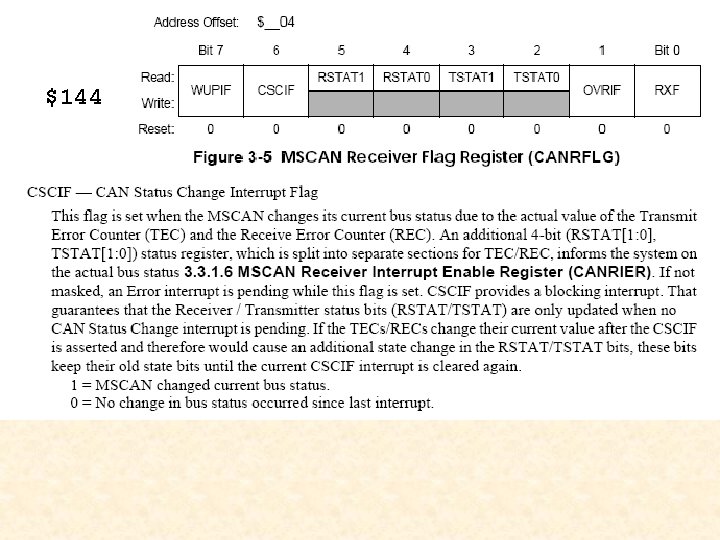

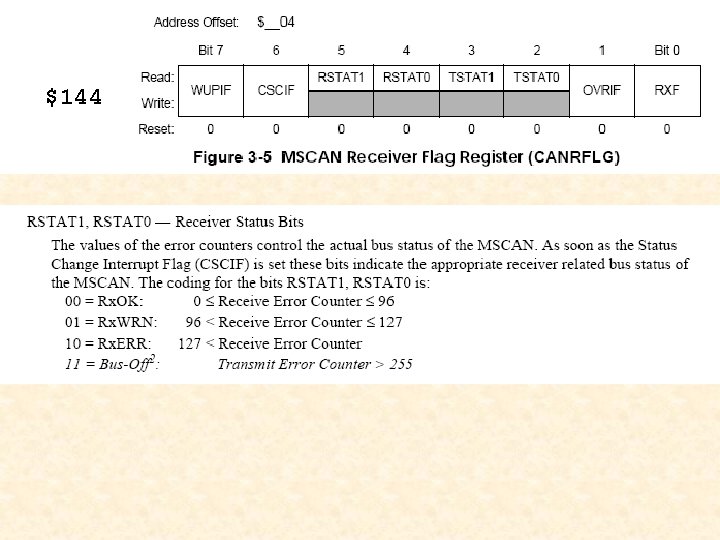

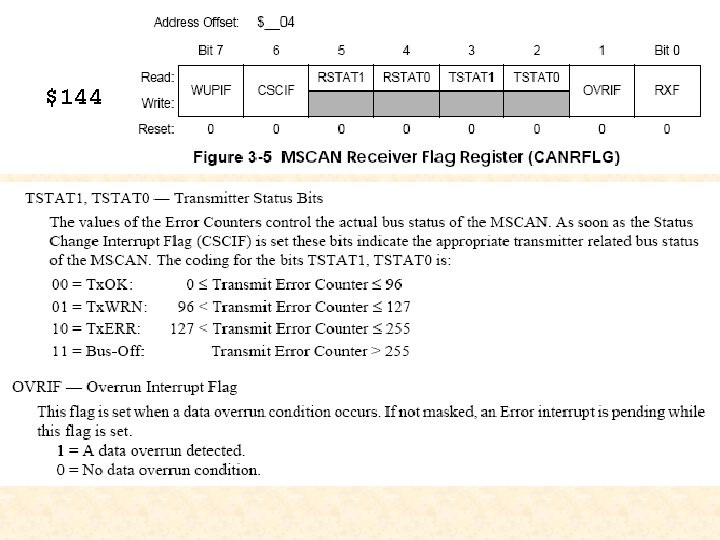

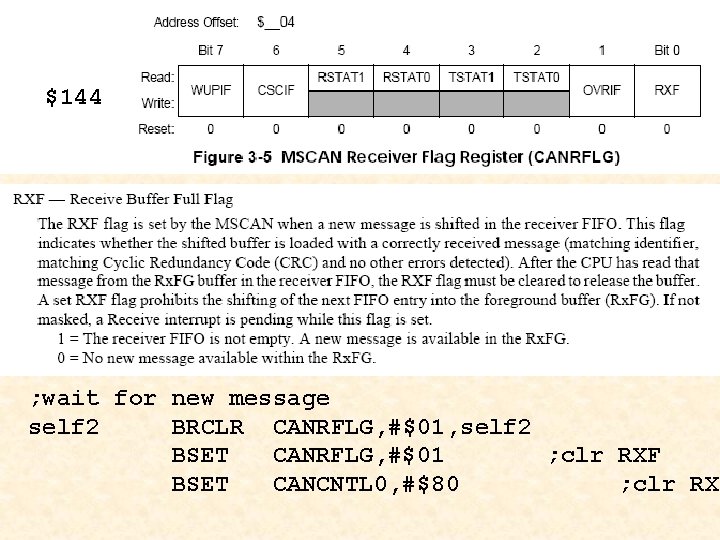

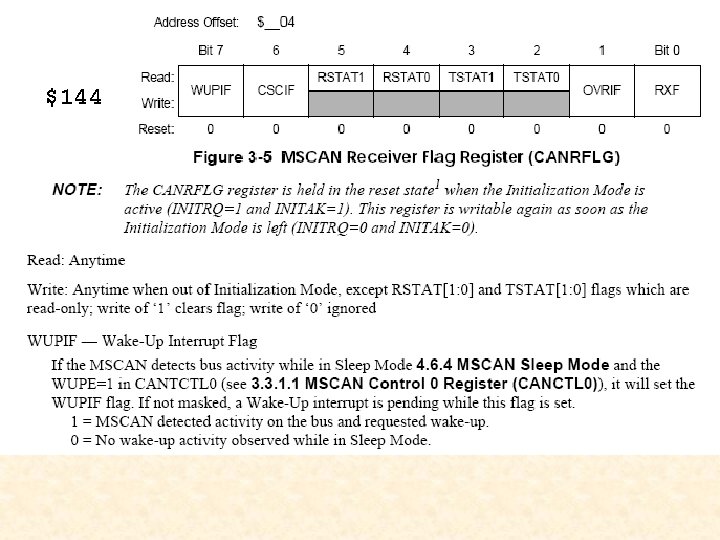

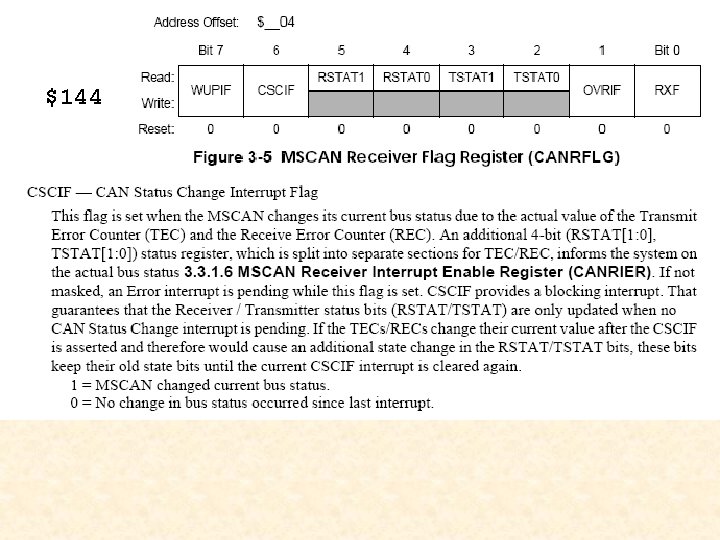

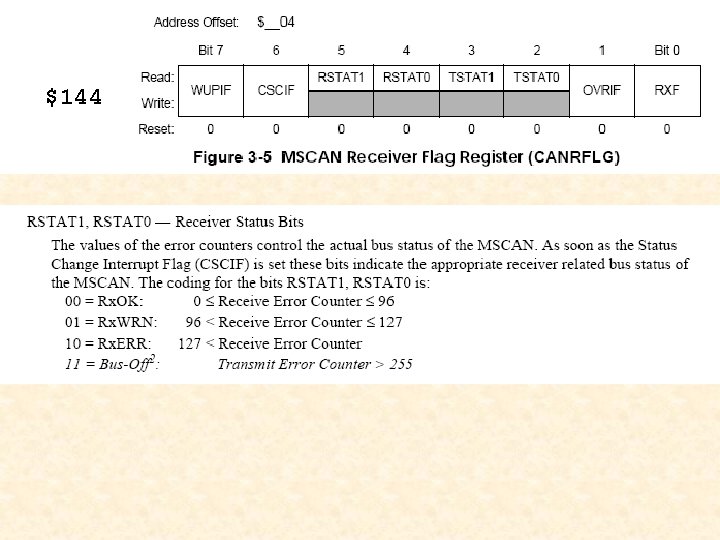

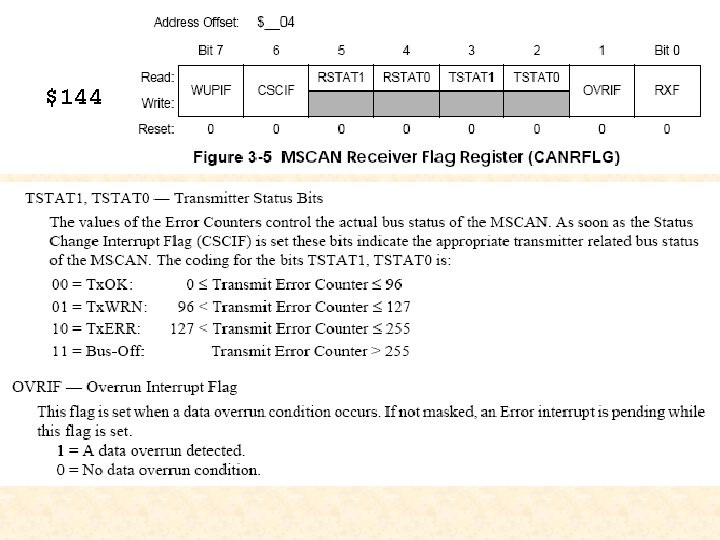

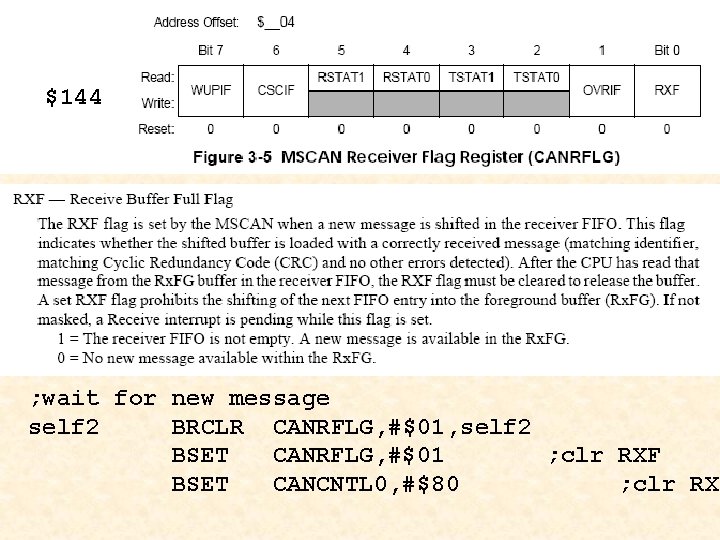

$144

$144

$144

$144

$144 ; wait for new message self 2 BRCLR CANRFLG, #$01, self 2 BSET CANRFLG, #$01 ; clr RXF BSET CANCNTL 0, #$80 ; clr RXF

$140

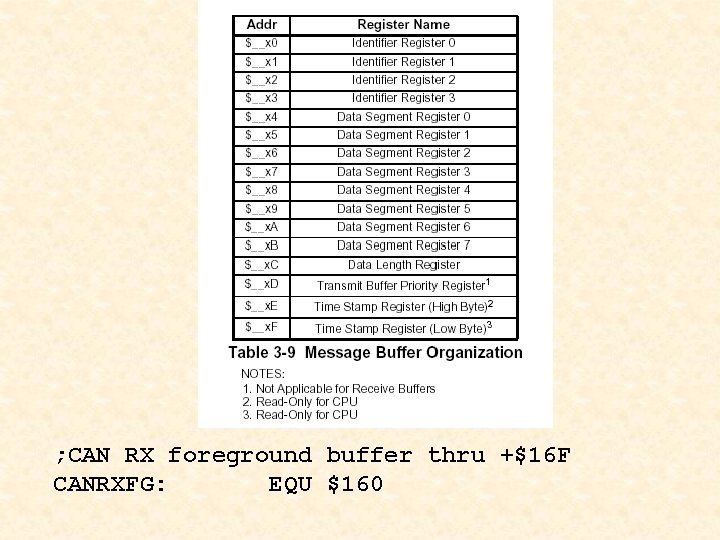

; CAN RX foreground buffer thru +$16 F CANRXFG: EQU $160

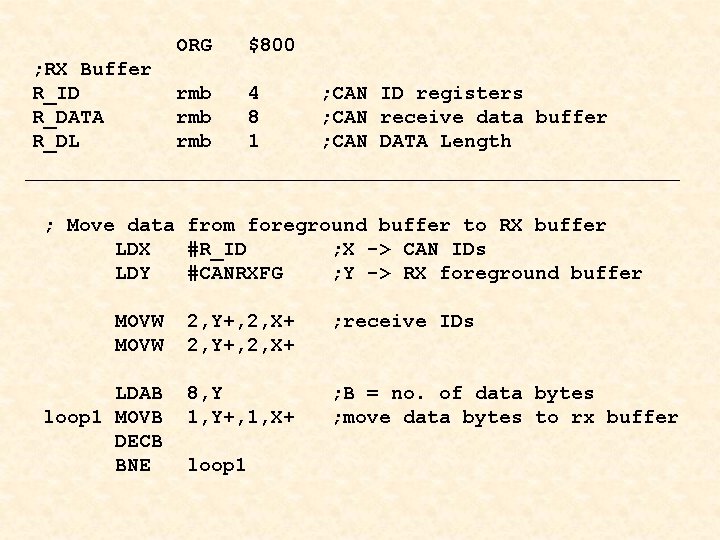

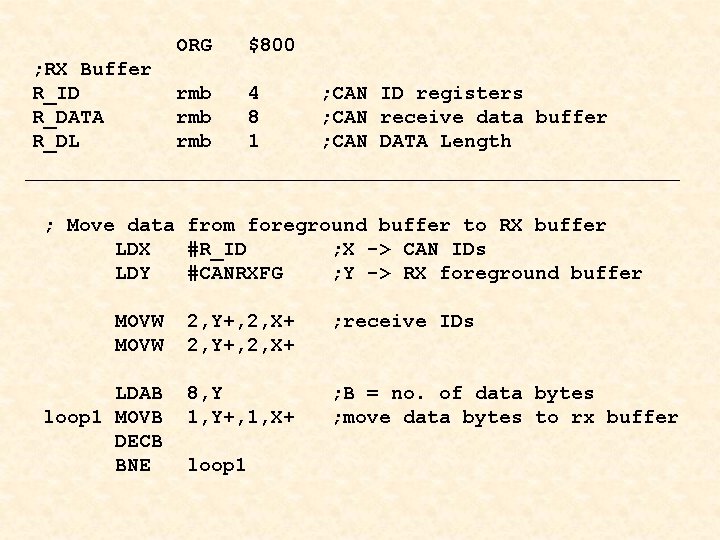

; RX Buffer R_ID R_DATA R_DL ORG $800 rmb rmb 4 8 1 ; CAN ID registers ; CAN receive data buffer ; CAN DATA Length ; Move data from foreground buffer to RX buffer LDX #R_ID ; X -> CAN IDs LDY #CANRXFG ; Y -> RX foreground buffer MOVW 2, Y+, 2, X+ ; receive IDs LDAB loop 1 MOVB DECB BNE 8, Y 1, Y+, 1, X+ ; B = no. of data bytes ; move data bytes to rx buffer loop 1

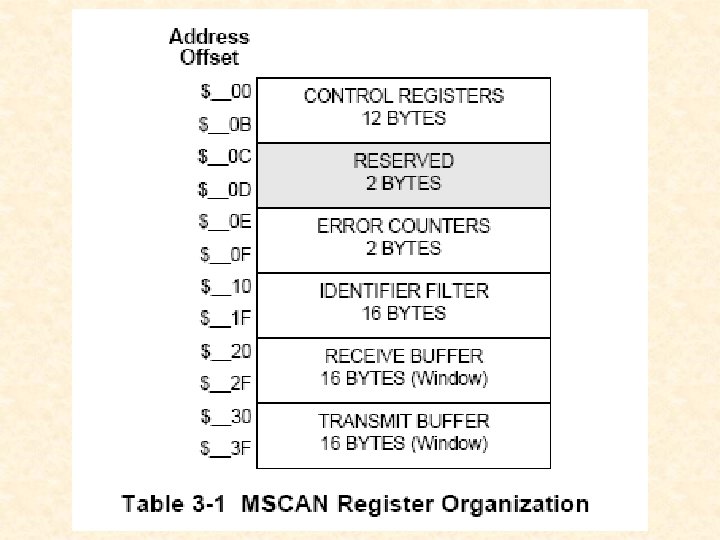

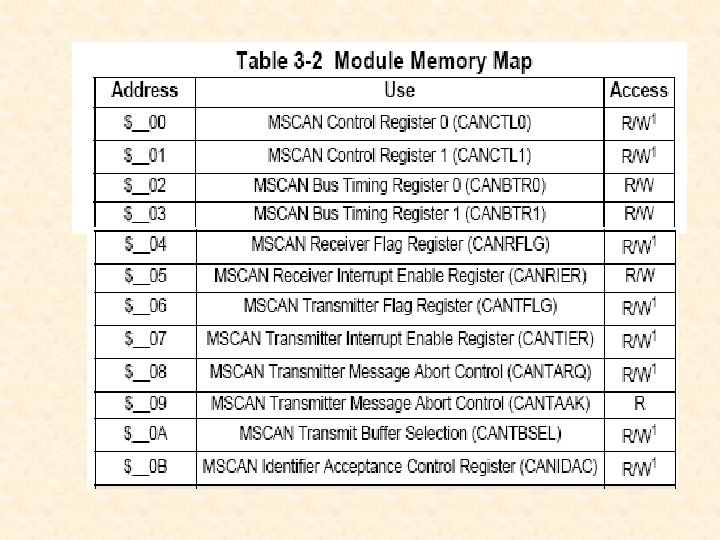

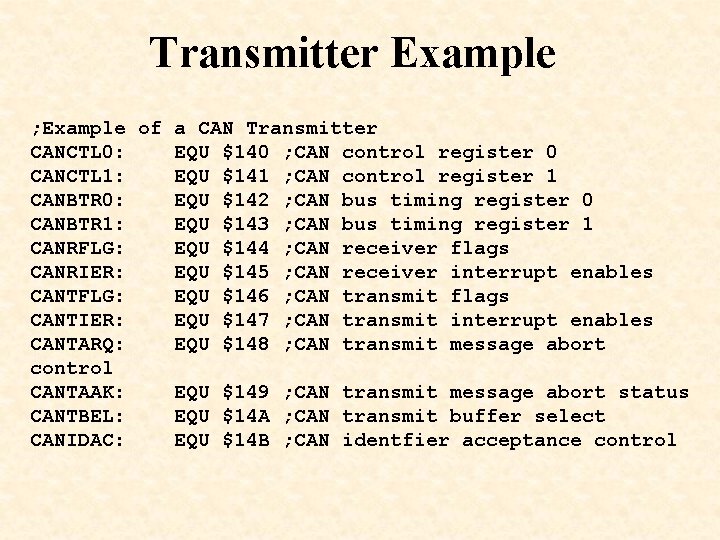

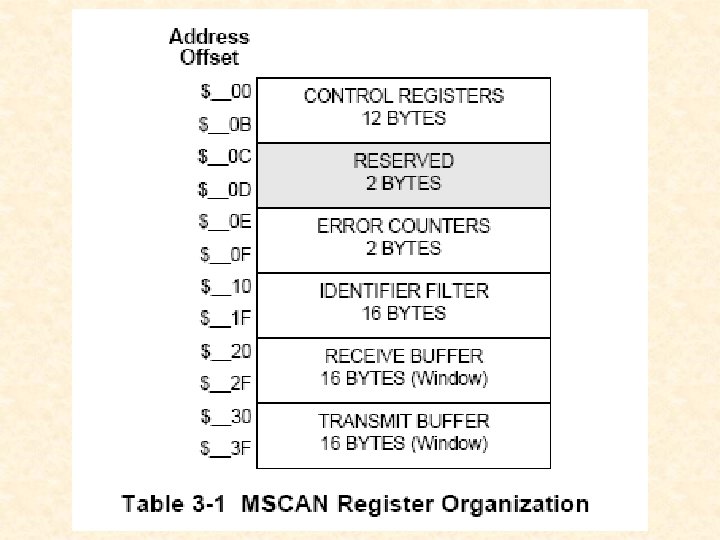

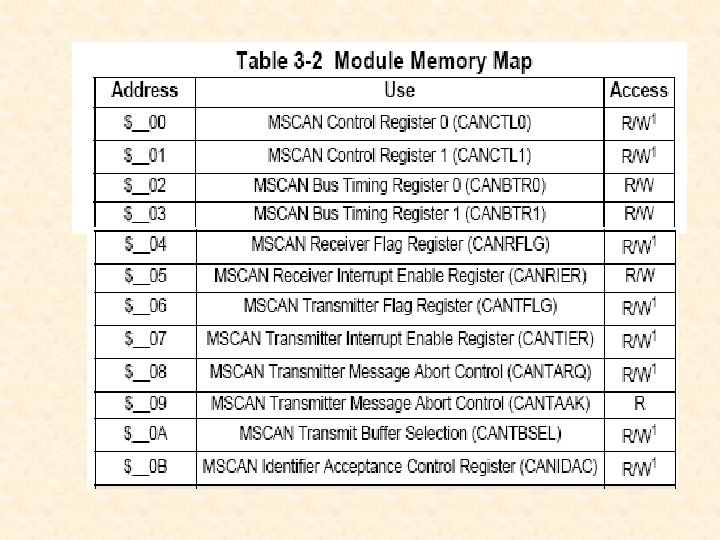

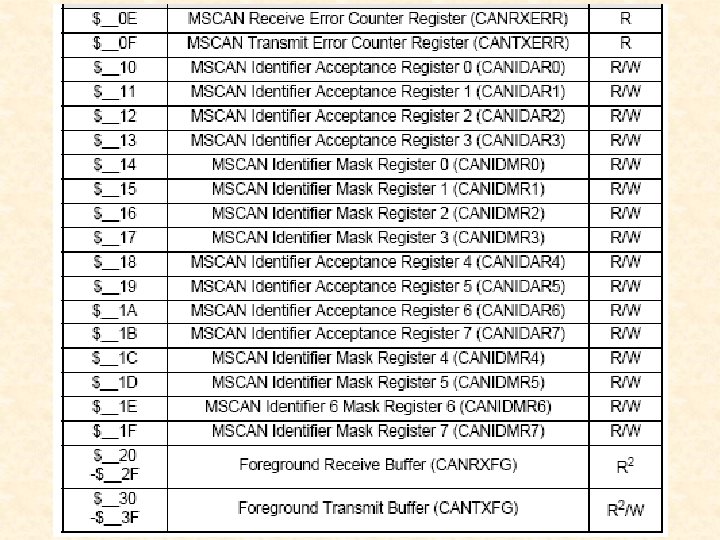

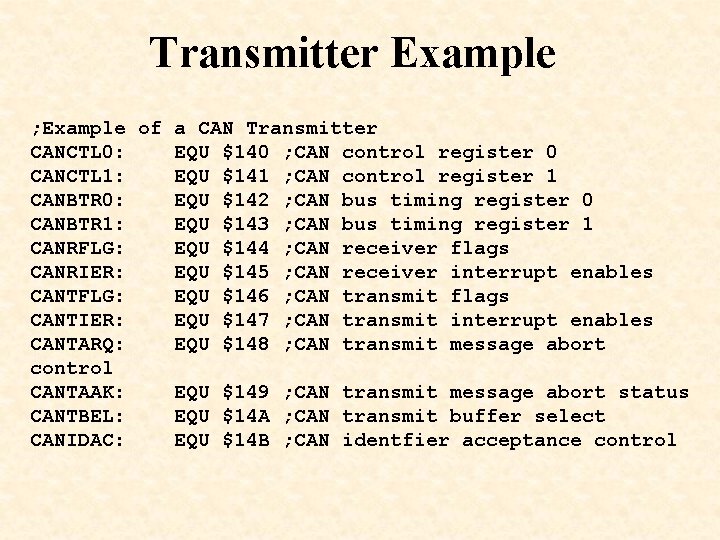

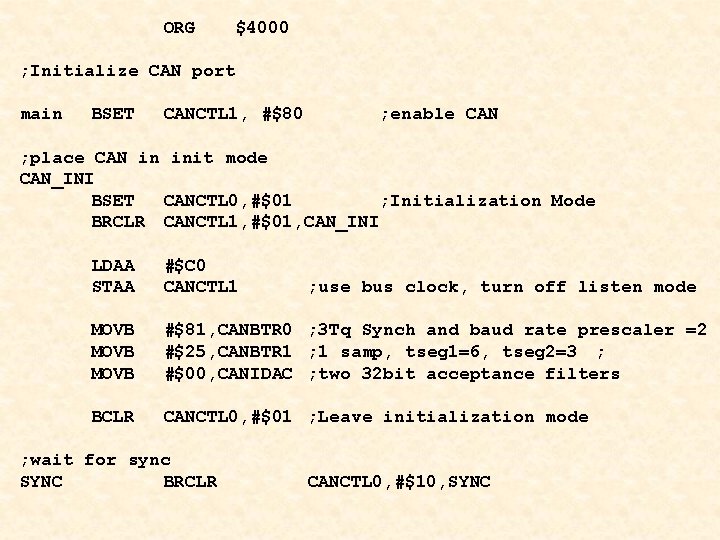

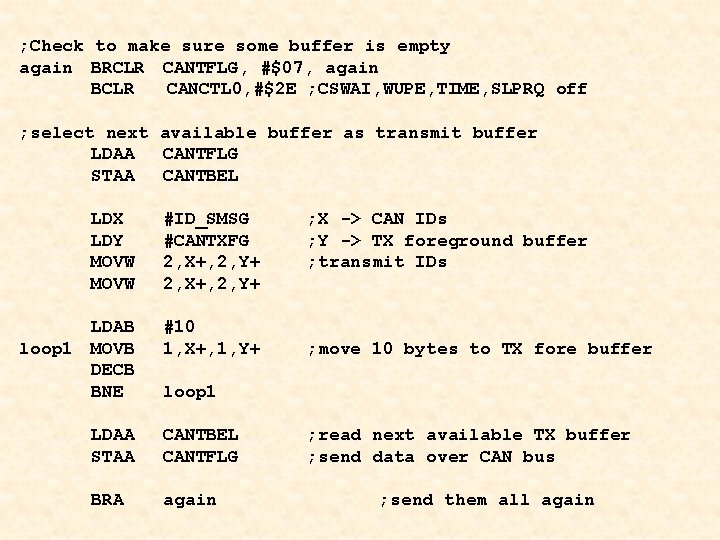

Transmitter Example ; Example of a CAN Transmitter CANCTL 0: EQU $140 ; CAN control register 0 CANCTL 1: EQU $141 ; CAN control register 1 CANBTR 0: EQU $142 ; CAN bus timing register 0 CANBTR 1: EQU $143 ; CAN bus timing register 1 CANRFLG: EQU $144 ; CAN receiver flags CANRIER: EQU $145 ; CAN receiver interrupt enables CANTFLG: EQU $146 ; CAN transmit flags CANTIER: EQU $147 ; CAN transmit interrupt enables CANTARQ: EQU $148 ; CAN transmit message abort control CANTAAK: EQU $149 ; CAN transmit message abort status CANTBEL: EQU $14 A ; CAN transmit buffer select CANIDAC: EQU $14 B ; CAN identfier acceptance control

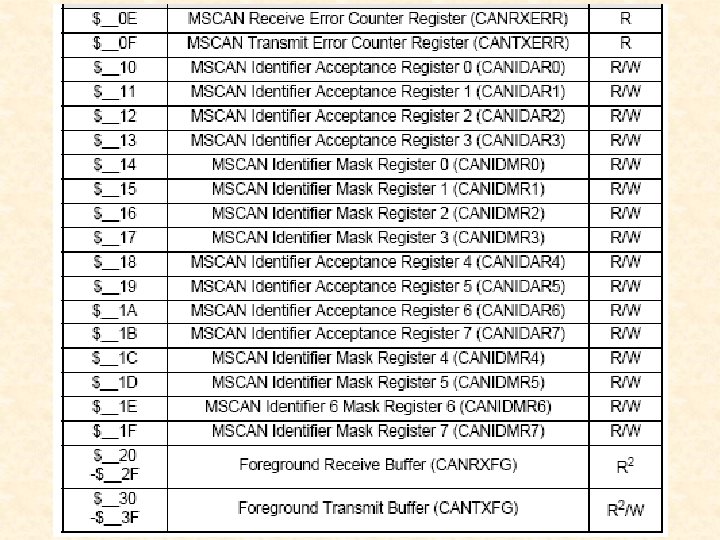

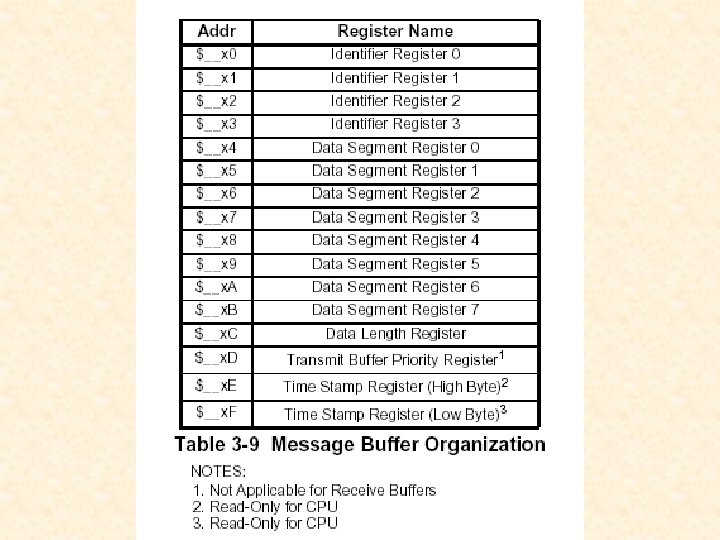

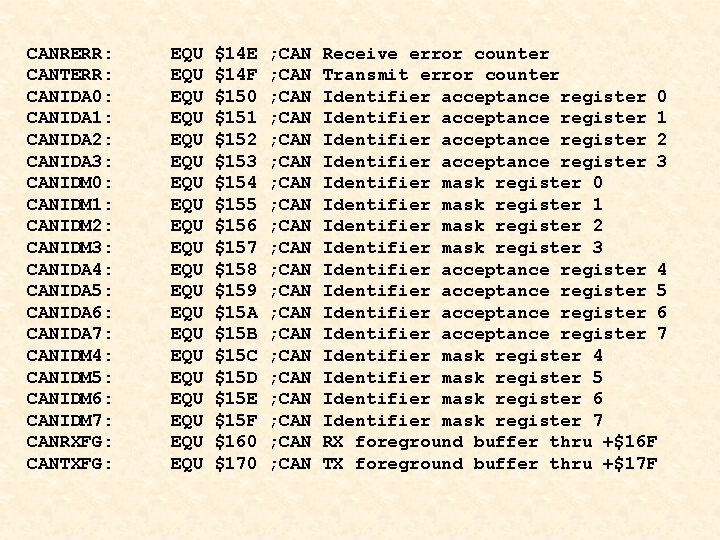

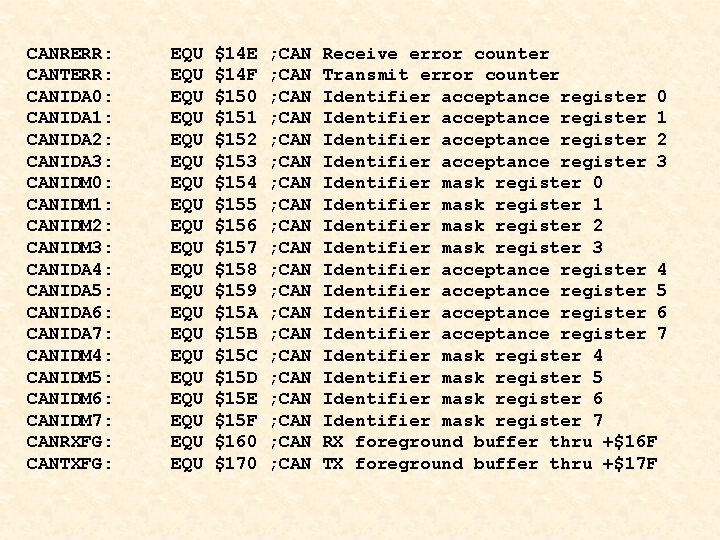

CANRERR: CANTERR: CANIDA 0: CANIDA 1: CANIDA 2: CANIDA 3: CANIDM 0: CANIDM 1: CANIDM 2: CANIDM 3: CANIDA 4: CANIDA 5: CANIDA 6: CANIDA 7: CANIDM 4: CANIDM 5: CANIDM 6: CANIDM 7: CANRXFG: CANTXFG: EQU EQU EQU EQU EQU $14 E $14 F $150 $151 $152 $153 $154 $155 $156 $157 $158 $159 $15 A $15 B $15 C $15 D $15 E $15 F $160 $170 ; CAN ; CAN ; CAN ; CAN ; CAN Receive error counter Transmit error counter Identifier acceptance register 0 Identifier acceptance register 1 Identifier acceptance register 2 Identifier acceptance register 3 Identifier mask register 0 Identifier mask register 1 Identifier mask register 2 Identifier mask register 3 Identifier acceptance register 4 Identifier acceptance register 5 Identifier acceptance register 6 Identifier acceptance register 7 Identifier mask register 4 Identifier mask register 5 Identifier mask register 6 Identifier mask register 7 RX foreground buffer thru +$16 F TX foreground buffer thru +$17 F

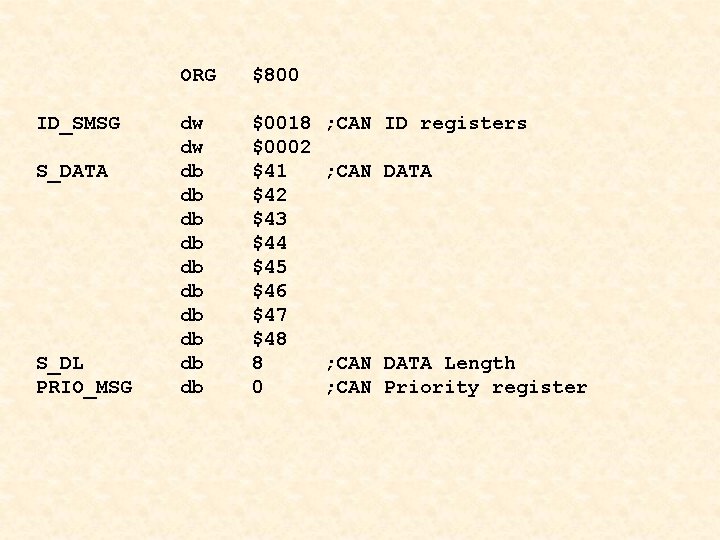

ID_SMSG S_DATA S_DL PRIO_MSG ORG $800 dw dw db db db $0018 $0002 $41 $42 $43 $44 $45 $46 $47 $48 8 0 ; CAN ID registers ; CAN DATA Length ; CAN Priority register

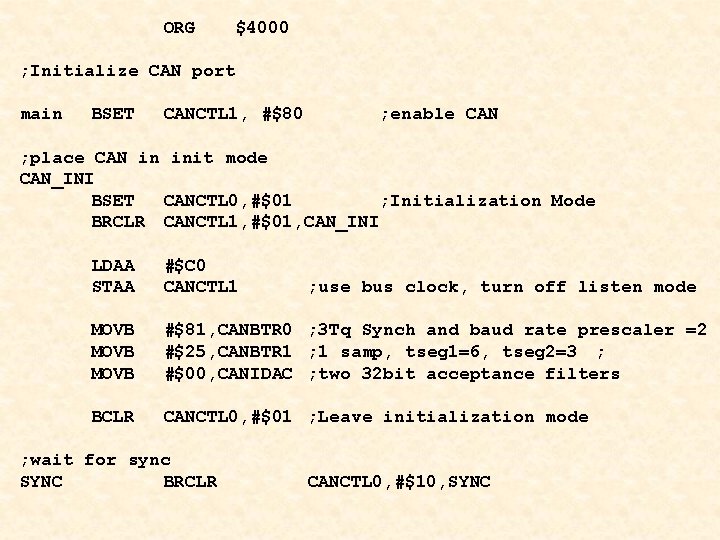

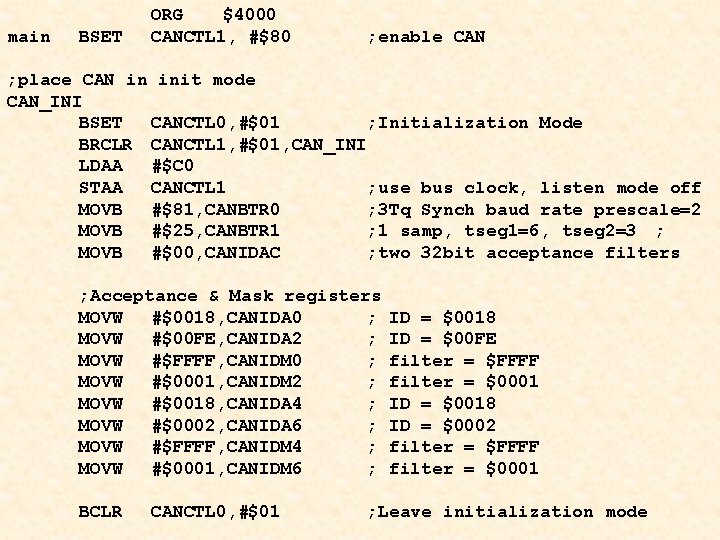

ORG $4000 ; Initialize CAN port main BSET CANCTL 1, #$80 ; enable CAN ; place CAN in init mode CAN_INI BSET CANCTL 0, #$01 ; Initialization Mode BRCLR CANCTL 1, #$01, CAN_INI LDAA STAA #$C 0 CANCTL 1 MOVB #$81, CANBTR 0 ; 3 Tq Synch and baud rate prescaler =2 #$25, CANBTR 1 ; 1 samp, tseg 1=6, tseg 2=3 ; #$00, CANIDAC ; two 32 bit acceptance filters BCLR CANCTL 0, #$01 ; Leave initialization mode ; wait for sync SYNC BRCLR ; use bus clock, turn off listen mode CANCTL 0, #$10, SYNC

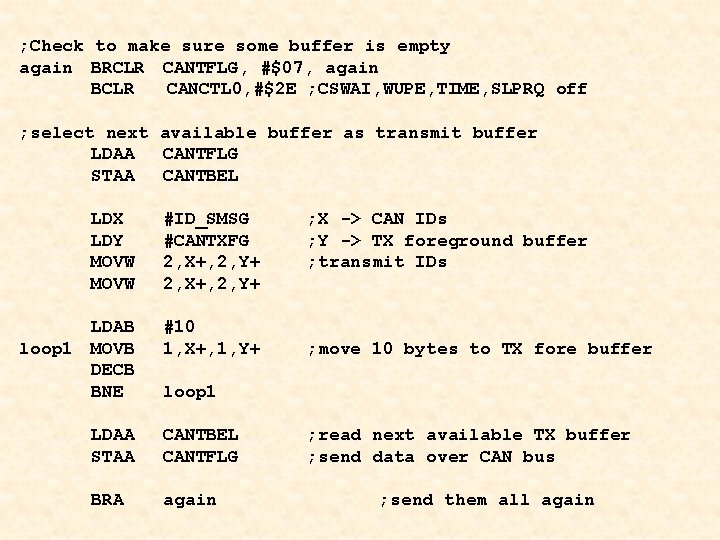

; Check to make sure some buffer is empty again BRCLR CANTFLG, #$07, again BCLR CANCTL 0, #$2 E ; CSWAI, WUPE, TIME, SLPRQ off ; select next available buffer as transmit buffer LDAA CANTFLG STAA CANTBEL loop 1 LDX LDY MOVW #ID_SMSG #CANTXFG 2, X+, 2, Y+ LDAB MOVB DECB BNE #10 1, X+, 1, Y+ LDAA STAA CANTBEL CANTFLG BRA again ; X -> CAN IDs ; Y -> TX foreground buffer ; transmit IDs ; move 10 bytes to TX fore buffer loop 1 ; read next available TX buffer ; send data over CAN bus ; send them all again

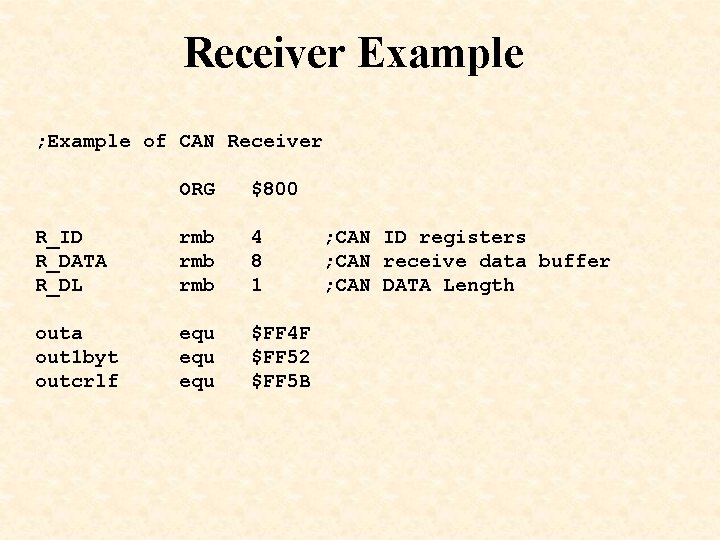

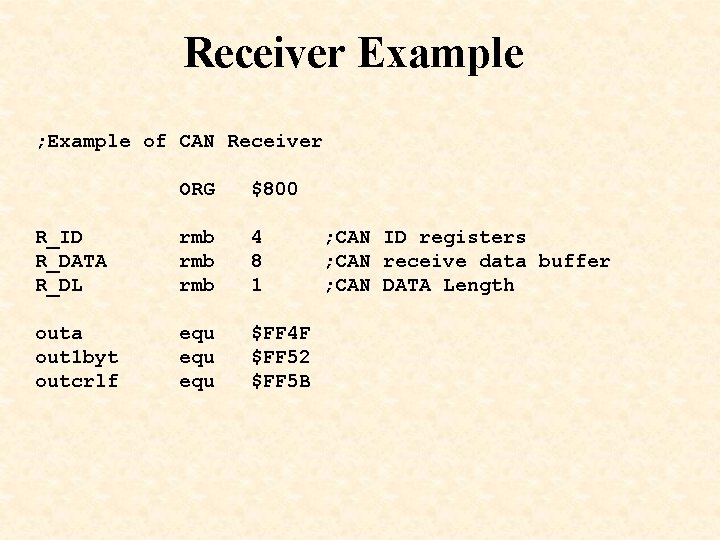

Receiver Example ; Example of CAN Receiver ORG $800 R_ID R_DATA R_DL rmb rmb 4 8 1 outa out 1 byt outcrlf equ equ $FF 4 F $FF 52 $FF 5 B ; CAN ID registers ; CAN receive data buffer ; CAN DATA Length

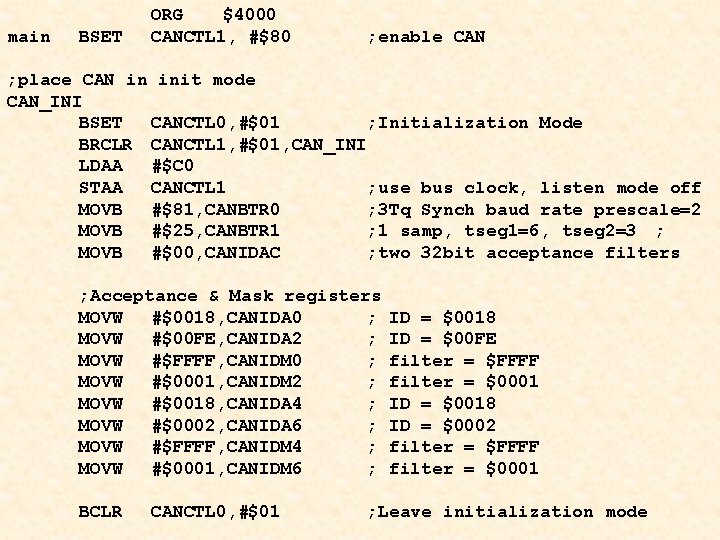

main BSET ORG $4000 CANCTL 1, #$80 ; enable CAN ; place CAN in init mode CAN_INI BSET CANCTL 0, #$01 ; Initialization Mode BRCLR CANCTL 1, #$01, CAN_INI LDAA #$C 0 STAA CANCTL 1 ; use bus clock, listen mode off MOVB #$81, CANBTR 0 ; 3 Tq Synch baud rate prescale=2 MOVB #$25, CANBTR 1 ; 1 samp, tseg 1=6, tseg 2=3 ; MOVB #$00, CANIDAC ; two 32 bit acceptance filters ; Acceptance & Mask registers MOVW #$0018, CANIDA 0 ; MOVW #$00 FE, CANIDA 2 ; MOVW #$FFFF, CANIDM 0 ; MOVW #$0001, CANIDM 2 ; MOVW #$0018, CANIDA 4 ; MOVW #$0002, CANIDA 6 ; MOVW #$FFFF, CANIDM 4 ; MOVW #$0001, CANIDM 6 ; BCLR CANCTL 0, #$01 ID = $0018 ID = $00 FE filter = $FFFF filter = $0001 ID = $0018 ID = $0002 filter = $FFFF filter = $0001 ; Leave initialization mode

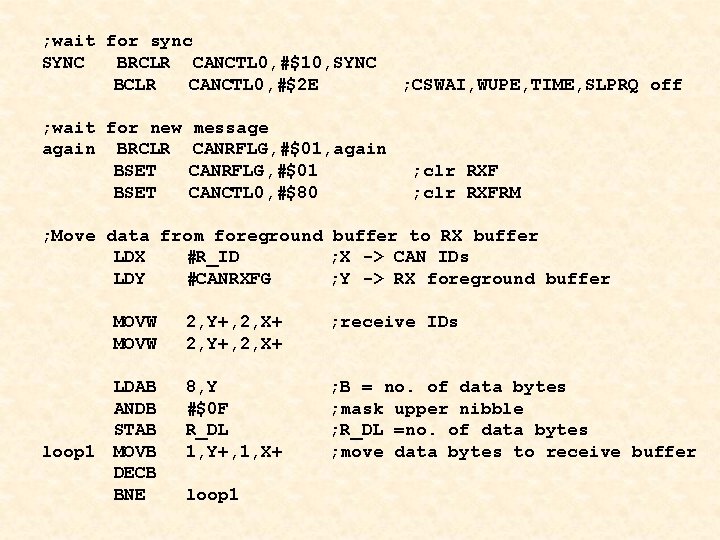

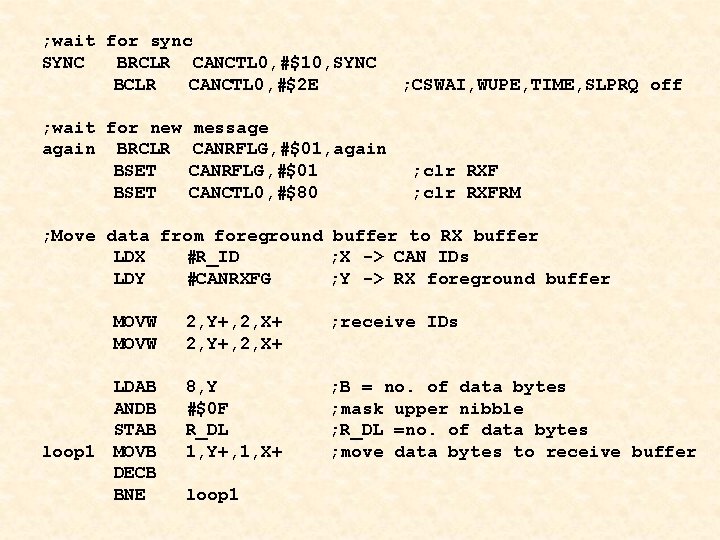

; wait for sync SYNC BRCLR CANCTL 0, #$10, SYNC BCLR CANCTL 0, #$2 E ; wait for new again BRCLR BSET message CANRFLG, #$01, again CANRFLG, #$01 CANCTL 0, #$80 ; CSWAI, WUPE, TIME, SLPRQ off ; clr RXFRM ; Move data from foreground buffer to RX buffer LDX #R_ID ; X -> CAN IDs LDY #CANRXFG ; Y -> RX foreground buffer loop 1 MOVW 2, Y+, 2, X+ ; receive IDs LDAB ANDB STAB MOVB DECB BNE 8, Y #$0 F R_DL 1, Y+, 1, X+ ; B = no. of data bytes ; mask upper nibble ; R_DL =no. of data bytes ; move data bytes to receive buffer loop 1

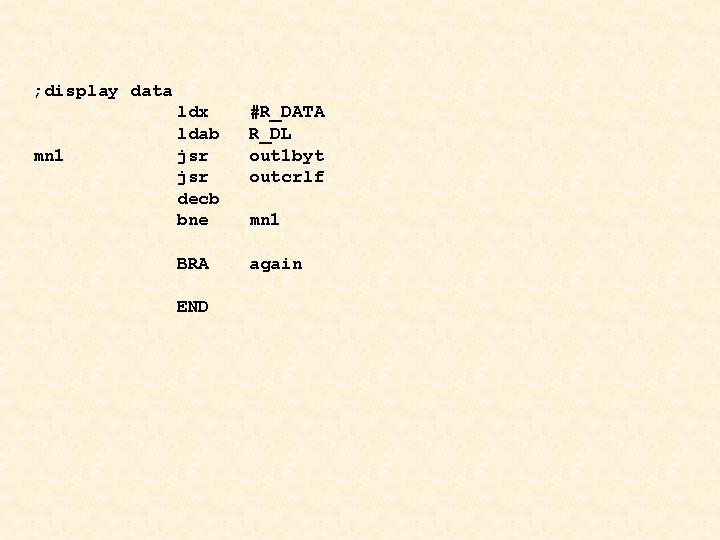

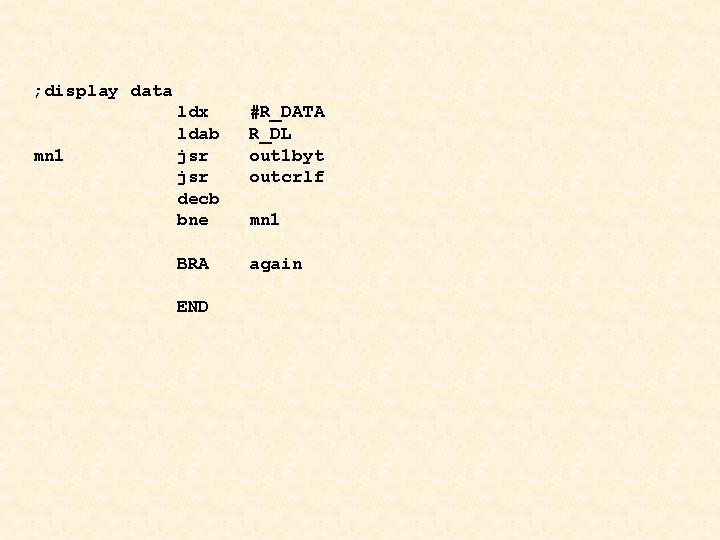

; display data mn 1 ldx ldab jsr decb bne #R_DATA R_DL out 1 byt outcrlf BRA again END mn 1