Control signals ALU Control Assume ALUOp has been

Control signals

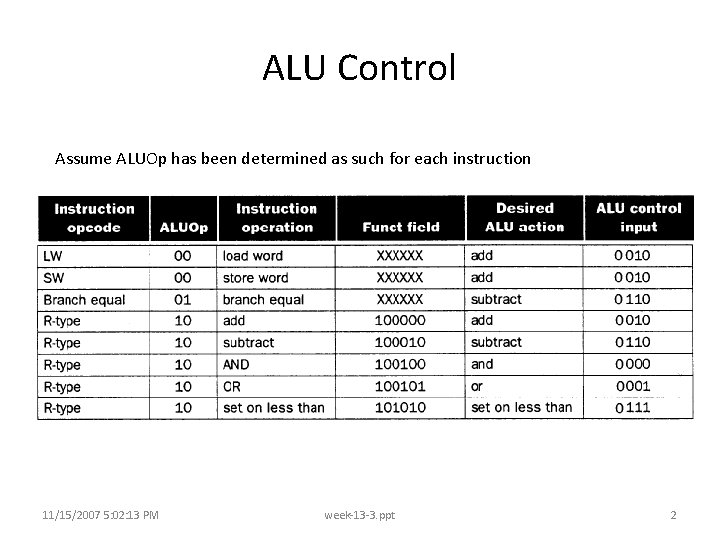

ALU Control Assume ALUOp has been determined as such for each instruction 11/15/2007 5: 02: 13 PM week-13 -3. ppt 2

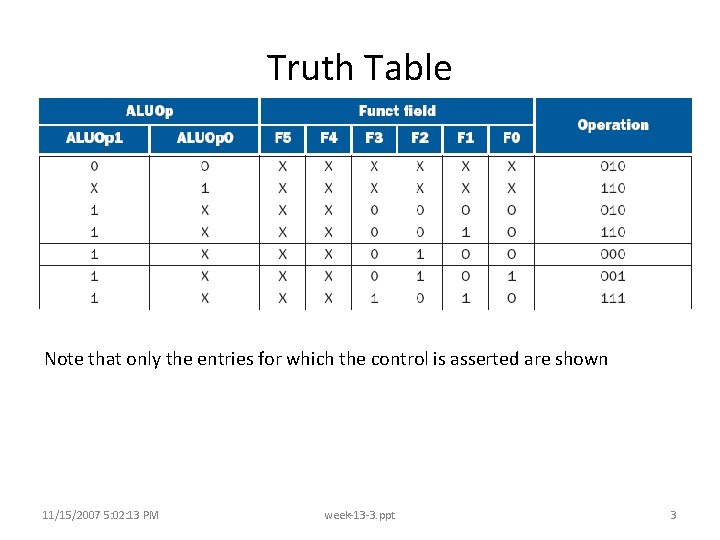

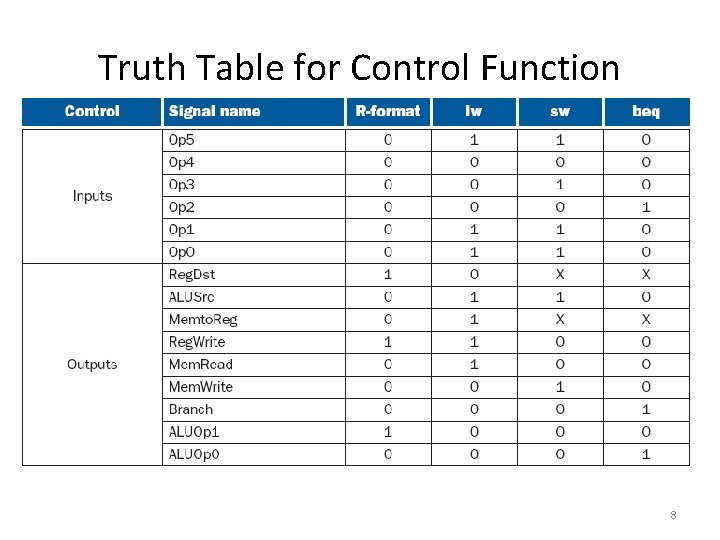

Truth Table Note that only the entries for which the control is asserted are shown 11/15/2007 5: 02: 13 PM week-13 -3. ppt 3

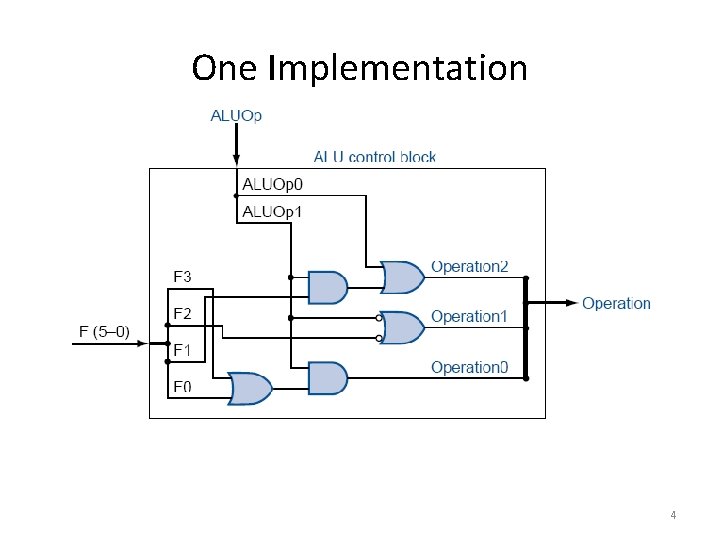

One Implementation 4

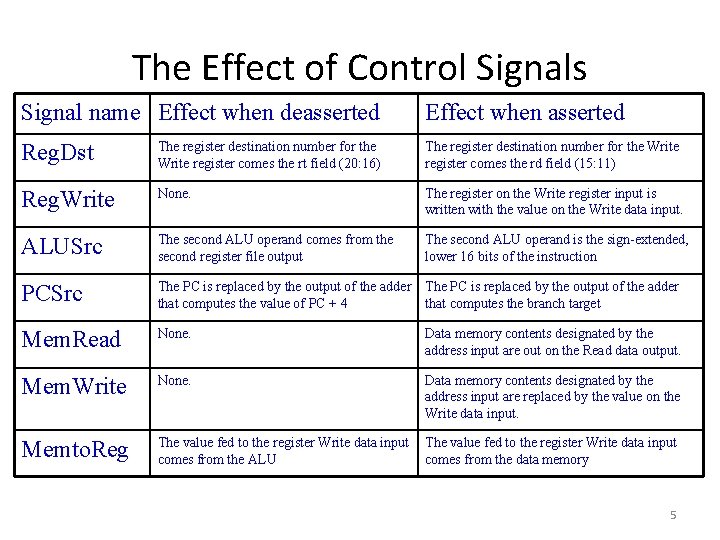

The Effect of Control Signals Signal name Effect when deasserted Effect when asserted Reg. Dst The register destination number for the Write register comes the rt field (20: 16) The register destination number for the Write register comes the rd field (15: 11) Reg. Write None. The register on the Write register input is written with the value on the Write data input. ALUSrc The second ALU operand comes from the second register file output The second ALU operand is the sign-extended, lower 16 bits of the instruction PCSrc The PC is replaced by the output of the adder that computes the value of PC + 4 that computes the branch target Mem. Read None. Data memory contents designated by the address input are out on the Read data output. Mem. Write None. Data memory contents designated by the address input are replaced by the value on the Write data input. Memto. Reg The value fed to the register Write data input comes from the ALU The value fed to the register Write data input comes from the data memory 5

Table for Control Line Setting Instruction R-format Lw Sw beq Reg. Dst ALUSrc Memto. Reg Write Mem Read Mem Write Branch ALUOp 1 ALUOp 0

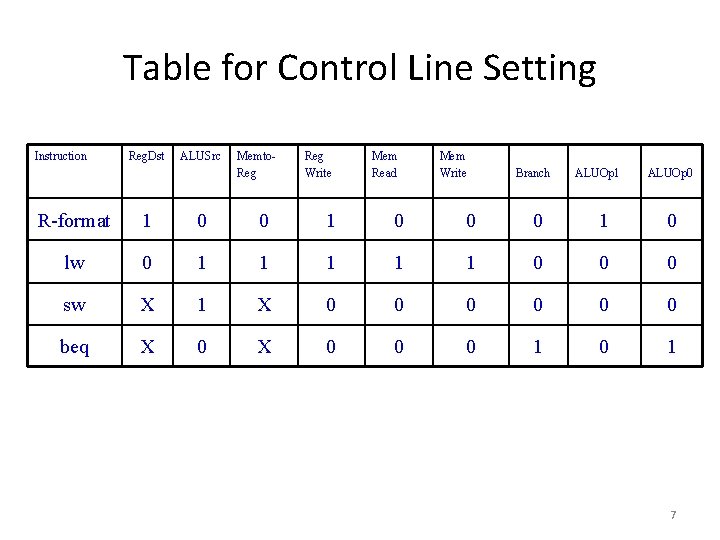

Table for Control Line Setting Instruction Reg. Dst ALUSrc Memto. Reg Write Mem Read Mem Write Branch ALUOp 1 ALUOp 0 R-format 1 0 0 0 1 0 lw 0 1 1 1 0 0 0 sw X 1 X 0 0 0 beq X 0 0 0 1 7

Truth Table for Control Function 8

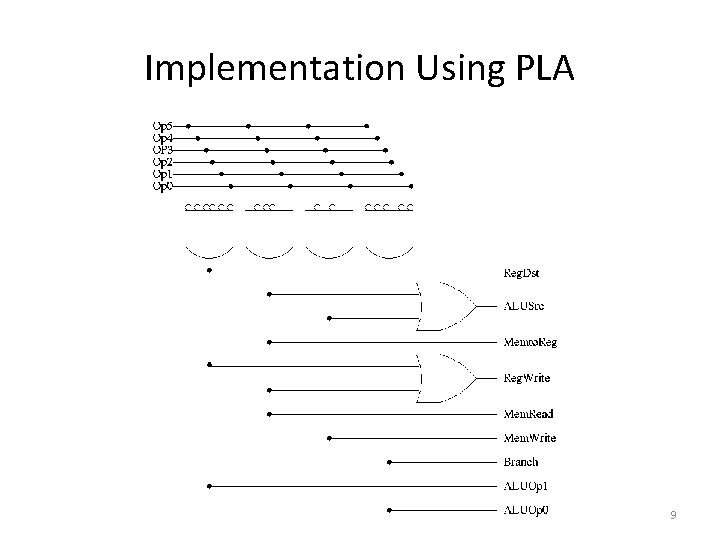

Implementation Using PLA 9

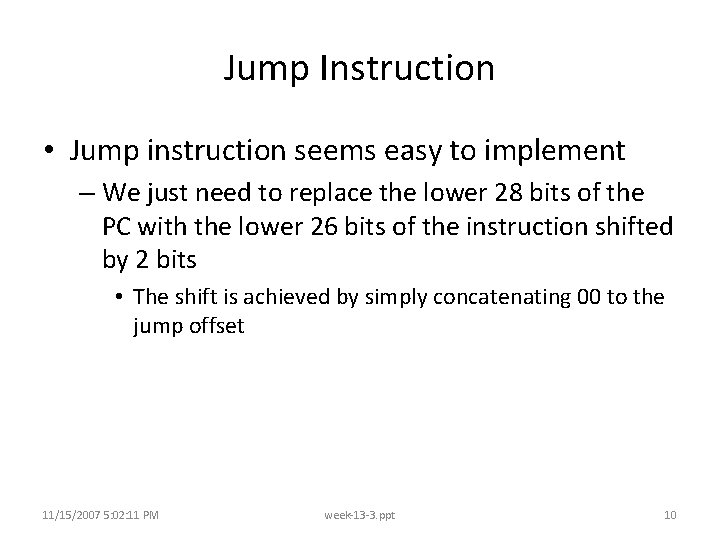

Jump Instruction • Jump instruction seems easy to implement – We just need to replace the lower 28 bits of the PC with the lower 26 bits of the instruction shifted by 2 bits • The shift is achieved by simply concatenating 00 to the jump offset 11/15/2007 5: 02: 11 PM week-13 -3. ppt 10

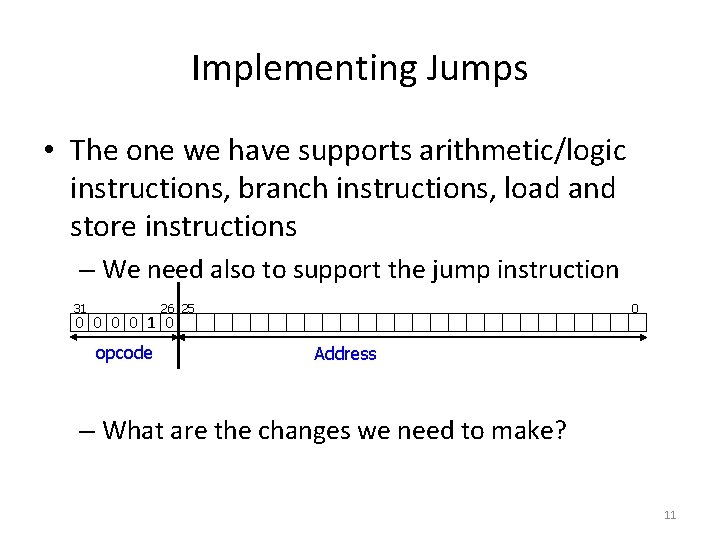

Implementing Jumps • The one we have supports arithmetic/logic instructions, branch instructions, load and store instructions – We need also to support the jump instruction 31 26 25 0 0 0 1 0 opcode Address – What are the changes we need to make? 11

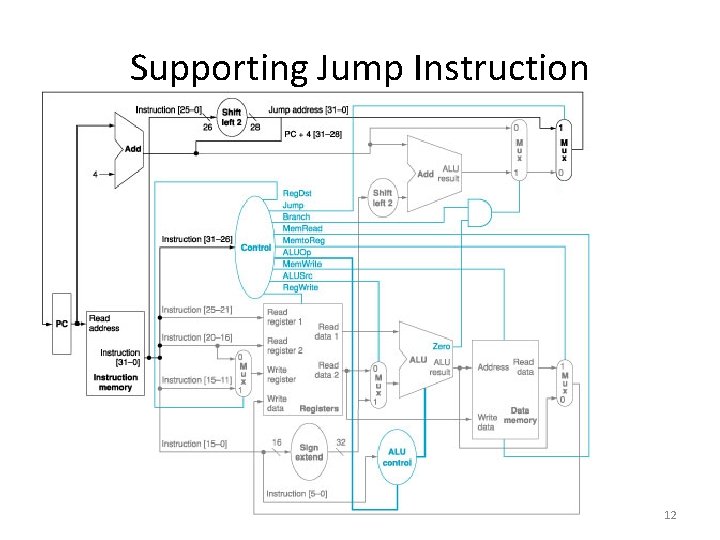

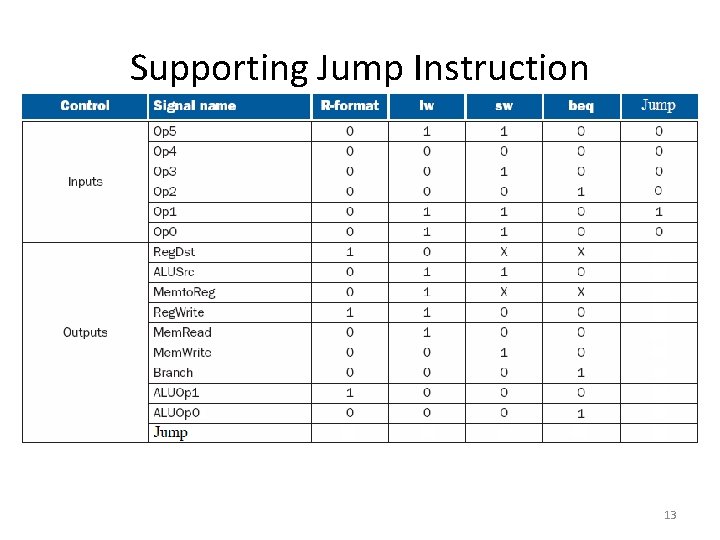

Supporting Jump Instruction 12

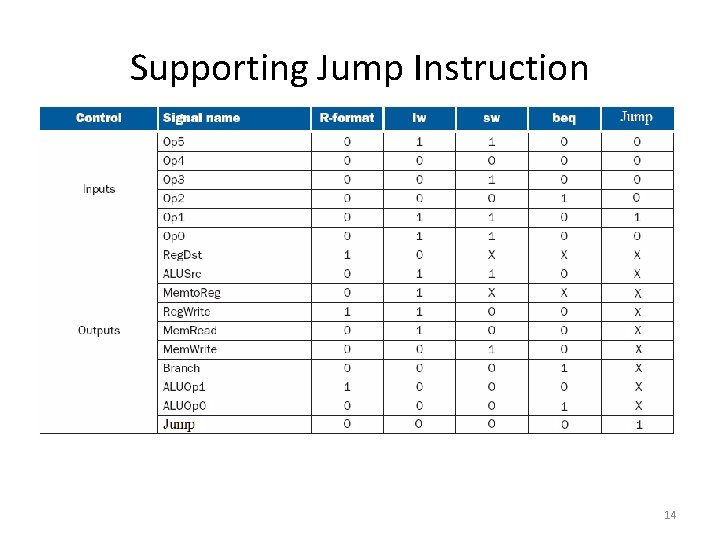

Supporting Jump Instruction 13

Supporting Jump Instruction 14

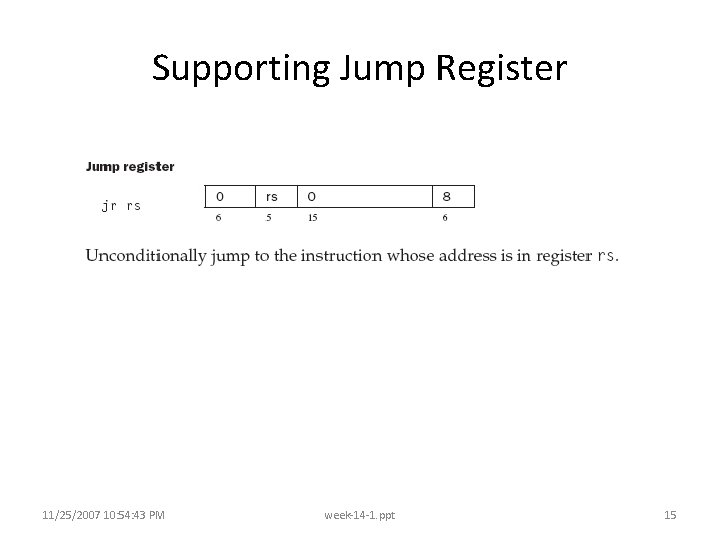

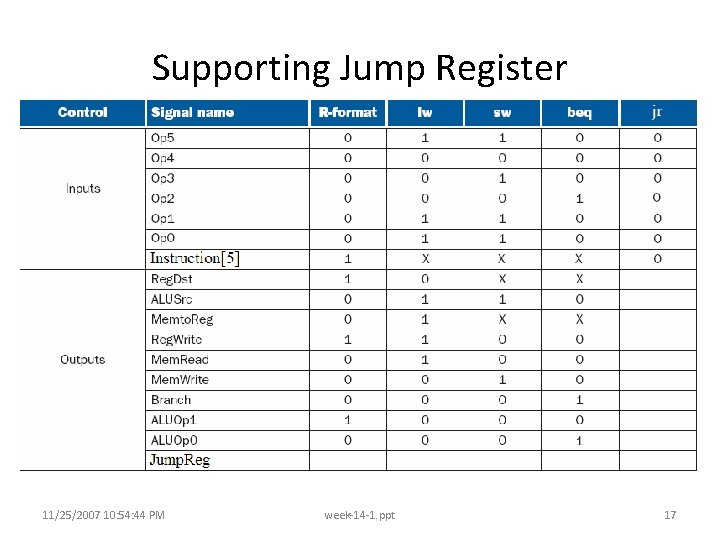

Supporting Jump Register 11/25/2007 10: 54: 43 PM week-14 -1. ppt 15

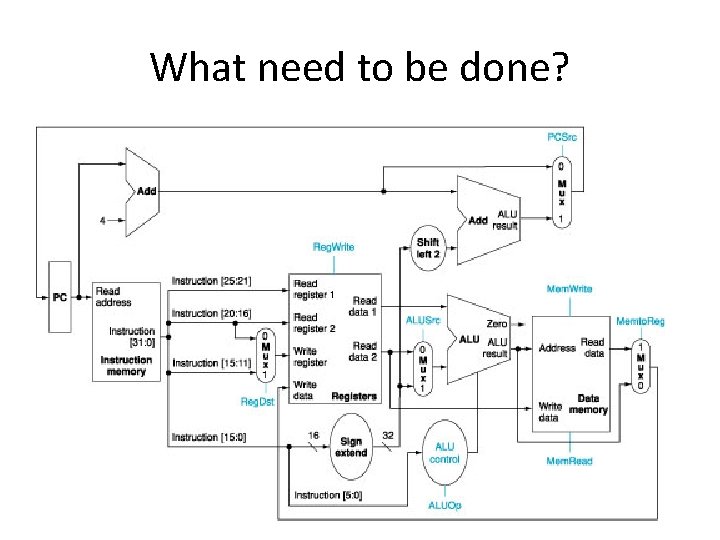

What need to be done?

Supporting Jump Register 11/25/2007 10: 54: 44 PM week-14 -1. ppt 17

Final • Final is going to be on Wednesday between 12: 30 - 2: 30 p. m. , in the same classroom. • It will cover both before the midterm and after the midterm. • It will consist of around 10 multiple choice questions and around 3 short answer questions.

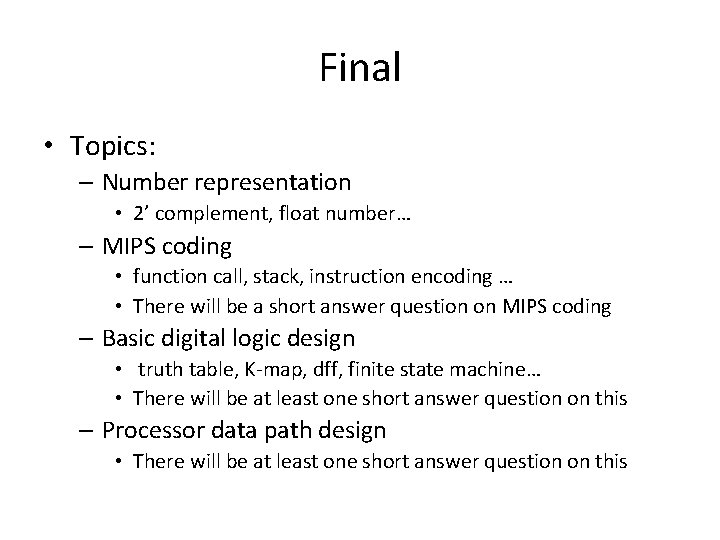

Final • Topics: – Number representation • 2’ complement, float number… – MIPS coding • function call, stack, instruction encoding … • There will be a short answer question on MIPS coding – Basic digital logic design • truth table, K-map, dff, finite state machine… • There will be at least one short answer question on this – Processor data path design • There will be at least one short answer question on this

- Slides: 19