Constructive Computer Architecture Tutorial 3 RISCV Processor Sizhuo

- Slides: 23

Constructive Computer Architecture Tutorial 3 RISC-V Processor Sizhuo Zhang 6. 175 TA Oct 16, 2015 http: //csg. csail. mit. edu/6. 175 T 03 -1

Course Content Oct 16, 2015 http: //csg. csail. mit. edu/6. 175 T 03 -2

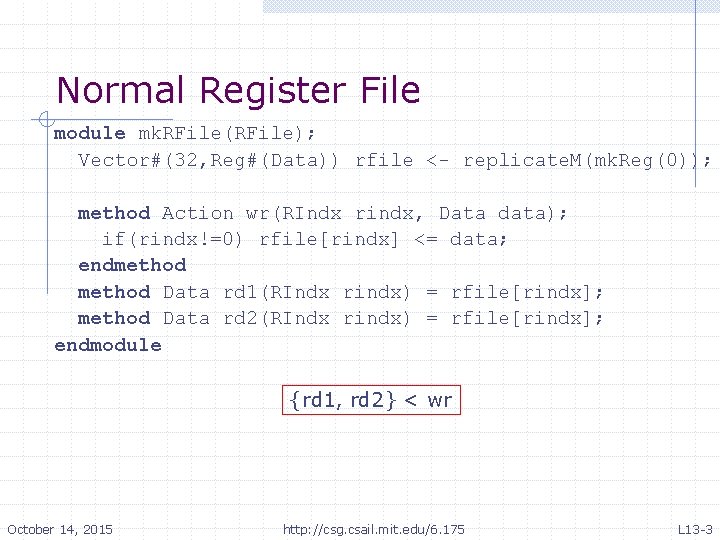

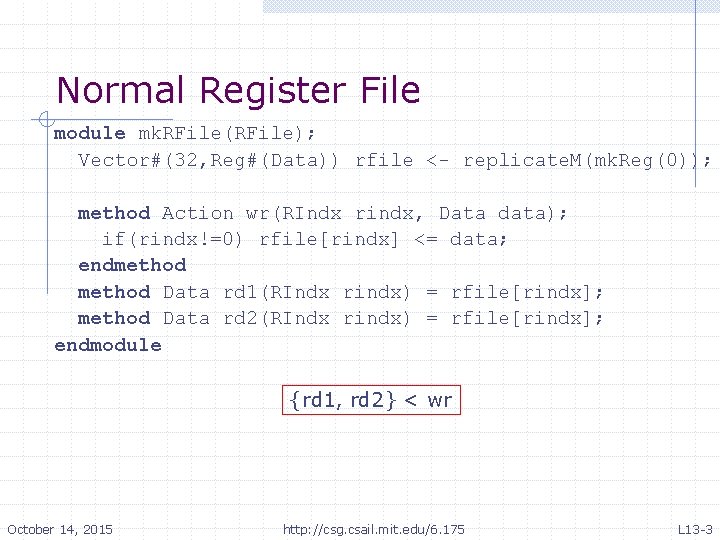

Normal Register File module mk. RFile(RFile); Vector#(32, Reg#(Data)) rfile <- replicate. M(mk. Reg(0)); method Action wr(RIndx rindx, Data data); if(rindx!=0) rfile[rindx] <= data; endmethod Data rd 1(RIndx rindx) = rfile[rindx]; method Data rd 2(RIndx rindx) = rfile[rindx]; endmodule {rd 1, rd 2} < wr October 14, 2015 http: //csg. csail. mit. edu/6. 175 L 13 -3

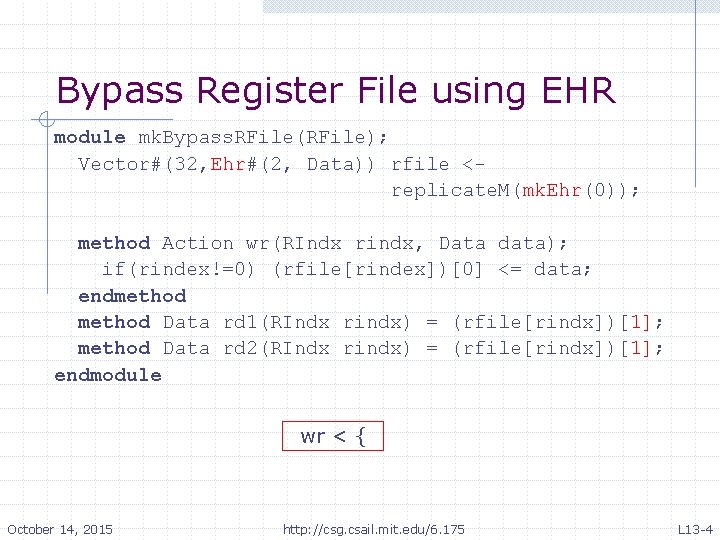

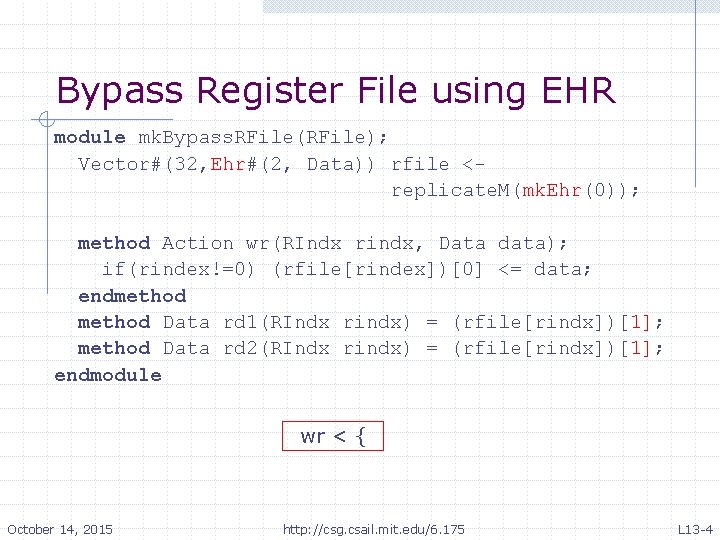

Bypass Register File using EHR module mk. Bypass. RFile(RFile); Vector#(32, Ehr#(2, Data)) rfile < replicate. M(mk. Ehr(0)); method Action wr(RIndx rindx, Data data); if(rindex!=0) (rfile[rindex])[0] <= data; endmethod Data rd 1(RIndx rindx) = (rfile[rindx])[1]; method Data rd 2(RIndx rindx) = (rfile[rindx])[1]; endmodule • wr < { October 14, 2015 http: //csg. csail. mit. edu/6. 175 L 13 -4

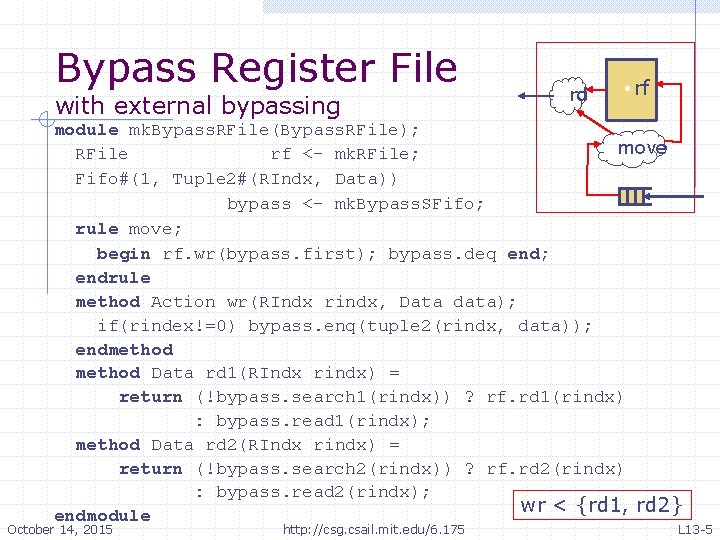

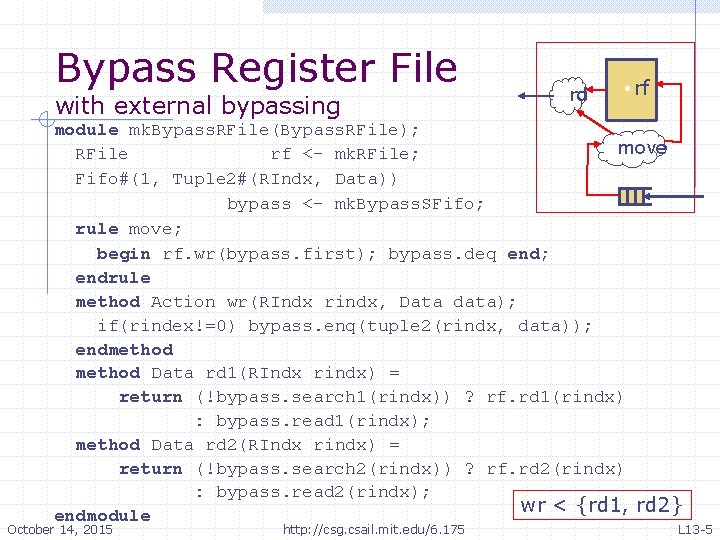

Bypass Register File with external bypassing • rd • rf module mk. Bypass. RFile(Bypass. RFile); • move RFile rf <- mk. RFile; Fifo#(1, Tuple 2#(RIndx, Data)) bypass <- mk. Bypass. SFifo; rule move; begin rf. wr(bypass. first); bypass. deq end; endrule method Action wr(RIndx rindx, Data data); if(rindex!=0) bypass. enq(tuple 2(rindx, data)); endmethod Data rd 1(RIndx rindx) = return (!bypass. search 1(rindx)) ? rf. rd 1(rindx) : bypass. read 1(rindx); method Data rd 2(RIndx rindx) = return (!bypass. search 2(rindx)) ? rf. rd 2(rindx) : bypass. read 2(rindx); wr < {rd 1, rd 2} endmodule October 14, 2015 http: //csg. csail. mit. edu/6. 175 L 13 -5

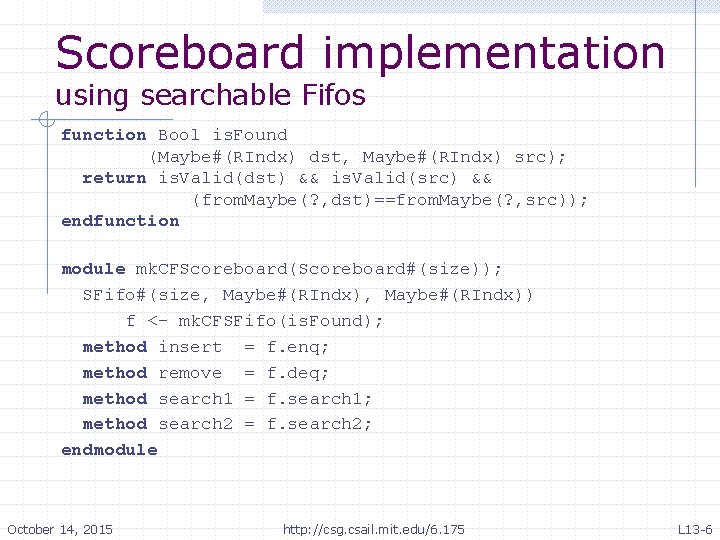

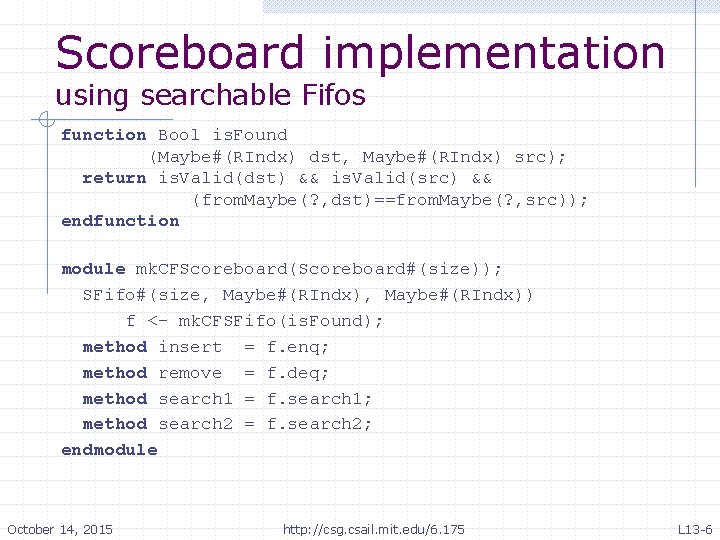

Scoreboard implementation using searchable Fifos function Bool is. Found (Maybe#(RIndx) dst, Maybe#(RIndx) src); return is. Valid(dst) && is. Valid(src) && (from. Maybe(? , dst)==from. Maybe(? , src)); endfunction module mk. CFScoreboard(Scoreboard#(size)); SFifo#(size, Maybe#(RIndx)) f <- mk. CFSFifo(is. Found); method insert = f. enq; method remove = f. deq; method search 1 = f. search 1; method search 2 = f. search 2; endmodule October 14, 2015 http: //csg. csail. mit. edu/6. 175 L 13 -6

Searchable FIFO Code Will see in Lab 6 Oct 16, 2015 http: //csg. csail. mit. edu/6. 175 T 03 -7

RISC-V Processor SCE-MI Infrastructure Oct 16, 2015 http: //csg. csail. mit. edu/6. 175 T 03 -8

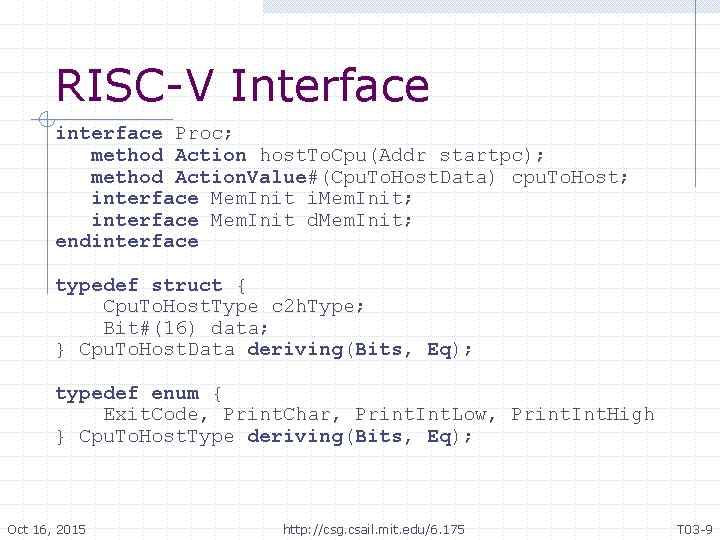

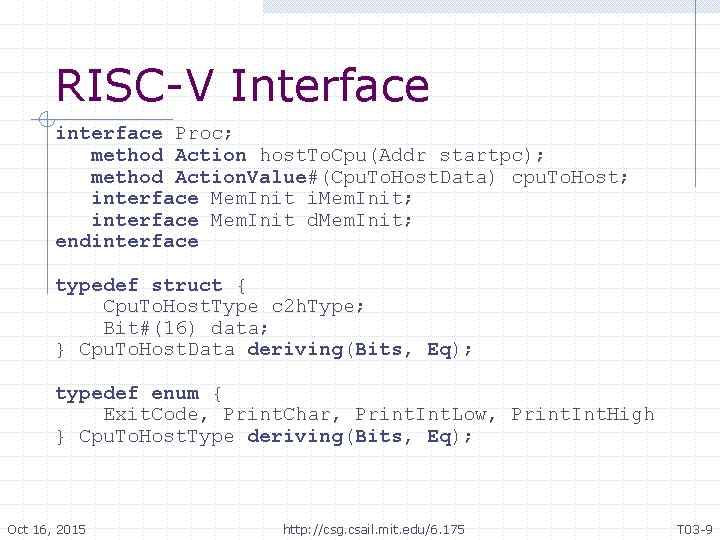

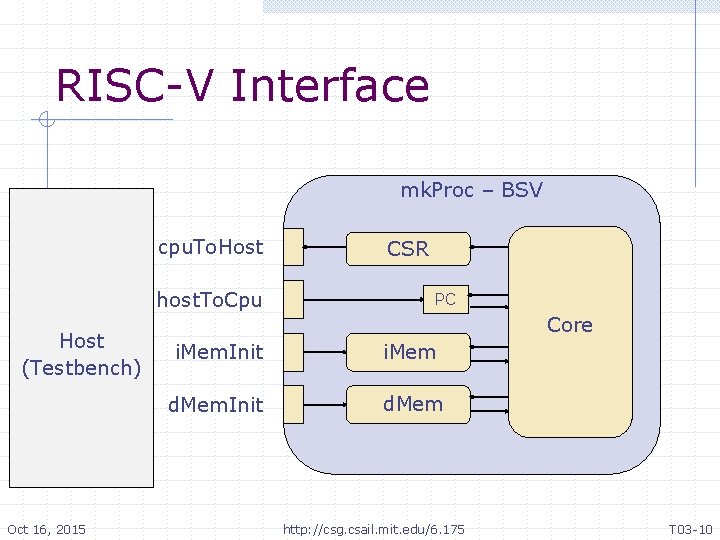

RISC-V Interface interface Proc; method Action host. To. Cpu(Addr startpc); method Action. Value#(Cpu. To. Host. Data) cpu. To. Host; interface Mem. Init i. Mem. Init; interface Mem. Init d. Mem. Init; endinterface typedef struct { Cpu. To. Host. Type c 2 h. Type; Bit#(16) data; } Cpu. To. Host. Data deriving(Bits, Eq); typedef enum { Exit. Code, Print. Char, Print. Int. Low, Print. Int. High } Cpu. To. Host. Type deriving(Bits, Eq); Oct 16, 2015 http: //csg. csail. mit. edu/6. 175 T 03 -9

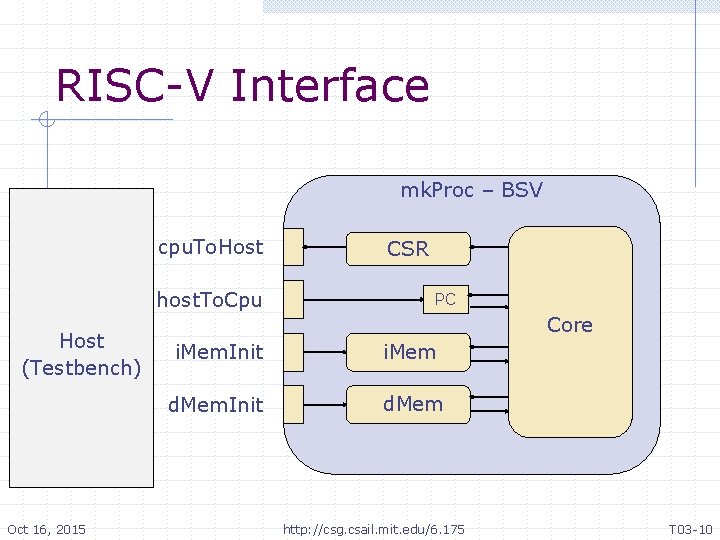

RISC-V Interface mk. Proc – BSV cpu. To. Host host. To. Cpu Host (Testbench) Oct 16, 2015 CSR PC Core i. Mem. Init i. Mem d. Mem. Init d. Mem http: //csg. csail. mit. edu/6. 175 T 03 -10

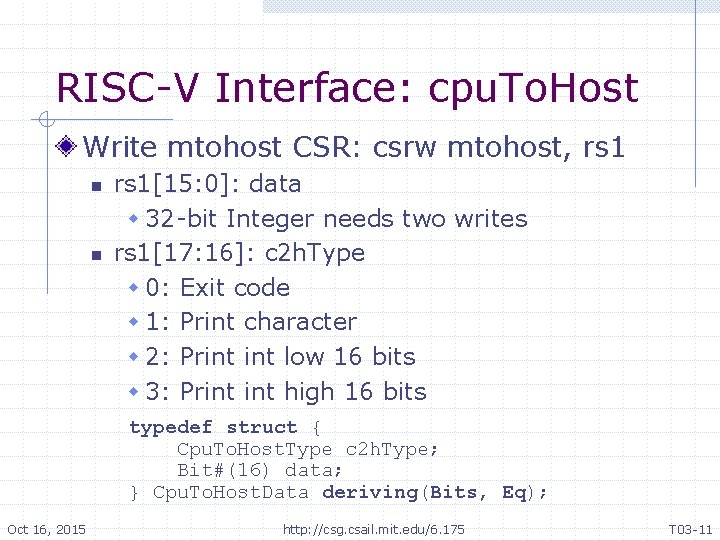

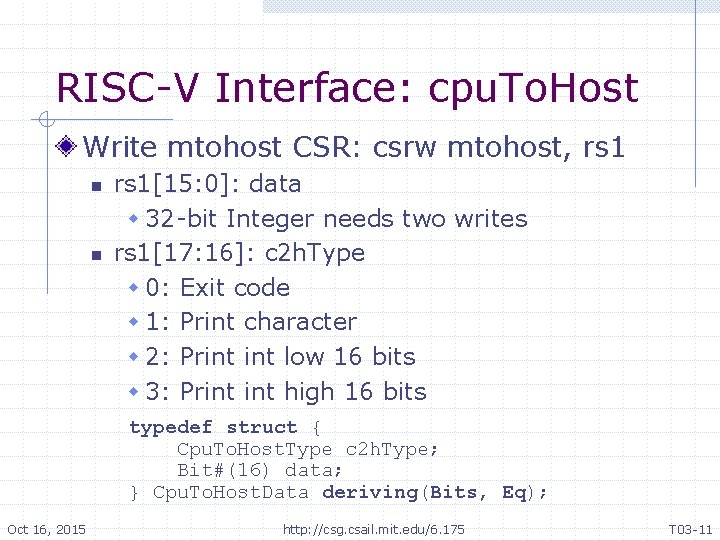

RISC-V Interface: cpu. To. Host Write mtohost CSR: csrw mtohost, rs 1 n n rs 1[15: 0]: data w 32 -bit Integer needs two writes rs 1[17: 16]: c 2 h. Type w 0: Exit code w 1: Print character w 2: Print low 16 bits w 3: Print high 16 bits typedef struct { Cpu. To. Host. Type c 2 h. Type; Bit#(16) data; } Cpu. To. Host. Data deriving(Bits, Eq); Oct 16, 2015 http: //csg. csail. mit. edu/6. 175 T 03 -11

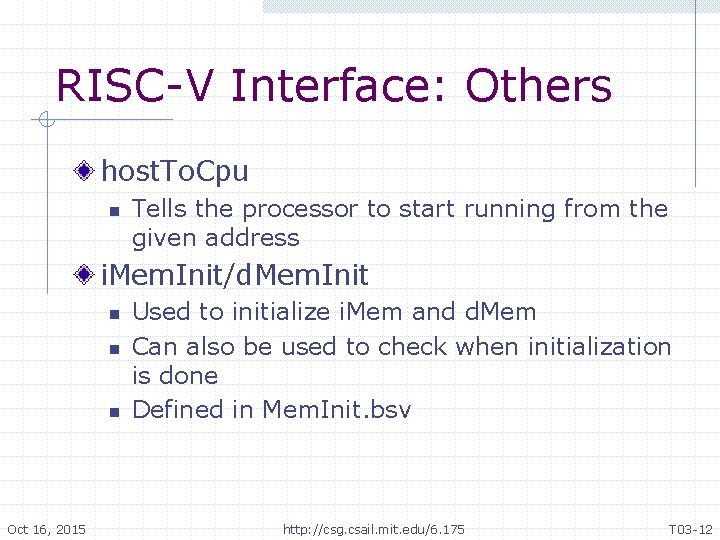

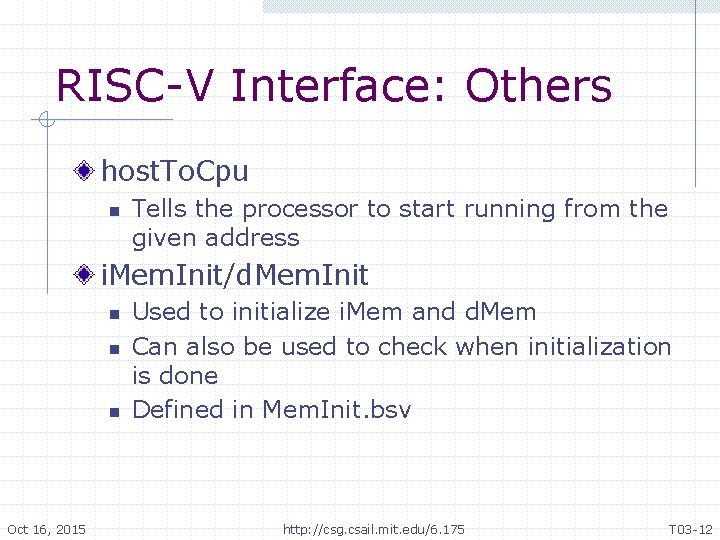

RISC-V Interface: Others host. To. Cpu n Tells the processor to start running from the given address i. Mem. Init/d. Mem. Init n n n Oct 16, 2015 Used to initialize i. Mem and d. Mem Can also be used to check when initialization is done Defined in Mem. Init. bsv http: //csg. csail. mit. edu/6. 175 T 03 -12

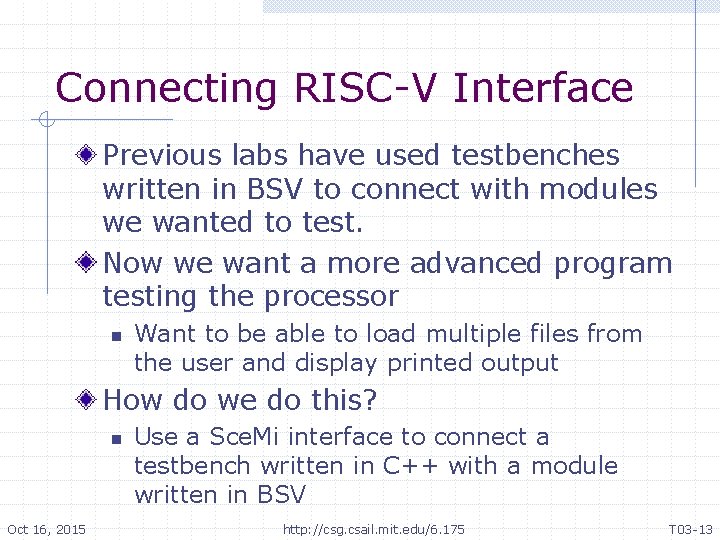

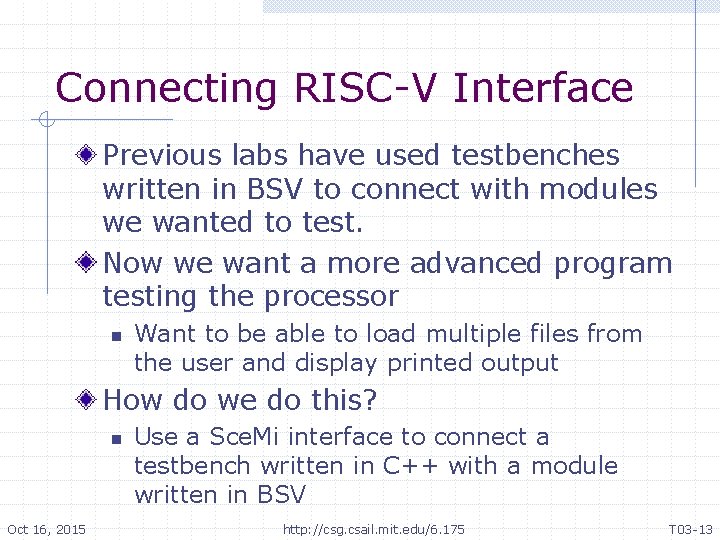

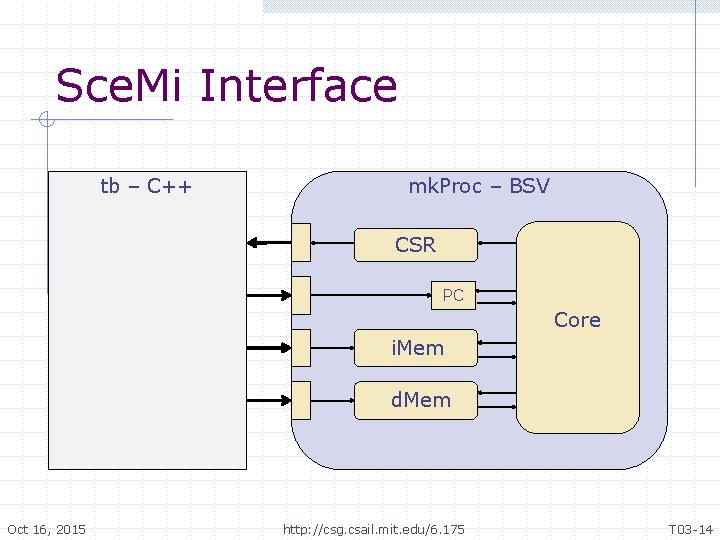

Connecting RISC-V Interface Previous labs have used testbenches written in BSV to connect with modules we wanted to test. Now we want a more advanced program testing the processor n Want to be able to load multiple files from the user and display printed output How do we do this? n Oct 16, 2015 Use a Sce. Mi interface to connect a testbench written in C++ with a module written in BSV http: //csg. csail. mit. edu/6. 175 T 03 -13

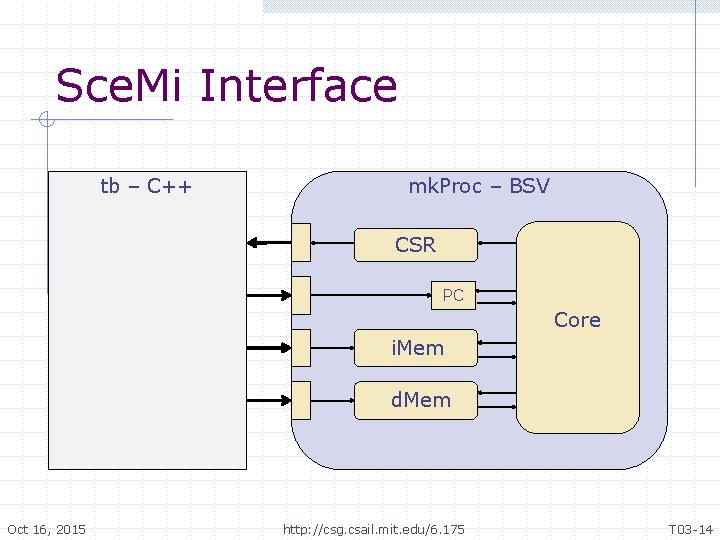

Sce. Mi Interface tb – C++ mk. Proc – BSV CSR PC Core i. Mem d. Mem Oct 16, 2015 http: //csg. csail. mit. edu/6. 175 T 03 -14

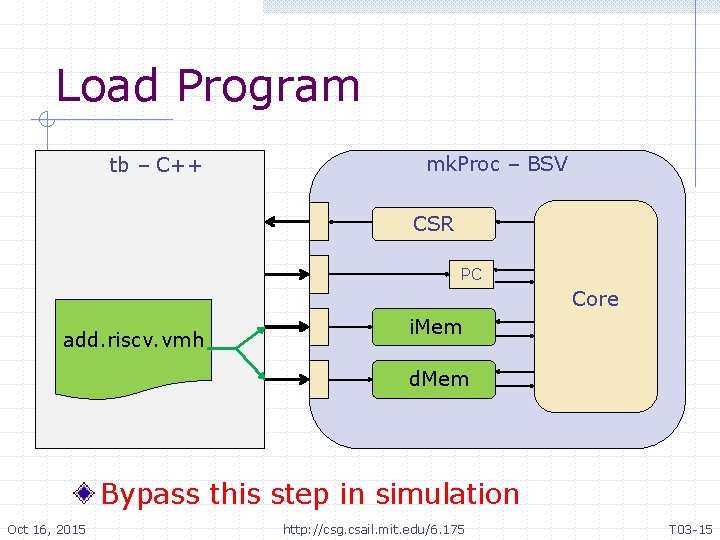

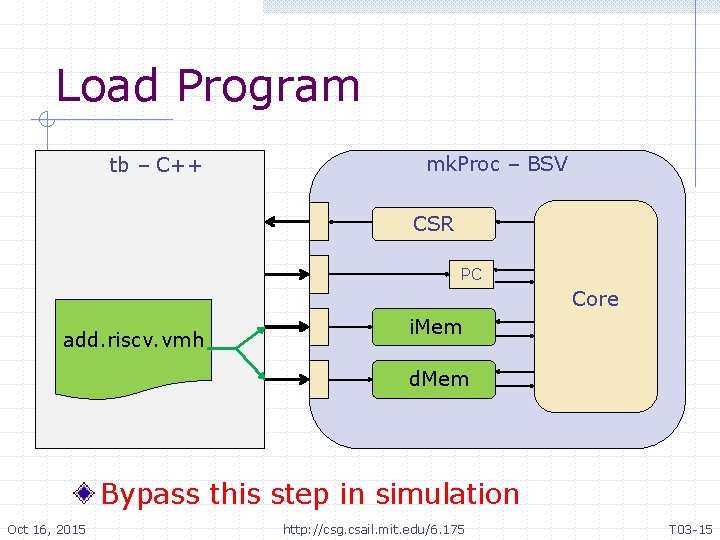

Load Program tb – C++ mk. Proc – BSV CSR PC Core add. riscv. vmh i. Mem d. Mem Bypass this step in simulation Oct 16, 2015 http: //csg. csail. mit. edu/6. 175 T 03 -15

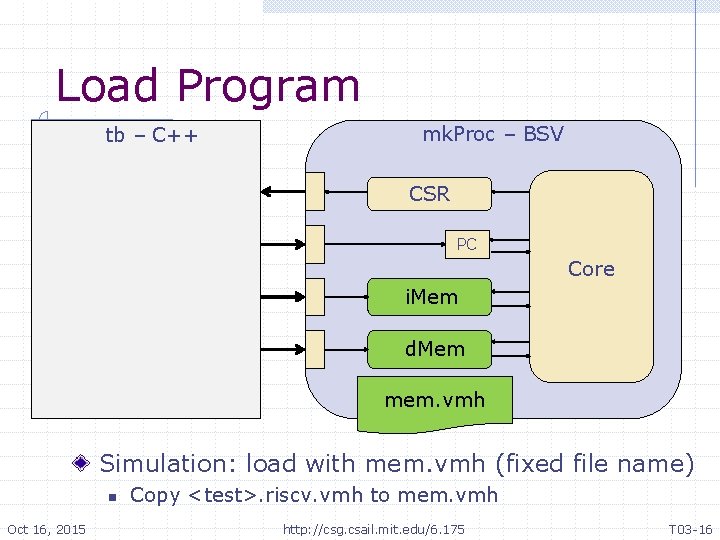

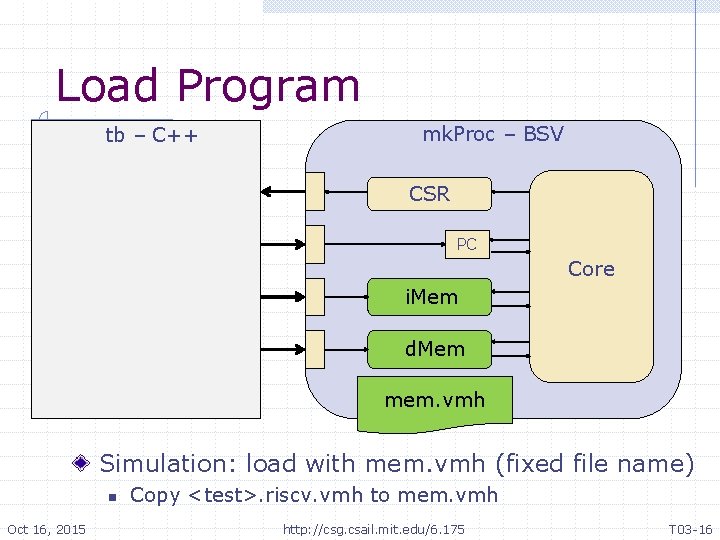

Load Program tb – C++ mk. Proc – BSV CSR PC Core i. Mem d. Mem mem. vmh Simulation: load with mem. vmh (fixed file name) n Oct 16, 2015 Copy <test>. riscv. vmh to mem. vmh http: //csg. csail. mit. edu/6. 175 T 03 -16

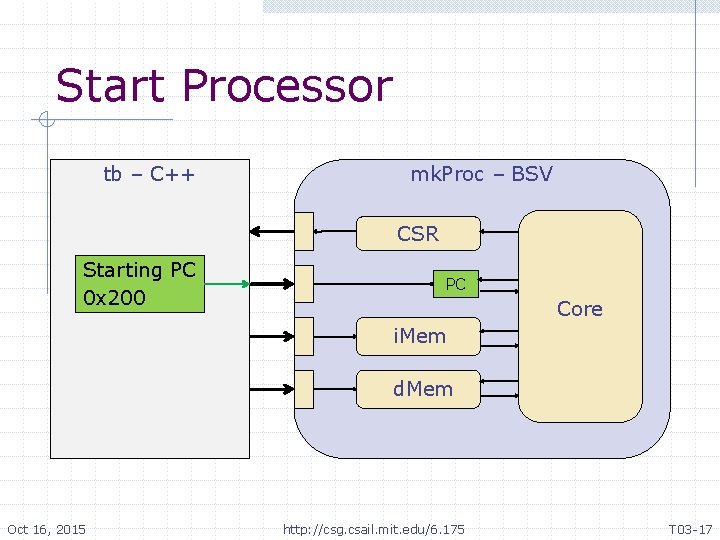

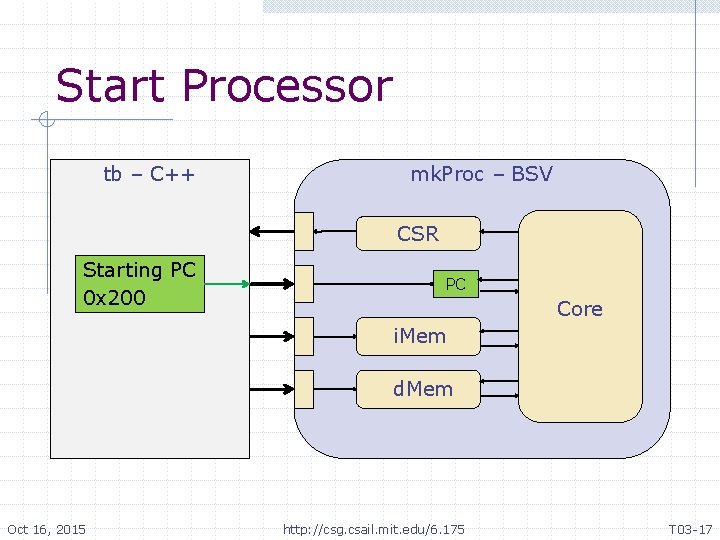

Start Processor tb – C++ mk. Proc – BSV CSR Starting PC 0 x 200 PC Core i. Mem d. Mem Oct 16, 2015 http: //csg. csail. mit. edu/6. 175 T 03 -17

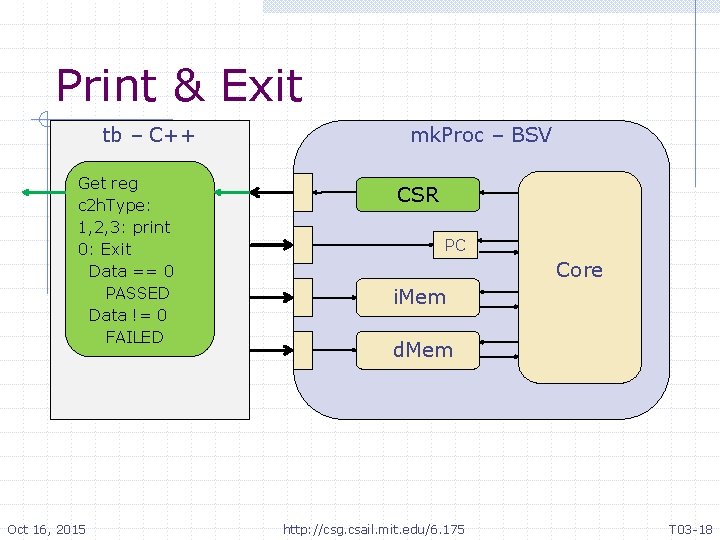

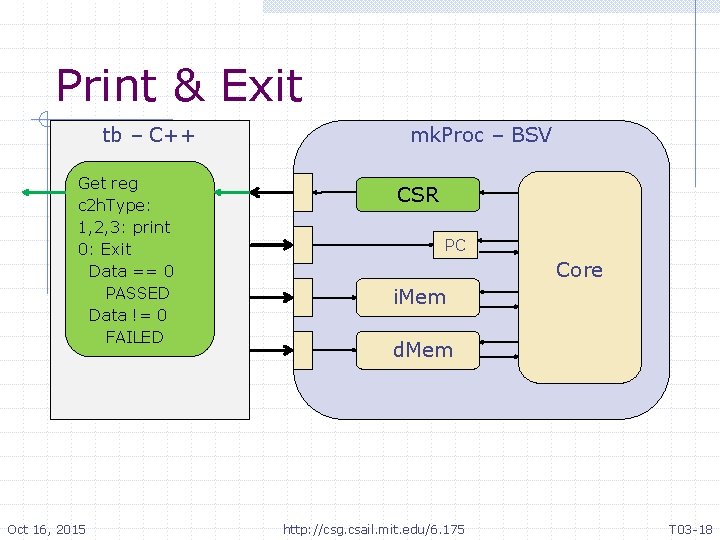

Print & Exit tb – C++ Get reg c 2 h. Type: 1, 2, 3: print 0: Exit Data == 0 PASSED Data != 0 FAILED Oct 16, 2015 mk. Proc – BSV CSR PC Core i. Mem d. Mem http: //csg. csail. mit. edu/6. 175 T 03 -18

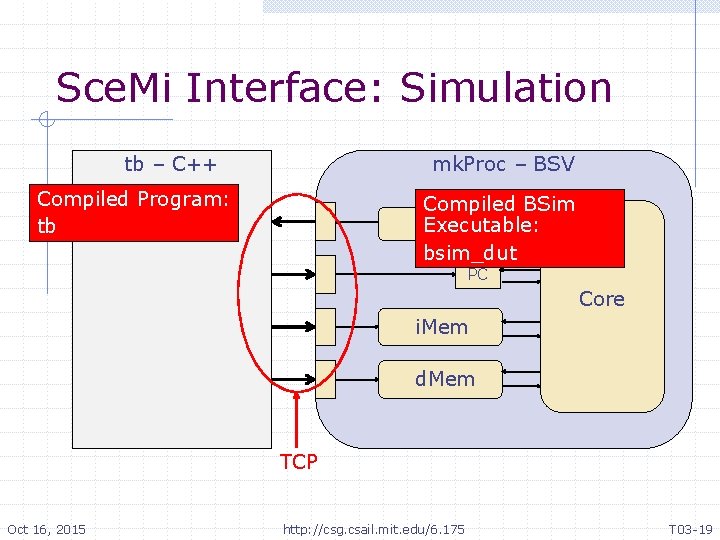

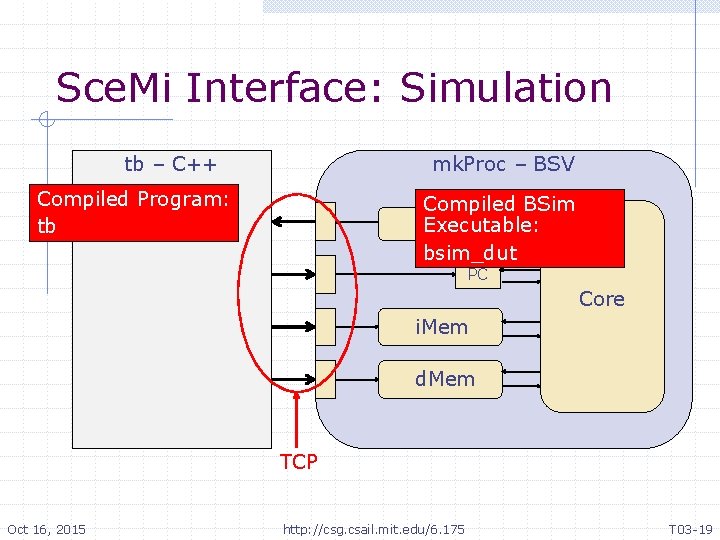

Sce. Mi Interface: Simulation tb – C++ mk. Proc – BSV Compiled Program: tb Compiled BSim COP Executable: bsim_dut PC Core i. Mem d. Mem TCP Oct 16, 2015 http: //csg. csail. mit. edu/6. 175 T 03 -19

Build and Run Processor Oct 16, 2015 http: //csg. csail. mit. edu/6. 175 T 03 -20

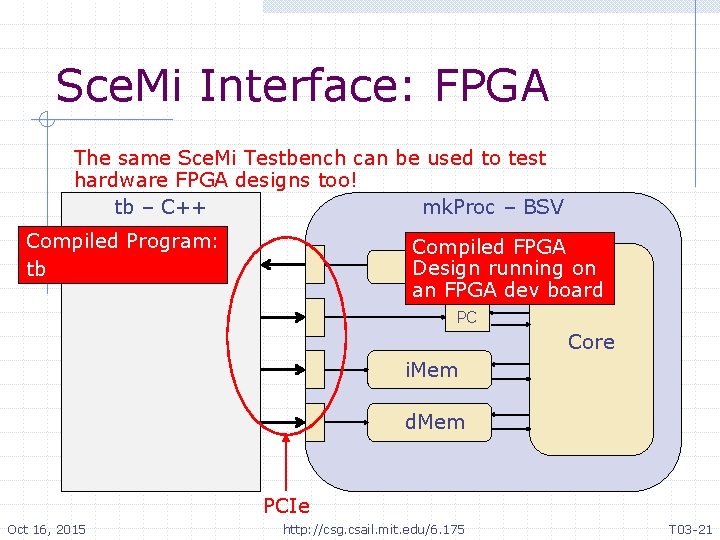

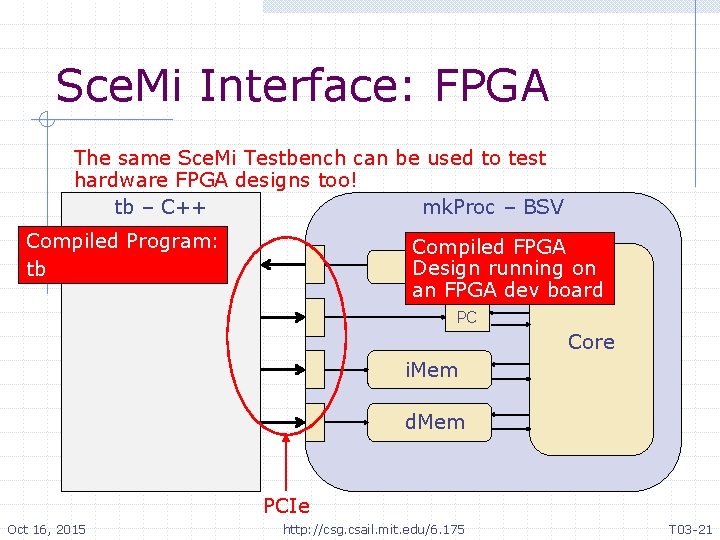

Sce. Mi Interface: FPGA The same Sce. Mi Testbench can be used to test hardware FPGA designs too! tb – C++ mk. Proc – BSV Compiled Program: tb Compiled FPGA COP Design running on an FPGA dev board PC Core i. Mem d. Mem PCIe Oct 16, 2015 http: //csg. csail. mit. edu/6. 175 T 03 -21

Sce. Mi Code Oct 16, 2015 http: //csg. csail. mit. edu/6. 175 T 03 -22

RISC-V Assembly Oct 16, 2015 http: //csg. csail. mit. edu/6. 175 T 03 -23